# E·XFL

#### AMD Xilinx - XC2VP40-6FG676I Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| 5 |

|---|

|   |

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 4848                                                        |

| Number of Logic Elements/Cells | 43632                                                       |

| Total RAM Bits                 | 3538944                                                     |

| Number of I/O                  | 416                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 676-BGA                                                     |

| Supplier Device Package        | 676-FBGA (27x27)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2vp40-6fg676i |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

implemented. In system mode, a Virtex-II Pro device will continue to function while executing non-test Boundary-Scan instructions. In test mode, Boundary-Scan test instructions control the I/O pins for testing purposes. The Virtex-II Pro Test Access Port (TAP) supports BYPASS, PRELOAD, SAMPLE, IDCODE, and USERCODE non-test instructions. The EXTEST, INTEST, and HIGHZ test instructions are also supported.

#### Configuration

Virtex-II Pro / Virtex-II Pro devices are configured by loading the bitstream into internal configuration memory using one of the following modes:

- Slave-serial mode

- Master-serial mode

- Slave SelectMAP mode

- Master SelectMAP mode

- Boundary-Scan mode (IEEE 1532)

A Data Encryption Standard (DES) decryptor is available on-chip to secure the bitstreams. One or two triple-DES key sets can be used to optionally encrypt the configuration data.

The Xilinx System Advanced Configuration Environment (System ACE) family offers high-capacity and flexible solution for FPGA configuration as well as program/data storage for the processor. See <u>DS080</u>, *System ACE CompactFlash Solution* for more information.

#### Readback and Integrated Logic Analyzer

Configuration data stored in Virtex-II Pro / Virtex-II Pro configuration memory can be read back for verification. Along with the configuration data, the contents of all flip-flops and latches, distributed SelectRAM+, and block SelectRAM+ memory resources can be read back. This capability is useful for real-time debugging. The Xilinx ChipScope Integrated Logic Analyzer (ILA) cores and Integrated Bus Analyzer (IBA) cores, along with the ChipScope Pro Analyzer software, provide a complete solution for accessing and verifying user designs within Virtex-II Pro devices.

# **IP Core and Reference Support**

Intellectual Property is part of the Platform FPGA solution. In addition to the existing FPGA fabric cores, the list below shows some of the currently available hardware and software intellectual properties specially developed for Virtex-II Pro / Virtex-II Pro X by Xilinx. Each IP core is modular, portable, Real-Time Operating System (RTOS) independent, and CoreConnect compatible for ease of design migration. Refer to <u>www.xilinx.com/ipcenter</u> for the latest and most complete list of cores.

#### Hardware Cores

- Bus Infrastructure cores (arbiters, bridges, and more)

- Memory cores (DDR, Flash, and more)

- Peripheral cores (UART, IIC, and more)

- Networking cores (ATM, Ethernet, and more)

#### **Software Cores**

- Boot code

- Test code

- Device drivers

- Protocol stacks

- RTOS integration

- Customized board support package

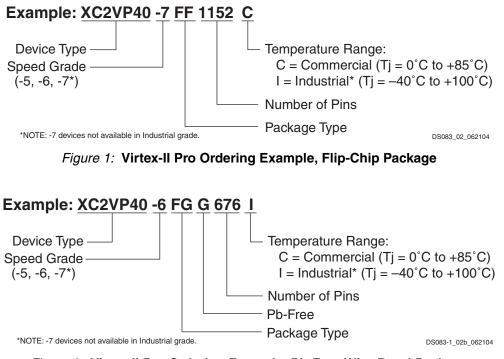

# **Virtex-II Pro Ordering Examples**

Virtex-II Pro ordering examples are shown in Figure 1 (flip-chip package) and Figure 2 (Pb-free wire-bond package).

Figure 2: Virtex-II Pro Ordering Example, Pb-Free Wire-Bond Package

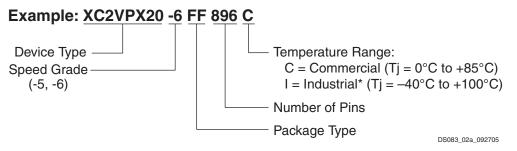

# Virtex-II Pro X Ordering Example

A Virtex-II Pro X ordering example is shown in Figure 3.

Figure 3: Virtex-II Pro X Ordering Example, Flip-Chip Package

### **Disparity Control**

The 8B/10B encoder is initialized with a negative running disparity. Unique control allows forcing the current running disparity state.

TXRUNDISP signals its current running disparity. This may be useful in those cases where there is a need to manipulate the initial running disparity value.

Bits TXCHARDISPMODE and TXCHARDISPVAL control the generation of running disparity before each byte.

For example, the transceiver can generate the sequence

```

K28.5+ K28.5+ K28.5- K28.5-

Or

K28.5- K28.5- K28.5+ K28.5+

```

by specifying inverted running disparity for the second and fourth bytes.

#### Transmit FIFO

Proper operation of the circuit is only possible if the FPGA clock (TXUSRCLK) is frequency-locked to the reference clock (REFCLK). Phase variations up to one clock cycle are allowable. The FIFO has a depth of four. Overflow or underflow conditions are detected and signaled at the interface. Bypassing of this FIFO is programmable.

#### 8B/10B Encoder

Note: In the RocketIO transceiver, the most-significant byte is sent first; in the RocketIO X transceiver, the least-significant byte is sent first.

A bypassable 8B/10B encoder is included. The encoder uses the same 256 data characters and 12 control characters used by Gigabit Ethernet, Fibre Channel, and InfiniBand.

The encoder accepts 8 bits of data along with a K-character signal for a total of 9 bits per character applied, and generates a 10 bit character for transmission. If the K-character signal is High, the data is encoded into one of the twelve possible K-characters available in the 8B/10B code. If the K-character input is Low, the 8 bits are encoded as standard data. If the K-character input is High, and a user applies other than one of the twelve possible combinations, TXKERR indicates the error.

#### 8B/10B Decoder

Note: In the RocketIO transceiver, the most-significant byte is sent first; in the RocketIO X transceiver, the least-significant byte is sent first.

An optional 8B/10B decoder is included. A programmable option allows the decoder to be bypassed. When the 8B/10B decoder is bypassed, the 10-bit character order is, for example,

| RXCHARISK[0] | (first bit received)             |

|--------------|----------------------------------|

| RXRUNDISP[0] |                                  |

| RXDATA[7:0]  | (last bit received is RXDATA[0]) |

The decoder uses the same table that is used for Gigabit Ethernet, Fibre Channel, and InfiniBand. In addition to

decoding all data and K-characters, the decoder has several extra features. The decoder separately detects both "disparity errors" and "out-of-band" errors. A disparity error is the reception of 10-bit character that exists within the 8B/10B table but has an incorrect disparity. An out-of-band error is the reception of a 10-bit character that does not exist within the 8B/10B table. It is possible to obtain an out-of-band error without having a disparity error. The proper disparity is always computed for both legal and illegal characters. The current running disparity is available at the RXRUNDISP signal.

The 8B/10B decoder performs a unique operation if out-of-band data is detected. If out-of-band data is detected, the decoder signals the error and passes the illegal 10-bits through and places them on the outputs. This can be used for debugging purposes if desired.

The decoder also signals the reception of one of the 12 valid K-characters. In addition, a programmable comma detect is included. The comma detect signal registers a comma on the receipt of any comma+, comma-, or both. Since the comma is defined as a 7-bit character, this includes several out-of-band characters. Another option allows the decoder to detect only the three defined commas (K28.1, K28.5, and K28.7) as comma+, comma-, or both. In total, there are six possible options, three for valid commas and three for "any comma."

Note that all bytes (1, 2, 4, or 8) at the RX FPGA interface each have their own individual 8B/10B indicators (K-character, disparity error, out-of-band error, current running disparity, and comma detect).

#### **Receiver Buffer**

The receiver includes buffers (FIFOs) in the datapath. This section gives the reasons for including the buffers and outlines their operation.

The receiver buffer is required for two reasons:

- *Clock correction* to accommodate the slight difference in frequency between the recovered clock RXRECCLK and the internal FPGA user clock RXUSRCLK

- *Channel bonding* to allow realignment of the input stream to ensure proper alignment of data being read through multiple transceivers

The receiver uses an *elastic buffer*, where "elastic" refers to the ability to modify the read pointer for clock correction and channel bonding.

#### **Comma Detection**

Word alignment is dependent on the state of comma detect bits. If comma detect is enabled, the transceiver recognizes up to two 10-bit preprogrammed characters. Upon detection of the character or characters, the comma detect output is driven high and the data is synchronously aligned. If a comma is detected and the data is aligned, no further alignment alteration takes place. If a comma is received and realignment is necessary, the data is realigned and an indi-

# XILINX<sup>®</sup>

- Single-cycle and multi-cycle mode option for I-side and D-side interfaces

- Single cycle = one CPU clock cycle; multi-cycle = minimum of two and maximum of eight CPU clock cycles

- FPGA configurable DCR addresses within DSOCM and ISOCM.

- Independent 16 MB logical memory space available within PPC405 memory map for each of the DSOCM and ISOCM. The number of block RAMs in the device might limit the maximum amount of OCM supported.

- Maximum of 64K and 128K bytes addressable from DSOCM and ISOCM interfaces, respectively, using address outputs from OCM directly without additional decoding logic.

#### Data-Side OCM (DSOCM)

- 32-bit Data Read bus and 32-bit Data Write bus

- Byte write access to DSBRAM support

- Second port of dual port DSBRAM is available to read/write from an FPGA interface

- 22-bit address to DSBRAM port

- 8-bit DCR Registers: DSCNTL, DSARC

- Three alternatives to write into DSBRAM: BRAM initialization, CPU, FPGA H/W using second port

#### Instruction-Side OCM (ISOCM)

The ISOCM interface contains a 64-bit read only port, for instruction fetches, and a 32-bit write only port, to initialize or test the ISBRAM. When implementing the read only port, the user must deassert the write port inputs. The preferred method of initializing the ISBRAM is through the configuration bitstream.

- 64-bit Data Read Only bus (two instructions per cycle)

- 32-bit Data Write Only bus (through DCR)

- Separate 21-bit address to ISBRAM

- 8-bit DCR Registers: ISCNTL, ISARC

- 32-bit DCR Registers: ISINIT, ISFILL

- Two alternatives to write into ISBRAM: BRAM initialization, DCR and write instruction

# **Clock/Control Interface Logic**

The clock/control interface logic provides proper initialization and connections for PPC405 clock/power management, resets, PLB cycle control, and OCM interfaces. It also couples user signals between the FPGA fabric and the embedded PPC405 CPU core.

The processor clock connectivity is similar to CLB clock pins. It can connect either to global clock nets or general routing resources. Therefore the processor clock source can come from DCM, CLB, or user package pin.

#### **CPU-FPGA Interfaces**

All Processor Block user pins link up with the general FPGA routing resources through the CPU-FPGA interface. Therefore processor signals have the same routability as other

non-Processor Block user signals. Longlines and hex lines travel across the Processor Block both vertically and horizontally, allowing signals to route through the Processor Block.

#### Processor Local Bus (PLB) Interfaces

The PPC405 core accesses high-speed system resources through PLB interfaces on the instruction and data cache controllers. The PLB interfaces provide separate 32-bit address/64-bit data buses for the instruction and data sides.

The cache controllers are both PLB masters. PLB arbiters are implemented in the FPGA fabric and are available as soft IP cores.

#### Device Control Register (DCR) Bus Interface

The device control register (DCR) bus has 10 bits of address space for components external to the PPC405 core. Using the DCR bus to manage status and configuration registers reduces PLB traffic and improves system integrity. System resources on the DCR bus are protected or isolated from wayward code since the DCR bus is not part of the system memory map.

#### External Interrupt Controller (EIC) Interface

Two level-sensitive user interrupt pins (critical and non-critical) are available. They can be either driven by user defined logic or Xilinx soft interrupt controller IP core outside the Processor Block.

#### Clock/Power Management (CPM) Interface

The CPM interface supports several methods of clock distribution and power management. Three modes of operation that reduce power consumption below the normal operational level are available.

#### Reset Interface

There are three user reset input pins (core, chip, and system) and three user reset output pins for different levels of reset, if required.

#### **Debug Interface**

Debugging interfaces on the embedded PPC405 core, consisting of the JTAG and Trace ports, offer access to resources internal to the core and assist in software development. The JTAG port provides basic JTAG chip testing functionality as well as the ability for external debug tools to gain control of the processor for debug purposes. The Trace port furnishes programmers with a mechanism for acquiring instruction execution traces.

The JTAG port is compatible with IEEE Std 1149.1, which defines a test access port (TAP) and Boundary-Scan architecture. Extensions to the JTAG interface provide debuggers with processor control that includes stopping, starting, and stepping the PPC405 core. These extensions are compliant with the IEEE 1149.1 specifications for vendor-specific extensions.

synchronously. The sequence can also be paused at any stage, until lock has been achieved on any or all DCMs, as well as DCI.

## Readback

In this mode, configuration data from the Virtex-II Pro FPGA device can be read back. Readback is supported only in the SelectMAP (master and slave) and Boundary-Scan mode.

Along with the configuration data, it is possible to read back the contents of all registers, distributed SelectRAM+, and block RAM resources. This capability is used for real-time debugging. For more detailed configuration information, see the *Virtex-II Pro Platform FPGA User Guide*.

#### **Bitstream Encryption**

Virtex-II Pro devices have an on-chip decryptor using one or two sets of three keys for triple-key Data Encryption Standard (DES) operation. Xilinx software tools offer an optional encryption of the configuration data (bitstream) with a triple-key DES determined by the designer.

The keys are stored in the FPGA by JTAG instruction and retained by a battery connected to the  $V_{BATT}$  pin, when the device is not powered. Virtex-II Pro devices can be config-

ured with the corresponding encrypted bitstream, using any of the configuration modes described previously.

A detailed description of how to use bitstream encryption is provided in the <u>Virtex-II Pro Platform FPGA User Guide</u>. Your local FAE can also provide specific information on this feature.

#### **Partial Reconfiguration**

Partial reconfiguration of Virtex-II Pro devices can be accomplished in either Slave SelectMAP mode or Boundary-Scan mode. Instead of resetting the chip and doing a full configuration, new data is loaded into a specified area of the chip, while the rest of the chip remains in operation. Data is loaded on a column basis, with the smallest load unit being a configuration "frame" of the bitstream (device size dependent).

Partial reconfiguration is useful for applications that require different designs to be loaded into the same area of a chip, or that require the ability to change portions of a design without having to reset or reconfigure the entire chip.

For more information on Partial Reconfiguration in Virtex-II Pro devices, please refer to Xilinx Application Note XAPP290, *Two Flows for Partial Reconfiguration*.

# **Revision History**

This section records the change history for this module of the data sheet.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01/31/02 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                   |

| 06/13/02 | 2.0     | New Virtex-II Pro family members. New timing parameters per speedsfile v1.62.                                                                                                                                                                                                                                                             |

| 09/03/02 | 2.1     | <ul> <li>Revised Reset and Power sections.</li> <li>Updated Table 8, which lists compatible input standards. [Table deleted in v2.6.]</li> <li>Added Figure 28, Figure 29, and Figure 30, which provide examples illustrating the use of I/O standards.</li> </ul>                                                                        |

| 09/27/02 | 2.2     | <ul> <li>In section RocketIO Overview, corrected max number of MGTs from 16 to 24.</li> <li>In section Input/Output Blocks (IOBs), added references to XAPP653 regarding implementation of 3.3V I/O standards.</li> </ul>                                                                                                                 |

| 11/20/02 | 2.3     | <ul> <li>Table 8: Added rows for LVTTL, LVCMOS33, and PCI-X.</li> <li>Table 8: Added LVTTL and LVCMOS33 to compatible 3.3V cells. [Table deleted in v2.6.]</li> <li>Table 33: Correct bitstream lengths.</li> </ul>                                                                                                                       |

| 12/03/02 | 2.4     | Added mention of LVTTL and PCI with respect to SelectIO-Ultra configurations. See section Input/Output Individual Options and Figure 22.                                                                                                                                                                                                  |

| 01/20/03 | 2.5     | <ul> <li>Added qualification to features vs. Virtex-II (open-drain output pin TDO does not have internal pull-up resistor)</li> <li>Table 7: Added HSTL18 (I, II, III, &amp; IV) and HSTL18_DCI (I,II, III &amp; IV) to 1.8V VCCO row. [Table deleted in v2.6.]</li> <li>Table 8: Numerous revisions. [Table deleted in v2.6.]</li> </ul> |

#### Table 27: RocketIO Transmitter Switching Characteristics

| Description                                       | Symbol             | Conditions               | Min   | Тур | Max                  | Units             |

|---------------------------------------------------|--------------------|--------------------------|-------|-----|----------------------|-------------------|

|                                                   |                    | Flipchip packages        | 1.0   |     | 3.125 <sup>(1)</sup> | Gb/s              |

| Serial data rate, full-speed clock                | _                  | Wirebond packages        | 1.0   |     | 2.5 <sup>(1)</sup>   | Gb/s              |

| Serial data rate, half-speed clock <sup>(3)</sup> | — F <sub>GTX</sub> | Flipchip packages        | 0.600 |     | 1.0                  | Gb/s              |

| (2X oversampling)                                 |                    | Wirebond packages        | 0.600 |     | 1.0                  | Gb/s              |

|                                                   |                    | 2.126 Gb/s – 3.125 Gb/s  |       |     | 0.17                 | UI <sup>(2)</sup> |

|                                                   |                    | 1.0626 Gb/s – 2.125 Gb/s |       |     | 0.08                 | UI                |

| Serial data output deterministic jitter           | T <sub>DJ</sub>    | 1.0 Gb/s – 1.0625 Gb/s   |       |     | 0.05                 | UI                |

|                                                   |                    | 600 Mb/s – 999 Mb/s      |       |     | 0.08 <sup>(4)</sup>  | UI                |

|                                                   |                    | 2.126 Gb/s – 3.125 Gb/s  |       |     | 0.18                 | UI                |

| Carial data autout vandara iittav                 |                    | 1.0626 Gb/s – 2.125 Gb/s |       |     | 0.19                 | UI                |

| Serial data output random jitter                  | T <sub>RJ</sub>    | 1.0 Gb/s – 1.0625 Gb/s   |       |     | 0.18                 | UI                |

|                                                   |                    | 600 Mb/s – 999 Mb/s      |       |     | 0.18 <sup>(4)</sup>  | UI                |

| TX rise time                                      | T <sub>RTX</sub>   | 000/ 000/                |       | 120 |                      | ps                |

| TX fall time                                      | T <sub>FTX</sub>   | 20% - 80%                |       | 120 |                      | ps                |

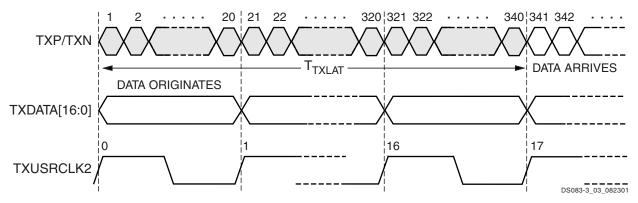

| Transmit latency <sup>(5)</sup>                   | т                  | Including CRC            |       | 14  | 17                   | TXUSR<br>CLK      |

|                                                   | T <sub>TXLAT</sub> | Excluding CRC            |       | 8   | 11                   | cycles            |

| TXUSRCLK duty cycle                               | T <sub>TXDC</sub>  |                          | 45    | 50  | 55                   | %                 |

| TXUSRCLK2 duty cycle                              | T <sub>TX2DC</sub> |                          | 45    | 50  | 55                   | %                 |

#### Notes:

1. Serial data rate in the -5 speed grade is limited to 2.0 Gb/s in both wirebond and flipchip packages.

2. UI = Unit Interval

3. For serial rates under 1 Gb/s, the 3X (or greater) oversampling techniques described in XAPP572 are required to meet the transmit jitter and receive jitter tolerance specifications defined in this data sheet.

4. The oversampling techniques described in XAPP572 are required to meet these specifications for serial rates less than 1 Gb/s.

5. Transmit latency delay TXDATA to TXP/TXN. Refer to RocketIO Transceiver User Guide for more information on calculating latency.

Figure 5: RocketIO Transmit Latency (Maximum, Including CRC)

#### Global Clock Set-Up and Hold for LVCMOS25 Standard, Without DCM

#### Table 56: Global Clock Set-Up and Hold for LVCMOS25 Standard, Without DCM

|                                                                                                                                                                                                                                                                            |                                      |          | Speed Grade |            |            |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------|-------------|------------|------------|-------|

| Description                                                                                                                                                                                                                                                                | Symbol                               | Device   | -7          | -6         | -5         | Units |

| Input Setup and Hold Time Relative to<br>Global Clock Input Signal for LVCMOS25<br>Standard.<br>For data input with different standards,<br>adjust the setup time delay by the values<br>shown in IOB Input Switching<br>Characteristics Standard Adjustments,<br>page 25. |                                      |          |             |            |            |       |

| Full Delay                                                                                                                                                                                                                                                                 |                                      |          |             |            |            |       |

| Global Clock and IFF without DCM                                                                                                                                                                                                                                           | T <sub>PSFD</sub> /T <sub>PHFD</sub> | XC2VP2   | 1.80/-0.44  | 1.85/-0.41 | 1.96/0.43  | ns    |

|                                                                                                                                                                                                                                                                            |                                      | XC2VP4   | 1.82/-0.53  | 1.83/-0.31 | 1.90/-0.29 | ns    |

|                                                                                                                                                                                                                                                                            |                                      | XC2VP7   | 1.80/-0.34  | 1.81/-0.24 | 1.88/-0.19 | ns    |

|                                                                                                                                                                                                                                                                            |                                      | XC2VP20  | 1.76/-0.24  | 1.83/-0.17 | 1.92/0.15  | ns    |

|                                                                                                                                                                                                                                                                            |                                      | XC2VPX20 | 1.76/-0.24  | 1.83/-0.17 | 1.92/-0.15 | ns    |

|                                                                                                                                                                                                                                                                            |                                      | XC2VP30  | 1.75/-0.22  | 1.92/0.26  | 1.99/0.23  | ns    |

|                                                                                                                                                                                                                                                                            |                                      | XC2VP40  | 2.25/-0.54  | 2.40/-0.56 | 2.49/-0.54 | ns    |

|                                                                                                                                                                                                                                                                            |                                      | XC2VP50  | 2.93/-1.02  | 2.98/-0.93 | 3.00/-0.83 | ns    |

|                                                                                                                                                                                                                                                                            |                                      | XC2VP70  | 2.79/-0.72  | 2.79/-0.55 | 2.78/-0.41 | ns    |

|                                                                                                                                                                                                                                                                            |                                      | XC2VPX70 | 2.79/-0.72  | 2.79/-0.55 | 2.78/-0.41 | ns    |

|                                                                                                                                                                                                                                                                            |                                      | XC2VP100 | N/A         | 5.58/-2.35 | 5.60/-2.35 | ns    |

#### Notes:

1. IFF = Input Flip-Flop or Latch

2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

3. A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

#### Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                 | Pin    |        | No Connects |        |

|------|-----------------|--------|--------|-------------|--------|

| Bank | Pin Description | Number | XC2VP2 | XC2VP4      | XC2VP7 |

| 2    | VCCO_2          | K2     |        |             |        |

| 2    | VCCO_2          | K8     |        |             |        |

| 2    | VCCO_2          | L9     |        |             |        |

| 2    | VCCO_2          | M9     |        |             |        |

| 2    | VCCO_2          | N9     |        |             |        |

| 3    | VCCO_3          | P9     |        |             |        |

| 3    | VCCO_3          | R9     |        |             |        |

| 3    | VCCO_3          | Т9     |        |             |        |

| 3    | VCCO_3          | U2     |        |             |        |

| 3    | VCCO_3          | U8     |        |             |        |

| 3    | VCCO_3          | V8     |        |             |        |

| 3    | VCCO_3          | Y2     |        |             |        |

| 4    | VCCO_4          | W9     |        |             |        |

| 4    | VCCO_4          | AD7    |        |             |        |

| 4    | VCCO_4          | V11    |        |             |        |

| 4    | VCCO_4          | V12    |        |             |        |

| 4    | VCCO_4          | V13    |        |             |        |

| 4    | VCCO_4          | W10    |        |             |        |

| 4    | VCCO_4          | AD10   |        |             |        |

| 5    | VCCO_5          | V14    |        |             |        |

| 5    | VCCO_5          | V15    |        |             |        |

| 5    | VCCO_5          | V16    |        |             |        |

| 5    | VCCO_5          | W17    |        |             |        |

| 5    | VCCO_5          | W18    |        |             |        |

| 5    | VCCO_5          | AD17   |        |             |        |

| 5    | VCCO_5          | AD20   |        |             |        |

| 6    | VCCO_6          | P18    |        |             |        |

| 6    | VCCO_6          | R18    |        |             |        |

| 6    | VCCO_6          | T18    |        |             |        |

| 6    | VCCO_6          | U19    |        |             |        |

| 6    | <br>VCCO_6      | U25    |        |             |        |

| 6    | VCCO_6          | V19    |        |             |        |

| 6    | <br>VCCO_6      | Y25    |        |             |        |

| 7    | VCCO_7          | G25    |        |             |        |

| 7    | VCCO_7          | J19    |        |             |        |

| 7    | VCCO_7          | K19    |        |             |        |

| 7    | VCCO_7          | K25    |        |             |        |

#### Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                 | Pin    | No Connects |        |        |  |

|------|-----------------|--------|-------------|--------|--------|--|

| Bank | Pin Description | Number | XC2VP2      | XC2VP4 | XC2VP7 |  |

| N/A  | AVCCAUXRX19     | AE15   |             |        |        |  |

| N/A  | VTRXPAD19       | AE16   |             |        |        |  |

| N/A  | RXNPAD19        | AF15   |             |        |        |  |

| N/A  | RXPPAD19        | AF16   |             |        |        |  |

| N/A  | GNDA19          | AD16   |             |        |        |  |

| N/A  | TXPPAD19        | AF17   |             |        |        |  |

| N/A  | TXNPAD19        | AF18   |             |        |        |  |

| N/A  | VTTXPAD19       | AE18   |             |        |        |  |

| N/A  | AVCCAUXTX19     | AE17   |             |        |        |  |

| N/A  | AVCCAUXRX21     | AE20   | NC          | NC     |        |  |

| N/A  | VTRXPAD21       | AE21   | NC          | NC     |        |  |

| N/A  | RXNPAD21        | AF20   | NC          | NC     |        |  |

| N/A  | RXPPAD21        | AF21   | NC          | NC     |        |  |

| N/A  | GNDA21          | AD22   | NC          | NC     |        |  |

| N/A  | TXPPAD21        | AF22   | NC          | NC     |        |  |

| N/A  | TXNPAD21        | AF23   | NC          | NC     |        |  |

| N/A  | VTTXPAD21       | AE23   | NC          | NC     |        |  |

| N/A  | AVCCAUXTX21     | AE22   | NC          | NC     |        |  |

|      |                 |        |             |        |        |  |

| N/A  | VCCINT          | H8     |             |        |        |  |

| N/A  | VCCINT          | J9     |             |        |        |  |

| N/A  | VCCINT          | К9     |             |        |        |  |

| N/A  | VCCINT          | U9     |             |        |        |  |

| N/A  | VCCINT          | V9     |             |        |        |  |

| N/A  | VCCINT          | W8     |             |        |        |  |

| N/A  | VCCINT          | H19    |             |        |        |  |

| N/A  | VCCINT          | J10    |             |        |        |  |

| N/A  | VCCINT          | J17    |             |        |        |  |

| N/A  | VCCINT          | J18    |             |        |        |  |

| N/A  | VCCINT          | K11    |             |        |        |  |

| N/A  | VCCINT          | K16    |             |        |        |  |

| N/A  | VCCINT          | K18    |             |        |        |  |

| N/A  | VCCINT          | L10    |             |        |        |  |

| N/A  | VCCINT          | L17    |             |        |        |  |

| N/A  | VCCINT          | T10    |             |        |        |  |

| N/A  | VCCINT          | T17    |             |        |        |  |

| N/A  | VCCINT          | U11    |             |        |        |  |

#### Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                 | Pin    | No Connects |        |        |  |  |

|------|-----------------|--------|-------------|--------|--------|--|--|

| Bank | Pin Description | Number | XC2VP2      | XC2VP4 | XC2VP7 |  |  |

| N/A  | GND             | K15    |             |        |        |  |  |

| N/A  | GND             | K17    |             |        |        |  |  |

| N/A  | GND             | L11    |             |        |        |  |  |

| N/A  | GND             | L12    |             |        |        |  |  |

| N/A  | GND             | L13    |             |        |        |  |  |

| N/A  | GND             | L14    |             |        |        |  |  |

| N/A  | GND             | L15    |             |        |        |  |  |

| N/A  | GND             | L16    |             |        |        |  |  |

| N/A  | GND             | M10    |             |        |        |  |  |

| N/A  | GND             | M11    |             |        |        |  |  |

| N/A  | GND             | M12    |             |        |        |  |  |

| N/A  | GND             | M13    |             |        |        |  |  |

| N/A  | GND             | M14    |             |        |        |  |  |

| N/A  | GND             | M15    |             |        |        |  |  |

| N/A  | GND             | M16    |             |        |        |  |  |

| N/A  | GND             | M17    |             |        |        |  |  |

| N/A  | GND             | N10    |             |        |        |  |  |

| N/A  | GND             | N11    |             |        |        |  |  |

| N/A  | GND             | N12    |             |        |        |  |  |

| N/A  | GND             | N13    |             |        |        |  |  |

| N/A  | GND             | N14    |             |        |        |  |  |

| N/A  | GND             | N15    |             |        |        |  |  |

| N/A  | GND             | N16    |             |        |        |  |  |

| N/A  | GND             | N17    |             |        |        |  |  |

| N/A  | GND             | P10    |             |        |        |  |  |

| N/A  | GND             | P11    |             |        |        |  |  |

| N/A  | GND             | P12    |             |        |        |  |  |

| N/A  | GND             | P13    |             |        |        |  |  |

| N/A  | GND             | P14    |             |        |        |  |  |

| N/A  | GND             | P15    |             |        |        |  |  |

| N/A  | GND             | P16    |             |        |        |  |  |

| N/A  | GND             | P17    |             |        |        |  |  |

| N/A  | GND             | R10    |             |        |        |  |  |

| N/A  | GND             | R11    |             |        |        |  |  |

| N/A  | GND             | R12    |             |        |        |  |  |

| N/A  | GND             | R13    |             |        |        |  |  |

| N/A  | GND             | R14    |             |        |        |  |  |

#### Table 9: FF896 — XC2VP7, XC2VP20, XC2VPX20, and XC2VP30

|      | Pin Description       |                            | No Connects   |        |                      |         |

|------|-----------------------|----------------------------|---------------|--------|----------------------|---------|

| Bank | Virtex-II Pro devices | XC2VPX20<br>(if Different) | Pin<br>Number | XC2VP7 | XC2VP20,<br>XC2VPX20 | XC2VP30 |

| 2    | IO_L59N_2             |                            | P8            |        |                      |         |

| 2    | IO_L59P_2             |                            | P7            |        |                      |         |

| 2    | IO_L60N_2             |                            | N4            |        |                      |         |

| 2    | IO_L60P_2             |                            | N3            |        |                      |         |

| 2    | IO_L85N_2             |                            | P3            |        |                      |         |

| 2    | IO_L85P_2             |                            | P2            |        |                      |         |

| 2    | IO_L86N_2             |                            | R8            |        |                      |         |

| 2    | IO_L86P_2             |                            | R7            |        |                      |         |

| 2    | IO_L87N_2             |                            | P5            |        |                      |         |

| 2    | IO_L87P_2             |                            | P4            |        |                      |         |

| 2    | IO_L88N_2/VREF_2      |                            | R2            |        |                      |         |

| 2    | IO_L88P_2             |                            | T2            |        |                      |         |

| 2    | IO_L89N_2             |                            | R6            |        |                      |         |

| 2    | IO_L89P_2             |                            | R5            |        |                      |         |

| 2    | IO_L90N_2             |                            | R4            |        |                      |         |

| 2    | IO_L90P_2             |                            | R3            |        |                      |         |

|      |                       |                            |               |        |                      |         |

| 3    | IO_L90N_3             |                            | U1            |        |                      |         |

| 3    | IO_L90P_3             |                            | V1            |        |                      |         |

| 3    | IO_L89N_3             |                            | T5            |        |                      |         |

| 3    | IO_L89P_3             |                            | Т6            |        |                      |         |

| 3    | IO_L88N_3             |                            | Т3            |        |                      |         |

| 3    | IO_L88P_3             |                            | T4            |        |                      |         |

| 3    | IO_L87N_3/VREF_3      |                            | U2            |        |                      |         |

| 3    | IO_L87P_3             |                            | U3            |        |                      |         |

| 3    | IO_L86N_3             |                            | T7            |        |                      |         |

| 3    | IO_L86P_3             |                            | Т8            |        |                      |         |

| 3    | IO_L85N_3             |                            | U4            |        |                      |         |

| 3    | IO_L85P_3             |                            | U5            |        |                      |         |

| 3    | IO_L60N_3             |                            | V2            |        |                      |         |

| 3    | IO_L60P_3             |                            | W2            |        |                      |         |

| 3    | IO_L59N_3             |                            | Т9            |        |                      |         |

| 3    | IO_L59P_3             |                            | U9            |        |                      |         |

| 3    | IO_L58N_3             |                            | V3            |        |                      |         |

| 3    | IO_L58P_3             |                            | V4            |        |                      |         |

| 3    | IO_L57N_3/VREF_3      |                            | W1            |        |                      |         |

#### Table 10: FF1152 — XC2VP20, XC2VP30, XC2VP40, and XC2VP50

|      |                                    | Pin    | No Connects |         |         |         |

|------|------------------------------------|--------|-------------|---------|---------|---------|

| Bank | Pin Description                    | Number | XC2VP20     | XC2VP30 | XC2VP40 | XC2VP50 |

| 3    | IO_L06P_3                          | AL2    |             |         |         |         |

| 3    | IO_L05N_3                          | AG7    |             |         |         |         |

| 3    | IO_L05P_3                          | AH8    |             |         |         |         |

| 3    | IO_L04N_3                          | AH5    |             |         |         |         |

| 3    | IO_L04P_3                          | AH6    |             |         |         |         |

| 3    | IO_L03N_3/VREF_3                   | AK3    |             |         |         |         |

| 3    | IO_L03P_3                          | AK4    |             |         |         |         |

| 3    | IO_L02N_3                          | AJ7    |             |         |         |         |

| 3    | IO_L02P_3                          | AJ8    |             |         |         |         |

| 3    | IO_L01N_3/VRP_3                    | AJ4    |             |         |         |         |

| 3    | IO_L01P_3/VRN_3                    | AJ5    |             |         |         |         |

|      |                                    |        | I           | 1       | ł       |         |

| 4    | IO_L01N_4/BUSY/DOUT <sup>(1)</sup> | AL5    |             |         |         |         |

| 4    | IO_L01P_4/INIT_B                   | AL6    |             |         |         |         |

| 4    | IO_L02N_4/D0/DIN <sup>(1)</sup>    | AG9    |             |         |         |         |

| 4    | IO_L02P_4/D1                       | AH9    |             |         |         |         |

| 4    | IO_L03N_4/D2                       | AK6    |             |         |         |         |

| 4    | IO_L03P_4/D3                       | AK7    |             |         |         |         |

| 4    | IO_L05_4/No_Pair                   | AF10   |             |         |         |         |

| 4    | IO_L06N_4/VRP_4                    | AL7    |             |         |         |         |

| 4    | IO_L06P_4/VRN_4                    | AM7    |             |         |         |         |

| 4    | IO_L07N_4                          | AE11   |             |         |         |         |

| 4    | IO_L07P_4/VREF_4                   | AF11   |             |         |         |         |

| 4    | IO_L08N_4                          | AG10   |             |         |         |         |

| 4    | IO_L08P_4                          | AH10   |             |         |         |         |

| 4    | IO_L09N_4                          | AK8    |             |         |         |         |

| 4    | IO_L09P_4/VREF_4                   | AL8    |             |         |         |         |

| 4    | IO_L19N_4                          | AE12   | NC          | NC      |         |         |

| 4    | IO_L19P_4                          | AF12   | NC          | NC      |         |         |

| 4    | IO_L20N_4                          | AJ9    | NC          | NC      |         |         |

| 4    | IO_L20P_4                          | AK9    | NC          | NC      |         |         |

| 4    | IO_L21N_4                          | AL9    | NC          | NC      |         |         |

| 4    | IO_L21P_4                          | AM9    | NC          | NC      |         |         |

| 4    | IO_L25N_4                          | AG11   | NC          | NC      |         |         |

| 4    | IO_L25P_4                          | AH11   | NC          | NC      |         |         |

| 4    | IO_L26N_4                          | AH12   | NC          | NC      |         |         |

| 4    | IO_L26P_4                          | AJ12   | NC          | NC      |         |         |

| 4    | IO_L27N_4                          | AK10   | NC          | NC      |         |         |

#### Table 11: FF1148 — XC2VP40 and XC2VP50

|      | Pin Description      |            | No Connects |         |  |

|------|----------------------|------------|-------------|---------|--|

| Bank |                      | Pin Number | XC2VP40     | XC2VP50 |  |

| 2    | IO_L21P_2            | E6         |             |         |  |

| 2    | IO_L22N_2/VREF_2     | F7         |             |         |  |

| 2    | IO_L22P_2            | F8         |             |         |  |

| 2    | IO_L23N_2            | M10        |             |         |  |

| 2    | IO_L23P_2            | L10        |             |         |  |

| 2    | IO_L24N_2            | G5         |             |         |  |

| 2    | IO_L24P_2            | F5         |             |         |  |

| 2    | IO_L25N_2            | F3         |             |         |  |

| 2    | IO_L25P_2            | F4         |             |         |  |

| 2    | IO_L26N_2            | M8         |             |         |  |

| 2    | IO_L26P_2            | M9         |             |         |  |

| 2    | IO_L27N_2            | F1         |             |         |  |

| 2    | IO_L27P_2            | F2         |             |         |  |

| 2    | IO_L28N_2/VREF_2     | G6         |             |         |  |

| 2    | IO_L28P_2            | G7         |             |         |  |

| 2    | IO_L29N_2            | M7         |             |         |  |

| 2    | IO_L29P_2            | N8         |             | -       |  |

| 2    | IO_L30N_2            | G3         |             | -       |  |

| 2    | IO_L30P_2            | H4         |             | -       |  |

| 2    | IO_L31N_2            | G1         |             |         |  |

| 2    | IO_L31P_2            | G2         |             |         |  |

| 2    | IO_L32N_2            | N10        |             |         |  |

| 2    | IO_L32P_2            | N11        |             |         |  |

| 2    | IO_L33N_2            | H5         |             |         |  |

| 2    | IO_L33P_2            | H6         |             |         |  |

| 2    | IO_L34N_2/VREF_2     | H2         |             | -       |  |

| 2    | IO_L34P_2            | H3         |             |         |  |

| 2    | IO_L35N_2            | N6         |             |         |  |

| 2    | IO_L35P_2            | N7         |             | -       |  |

| 2    | IO_L36N_2            | K4         |             |         |  |

| 2    | IO_L36P_2            | J4         |             |         |  |

| 2    | IO_L37N_2            | J2         |             |         |  |

| 2    | IO_L37P_2            | J3         |             |         |  |

| 2    | IO_L38N_2            | P10        |             |         |  |

| 2    | IO_L38P_2            | P11        |             | +       |  |

| 2    | IO_L39N_2            | K5         |             | +       |  |

| 2    | IO_L39P_2            | K6         |             | +       |  |

| 2    | <br>IO_L40N_2/VREF_2 | L3         |             | +       |  |

#### Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                  | Pin    | No Connects |         |  |

|------|------------------|--------|-------------|---------|--|

| Bank | Pin Description  | Number | XC2VP50     | XC2VP70 |  |

| 0    | IO_L34P_0        | E27    | NC          |         |  |

| 0    | IO_L35N_0        | L26    | NC          |         |  |

| 0    | IO_L35P_0        | L25    | NC          |         |  |

| 0    | IO_L36N_0        | G26    | NC          |         |  |

| 0    | IO_L36P_0/VREF_0 | H26    | NC          |         |  |

| 0    | IO_L37N_0        | E26    |             |         |  |

| 0    | IO_L37P_0        | F26    |             |         |  |

| 0    | IO_L38N_0        | K25    |             |         |  |

| 0    | IO_L38P_0        | K24    |             |         |  |

| 0    | IO_L39N_0        | C26    |             |         |  |

| 0    | IO_L39P_0        | D26    |             |         |  |

| 0    | IO_L43N_0        | H25    |             |         |  |

| 0    | IO_L43P_0        | J25    |             |         |  |

| 0    | IO_L44N_0        | M25    |             |         |  |

| 0    | IO_L44P_0        | M24    |             |         |  |

| 0    | IO_L45N_0        | F25    |             |         |  |

| 0    | IO_L45P_0/VREF_0 | G25    |             |         |  |

| 0    | IO_L46N_0        | C25    |             |         |  |

| 0    | IO_L46P_0        | D25    |             |         |  |

| 0    | IO_L47N_0        | L23    |             |         |  |

| 0    | IO_L47P_0        | M22    |             |         |  |

| 0    | IO_L48N_0        | H24    |             |         |  |

| 0    | IO_L48P_0        | J24    |             |         |  |

| 0    | IO_L49N_0        | E25    |             |         |  |

| 0    | IO_L49P_0        | E24    |             |         |  |

| 0    | IO_L50_0/No_Pair | N23    |             |         |  |

| 0    | IO_L53_0/No_Pair | M23    |             |         |  |

| 0    | IO_L54N_0        | H23    |             |         |  |

| 0    | IO_L54P_0        | J23    |             |         |  |

| 0    | IO_L55N_0        | F24    |             |         |  |

| 0    | IO_L55P_0        | G23    |             |         |  |

| 0    | IO_L56N_0        | K22    |             |         |  |

| 0    | IO_L56P_0        | L22    |             |         |  |

| 0    | IO_L57N_0        | C23    |             |         |  |

| 0    | IO_L57P_0/VREF_0 | D23    |             |         |  |

| 0    | IO_L58N_0        | H22    |             |         |  |

| 0    | IO_L58P_0        | J22    |             |         |  |

| 0    | IO_L59N_0        | N22    |             |         |  |

#### Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                 | Pin    | No Connects |         |  |

|------|-----------------|--------|-------------|---------|--|

| Bank | Pin Description | Number | XC2VP50     | XC2VP70 |  |

| N/A  | M2              | AJ29   |             |         |  |

| N/A  | ТСК             | E8     |             |         |  |

| N/A  | TDI             | L30    |             |         |  |

| N/A  | TDO             | L10    |             |         |  |

| N/A  | TMS             | F9     |             |         |  |

| N/A  | PWRDWN_B        | AP9    |             |         |  |

| N/A  | HSWAP_EN        | E32    |             |         |  |

| N/A  | RSVD            | D8     |             |         |  |

| N/A  | VBATT           | L11    |             |         |  |

| N/A  | DXP             | L29    |             |         |  |

| N/A  | DXN             | F31    |             |         |  |

| N/A  | AVCCAUXTX2      | B35    |             |         |  |

| N/A  | VTTXPAD2        | B36    |             |         |  |

| N/A  | TXNPAD2         | A36    |             |         |  |

| N/A  | TXPPAD2         | A35    |             |         |  |

| N/A  | GNDA2           | C34    |             |         |  |

| N/A  | RXPPAD2         | A34    |             |         |  |

| N/A  | RXNPAD2         | A33    |             |         |  |

| N/A  | VTRXPAD2        | B34    |             |         |  |

| N/A  | AVCCAUXRX2      | B33    |             |         |  |

| N/A  | AVCCAUXTX4      | B31    |             |         |  |

| N/A  | VTTXPAD4        | B32    |             |         |  |

| N/A  | TXNPAD4         | A32    |             |         |  |

| N/A  | TXPPAD4         | A31    |             |         |  |

| N/A  | GNDA4           | C31    |             |         |  |

| N/A  | RXPPAD4         | A30    |             |         |  |

| N/A  | RXNPAD4         | A29    |             |         |  |

| N/A  | VTRXPAD4        | B30    |             |         |  |

| N/A  | AVCCAUXRX4      | B29    |             |         |  |

| N/A  | AVCCAUXTX5      | B27    |             |         |  |

| N/A  | VTTXPAD5        | B28    |             |         |  |

| N/A  | TXNPAD5         | A28    |             |         |  |

| N/A  | TXPPAD5         | A27    |             |         |  |

| N/A  | GNDA5           | C27    |             |         |  |

| N/A  | RXPPAD5         | A26    |             |         |  |

| N/A  | RXNPAD5         | A25    |             |         |  |

| N/A  | VTRXPAD5        | B26    |             |         |  |

| N/A  | AVCCAUXRX5      | B25    |             |         |  |

|      | Pin Description       |                            |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

| Bank | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 0    | IO_L34N_0             |                            | E30        |                      |          |

| 0    | IO_L34P_0             |                            | F30        |                      |          |

| 0    | IO_L35N_0             |                            | D30        |                      |          |

| 0    | IO_L35P_0             |                            | C30        |                      |          |

| 0    | IO_L36N_0             |                            | M28        |                      |          |

| 0    | IO_L36P_0/VREF_0      |                            | M29        |                      |          |

| 0    | IO_L78N_0             |                            | K29        | NC                   |          |

| 0    | IO_L78P_0             |                            | L29        | NC                   |          |

| 0    | IO_L83_0/No_Pair      |                            | H29        | NC                   |          |

| 0    | IO_L84N_0             |                            | F29        | NC                   |          |

| 0    | IO_L84P_0             |                            | G29        | NC                   |          |

| 0    | IO_L85N_0             |                            | D29        | NC                   |          |

| 0    | IO_L85P_0             |                            | E29        | NC                   |          |

| 0    | IO_L86N_0             |                            | L28        | NC                   |          |

| 0    | IO_L86P_0             |                            | K28        | NC                   |          |

| 0    | IO_L87N_0             |                            | H28        | NC                   |          |

| 0    | IO_L87P_0/VREF_0      |                            | J28        | NC                   |          |

| 0    | IO_L37N_0             |                            | E28        |                      |          |

| 0    | IO_L37P_0             |                            | F28        |                      |          |

| 0    | IO_L38N_0             |                            | C29        |                      |          |

| 0    | IO_L38P_0             |                            | C28        |                      |          |

| 0    | IO_L39N_0             |                            | L27        |                      |          |

| 0    | IO_L39P_0             |                            | M27        |                      |          |

| 0    | IO_L43N_0             |                            | J27        |                      |          |

| 0    | IO_L43P_0             |                            | K27        |                      |          |

| 0    | IO_L44N_0             |                            | H27        |                      |          |

| 0    | IO_L44P_0             |                            | G27        |                      |          |

| 0    | IO_L45N_0             |                            | E27        |                      |          |

| 0    | IO_L45P_0/VREF_0      |                            | F27        |                      |          |

| 0    | IO_L46N_0             |                            | M25        |                      |          |

| 0    | IO_L46P_0             |                            | M26        |                      |          |

| 0    | IO_L47N_0             |                            | L26        |                      |          |

| 0    | IO_L47P_0             |                            | K26        |                      |          |

| 0    | IO_L48N_0             |                            | H26        |                      |          |

| 0    | IO_L48P_0             |                            | J26        |                      |          |

| 0    | IO_L49N_0             |                            | F26        |                      |          |

| Bank | Pin Description       |                            |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

|      | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 2    | IO_L02P_2             |                            | D7         |                      |          |

| 2    | IO_L03N_2             |                            | E6         |                      |          |

| 2    | IO_L03P_2             |                            | D6         |                      |          |

| 2    | IO_L04N_2/VREF_2      |                            | G6         |                      |          |

| 2    | IO_L04P_2             |                            | F7         |                      |          |

| 2    | IO_L05N_2             |                            | D3         |                      |          |

| 2    | IO_L05P_2             |                            | E3         |                      |          |

| 2    | IO_L06N_2             |                            | D1         |                      |          |

| 2    | IO_L06P_2             |                            | D2         |                      |          |

| 2    | IO_L73N_2             |                            | E1         |                      |          |

| 2    | IO_L73P_2             |                            | E2         |                      |          |

| 2    | IO_L74N_2             |                            | F4         |                      |          |

| 2    | IO_L74P_2             |                            | F3         |                      |          |

| 2    | IO_L75N_2             |                            | F1         |                      |          |

| 2    | IO_L75P_2             |                            | F2         |                      |          |

| 2    | IO_L76N_2/VREF_2      |                            | G3         |                      |          |

| 2    | IO_L76P_2             |                            | G4         |                      |          |

| 2    | IO_L77N_2             |                            | G2         |                      |          |

| 2    | IO_L77P_2             |                            | G1         |                      |          |

| 2    | IO_L78N_2             |                            | G5         |                      |          |

| 2    | IO_L78P_2             |                            | H6         |                      |          |

| 2    | IO_L79N_2             |                            | H4         |                      |          |

| 2    | IO_L79P_2             |                            | H5         |                      |          |

| 2    | IO_L80N_2             |                            | H3         |                      |          |

| 2    | IO_L80P_2             |                            | H2         |                      |          |

| 2    | IO_L81N_2             |                            | H7         |                      |          |

| 2    | IO_L81P_2             |                            | J8         |                      |          |

| 2    | IO_L82N_2/VREF_2      |                            | J6         |                      |          |

| 2    | IO_L82P_2             |                            | J7         |                      |          |

| 2    | IO_L83N_2             |                            | J5         |                      |          |

| 2    | IO_L83P_2             |                            | J4         |                      |          |

| 2    | IO_L84N_2             |                            | J1         |                      |          |

| 2    | IO_L84P_2             |                            | J2         |                      |          |

| 2    | IO_L07N_2             |                            | K9         |                      |          |

| 2    | IO_L07P_2             |                            | L10        |                      |          |

| 2    | IO_L08N_2             |                            | K6         |                      |          |

| Bank | Pin Description       |                            |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

|      | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 4    | IO_L60P_4             |                            | AR19       |                      |          |

| 4    | IO_L64N_4             |                            | AV19       |                      |          |

| 4    | IO_L64P_4             |                            | AU19       |                      |          |

| 4    | IO_L65N_4             |                            | AW19       |                      |          |

| 4    | IO_L65P_4             |                            | AY19       |                      |          |

| 4    | IO_L66N_4             |                            | AL21       |                      |          |

| 4    | IO_L66P_4/VREF_4      |                            | AL20       |                      |          |

| 4    | IO_L67N_4             |                            | AN20       |                      |          |

| 4    | IO_L67P_4             |                            | AM20       |                      |          |

| 4    | IO_L68N_4             |                            | AP20       |                      |          |

| 4    | IO_L68P_4             |                            | AR20       |                      |          |

| 4    | IO_L69N_4             |                            | AV20       |                      |          |

| 4    | IO_L69P_4/VREF_4      |                            | AU20       |                      |          |

| 4    | IO_L73N_4             |                            | AY20       |                      |          |

| 4    | IO_L73P_4             |                            | AW20       |                      |          |

| 4    | IO_L74N_4/GCLK3S      |                            | AN21       |                      |          |

| 4    | IO_L74P_4/GCLK2P      |                            | AP21       |                      |          |

| 4    | IO_L75N_4/GCLK1S      |                            | AU21       |                      |          |

| 4    | IO_L75P_4/GCLK0P      |                            | AT21       |                      |          |

|      |                       |                            |            |                      |          |

| 5    | IO_L75N_5/GCLK7S      | BREFCLKN                   | AT22       |                      |          |

| 5    | IO_L75P_5/GCLK6P      | BREFCLKP                   | AU22       |                      |          |

| 5    | IO_L74N_5/GCLK5S      |                            | AP22       |                      |          |

| 5    | IO_L74P_5/GCLK4P      |                            | AN22       |                      |          |

| 5    | IO_L73N_5             |                            | AW23       |                      |          |

| 5    | IO_L73P_5             |                            | AY23       |                      |          |

| 5    | IO_L69N_5/VREF_5      |                            | AU23       |                      |          |

| 5    | IO_L69P_5             |                            | AV23       |                      |          |

| 5    | IO_L68N_5             |                            | AR23       |                      |          |

| 5    | IO_L68P_5             |                            | AP23       |                      |          |

| 5    | IO_L67N_5             |                            | AM23       |                      |          |

| 5    | IO_L67P_5             |                            | AN23       |                      |          |

| 5    | IO_L66N_5/VREF_5      |                            | AL23       |                      |          |

| 5    | IO_L66P_5             |                            | AL22       |                      |          |

| 5    | IO_L65N_5             |                            | AY24       |                      |          |

| 5    | IO_L65P_5             |                            | AW24       |                      |          |

| Bank | Pin Description       |                            |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

|      | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| N/A  | VCCINT                |                            | U26        |                      |          |

| N/A  | VCCINT                |                            | U17        |                      |          |

| N/A  | VCCINT                |                            | U16        |                      |          |

| N/A  | VCCINT                |                            | T27        |                      |          |

| N/A  | VCCINT                |                            | T26        |                      |          |

| N/A  | VCCINT                |                            | T25        |                      |          |

| N/A  | VCCINT                |                            | T24        |                      |          |

| N/A  | VCCINT                |                            | T23        |                      |          |

| N/A  | VCCINT                |                            | T22        |                      |          |

| N/A  | VCCINT                |                            | T21        |                      |          |

| N/A  | VCCINT                |                            | T20        |                      |          |

| N/A  | VCCINT                |                            | T19        |                      |          |

| N/A  | VCCINT                |                            | T18        |                      |          |

| N/A  | VCCINT                |                            | T17        |                      |          |

| N/A  | VCCINT                |                            | T16        |                      |          |

| N/A  | VCCINT                |                            | R28        |                      |          |

| N/A  | VCCINT                |                            | R27        |                      |          |

| N/A  | VCCINT                |                            | R26        |                      |          |

| N/A  | VCCINT                |                            | R17        |                      |          |

| N/A  | VCCINT                |                            | R16        |                      |          |

| N/A  | VCCINT                |                            | R15        |                      |          |

| N/A  | VCCINT                |                            | P29        |                      |          |

| N/A  | VCCINT                |                            | P28        |                      |          |

| N/A  | VCCINT                |                            | P27        |                      |          |

| N/A  | VCCINT                |                            | P16        |                      |          |

| N/A  | VCCINT                |                            | P15        |                      |          |

| N/A  | VCCINT                |                            | P14        |                      |          |

| N/A  | VCCINT                |                            | N30        |                      |          |

| N/A  | VCCINT                |                            | N13        |                      |          |

| N/A  | VCCAUX                |                            | AB42       |                      |          |

| N/A  | VCCAUX                |                            | AB41       |                      |          |

| N/A  | VCCAUX                |                            | AB2        |                      |          |

| N/A  | VCCAUX                |                            | AB1        |                      |          |

| N/A  | VCCAUX                |                            | AC42       |                      |          |

| N/A  | VCCAUX                |                            | AC1        |                      |          |

| N/A  | VCCAUX                |                            | AM32       |                      |          |

#### Table 14: FF1696 — XC2VP100

|      |                  |            | No Connects |  |

|------|------------------|------------|-------------|--|

| Bank | Pin Description  | Pin Number | XC2VP100    |  |

| 2    | IO_L69P_2        | F6         |             |  |

| 2    | IO_L70N_2/VREF_2 | G5         |             |  |

| 2    | IO_L70P_2        | F5         |             |  |

| 2    | IO_L71N_2        | P10        |             |  |

| 2    | IO_L71P_2        | P11        |             |  |

| 2    | IO_L72N_2        | G3         |             |  |

| 2    | IO_L72P_2        | G4         |             |  |

| 2    | IO_L07N_2        | G1         |             |  |

| 2    | IO_L07P_2        | G2         |             |  |

| 2    | IO_L08N_2        | N8         |             |  |

| 2    | IO_L08P_2        | P9         |             |  |

| 2    | IO_L09N_2        | H6         |             |  |

| 2    | IO_L09P_2        | H7         |             |  |

| 2    | IO_L10N_2/VREF_2 | H4         |             |  |

| 2    | IO_L10P_2        | H5         |             |  |

| 2    | IO_L11N_2        | R12        |             |  |

| 2    | IO_L11P_2        | T12        |             |  |

| 2    | IO_L12N_2        | H2         |             |  |

| 2    | IO_L12P_2        | H3         |             |  |

| 2    | IO_L13N_2        | J6         |             |  |

| 2    | IO_L13P_2        | J7         |             |  |

| 2    | IO_L14N_2        | R10        |             |  |

| 2    | IO_L14P_2        | R11        |             |  |