Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 5904                                                         |

| Number of Logic Elements/Cells | 53136                                                        |

| Total RAM Bits                 | 4276224                                                      |

| Number of I/O                  | 852                                                          |

| Number of Gates                | -                                                            |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 1517-BBGA, FCBGA                                             |

| Supplier Device Package        | 1517-FCBGA (40x40)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2vp50-6ff1517c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Product Not Recommended For New Designs**

# **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

# Virtex-II Pro Data Sheet

The Virtex-II Pro Data Sheet contains the following modules:

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Introduction and Overview (Module 1)

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description (Module 2)

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics (Module 3)

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Pinout Information (Module 4)

# **Product Not Recommended For New Designs**

### Other RocketlO X Features and Notes

#### Loopback

In order to facilitate testing without having the need to either apply patterns or measure data at GHz rates, four programmable loop-back features are available.

The first option, serial loopback, is available in two modes: *pre-driver* and *post-driver*.

- The pre-driver mode loops back to the receiver without going through the output driver. In this mode, TXP and TXN are not driven and therefore need not be terminated.

- The post-driver mode is the same as the RocketIO loopback. In this mode, TXP and TXN are driven and must be properly terminated.

The third option, parallel loopback, checks the digital circuitry. When parallel loopback is enabled, the serial loopback path is disabled. However, the transmitter outputs remain active, and data can be transmitted. If TXINHIBIT is asserted, TXP is forced to 0 until TXINHIBIT is de-asserted.

The fourth option, repeater loopback, allows received data to be transmitted without going through the FPGA fabric.

#### Reset

The receiver and transmitter have their own synchronous reset inputs. The transmitter reset, TXRESET, recenters the transmission FIFO and resets all transmitter registers and the encoder. The receiver reset, RXRESET, recenters the

receiver elastic buffer and resets all receiver registers and the decoder. When the signals TXRESET or RXRESET are asserted High, the PCS is in reset. After TXRESET or RXRESET are deasserted, the PCS takes five clocks to come out of reset for each clock domain.

The PMA configuration vector is not affected during this reset, so the PMA speed, filter settings, and so on, all remain the same. Also, the PMA internal pipeline is not affected and continues to operate in normal fashion.

#### Power

The transceiver voltage regulator circuits must not be shared with any other supplies (including FPGA supplies  $V_{CCINT}$ ,  $V_{CCO}$ ,  $V_{CCAUX}$ , and  $V_{REF}$ ). Voltage regulators can be shared among transceiver power supplies of the same voltage, but each supply pin must still have its own separate passive filtering network.

All RocketIO transceivers in the FPGA, whether instantiated in the design or not, must be connected to power and ground. Unused transceivers can be powered by any 1.5V or 2.5V source, and passive filtering is not required.

The Power Down feature is controlled by the transceiver's POWERDOWN input pin. Any given transceiver that is not instantiated in the design is automatically set to the POWERDOWN state by the Xilinx ISE development software. The Power Down pin on the FPGA package has no effect on the MGT.

# **Functional Description: FPGA**

# Input/Output Blocks (IOBs)

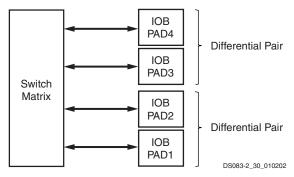

Virtex-II Pro I/O blocks (IOBs) are provided in groups of two or four on the perimeter of each device. Each IOB can be used as input and/or output for single-ended I/Os. Two IOBs can be used as a differential pair. A differential pair is always connected to the same switch matrix, as shown in Figure 18.

IOB blocks are designed for high-performance I/O, supporting 22 single-ended standards, as well as differential signaling with LVDS, LDT, bus LVDS, and LVPECL.

Figure 18: Virtex-II Pro Input/Output Tile

Note: Differential I/Os must use the same clock.

# Supported I/O Standards

Virtex-II Pro IOB blocks feature SelectIO-Ultra inputs and outputs that support a wide variety of I/O signaling standards. In addition to the internal supply voltage ( $V_{CCINT}=1.5V$ ), output driver supply voltage ( $V_{CCO}$ ) is dependent on the I/O standard (see Table 8 and Table 9). An auxiliary supply voltage ( $V_{CCAUX}=2.5V$ ) is required, regardless of the I/O standard used. For exact supply voltage absolute maximum ratings, see Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics.

All of the user IOBs have fixed-clamp diodes to  $V_{\rm CCO}$  and to ground. The IOBs are not compatible or compliant with 5V I/O standards (not 5V-tolerant).

Table 10 lists supported I/O standards with Digitally Controlled Impedance. See Digitally Controlled Impedance (DCI), page 31.

Table 8: Supported Single-Ended I/O Standards

| IOSTANDARD<br>Attribute | Output<br>V <sub>CCO</sub> | Input<br>V <sub>CCO</sub> | Input<br>V <sub>REF</sub> | Board<br>Termination<br>Voltage (V <sub>TT</sub> ) |

|-------------------------|----------------------------|---------------------------|---------------------------|----------------------------------------------------|

| LVTTL <sup>(1)</sup>    | 3.3                        | 3.3                       | N/R                       | N/R                                                |

| LVCMOS33 <sup>(1)</sup> | 3.3                        | 3.3                       | N/R                       | N/R                                                |

| LVCMOS25                | 2.5                        | 2.5                       | N/R                       | N/R                                                |

| LVCMOS18                | 1.8                        | 1.8                       | N/R                       | N/R                                                |

| LVCMOS15                | 1.5                        | 1.5                       | N/R                       | N/R                                                |

| PCl33_3                 | Note (2)                   | Note (2)                  | N/R                       | N/R                                                |

| PCI66_3                 | Note (2)                   | Note (2)                  | N/R                       | N/R                                                |

| PCIX                    | Note (2)                   | Note (2)                  | N/R                       | N/R                                                |

| GTL                     | Note (3)                   | Note (3)                  | 0.8                       | 1.2                                                |

| GTLP                    | Note (3)                   | Note (3)                  | 1.0                       | 1.5                                                |

| HSTL_I                  | 1.5                        | N/R                       | 0.75                      | 0.75                                               |

| HSTL_II                 | 1.5                        | N/R                       | 0.75                      | 0.75                                               |

| HSTL_III                | 1.5                        | N/R                       | 0.9                       | 1.5                                                |

| HSTL_IV                 | 1.5                        | N/R                       | 0.9                       | 1.5                                                |

| HSTL_I_18               | 1.8                        | N/R                       | 0.9                       | 0.9                                                |

| HSTL_II_18              | 1.8                        | N/R                       | 0.9                       | 0.9                                                |

| HSTL_III _18            | 1.8                        | N/R                       | 1.1                       | 1.8                                                |

| HSTL_IV_18              | 1.8                        | N/R                       | 1.1                       | 1.8                                                |

| SSTL2_I                 | 2.5                        | N/R                       | 1.25                      | 1.25                                               |

| SSTL2_II                | 2.5                        | N/R                       | 1.25                      | 1.25                                               |

| SSTL18_I (4)            | 1.8                        | N/R                       | 0.9                       | 0.9                                                |

| SSTL18_II               | 1.8                        | N/R                       | 0.9                       | 0.9                                                |

#### Notes:

- Refer to XAPP659 for more details on interfacing to these 3.3V standards.

- 2. For PCI and PCI-X standards, refer to XAPP653.

- V<sub>CCO</sub> of GTL or GTLP should not be lower than the termination voltage or the voltage seen at the I/O pad. Example: If the pin High level is 1.5V, connect V<sub>CCO</sub> to 1.5V.

- 4. SSTL18\_I is not a JEDEC-supported standard.

- 5. N/R = no requirement.

Table 9: Supported Differential Signal I/O Standards

| I/O Standard                 | Output<br>V <sub>CCO</sub> | Input<br>V <sub>CCO</sub> | Input<br>V <sub>REF</sub> | Output<br>V <sub>OD</sub> |

|------------------------------|----------------------------|---------------------------|---------------------------|---------------------------|

| LDT_25                       | 2.5                        | N/R                       | N/R                       | 0.500 - 0.740             |

| LVDS_25                      | 2.5                        | N/R                       | N/R                       | 0.247 - 0.454             |

| LVDSEXT_25                   | 2.5                        | N/R                       | N/R                       | 0.440 - 0.820             |

| BLVDS_25                     | 2.5                        | N/R                       | N/R                       | 0.250 - 0.450             |

| ULVDS_25                     | 2.5                        | N/R                       | N/R                       | 0.500 - 0.740             |

| LVPECL_25                    | 2.5                        | N/R                       | N/R                       | 0.345 - 1.185             |

| LDT_25_DT <sup>(1)</sup>     | 2.5                        | 2.5                       | N/R                       | 0.500 - 0.740             |

| LVDS_25_DT <sup>(1)</sup>    | 2.5                        | 2.5                       | N/R                       | 0.247 - 0.454             |

| LVDSEXT_25_DT <sup>(1)</sup> | 2.5                        | 2.5                       | N/R                       | 0.330 - 0.700             |

| ULVDS_25_DT <sup>(1)</sup>   | 2.5                        | 2.5                       | N/R                       | 0.500 - 0.740             |

#### Notes:

- 1. These standards support on-chip  $100\Omega$  termination.

- 2. N/R = no requirement.

Table 10: Supported DCI I/O Standards

| I/O Standard                | Output<br>V <sub>CCO</sub> | Input<br>V <sub>CCO</sub> | Input<br>V <sub>REF</sub> | Termination<br>Type |

|-----------------------------|----------------------------|---------------------------|---------------------------|---------------------|

| LVDCI_33 <sup>(1)</sup>     | 3.3                        | 3.3                       | N/R                       | Series              |

| LVDCI_25                    | 2.5                        | 2.5                       | N/R                       | Series              |

| LVDCI_DV2_25                | 2.5                        | 2.5                       | N/R                       | Series              |

| LVDCI_18                    | 1.8                        | 1.8                       | N/R                       | Series              |

| LVDCI_DV2_18                | 1.8                        | 1.8                       | N/R                       | Series              |

| LVDCI_15                    | 1.5                        | 1.5                       | N/R                       | Series              |

| LVDCI_DV2_15                | 1.5                        | 1.5                       | N/R                       | Series              |

| GTL_DCI                     | 1.2                        | 1.2                       | 0.8                       | Single              |

| GTLP_DCI                    | 1.5                        | 1.5                       | 1.0                       | Single              |

| HSTL_I_DCI                  | 1.5                        | 1.5                       | 0.75                      | Split               |

| HSTL_II_DCI                 | 1.5                        | 1.5                       | 0.75                      | Split               |

| HSTL_III_DCI                | 1.5                        | 1.5                       | 0.9                       | Single              |

| HSTL_IV_DCI                 | 1.5                        | 1.5                       | 0.9                       | Single              |

| HSTL_I_DCI_18               | 1.8                        | 1.8                       | 0.9                       | Split               |

| HSTL_II_DCI_18              | 1.8                        | 1.8                       | 0.9                       | Split               |

| HSTL_III_DCI_18             | 1.8                        | 1.8                       | 1.1                       | Single              |

| HSTL_IV_DCI_18              | 1.8                        | 1.8                       | 1.1                       | Single              |

| SSTL2_I_DCI <sup>(2)</sup>  | 2.5                        | 2.5                       | 1.25                      | Split               |

| SSTL2_II_DCI <sup>(2)</sup> | 2.5                        | 2.5                       | 1.25                      | Split               |

| SSTL18_I_DCI (3)            | 1.8                        | 1.8                       | 0.9                       | Split               |

| SSTL18_II_DCI               | 1.8                        | 1.8                       | 0.9                       | Split               |

Table 10: Supported DCI I/O Standards (Continued)

| I/O Standard   | Output<br>V <sub>CCO</sub> | Input<br>V <sub>CCO</sub> | Input<br>V <sub>REF</sub> | Termination<br>Type |

|----------------|----------------------------|---------------------------|---------------------------|---------------------|

| LVDS_25_DCI    | 2.5                        | 2.5                       | N/R                       | Split               |

| LVDSEXT_25_DCI | 2.5                        | 2.5                       | N/R                       | Split               |

#### Notes:

- LVDCI\_XX is LVCMOS output controlled impedance buffers, matching all or half of the reference resistors.

- 2. These are SSTL compatible.

- 3. SSTL18\_I is not a JEDEC-supported standard.

- 4. N/R = no requirement.

# Logic Resources

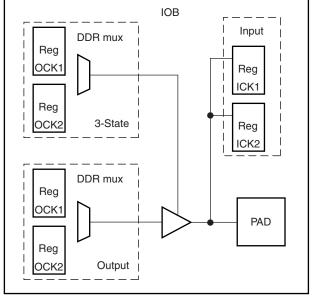

IOB blocks include six storage elements, as shown in Figure 19.

DS031\_29\_100900

Figure 19: Virtex-II Pro IOB Block

Each storage element can be configured either as an edge-triggered D-type flip-flop or as a level-sensitive latch. On the input, output, and 3-state path, one or two DDR registers can be used.

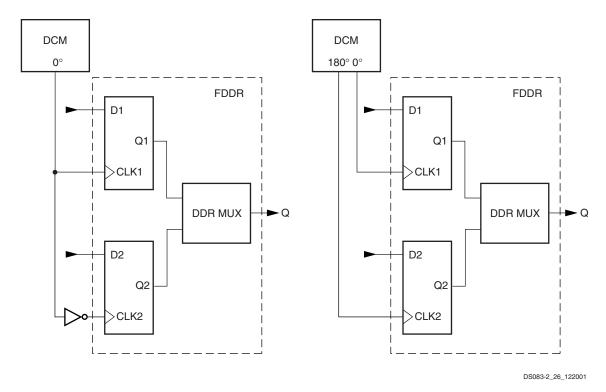

Double data rate is directly accomplished by the two registers on each path, clocked by the rising edges (or falling edges) from two different clock nets. The two clock signals are generated by the DCM and must be 180 degrees out of phase, as shown in Figure 20. There are two input, output, and 3-state data signals, each being alternately clocked out.

Figure 20: Double Data Rate Registers

This DDR mechanism can be used to mirror a copy of the clock on the output. This is useful for propagating a clock along the data that has an identical delay. It is also useful for multiple clock generation, where there is a unique clock driver for every clock load. Virtex-II Pro devices can produce many copies of a clock with very little skew.

Each group of two registers has a clock enable signal (ICE for the input registers, OCE for the output registers, and TCE for the 3-state registers). The clock enable signals are active High by default. If left unconnected, the clock enable for that storage element defaults to the active state.

Each IOB block has common synchronous or asynchronous set and reset (SR and REV signals). Two neighboring IOBs have a shared routing resource connecting the ICLK and OTCLK pins on pairs of IOBs. If two adjacent IOBs using DDR registers do not share the same clock signals on their clock pins (ICLK1, ICLK2, OTCLK1, and OTCLK2), one of the clock signals will be unroutable.

The IOB pairing is identical to the LVDS IOB pairs. Hence, the package pin-out table can also be used for pin assignment to avoid conflict.

SR forces the storage element into the state specified by the SRHIGH or SRLOW attribute. SRHIGH forces a logic 1. SRLOW forces a logic "0". When SR is used, a second input

(REV) forces the storage element into the opposite state. The reset condition predominates over the set condition. The initial state after configuration or global initialization state is defined by a separate INIT0 and INIT1 attribute. By default, the SRLOW attribute forces INIT0, and the SRHIGH attribute forces INIT1.

For each storage element, the SRHIGH, SRLOW, INITO, and INIT1 attributes are independent. Synchronous or asynchronous set / reset is consistent in an IOB block.

All the control signals have independent polarity. Any inverter placed on a control input is automatically absorbed.

Each register or latch, independent of all other registers or latches, can be configured as follows:

- No set or reset

- Synchronous set

- Synchronous reset

- Synchronous set and reset

- Asynchronous set (preset)

- Asynchronous reset (clear)

- · Asynchronous set and reset (preset and clear)

The synchronous reset overrides a set, and an asynchronous clear overrides a preset.

Refer to Figure 21.

# Configurable Logic Blocks (CLBs)

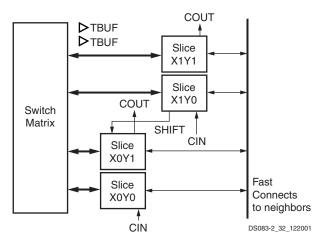

The Virtex-II Pro configurable logic blocks (CLB) are organized in an array and are used to build combinatorial and synchronous logic designs. Each CLB element is tied to a switch matrix to access the general routing matrix, as shown in Figure 32. A CLB element comprises 4 similar slices, with fast local feedback within the CLB. The four slices are split in two columns of two slices with two independent carry logic chains and one common shift chain.

Figure 32: Virtex-II Pro CLB Element

## Slice Description

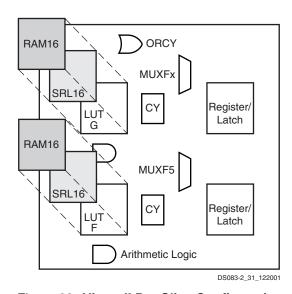

Each slice includes two 4-input function generators, carry logic, arithmetic logic gates, wide function multiplexers and two storage elements. As shown in Figure 33, each 4-input function generator is programmable as a 4-input LUT, 16 bits of distributed SelectRAM+ memory, or a 16-bit variable-tap shift register element.

The output from the function generator in each slice drives both the slice output and the D input of the storage element. Figure 34 shows a more detailed view of a single slice.

Figure 33: Virtex-II Pro Slice Configuration

### **Configurations**

# Look-Up Table

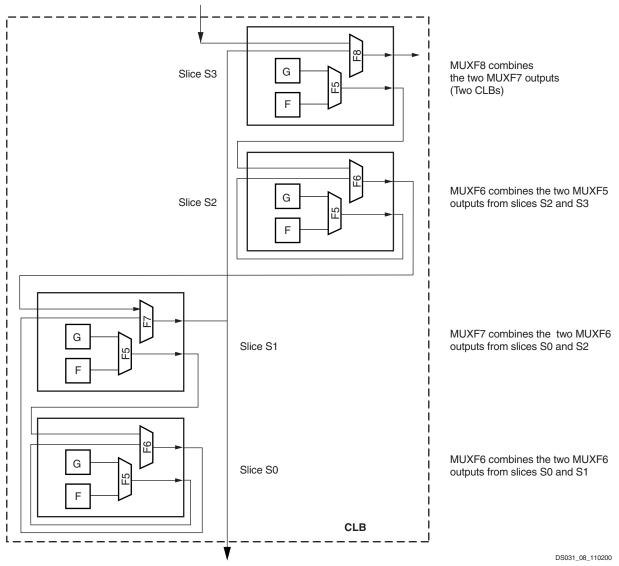

Virtex-II Pro function generators are implemented as 4-input look-up tables (LUTs). Four independent inputs are provided to each of the two function generators in a slice (F and G). These function generators are each capable of implementing any arbitrarily defined boolean function of four inputs. The propagation delay is therefore independent of the function implemented. Signals from the function generators can exit the slice (X or Y output), can input the XOR dedicated gate (see arithmetic logic), or input the carry-logic multiplexer (see fast look-ahead carry logic), or feed the D input of the storage element, or go to the MUXF5 (not shown in Figure 34).

In addition to the basic LUTs, the Virtex-II Pro slice contains logic (MUXF5 and MUXFX multiplexers) that combines function generators to provide any function of five, six, seven, or eight inputs. The MUXFX is either MUXF6, MUXF7, or MUXF8 according to the slice considered in the CLB. Selected functions up to nine inputs (MUXF5 multiplexer) can be implemented in one slice. The MUXFX can also be a MUXF6, MUXF7, or MUXF8 multiplexer to map any function of six, seven, or eight inputs and selected wide logic functions.

## Register/Latch

The storage elements in a Virtex-II Pro slice can be configured either as edge-triggered D-type flip-flops or as level-sensitive latches. The D input can be directly driven by the X or Y output via the DX or DY input, or by the slice inputs bypassing the function generators via the BX or BY input. The clock enable signal (CE) is active High by default. If left unconnected, the clock enable for that storage element defaults to the active state.

In addition to clock (CK) and clock enable (CE) signals, each slice has set and reset signals (SR and BY slice inputs). SR forces the storage element into the state specified by the attribute SRHIGH or SRLOW. SRHIGH forces a logic 1 when SR is asserted. SRLOW forces a logic 0. When SR is used, an optional second input (BY) forces the storage element into the opposite state via the REV pin. The reset condition is predominant over the set condition. (See Figure 35.)

The initial state after configuration or global initial state is defined by a separate INITO and INIT1 attribute. By default, setting the SRLOW attribute sets INIT0, and setting the SRHIGH attribute sets INIT1. For each slice, set and reset can be set to be synchronous or asynchronous. Virtex-II Pro devices also have the ability to set INIT0 and INIT1 independent of SRHIGH and SRLOW.

The control signals clock (CLK), clock enable (CE) and set/reset (SR) are common to both storage elements in one slice. All of the control signals have independent polarity. Any inverter placed on a control input is automatically absorbed.

Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description

#### **Multiplexers**

Virtex-II Pro function generators and associated multiplexers can implement the following:

- 4:1 multiplexer in one slice

- 8:1 multiplexer in two slices

- 16:1 multiplexer in one CLB element (4 slices)

- 32:1 multiplexer in two CLB elements (8 slices)

Each Virtex-II Pro slice has one MUXF5 multiplexer and one MUXFX multiplexer. The MUXFX multiplexer implements the MUXF6, MUXF7, or MUXF8, as shown in Figure 41. Each CLB element has two MUXF6 multiplexers, one MUXF7 multiplexer and one MUXF8 multiplexer. Examples of multiplexers are shown in the *Virtex-II Pro Platform FPGA User Guide*. Any LUT can implement a 2:1 multiplexer.

Figure 41: MUXF5 and MUXFX multiplexers

# **Fast Lookahead Carry Logic**

Dedicated carry logic provides fast arithmetic addition and subtraction. The Virtex-II Pro CLB has two separate carry chains, as shown in the Figure 42.

The height of the carry chains is two bits per slice. The carry chain in the Virtex-II Pro device is running upward. The dedicated carry path and carry multiplexer (MUXCY) can also

be used to cascade function generators for implementing wide logic functions.

#### **Arithmetic Logic**

The arithmetic logic includes an XOR gate that allows a 2-bit full adder to be implemented within a slice. In addition, a dedicated AND (MULT\_AND) gate (shown in Figure 34) improves the efficiency of multiplier implementation.

Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description

# 18-Bit x 18-Bit Multipliers

#### Introduction

A Virtex-II Pro multiplier block is an 18-bit by 18-bit 2's complement signed multiplier. Virtex-II Pro devices incorporate many embedded multiplier blocks. These multipliers can be associated with an 18 Kb block SelectRAM+ resource or can be used independently. They are optimized for high-speed operations and have a lower power consumption compared to an 18-bit x 18-bit multiplier in slices.

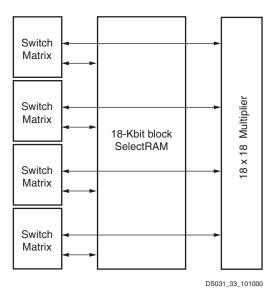

Each SelectRAM+ memory and multiplier block is tied to four switch matrices, as shown in Figure 53.

Figure 53: SelectRAM+ and Multiplier Blocks

#### Association With Block SelectRAM+ Memory

The interconnect is designed to allow SelectRAM+ memory and multiplier blocks to be used at the same time, but some interconnect is shared between the SelectRAM+ and the multiplier. Thus, SelectRAM+ memory can be used only up to 18 bits wide when the multiplier is used, because the multiplier shares inputs with the upper data bits of the SelectRAM+ memory.

This sharing of the interconnect is optimized for an 18-bit-wide block SelectRAM+ resource feeding the multiplier. The use of SelectRAM+ memory and the multiplier with an accumulator in LUTs allows for implementation of a digital signal processor (DSP) multiplier-accumulator (MAC) function, which is commonly used in finite and infinite impulse response (FIR and IIR) digital filters.

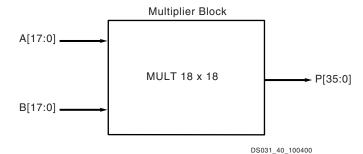

### Configuration

The multiplier block is an 18-bit by 18-bit signed multiplier (2's complement). Both A and B are 18-bit-wide inputs, and the output is 36 bits. Figure 54 shows a multiplier block.

Figure 54: Multiplier Block

## Locations / Organization

Multiplier organization is identical to the 18 Kb SelectRAM+ organization, because each multiplier is associated with an 18 Kb block SelectRAM+ resource.

Table 26: Multiplier Resources

| Device   | Columns | Total Multipliers |

|----------|---------|-------------------|

| XC2VP2   | 4       | 12                |

| XC2VP4   | 4       | 28                |

| XC2VP7   | 6       | 44                |

| XC2VP20  | 8       | 88                |

| XC2VP30  | 8       | 136               |

| XC2VPX20 | 8       | 88                |

| XC2VP40  | 10      | 192               |

| XC2VP50  | 12      | 232               |

| XC2VP70  | 14      | 328               |

| XC2VPX70 | 14      | 308               |

| XC2VP100 | 16      | 444               |

In addition to the built-in multiplier blocks, the CLB elements have dedicated logic to implement efficient multipliers in logic. (Refer to Configurable Logic Blocks (CLBs), page 35).

# **Global Clock Multiplexer Buffers**

Virtex-II Pro devices have 16 clock input pins that can also be used as regular user I/Os. Eight clock pads center on both the top edge and the bottom edge of the device, as illustrated in Figure 55.

The global clock multiplexer buffer represents the input to dedicated low-skew clock tree distribution in Virtex-II Pro devices. Like the clock pads, eight global clock multiplexer buffers are on the top edge of the device and eight are on the bottom edge.

Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics

# **SelectiO-Ultra DC Input and Output Levels**

Values for  $V_{IL}$  and  $V_{IH}$  are recommended input voltages. Values for  $I_{OL}$  and  $I_{OH}$  are guaranteed over the recommended operating conditions at the  $V_{OL}$  and  $V_{OH}$  test points. Only selected standards are tested. These are cho-

sen to ensure that all standards meet their specifications. The selected standards are tested at minimum  $V_{CCO}$  with the respective  $V_{OL}$  and  $V_{OH}$  voltage levels shown. Other standards are sample tested.

Table 6: DC Input and Output Levels

| IOSTANDARD |        | V <sub>IL</sub>          | VI                       | Н                      | V <sub>OL</sub>        | V <sub>OH</sub>         | I <sub>OL</sub>   | I <sub>OH</sub>    |

|------------|--------|--------------------------|--------------------------|------------------------|------------------------|-------------------------|-------------------|--------------------|

| Attribute  | V, min | V, max                   | V, min                   | V, max                 | V, max                 | V, min                  | mA                | mA                 |

| LVTTL      | -0.2   | 0.8                      | 2.0                      | 3.45                   | 0.4                    | 2.4                     | 24                | -24                |

| LVCMOS33   | -0.2   | 0.8                      | 2.0                      | 3.45                   | 0.4                    | V <sub>CCO</sub> - 0.4  | 24                | -24                |

| LVCMOS25   | -0.2   | 0.7                      | 1.7                      | V <sub>CCO</sub> + 0.4 | 0.4                    | V <sub>CCO</sub> - 0.4  | 24                | -24                |

| LVCMOS18   | -0.2   | 30% V <sub>CCO</sub>     | 70% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.4 | 0.4                    | V <sub>CCO</sub> - 0.45 | 16                | -16                |

| LVCMOS15   | -0.2   | 30% V <sub>CCO</sub>     | 70% V <sub>CCO</sub>     | V <sub>CCO</sub> + 0.4 | 0.4                    | V <sub>CCO</sub> - 0.45 | 16                | -16                |

| PCl33_3    | -0.2   | 30% V <sub>CCO</sub>     | 50% V <sub>CCO</sub>     | 3.6                    | 10% V <sub>CCO</sub>   | 90% V <sub>CCO</sub>    |                   |                    |

| PCI66_3    | -0.2   | 30% V <sub>CCO</sub>     | 50% V <sub>CCO</sub>     | 3.6                    | 10% V <sub>CCO</sub>   | 90% V <sub>CCO</sub>    |                   |                    |

| PCIX       | -0.2   | Note (1)                 | Note (1)                 | Note (1)               | Note (1)               | Note (1)                | Note (1)          | Note (1)           |

| GTLP       | -0.2   | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | V <sub>CCO</sub> + 0.4 | 0.6                    | n/a                     | 36                | n/a                |

| GTL        | -0.2   | V <sub>REF</sub> - 0.05  | V <sub>REF</sub> + 0.05  | V <sub>CCO</sub> + 0.4 | 0.4                    | n/a                     | 40                | n/a                |

| HSTL_I     | -0.2   | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | V <sub>CCO</sub> + 0.4 | 0.4 <sup>(2)</sup>     | V <sub>CCO</sub> - 0.4  | 8(2)              | -8(2)              |

| HSTL_II    | -0.2   | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | V <sub>CCO</sub> + 0.4 | 0.4(2)                 | V <sub>CCO</sub> - 0.4  | 16 <sup>(2)</sup> | -16 <sup>(2)</sup> |

| HSTL_III   | -0.2   | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | V <sub>CCO</sub> + 0.4 | 0.4 <sup>(2)</sup>     | V <sub>CCO</sub> - 0.4  | 24 <sup>(2)</sup> | -8(2)              |

| HSTL_IV    | -0.2   | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   | V <sub>CCO</sub> + 0.4 | 0.4 <sup>(2)</sup>     | V <sub>CCO</sub> - 0.4  | 48 <sup>(2)</sup> | -8(2)              |

| SSTL2_I    | -0.2   | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | V <sub>CCO</sub> + 0.3 | V <sub>TT</sub> – 0.61 | V <sub>TT</sub> + 0.61  | 8.1               | -8.1               |

| SSTL2_II   | -0.2   | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | V <sub>CCO</sub> + 0.3 | V <sub>TT</sub> – 0.81 | V <sub>TT</sub> + 0.81  | 16.2              | -16.2              |

| SSTL18_I   | -0.2   | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCO</sub> + 0.3 | V <sub>TT</sub> – 0.61 | V <sub>TT</sub> + 0.61  | 6.7               | -6.7               |

| SSTL18_II  | -0.2   | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCO</sub> + 0.3 | V <sub>TT</sub> – 0.61 | V <sub>TT</sub> + 0.61  | 13.4              | -13.4              |

#### Notes:

- 1. Tested according to relevant specifications.

- 2. This applies to 1.5V and 1.8V HSTL.

# LDT DC Specifications (LDT\_25)

Table 7: LDT DC Specifications

| DC Parameter                         | Symbol             | Conditions                                          | Min  | Тур | Max  | Units |

|--------------------------------------|--------------------|-----------------------------------------------------|------|-----|------|-------|

| Supply Voltage                       | V <sub>CCO</sub>   |                                                     | 2.38 | 2.5 | 2.63 | V     |

| Differential Output Voltage          | V <sub>OD</sub>    | $R_T = 100$ ohm across Q and $\overline{Q}$ signals | 495  | 600 | 715  | mV    |

| Change in V <sub>OD</sub> Magnitude  | Δ V <sub>OD</sub>  |                                                     | -15  |     | 15   | mV    |

| Output Common Mode Voltage           | V <sub>OCM</sub>   | $R_T = 100$ ohm across Q and $\overline{Q}$ signals | 495  | 600 | 715  | mV    |

| Change in V <sub>OS</sub> Magnitude  | Δ V <sub>OCM</sub> |                                                     | -15  |     | 15   | mV    |

| Input Differential Voltage           | V <sub>ID</sub>    |                                                     | 200  | 600 | 1000 | mV    |

| Change in V <sub>ID</sub> Magnitude  | ΔV <sub>ID</sub>   |                                                     | -15  |     | 15   | mV    |

| Input Common Mode Voltage            | V <sub>ICM</sub>   |                                                     | 440  | 600 | 780  | mV    |

| Change in V <sub>ICM</sub> Magnitude | Δ V <sub>ICM</sub> |                                                     | -15  |     | 15   | mV    |

Table 5: FG256/FGG256 — XC2VP2 and XC2VP4

| Bank | Pin Description | Pin Number |

|------|-----------------|------------|

| 7    | VCCO_7          | G6         |

|      |                 |            |

| N/A  | CCLK            | N15        |

| N/A  | PROG_B          | D1         |

| N/A  | DONE            | P16        |

| N/A  | МО              | N3         |

| N/A  | M1              | N2         |

| N/A  | M2              | P1         |

| N/A  | TCK             | D16        |

| N/A  | TDI             | E1         |

| N/A  | TDO             | E16        |

| N/A  | TMS             | C16        |

| N/A  | PWRDWN_B        | N14        |

| N/A  | HSWAP_EN        | C1         |

| N/A  | RSVD            | D14        |

| N/A  | VBATT           | D15        |

| N/A  | DXP             | D2         |

| N/A  | DXN             | D3         |

| N/A  | AVCCAUXTX6      | B5         |

| N/A  | VTTXPAD6        | B4         |

| N/A  | TXNPAD6         | A4         |

| N/A  | TXPPAD6         | A5         |

| N/A  | GNDA6           | C6         |

| N/A  | RXPPAD6         | A6         |

| N/A  | RXNPAD6         | A7         |

| N/A  | VTRXPAD6        | B6         |

| N/A  | AVCCAUXRX6      | В7         |

| N/A  | AVCCAUXTX7      | B11        |

| N/A  | VTTXPAD7        | B10        |

| N/A  | TXNPAD7         | A10        |

| N/A  | TXPPAD7         | A11        |

| N/A  | GNDA7           | C11        |

| N/A  | RXPPAD7         | A12        |

| N/A  | RXNPAD7         | A13        |

| N/A  | VTRXPAD7        | B12        |

# FG676/FGG676 Fine-Pitch BGA Package

As shown in Table 7, XC2VP20, XC2VP30, and XC2VP40 Virtex-II Pro devices are available in the FG676/FGG676 fine-pitch BGA package. The pins in these devices are the same, except for the differences shown in the "No Connects" column. Following this table are the FG676/FGG676 Fine-Pitch BGA Package Specifications (1.00mm pitch).

Table 7: FG676/FGG676 — XC2VP20, XC2VP30, and XC2VP40

|      |                  | No Connects |         |         |         |

|------|------------------|-------------|---------|---------|---------|

| Bank | Pin Description  | Pin Number  | XC2VP20 | XC2VP30 | XC2VP40 |

| 0    | IO_L01N_0/VRP_0  | E5          |         |         |         |

| 0    | IO_L01P_0/VRN_0  | D5          |         |         |         |

| 0    | IO_L02N_0        | E6          |         |         |         |

| 0    | IO_L02P_0        | D6          |         |         |         |

| 0    | IO_L03N_0        | G7          |         |         |         |

| 0    | IO_L03P_0/VREF_0 | F7          |         |         |         |

| 0    | IO_L05_0/No_Pair | E7          |         |         |         |

| 0    | IO_L06N_0        | D7          |         |         |         |

| 0    | IO_L06P_0        | C7          |         |         |         |

| 0    | IO_L07N_0        | H8          |         |         |         |

| 0    | IO_L07P_0        | G8          |         |         |         |

| 0    | IO_L09N_0        | F8          |         |         |         |

| 0    | IO_L09P_0/VREF_0 | E8          |         |         |         |

| 0    | IO_L37N_0        | B8          |         |         |         |

| 0    | IO_L37P_0        | A8          |         |         |         |

| 0    | IO_L39N_0        | H9          |         |         |         |

| 0    | IO_L39P_0        | G9          |         |         |         |

| 0    | IO_L43N_0        | F9          |         |         |         |

| 0    | IO_L43P_0        | E9          |         |         |         |

| 0    | IO_L45N_0        | D9          |         |         |         |

| 0    | IO_L45P_0/VREF_0 | C9          |         |         |         |

| 0    | IO_L46N_0        | H10         |         |         |         |

| 0    | IO_L46P_0        | H11         |         |         |         |

| 0    | IO_L48N_0        | E10         |         |         |         |

| 0    | IO_L48P_0        | E11         |         |         |         |

| 0    | IO_L49N_0        | D10         |         |         |         |

| 0    | IO_L49P_0        | C10         |         |         |         |

| 0    | IO_L50_0/No_Pair | G11         |         |         |         |

| 0    | IO_L53_0/No_Pair | F11         |         |         |         |

| 0    | IO_L54N_0        | J12         |         |         |         |

| 0    | IO_L54P_0        | H12         |         |         |         |

Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                  | Pin    |        | No Connects |        |

|------|------------------|--------|--------|-------------|--------|

| Bank | Pin Description  | Number | XC2VP2 | XC2VP4      | XC2VP7 |

| 2    | IO_L48P_2        | H1     | NC     |             |        |

| 2    | IO_L49N_2        | J7     | NC     |             |        |

| 2    | IO_L49P_2        | J6     | NC     |             |        |

| 2    | IO_L50N_2        | J5     | NC     |             |        |

| 2    | IO_L50P_2        | J4     | NC     |             |        |

| 2    | IO_L51N_2        | J3     | NC     |             |        |

| 2    | IO_L51P_2        | J2     | NC     |             |        |

| 2    | IO_L52N_2/VREF_2 | K6     | NC     |             |        |

| 2    | IO_L52P_2        | K5     | NC     |             |        |

| 2    | IO_L53N_2        | K4     | NC     |             |        |

| 2    | IO_L53P_2        | K3     | NC     |             |        |

| 2    | IO_L54N_2        | J1     | NC     |             |        |

| 2    | IO_L54P_2        | K1     | NC     |             |        |

| 2    | IO_L55N_2        | K7     | NC     |             |        |

| 2    | IO_L55P_2        | L8     | NC     |             |        |

| 2    | IO_L56N_2        | L7     | NC     |             |        |

| 2    | IO_L56P_2        | M7     | NC     |             |        |

| 2    | IO_L57N_2        | L6     | NC     |             |        |

| 2    | IO_L57P_2        | L5     | NC     |             |        |

| 2    | IO_L58N_2/VREF_2 | L4     | NC     |             |        |

| 2    | IO_L58P_2        | L3     | NC     |             |        |

| 2    | IO_L59N_2        | L2     | NC     |             |        |

| 2    | IO_L59P_2        | L1     | NC     |             |        |

| 2    | IO_L60N_2        | M8     | NC     |             |        |

| 2    | IO_L60P_2        | N8     | NC     |             |        |

| 2    | IO_L85N_2        | M6     |        |             |        |

| 2    | IO_L85P_2        | M5     |        |             |        |

| 2    | IO_L86N_2        | M4     |        |             |        |

| 2    | IO_L86P_2        | M3     |        |             |        |

| 2    | IO_L87N_2        | M2     |        |             |        |

| 2    | IO_L87P_2        | M1     |        |             |        |

| 2    | IO_L88N_2/VREF_2 | N7     |        |             |        |

| 2    | IO_L88P_2        | N6     |        |             |        |

| 2    | IO_L89N_2        | N5     |        |             |        |

| 2    | IO_L89P_2        | N4     |        |             |        |

| 2    | IO_L90N_2        | N3     |        |             |        |

| 2    | IO_L90P_2        | N2     |        |             |        |

Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                                    | Pin    |        | No Connects |        |

|------|------------------------------------|--------|--------|-------------|--------|

| Bank | Pin Description                    | Number | XC2VP2 | XC2VP4      | XC2VP7 |

| 3    | IO_L48N_3                          | W1     | NC     |             |        |

| 3    | IO_L48P_3                          | W2     | NC     |             |        |

| 3    | IO_L47N_3                          | W3     | NC     |             |        |

| 3    | IO_L47P_3                          | W4     | NC     |             |        |

| 3    | IO_L46N_3                          | W5     | NC     |             |        |

| 3    | IO_L46P_3                          | W6     | NC     |             |        |

| 3    | IO_L45N_3/VREF_3                   | Y1     | NC     |             |        |

| 3    | IO_L45P_3                          | AA1    | NC     |             |        |

| 3    | IO_L44N_3                          | Y3     | NC     |             |        |

| 3    | IO_L44P_3                          | Y4     | NC     |             |        |

| 3    | IO_L43N_3                          | Y5     | NC     |             |        |

| 3    | IO_L43P_3                          | Y6     | NC     |             |        |

| 3    | IO_L42N_3                          | AA2    | NC     | NC          | NC     |

| 3    | IO_L42P_3                          | AA3    | NC     | NC          | NC     |

| 3    | IO_L41N_3                          | AA4    | NC     | NC          | NC     |

| 3    | IO_L41P_3                          | AA5    | NC     | NC          | NC     |

| 3    | IO_L39N_3/VREF_3                   | AB1    | NC     | NC          | NC     |

| 3    | IO_L39P_3                          | AB2    | NC     | NC          | NC     |

| 3    | IO_L06N_3                          | AB3    |        |             |        |

| 3    | IO_L06P_3                          | AB4    |        |             |        |

| 3    | IO_L05N_3                          | AC1    |        |             |        |

| 3    | IO_L05P_3                          | AC2    |        |             |        |

| 3    | IO_L04N_3                          | AD1    |        |             |        |

| 3    | IO_L04P_3                          | AD2    |        |             |        |

| 3    | IO_L03N_3/VREF_3                   | AE1    |        |             |        |

| 3    | IO_L03P_3                          | AF2    |        |             |        |

| 3    | IO_L02N_3                          | AC3    |        |             |        |

| 3    | IO_L02P_3                          | AD4    |        |             |        |

| 3    | IO_L01N_3/VRP_3                    | AE3    |        |             |        |

| 3    | IO_L01P_3/VRN_3                    | AF3    |        |             |        |

|      |                                    |        |        |             |        |

| 4    | IO_L01N_4/BUSY/DOUT <sup>(1)</sup> | AC6    |        |             |        |

| 4    | IO_L01P_4/INIT_B                   | AD6    |        |             |        |

| 4    | IO_L02N_4/D0/DIN <sup>(1)</sup>    | AB7    |        |             |        |

| 4    | IO_L02P_4/D1                       | AC7    |        |             |        |

| 4    | IO_L03N_4/D2                       | AA7    |        |             |        |

| 4    | IO_L03P_4/D3                       | AA8    |        |             |        |

Table 10: FF1152 — XC2VP20, XC2VP30, XC2VP40, and XC2VP50

|      | Pin Description  | Pin     | No Connects |         |         |         |

|------|------------------|---------|-------------|---------|---------|---------|

| Bank |                  | Number  | XC2VP20     | XC2VP30 | XC2VP40 | XC2VP50 |

| 7    | IO_L86N_7        | U25     |             |         |         |         |

| 7    | IO_L85P_7        | T32     |             |         |         |         |

| 7    | IO_L85N_7        | T31     |             |         |         |         |

| 7    | IO_L60P_7        | T30     |             |         |         |         |

| 7    | IO_L60N_7        | T29     |             |         |         |         |

| 7    | IO_L59P_7        | T28     |             |         |         |         |

| 7    | IO_L59N_7        | T27     |             |         |         |         |

| 7    | IO_L58P_7        | T33     |             |         |         |         |

| 7    | IO_L58N_7/VREF_7 | R33     |             |         |         |         |

| 7    | IO_L57P_7        | R32     |             |         |         |         |

| 7    | IO_L57N_7        | R31     |             |         |         |         |

| 7    | IO_L56P_7        | T26     |             |         |         |         |

| 7    | IO_L56N_7        | T25     |             |         |         |         |

| 7    | IO_L55P_7        | R34     |             |         |         |         |

| 7    | IO_L55N_7        | P34     |             |         |         |         |

| 7    | IO_L54P_7        | R29     |             |         |         |         |

| 7    | IO_L54N_7        | R28     |             |         |         |         |

| 7    | IO_L53P_7        | U24     |             |         |         |         |

| 7    | IO_L53N_7        | T24     |             |         |         |         |

| 7    | IO_L52P_7        | P32     |             |         |         |         |

| 7    | IO_L52N_7/VREF_7 | P31     |             |         |         |         |

| 7    | IO_L51P_7        | P30     |             |         |         |         |

| 7    | IO_L51N_7        | P29     |             |         |         |         |

| 7    | IO_L50P_7        | R26     |             |         |         |         |

| 7    | IO_L50N_7        | R25     |             |         |         |         |

| 7    | IO_L49P_7        | P33     |             |         |         |         |

| 7    | IO_L49N_7        | N33     |             |         |         |         |

| 7    | IO_L48P_7        | N32     |             |         |         |         |

| 7    | IO_L48N_7        | N31     |             |         |         |         |

| 7    | IO_L47P_7        | P28     |             |         |         |         |

| 7    | IO_L47N_7        | P27     |             |         |         |         |

| 7    | IO_L46P_7        | N34     |             |         |         |         |

| 7    | IO_L46N_7/VREF_7 | M34     |             |         |         |         |

| 7    | <br>IO_L45P_7    | N30     |             |         |         |         |

| 7    | IO_L45N_7        | N29     |             |         |         |         |

| 7    | <br>IO_L44P_7    | P26     |             |         |         |         |

| 7    | IO_L44N_7        | P25     |             |         |         |         |

| 7    | IO_L43P_7        | M32     |             |         |         |         |

|      | *_= :*: _'       | <b></b> | i           |         | i       |         |

Table 11: FF1148 — XC2VP40 and XC2VP50

|      | Pin Description  |            | No Connects |         |  |

|------|------------------|------------|-------------|---------|--|

| Bank |                  | Pin Number | XC2VP40     | XC2VP50 |  |

| 2    | IO_L02P_2        | D9         |             |         |  |

| 2    | IO_L03N_2        | B7         |             |         |  |

| 2    | IO_L03P_2        | A7         |             |         |  |

| 2    | IO_L04N_2/VREF_2 | B6         |             |         |  |

| 2    | IO_L04P_2        | A6         |             |         |  |

| 2    | IO_L05N_2        | E8         |             |         |  |

| 2    | IO_L05P_2        | D8         |             |         |  |

| 2    | IO_L06N_2        | B4         |             |         |  |

| 2    | IO_L06P_2        | A4         |             |         |  |

| 2    | IO_L07N_2        | B3         |             |         |  |

| 2    | IO_L07P_2        | A3         |             |         |  |

| 2    | IO_L08N_2        | H7         |             |         |  |

| 2    | IO_L08P_2        | H8         |             |         |  |

| 2    | IO_L09N_2        | C6         |             |         |  |

| 2    | IO_L09P_2        | C7         |             |         |  |

| 2    | IO_L10N_2/VREF_2 | C5         |             |         |  |

| 2    | IO_L10P_2        | B5         |             |         |  |

| 2    | IO_L11N_2        | K8         |             |         |  |

| 2    | IO_L11P_2        | J8         |             |         |  |

| 2    | IO_L12N_2        | C1         |             |         |  |

| 2    | IO_L12P_2        | C2         |             |         |  |

| 2    | IO_L13N_2        | E7         |             |         |  |

| 2    | IO_L13P_2        | D7         |             |         |  |

| 2    | IO_L14N_2        | J6         |             |         |  |

| 2    | IO_L14P_2        | J7         |             |         |  |

| 2    | IO_L15N_2        | D5         |             |         |  |

| 2    | IO_L15P_2        | D6         |             |         |  |

| 2    | IO_L16N_2/VREF_2 | E4         |             |         |  |

| 2    | IO_L16P_2        | D4         |             |         |  |

| 2    | IO_L17N_2        | L9         |             |         |  |

| 2    | IO_L17P_2        | K9         |             |         |  |

| 2    | IO_L18N_2        | E3         |             |         |  |

| 2    | IO_L18P_2        | D3         |             |         |  |

| 2    | <br>IO_L19N_2    | D1         |             |         |  |

| 2    | IO_L19P_2        | D2         |             |         |  |

| 2    | IO_L20N_2        | K7         |             |         |  |

| 2    | IO_L20P_2        | L7         |             |         |  |

| 2    | IO_L21N_2        | F6         |             |         |  |

Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                  | Pin    | No Connects |         |  |

|------|------------------|--------|-------------|---------|--|

| Bank | Pin Description  | Number | XC2VP50     | XC2VP70 |  |

| 2    | IO_L49N_2        | U5     |             |         |  |

| 2    | IO_L49P_2        | U6     |             |         |  |

| 2    | IO_L50N_2        | U13    |             |         |  |

| 2    | IO_L50P_2        | V13    |             |         |  |

| 2    | IO_L51N_2        | U4     |             |         |  |

| 2    | IO_L51P_2        | T4     |             |         |  |

| 2    | IO_L52N_2/VREF_2 | U1     |             |         |  |

| 2    | IO_L52P_2        | U2     |             |         |  |

| 2    | IO_L53N_2        | V9     |             |         |  |

| 2    | IO_L53P_2        | V10    |             |         |  |

| 2    | IO_L54N_2        | V7     |             |         |  |

| 2    | IO_L54P_2        | V8     |             |         |  |

| 2    | IO_L55N_2        | V5     |             |         |  |

| 2    | IO_L55P_2        | V6     |             |         |  |

| 2    | IO_L56N_2        | V11    |             |         |  |

| 2    | IO_L56P_2        | V12    |             |         |  |

| 2    | IO_L57N_2        | V3     |             |         |  |

| 2    | IO_L57P_2        | V4     |             |         |  |

| 2    | IO_L58N_2/VREF_2 | V1     |             |         |  |

| 2    | IO_L58P_2        | V2     |             |         |  |

| 2    | IO_L59N_2        | W10    |             |         |  |

| 2    | IO_L59P_2        | W11    |             |         |  |

| 2    | IO_L60N_2        | W7     |             |         |  |

| 2    | IO_L60P_2        | W8     |             |         |  |

| 2    | IO_L85N_2        | W5     |             |         |  |

| 2    | IO_L85P_2        | W6     |             |         |  |

| 2    | IO_L86N_2        | W12    |             |         |  |

| 2    | IO_L86P_2        | W13    |             |         |  |

| 2    | IO_L87N_2        | W3     |             |         |  |

| 2    | IO_L87P_2        | W4     |             |         |  |

| 2    | IO_L88N_2/VREF_2 | Y7     |             |         |  |

| 2    | IO_L88P_2        | Y8     |             |         |  |

| 2    | IO_L89N_2        | W9     |             |         |  |

| 2    | IO_L89P_2        | Y9     |             |         |  |

| 2    | IO_L90N_2        | Y3     |             |         |  |

| 2    | IO_L90P_2        | Y4     |             |         |  |

|      |                  |        |             |         |  |

| 3    | IO_L90N_3        | AA7    |             |         |  |

|      |                  |        |             |         |  |

Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                  | Pin    | No Connects |         |  |

|------|------------------|--------|-------------|---------|--|

| Bank | Pin Description  | Number | XC2VP50     | XC2VP70 |  |

| 6    | IO_L15P_6        | AL37   |             |         |  |

| 6    | IO_L15N_6/VREF_6 | AK37   |             |         |  |

| 6    | IO_L16P_6        | AL33   |             |         |  |

| 6    | IO_L16N_6        | AL34   |             |         |  |

| 6    | IO_L17P_6        | AH32   |             |         |  |

| 6    | IO_L17N_6        | AG31   |             |         |  |

| 6    | IO_L18P_6        | AK38   |             |         |  |

| 6    | IO_L18N_6        | AK39   |             |         |  |

| 6    | IO_L19P_6        | AK35   |             |         |  |

| 6    | IO_L19N_6        | AK36   |             |         |  |

| 6    | IO_L20P_6        | AF28   |             |         |  |

| 6    | IO_L20N_6        | AF29   |             |         |  |

| 6    | IO_L21P_6        | AK33   |             |         |  |

| 6    | IO_L21N_6/VREF_6 | AK34   |             |         |  |

| 6    | IO_L22P_6        | AJ38   |             |         |  |

| 6    | IO_L22N_6        | AJ39   |             |         |  |

| 6    | IO_L23P_6        | AG30   |             |         |  |

| 6    | IO_L23N_6        | AF30   |             |         |  |

| 6    | IO_L24P_6        | AJ36   |             |         |  |

| 6    | IO_L24N_6        | AJ37   |             |         |  |

| 6    | IO_L25P_6        | AJ34   |             |         |  |

| 6    | IO_L25N_6        | AJ35   |             |         |  |

| 6    | IO_L26P_6        | AF31   |             |         |  |

| 6    | IO_L26N_6        | AF32   |             |         |  |

| 6    | IO_L27P_6        | AJ32   |             |         |  |

| 6    | IO_L27N_6/VREF_6 | AJ33   |             |         |  |

| 6    | IO_L28P_6        | AH37   |             |         |  |

| 6    | IO_L28N_6        | AH38   |             |         |  |

| 6    | IO_L29P_6        | AE27   |             |         |  |

| 6    | IO_L29N_6        | AD27   |             |         |  |

| 6    | IO_L30P_6        | AH36   |             |         |  |

| 6    | IO_L30N_6        | AG35   |             |         |  |

| 6    | IO_L31P_6        | AH33   |             |         |  |

| 6    | IO_L31N_6        | AH34   |             |         |  |

| 6    | IO_L32P_6        | AE28   |             |         |  |

| 6    | IO_L32N_6        | AE29   |             |         |  |

| 6    | IO_L33P_6        | AG38   |             |         |  |

| 6    | IO_L33N_6/VREF_6 | AG39   |             |         |  |

Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                 | Pin    | No Connects |         |  |

|------|-----------------|--------|-------------|---------|--|

| Bank | Pin Description | Number | XC2VP50     | XC2VP70 |  |

| N/A  | TXNPAD11        | A7     |             |         |  |

| N/A  | TXPPAD11        | A6     |             |         |  |

| N/A  | GNDA11          | C6     |             |         |  |

| N/A  | RXPPAD11        | A5     |             |         |  |

| N/A  | RXNPAD11        | A4     |             |         |  |

| N/A  | VTRXPAD11       | B5     |             |         |  |

| N/A  | AVCCAUXRX11     | B4     |             |         |  |

| N/A  | AVCCAUXRX14     | AV4    |             |         |  |

| N/A  | VTRXPAD14       | AV5    |             |         |  |

| N/A  | RXNPAD14        | AW4    |             |         |  |

| N/A  | RXPPAD14        | AW5    |             |         |  |

| N/A  | GNDA14          | AU6    |             |         |  |

| N/A  | TXPPAD14        | AW6    |             |         |  |

| N/A  | TXNPAD14        | AW7    |             |         |  |

| N/A  | VTTXPAD14       | AV7    |             |         |  |

| N/A  | AVCCAUXTX14     | AV6    |             |         |  |

| N/A  | AVCCAUXRX16     | AV8    |             |         |  |

| N/A  | VTRXPAD16       | AV9    |             |         |  |

| N/A  | RXNPAD16        | AW8    |             |         |  |

| N/A  | RXPPAD16        | AW9    |             |         |  |

| N/A  | GNDA16          | AU9    |             |         |  |

| N/A  | TXPPAD16        | AW10   |             |         |  |

| N/A  | TXNPAD16        | AW11   |             |         |  |

| N/A  | VTTXPAD16       | AV11   |             |         |  |

| N/A  | AVCCAUXTX16     | AV10   |             |         |  |

| N/A  | AVCCAUXRX17     | AV12   |             |         |  |

| N/A  | VTRXPAD17       | AV13   |             |         |  |

| N/A  | RXNPAD17        | AW12   |             |         |  |

| N/A  | RXPPAD17        | AW13   |             |         |  |

| N/A  | GNDA17          | AU13   |             |         |  |

| N/A  | TXPPAD17        | AW14   |             |         |  |

| N/A  | TXNPAD17        | AW15   |             |         |  |

| N/A  | VTTXPAD17       | AV15   |             |         |  |

| N/A  | AVCCAUXTX17     | AV14   |             |         |  |

| N/A  | AVCCAUXRX18     | AV16   |             |         |  |

| N/A  | VTRXPAD18       | AV17   |             |         |  |

| N/A  | RXNPAD18        | AW16   |             |         |  |

| N/A  | RXPPAD18        | AW17   |             |         |  |

Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       |                            | No Connects |                      |          |

|------|-----------------------|----------------------------|-------------|----------------------|----------|

| Bank | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number  | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 1    | IO_L30P_1             |                            | G13         |                      |          |

| 1    | IO_L29N_1             |                            | K13         |                      |          |

| 1    | IO_L29P_1             |                            | J13         |                      |          |

| 1    | IO_L28N_1             |                            | M13         |                      |          |

| 1    | IO_L28P_1             |                            | L13         |                      |          |

| 1    | IO_L27N_1/VREF_1      |                            | E12         |                      |          |

| 1    | IO_L27P_1             |                            | D12         |                      |          |

| 1    | IO_L26N_1             |                            | F12         |                      |          |

| 1    | IO_L26P_1             |                            | G12         |                      |          |

| 1    | IO_L25N_1             |                            | J12         |                      |          |

| 1    | IO_L25P_1             |                            | H12         |                      |          |

| 1    | IO_L21N_1             |                            | L12         |                      |          |

| 1    | IO_L21P_1             |                            | K12         |                      |          |

| 1    | IO_L20N_1             |                            | C11         |                      |          |

| 1    | IO_L20P_1             |                            | C10         |                      |          |

| 1    | IO_L19N_1             |                            | F11         |                      |          |

| 1    | IO_L19P_1             |                            | E11         |                      |          |

| 1    | IO_L09N_1/VREF_1      |                            | J11         |                      |          |

| 1    | IO_L09P_1             |                            | H11         |                      |          |

| 1    | IO_L08N_1             |                            | D10         |                      |          |

| 1    | IO_L08P_1             |                            | E10         |                      |          |

| 1    | IO_L07N_1             |                            | G10         |                      |          |

| 1    | IO_L07P_1             |                            | F10         |                      |          |

| 1    | IO_L06N_1             |                            | J10         |                      |          |

| 1    | IO_L06P_1             |                            | H10         |                      |          |

| 1    | IO_L05_1/No_Pair      |                            | K11         |                      |          |

| 1    | IO_L03N_1/VREF_1      |                            | D9          |                      |          |

| 1    | IO_L03P_1             |                            | C9          |                      |          |

| 1    | IO_L02N_1             |                            | E9          |                      |          |

| 1    | IO_L02P_1             |                            | F9          |                      |          |

| 1    | IO_L01N_1/VRP_1       |                            | H9          |                      |          |

| 1    | IO_L01P_1/VRN_1       |                            | G9          |                      |          |

|      |                       |                            |             |                      |          |

| 2    | IO_L01N_2/VRP_2       |                            | C5          |                      |          |

| 2    | IO_L01P_2/VRN_2       |                            | C6          |                      |          |

| 2    | IO_L02N_2             |                            | E7          |                      |          |

Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       |                         |            | No Connects          |          |

|------|-----------------------|-------------------------|------------|----------------------|----------|

| Bank | Virtex-II Pro Devices | XC2VPX70 (if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| N/A  | GND                   |                         | AU25       |                      |          |

| N/A  | GND                   |                         | AU18       |                      |          |

| N/A  | GND                   |                         | AU6        |                      |          |

| N/A  | GND                   |                         | AV38       |                      |          |

| N/A  | GND                   |                         | AV22       |                      |          |

| N/A  | GND                   |                         | AV21       |                      |          |

| N/A  | GND                   |                         | AV5        |                      |          |

| N/A  | GND                   |                         | AW39       |                      |          |

| N/A  | GND                   |                         | AW32       |                      |          |

| N/A  | GND                   |                         | AW28       |                      |          |

| N/A  | GND                   |                         | AW15       |                      |          |

| N/A  | GND                   |                         | AW11       |                      |          |

| N/A  | GND                   |                         | AW4        |                      |          |

| N/A  | GND                   |                         | AY42       |                      |          |

| N/A  | GND                   |                         | AY41       |                      |          |

| N/A  | GND                   |                         | AY40       |                      |          |

| N/A  | GND                   |                         | AY3        |                      |          |

| N/A  | GND                   |                         | AY2        |                      |          |

| N/A  | GND                   |                         | AY1        |                      |          |

| N/A  | GND                   |                         | BA42       |                      |          |

| N/A  | GND                   |                         | BA1        |                      |          |

| N/A  | GND                   |                         | AA38       |                      |          |

| N/A  | GND                   |                         | AA35       |                      |          |

| N/A  | GND                   |                         | AA32       |                      |          |

| N/A  | GND                   |                         | AA26       |                      |          |

| N/A  | GND                   |                         | AA25       |                      |          |

| N/A  | GND                   |                         | AA24       |                      |          |

| N/A  | GND                   |                         | AA23       |                      |          |

| N/A  | GND                   |                         | AA22       |                      |          |

| N/A  | GND                   |                         | AA21       |                      |          |

| N/A  | GND                   |                         | AA20       |                      |          |

| N/A  | GND                   |                         | AA19       |                      |          |

| N/A  | GND                   |                         | AA18       |                      |          |

| N/A  | GND                   |                         | AA17       |                      |          |

| N/A  | GND                   |                         | AA11       |                      |          |

| N/A  | GND                   |                         | AA8        |                      |          |