# E·XFL

### AMD Xilinx - XC2VP70-6FF1517I Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 8272                                                         |

| Number of Logic Elements/Cells | 74448                                                        |

| Total RAM Bits                 | 6045696                                                      |

| Number of I/O                  | 964                                                          |

| Number of Gates                | •                                                            |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                           |

| Package / Case                 | 1517-BBGA, FCBGA                                             |

| Supplier Device Package        | 1517-FCBGA (40x40)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc2vp70-6ff1517i |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#

### Product Not Recommended For New Designs Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Introduction and Overview

- Programmable Receiver Equalization

- Internal AC Coupling

- On-Chip 50Ω Termination

- Eliminates the need for external termination resistors

- Pre- and Post-Driver Serial and Parallel TX-to-RX

# RocketIO Transceiver Features (All Except XC2VPX20 and XC2VPX70)

- Full-Duplex Serial Transceiver (SERDES) Capable of Baud Rates from 600 Mb/s to 3.125 Gb/s

- 100 Gb/s Duplex Data Rate (20 Channels)

- Monolithic Clock Synthesis and Clock Recovery (CDR)

- Fibre Channel, 10G Fibre Channel, Gigabit Ethernet, 10 Gb Attachment Unit Interface (XAUI), and Infiniband-Compliant Transceivers

- 8-, 16-, or 32-bit Selectable Internal FPGA Interface

- 8B/10B Encoder and Decoder (optional)

- PowerPC RISC Processor Block Features (All Except XC2VP2)

- Embedded 300+ MHz Harvard Architecture Block

- Low Power Consumption: 0.9 mW/MHz

- Five-Stage Data Path Pipeline

- Hardware Multiply/Divide Unit

- Thirty-Two 32-bit General Purpose Registers

- 16 KB Two-Way Set-Associative Instruction Cache

- 16 KB Two-Way Set-Associative Data Cache

# Virtex-II Pro Platform FPGA Technology (All Devices)

- SelectRAM+ Memory Hierarchy

- Up to 8 Mb of True Dual-Port RAM in 18 Kb block SelectRAM+ resources

- Up to 1,378 Kb of distributed SelectRAM+ resources

- High-performance interfaces to external memory

- Arithmetic Functions

- Dedicated 18-bit x 18-bit multiplier blocks

- Fast look-ahead carry logic chains

- Flexible Logic Resources

- Up to 88,192 internal registers/latches with Clock Enable

- Up to 88,192 look-up tables (LUTs) or cascadable variable (1 to 16 bits) shift registers

- Wide multiplexers and wide-input function support

- Horizontal cascade chain and Sum-of-Products support

- Internal 3-state busing

- High-Performance Clock Management Circuitry

- Up to twelve Digital Clock Manager (DCM) modules

- Precise clock de-skew

- Internal Loopback Modes for Testing Operability

- Programmable Comma Detection

- Allows for any protocol

- Allows for detection of any 10-bit character

- 8B/10B and 64B/66B Encoding Blocks

- $50\Omega/75\Omega$  on-chip Selectable Transmit and Receive Terminations

- Programmable Comma Detection

- Channel Bonding Support (from 2 to 20 Channels)

- Rate Matching via Insertion/Deletion Characters

- Four Levels of Selectable Pre-Emphasis

- Five Levels of Output Differential Voltage

- Per-Channel Internal Loopback Modes

- 2.5V Transceiver Supply Voltage

- Memory Management Unit (MMU)

- 64-entry unified Translation Look-aside Buffers (TLB)

- Variable page sizes (1 KB to 16 MB)

- Dedicated On-Chip Memory (OCM) Interface

- Supports IBM CoreConnect™ Bus Architecture

- Debug and Trace Support

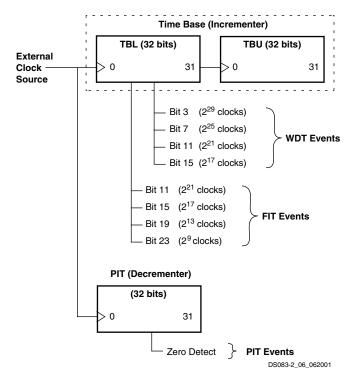

- Timer Facilities

- · Flexible frequency synthesis

- High-resolution phase shifting

- 16 global clock multiplexer buffers in all parts

- Active Interconnect Technology

- Fourth-generation segmented routing structure

- Fast, predictable routing delay, independent of fanout

- Deep sub-micron noise immunity benefits

- SelectIO™-Ultra Technology

- Up to 1,164 user I/Os

- Twenty-two single-ended standards and ten differential standards

- Programmable LVCMOS sink/source current (2 mA to 24 mA) per I/O

- XCITE Digitally Controlled Impedance (DCI) I/O

- PCI/PCI-X support <sup>(1)</sup>

- Differential signaling

- 840 Mb/s Low-Voltage Differential Signaling I/O

(LVDS) with current mode drivers

- On-chip differential termination

- Bus LVDS I/O

.

implemented. In system mode, a Virtex-II Pro device will continue to function while executing non-test Boundary-Scan instructions. In test mode, Boundary-Scan test instructions control the I/O pins for testing purposes. The Virtex-II Pro Test Access Port (TAP) supports BYPASS, PRELOAD, SAMPLE, IDCODE, and USERCODE non-test instructions. The EXTEST, INTEST, and HIGHZ test instructions are also supported.

### Configuration

Virtex-II Pro / Virtex-II Pro devices are configured by loading the bitstream into internal configuration memory using one of the following modes:

- Slave-serial mode

- Master-serial mode

- Slave SelectMAP mode

- Master SelectMAP mode

- Boundary-Scan mode (IEEE 1532)

A Data Encryption Standard (DES) decryptor is available on-chip to secure the bitstreams. One or two triple-DES key sets can be used to optionally encrypt the configuration data.

The Xilinx System Advanced Configuration Environment (System ACE) family offers high-capacity and flexible solution for FPGA configuration as well as program/data storage for the processor. See <u>DS080</u>, *System ACE CompactFlash Solution* for more information.

### Readback and Integrated Logic Analyzer

Configuration data stored in Virtex-II Pro / Virtex-II Pro configuration memory can be read back for verification. Along with the configuration data, the contents of all flip-flops and latches, distributed SelectRAM+, and block SelectRAM+ memory resources can be read back. This capability is useful for real-time debugging. The Xilinx ChipScope Integrated Logic Analyzer (ILA) cores and Integrated Bus Analyzer (IBA) cores, along with the ChipScope Pro Analyzer software, provide a complete solution for accessing and verifying user designs within Virtex-II Pro devices.

# **IP Core and Reference Support**

Intellectual Property is part of the Platform FPGA solution. In addition to the existing FPGA fabric cores, the list below shows some of the currently available hardware and software intellectual properties specially developed for Virtex-II Pro / Virtex-II Pro X by Xilinx. Each IP core is modular, portable, Real-Time Operating System (RTOS) independent, and CoreConnect compatible for ease of design migration. Refer to <u>www.xilinx.com/ipcenter</u> for the latest and most complete list of cores.

### Hardware Cores

- Bus Infrastructure cores (arbiters, bridges, and more)

- Memory cores (DDR, Flash, and more)

- Peripheral cores (UART, IIC, and more)

- Networking cores (ATM, Ethernet, and more)

### **Software Cores**

- Boot code

- Test code

- Device drivers

- Protocol stacks

- RTOS integration

- Customized board support package

# **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

# **Virtex-II Pro Data Sheet**

The Virtex-II Pro Data Sheet contains the following modules:

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Introduction and Overview (Module 1)

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description (Module 2)

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics (Module 3)

- Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Pinout Information (Module 4)

### **Receiver Buffer**

The receiver includes buffers (FIFOs) in the datapath. This section gives the reasons for including the buffers and outlines their operation.

The receiver buffer is required for two reasons:

- *Clock correction* to accommodate the slight difference in frequency between the recovered clock RXRECCLK and the internal FPGA user clock RXUSRCLK

- *Channel bonding* to allow realignment of the input stream to ensure proper alignment of data being read through multiple transceivers

The receiver uses an *elastic buffer*, where "elastic" refers to the ability to modify the read pointer for clock correction and channel bonding.

### **Comma Detection**

Word alignment is dependent on the state of comma detect bits. If comma detect is enabled, the transceiver recognizes up to two 10-bit preprogrammed characters. Upon detection of the character or characters, the comma detect output is driven high and the data is synchronously aligned. If a comma is detected and the data is aligned, no further alignment alteration takes place. If a comma is received and realignment is necessary, the data is realigned and an indication is given at the receiver interface. The realignment indicator is a distinct output.

The transceiver continuously monitors the data for the presence of the 10-bit character(s). Upon each occurrence of a 10-bit character, the data is checked for word alignment. If comma detect is disabled, the data is not aligned to any particular pattern. The programmable option allows a user to align data on comma+, comma-, both, or a unique user-defined and programmed sequence.

### **Clock Correction**

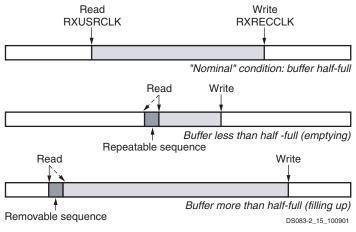

RXRECCLK (the recovered clock) reflects the data rate of the incoming data. RXUSRCLK defines the rate at which the FPGA fabric consumes the data. Ideally, these rates are identical. However, since the clocks typically have different sources, one of the clocks will be faster than the other. The receiver buffer accommodates this difference between the clock rates. See Figure 12.

Nominally, the buffer is always half full. This is shown in the top buffer, Figure 12, where the shaded area represents buffered data not yet read. Received data is inserted via the write pointer under control of RXRECCLK. The FPGA fabric reads data via the read pointer under control of RXUS-RCLK. The half full/half empty condition of the buffer gives a cushion for the differing clock rates. This operation continues indefinitely, regardless of whether or not "meaningful" data is being received. When there is no meaningful data to be received, the incoming data will consist of IDLE characters or other padding.

If RXUSRCLK is faster than RXRECCLK, the buffer becomes more empty over time. The clock correction logic

corrects for this by decrementing the read pointer to reread a repeatable byte sequence. This is shown in the middle buffer, Figure 12, where the solid read pointer decrements to the value represented by the dashed pointer.

Figure 12: Clock Correction in Receiver

By decrementing the read pointer instead of incrementing it in the usual fashion, the buffer is partially refilled. The transceiver design will repeat a single repeatable byte sequence when necessary to refill a buffer. If the byte sequence length is greater than one, and if attribute CLK\_COR\_REPEAT\_WAIT is 0, then the transceiver may repeat the same sequence multiple times until the buffer is refilled to the desired extent.

Similarly, if RXUSRCLK is slower than RXRECCLK, the buffer will fill up over time. The clock correction logic corrects for this by incrementing the read pointer to skip over a removable byte sequence that need not appear in the final FPGA fabric byte stream. This is shown in the bottom buffer, Figure 12, where the solid read pointer increments to the value represented by the dashed pointer. This accelerates the emptying of the buffer, preventing its overflow. The transceiver design will skip a single byte sequence when necessary to partially empty a buffer. If attribute CLK\_COR\_REPEAT\_WAIT is 0, the transceiver may also skip two consecutive removable byte sequences in one step to further empty the buffer when necessary.

These operations require the clock correction logic to recognize a byte sequence that can be freely repeated or omitted in the incoming data stream. This sequence is generally an IDLE sequence, or other sequence comprised of special values that occur in the gaps separating packets of meaningful data. These gaps are required to occur sufficiently often to facilitate the timely execution of clock correction.

### **Channel Bonding**

Some gigabit I/O standards such as Infiniband specify the use of multiple transceivers in parallel for even higher data rates. Words of data are split into bytes, with each byte sent over a separate channel (transceiver). See Figure 13.

Figure 17: Relationship of Timer Facilities to Base Clock

### Interrupts

The PPC405 provides an interface to an interrupt controller that is logically outside the PPC405 core. This controller combines the asynchronous interrupt inputs and presents them to the embedded core as a single interrupt signal. The sources of asynchronous interrupts are external signals, the JTAG/debug unit, and any implemented peripherals.

### **Debug Logic**

All architected resources on the embedded PPC405 core can be accessed through the debug logic. Upon a debug event, the PPC405 core provides debug information to an external debug tool. Three different types of tools are supported depending on the debug mode: ROM monitors, JTAG debuggers, and instruction trace tools.

In internal debug mode, a debug event enables exception-handling software at a dedicated interrupt vector to take

over the CPU core and communicate with a debug tool. The debug tool has read-write access to all registers and can set hardware or software breakpoints. ROM monitors typically use the internal debug mode.

In external debug mode, the CPU core enters stop state (stops instruction execution) when a debug event occurs. This mode offers a debug tool read-write access to all registers in the PPC405 core. Once the CPU core is in stop state, the debug tool can start the CPU core, step an instruction, freeze the timers, or set hardware or software break points. In addition to CPU core control, the debug logic is capable of writing instructions into the instruction cache, eliminating the need for external memory during initial board bring-up. Communication to a debug tool using external debug mode is through the JTAG port.

Debug wait mode offers the same functionality as external debug mode with one exception. In debug wait mode, the CPU core goes into wait state instead of stop state after a debug event. Wait state is identical to stop state until an interrupt occurs. In wait state, the PPC405 core can vector to an exception handler, service an interrupt and return to wait state. This mode is particularly useful when debugging real time control systems.

Real-time trace debug mode is always enabled. The debug logic continuously broadcasts instruction trace information to the trace port. When a debug event occurs, the debug logic signals an external debug tool to save instruction trace information before and after the event. The number of instructions traced depends on the trace tool.

Debug events signal the debug logic to stop the CPU core, put the CPU core in debug wait state, cause a debug exception or save instruction trace information.

# **Big Endian and Little Endian Support**

The embedded PPC405 core supports big endian or little endian byte ordering for instructions stored in external memory. Since the PowerPC architecture is big endian internally, the ICU rearranges the instructions stored as little endian into the big endian format. Therefore, the instruction cache always contains instructions in big endian format so that the byte ordering is correct for the execution unit. This feature allows the 405 core to be used in systems designed to function in a little endian environment.

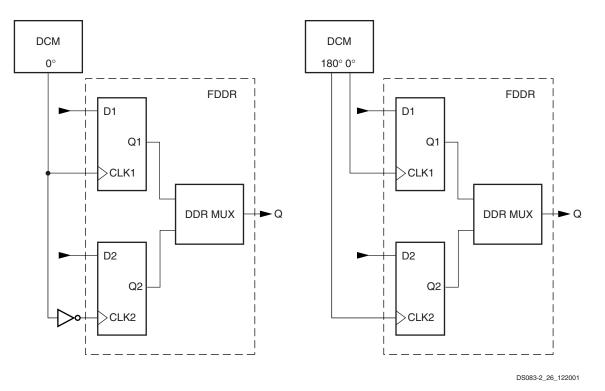

Figure 20: Double Data Rate Registers

This DDR mechanism can be used to mirror a copy of the clock on the output. This is useful for propagating a clock along the data that has an identical delay. It is also useful for multiple clock generation, where there is a unique clock driver for every clock load. Virtex-II Pro devices can produce many copies of a clock with very little skew.

Each group of two registers has a clock enable signal (ICE for the input registers, OCE for the output registers, and TCE for the 3-state registers). The clock enable signals are active High by default. If left unconnected, the clock enable for that storage element defaults to the active state.

Each IOB block has common synchronous or asynchronous set and reset (SR and REV signals). Two neighboring IOBs have a shared routing resource connecting the ICLK and OTCLK pins on pairs of IOBs. If two adjacent IOBs using DDR registers do not share the same clock signals on their clock pins (ICLK1, ICLK2, OTCLK1, and OTCLK2), one of the clock signals will be unroutable.

The IOB pairing is identical to the LVDS IOB pairs. Hence, the package pin-out table can also be used for pin assignment to avoid conflict.

SR forces the storage element into the state specified by the SRHIGH or SRLOW attribute. SRHIGH forces a logic 1. SRLOW forces a logic "0". When SR is used, a second input

(REV) forces the storage element into the opposite state. The reset condition predominates over the set condition. The initial state after configuration or global initialization state is defined by a separate INIT0 and INIT1 attribute. By default, the SRLOW attribute forces INIT0, and the SRHIGH attribute forces INIT1.

For each storage element, the SRHIGH, SRLOW, INITO, and INIT1 attributes are independent. Synchronous or asynchronous set / reset is consistent in an IOB block.

All the control signals have independent polarity. Any inverter placed on a control input is automatically absorbed.

Each register or latch, independent of all other registers or latches, can be configured as follows:

- No set or reset

- Synchronous set

- Synchronous reset

- · Synchronous set and reset

- Asynchronous set (preset)

- Asynchronous reset (clear)

- Asynchronous set and reset (preset and clear)

The synchronous reset overrides a set, and an asynchronous clear overrides a preset.

Refer to Figure 21.

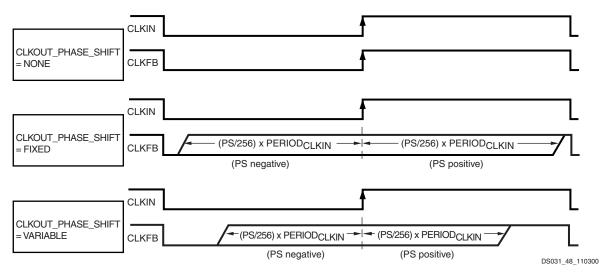

Figure 63: Fine-Phase Shifting Effects

Two separate components of the phase shift range must be understood:

- PHASE\_SHIFT attribute range

- FINE\_SHIFT\_RANGE DCM timing parameter range

The PHASE\_SHIFT attribute is the numerator in the following equation:

Phase Shift (ns) = (PHASE\_SHIFT/256) \* PERIOD<sub>CLKIN</sub>

The full range of this attribute is always -255 to +255, but its practical range varies with CLKIN frequency, as constrained by the FINE\_SHIFT\_RANGE component, which represents the total delay achievable by the phase shift delay line. Total delay is a function of the number of delay taps used in the circuit. Across process, voltage, and temperature, this absolute range is guaranteed to be as specified under **DCM Timing Parameters** in Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics.

Absolute range (fixed mode) = ± FINE\_SHIFT\_RANGE

Absolute range (variable mode) = ± FINE\_SHIFT\_RANGE/2

The reason for the difference between fixed and variable modes is as follows. For variable mode to allow symmetric, dynamic sweeps from -255/256 to +255/256, the DCM sets the "zero phase skew" point as the middle of the delay line, thus dividing the total delay line range in half. In fixed mode,

since the PHASE\_SHIFT value never changes after configuration, the entire delay line is available for insertion into either the CLKIN or CLKFB path (to create either positive or negative skew).

Taking both of these components into consideration, the following are some usage examples:

- If PERIOD<sub>CLKIN</sub> = 2 \* FINE\_SHIFT\_RANGE, then PHASE\_SHIFT in fixed mode is limited to ± 128, and in variable mode it is limited to ± 64.

- If PERIOD<sub>CLKIN</sub> = FINE\_SHIFT\_RANGE, then PHASE\_SHIFT in fixed mode is limited to ± 255, and in variable mode it is limited to ± 128.

- If PERIOD<sub>CLKIN</sub>  $\leq$  0.5 \* FINE\_SHIFT\_RANGE, then PHASE\_SHIFT is limited to  $\pm$  255 in either mode.

### **Operating Modes**

The frequency ranges of DCM input and output clocks depend on the operating mode specified, either low-frequency mode or high-frequency mode, according to Table 30. For actual values, see Virtex-II Pro and Virtex-II Pro X Platform FPGAs: DC and Switching Characteristics. The CLK2X, CLK2X180, CLK90, and CLK270 outputs are not available in high-frequency mode.

High or low-frequency mode is selected by an attribute.

|                 | Low-Frequency Mode |                   | High-Freq         | uency Mode        |

|-----------------|--------------------|-------------------|-------------------|-------------------|

| Output Clock    | CLKIN Input        | CLK Output        | CLKIN Input       | CLK Output        |

| CLK0, CLK180    | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_1X_LF | CLKIN_FREQ_DLL_HF | CLKOUT_FREQ_1X_HF |

| CLK90, CLK270   | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_1X_LF | NA                | NA                |

| CLK2X, CLK2X180 | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_2X_LF | NA                | NA                |

| CLKDV           | CLKIN_FREQ_DLL_LF  | CLKOUT_FREQ_DV_LF | CLKIN_FREQ_DLL_HF | CLKOUT_FREQ_DV_HF |

| CLKFX, CLKFX180 | CLKIN_FREQ_FX_LF   | CLKOUT_FREQ_FX_LF | CLKIN_FREQ_FX_HF  | CLKOUT_FREQ_FX_HF |

#### Table 30: DCM Frequency Ranges

# Routing

### **DCM and MGT Locations/Organization**

Virtex-II Pro DCMs and serial transceivers (MGTs) are placed on the top and bottom of each block RAM and multiplier column in some combination, as shown in Table 31. The number of DCMs and RocketIO transceivers total twice the number of block RAM columns in the device. Refer to Figure 52, page 47 for an illustration of this in the XC2VP4 device.

| Device   | Block RAM<br>Columns | DCMs | MGTs |

|----------|----------------------|------|------|

| XC2VP2   | 4                    | 4    | 4    |

| XC2VP4   | 4                    | 4    | 4    |

| XC2VP7   | 6                    | 4    | 8    |

| XC2VP20  | 8                    | 8    | 8    |

| XC2VPX20 | 8                    | 8    | 8    |

| XC2VP30  | 8                    | 8    | 8    |

| XC2VP40  | 10                   | 8    | 12   |

| XC2VP50  | 12                   | 8    | 16   |

| XC2VP70  | 14                   | 8    | 20   |

| XC2VPX70 | 14                   | 8    | 20   |

| XC2VP100 | 16                   | 12   | 20   |

#### Table 31: DCM and MGT Organization

Place-and-route software takes advantage of this regular array to deliver optimum system performance and fast compile times. The segmented routing resources are essential to guarantee IP cores portability and to efficiently handle an incremental design flow that is based on modular implementations. Total design time is reduced due to fewer and shorter design iterations.

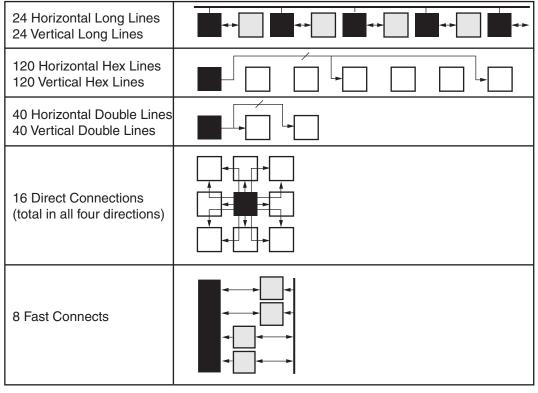

### **Hierarchical Routing Resources**

Most Virtex-II Pro signals are routed using the global routing resources, which are located in horizontal and vertical routing channels between each switch matrix.

As shown in Figure 64, page 54, Virtex-II Pro has fully buffered programmable interconnections, with a number of resources counted between any two adjacent switch matrix rows or columns. Fanout has minimal impact on the performance of each net.

- The long lines are bidirectional wires that distribute signals across the device. Vertical and horizontal long lines span the full height and width of the device.

- The hex lines route signals to every third or sixth block away in all four directions. Organized in a staggered pattern, hex lines can only be driven from one end. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source).

DS031\_60\_110200

Figure 64: Hierarchical Routing Resources

# **Virtex-II Pro Performance Characteristics**

This section provides the performance characteristics of some common functions and designs implemented in Virtex-II Pro devices. The numbers reported here are fully characterized worst-case values. Note that these values are subject to the same guidelines as Virtex-II Pro Switching Characteristics (speed files). Table 13 provides pin-to-pin values (in nanoseconds) including IOB delays; that is, delay through the device from input pin to output pin. In the case of multiple inputs and outputs, the worst delay is reported.

### Table 13: Pin-to-Pin Performance

| Description                       | Device Used & Speed Grade | Pin-to-Pin Performance<br>(with I/O Delays) | Units |

|-----------------------------------|---------------------------|---------------------------------------------|-------|

| Basic Functions:                  |                           |                                             |       |

| 16-bit Address Decoder            | XC2VP20FF1152-6           | 7.20                                        | ns    |

| 32-bit Address Decoder            | XC2VP20FF1152-6           | 8.08                                        | ns    |

| 64-bit Address Decoder            | XC2VP20FF1152-6           | 8.15                                        | ns    |

| 4:1 MUX                           | XC2VP20FF1152-6           | 3.85                                        | ns    |

| 8:1 MUX                           | XC2VP20FF1152-6           | 7.24                                        | ns    |

| 16:1 MUX                          | XC2VP20FF1152-6           | 7.30                                        | ns    |

| 32:1 MUX                          | XC2VP20FF1152-6           | 7.64                                        | ns    |

| Combinatorial (pad to LUT to pad) | XC2VP20FF1152-6           | 3.26                                        | ns    |

| Memory:                           |                           |                                             |       |

| Block RAM                         |                           |                                             |       |

| Pad to setup                      | XC2VP20FF1152-6           | 1.72                                        | ns    |

| Clock to Pad                      | XC2VP20FF1152-6           | 6.63                                        | ns    |

| Distributed RAM                   |                           |                                             |       |

| Pad to setup                      | XC2VP20FF1152-6           | 1.78                                        | ns    |

| Clock to Pad                      | XC2VP20FF1152-6           | 4.12                                        | ns    |

# **Miscellaneous Timing Parameters**

### Table 61: Miscellaneous Timing Parameters

|                                               |                     |                                   | S        | peed Grad | е      |       |

|-----------------------------------------------|---------------------|-----------------------------------|----------|-----------|--------|-------|

| Description                                   | Symbol              | Constraints<br>F <sub>CLKIN</sub> | -7       | -6        | -5     | Units |

| Time Required to Achieve LOCK                 |                     |                                   |          |           |        |       |

| Using DLL outputs <sup>(1)</sup>              | LOCK_DLL:           |                                   |          |           |        |       |

| -                                             | LOCK_DLL_60         | > 60MHz                           | 20.00    | 20.00     | 20.00  | us    |

|                                               | LOCK_DLL_50_60      | 50 - 60 MHz                       | 25.00    | 25.00     | 25.00  | us    |

|                                               | LOCK_DLL_40_50      | 40 - 50 MHz                       | 50.00    | 50.00     | 50.00  | us    |

|                                               | LOCK_DLL_30_40      | 30 - 40 MHz                       | 90.00    | 90.00     | 90.00  | us    |

|                                               | LOCK_DLL_24_30      | 24 - 30 MHz                       | 120.00   | 120.00    | 120.00 | us    |

| Using CLKFX outputs                           | LOCK_FX_MIN         |                                   | 10.00    | 10.00     | 10.00  | ms    |

|                                               | LOCK_FX_MAX         |                                   | 10.00    | 10.00     | 10.00  | ms    |

| Additional lock time with fine phase shifting | LOCK_DLL_FINE_SHIFT |                                   | 50.00    | 50.00     | 50.00  | us    |

| Fine Phase Shifting                           |                     |                                   | ·        |           |        |       |

| Absolute shifting range                       | FINE_SHIFT_RANGE    |                                   | 10.00    | 10.00     | 10.00  | ns    |

| Delay Lines                                   |                     | 1                                 | <u> </u> |           |        |       |

| Tap delay resolution                          | DCM_TAP_MIN         |                                   | 30.00    | 30.00     | 30.00  | ps    |

|                                               | DCM_TAP_MAX         |                                   | 50.00    | 50.00     | 50.00  | ps    |

Notes:

1. "DLL outputs" is used here to describe the outputs: CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV.

# **Frequency Synthesis**

#### Table 62: Frequency Synthesis

| Attribute      | Min | Max |

|----------------|-----|-----|

| CLKFX_MULTIPLY | 2   | 32  |

| CLKFX_DIVIDE   | 1   | 32  |

### Parameter Cross-Reference

### Table 63: Parameter Cross-Reference

| Libraries Guide         | Data Sheet                |

|-------------------------|---------------------------|

| DLL_CLKOUT_{MINIMAX}_LF | CLKOUT_FREQ_{1XI2XIDV}_LF |

| DFS_CLKOUT_{MINIMAX}_LF | CLKOUT_FREQ_FX_LF         |

| DLL_CLKIN_{MINIMAX}_LF  | CLKIN_FREQ_DLL_LF         |

| DFS_CLKIN_{MINIMAX}_LF  | CLKIN_FREQ_FX_LF          |

| DLL_CLKOUT_{MINIMAX}_HF | CLKOUT_FREQ_{1XIDV}_HF    |

| DFS_CLKOUT_{MINIMAX}_HF | CLKOUT_FREQ_FX_HF         |

| DLL_CLKIN_{MINIMAX}_HF  | CLKIN_FREQ_DLL_HF         |

| DFS_CLKIN_{MINIMAX}_HF  | CLKIN_FREQ_FX_HF          |

### Table 7: FG676/FGG676 — XC2VP20, XC2VP30, and XC2VP40

|      |                  |            |         | No Connects | 3       |

|------|------------------|------------|---------|-------------|---------|

| Bank | Pin Description  | Pin Number | XC2VP20 | XC2VP30     | XC2VP40 |

| 5    | IO_L46N_5        | W11        |         |             |         |

| 5    | IO_L46P_5        | W10        |         |             |         |

| 5    | IO_L45N_5/VREF_5 | AD9        |         |             |         |

| 5    | IO_L45P_5        | AC9        |         |             |         |

| 5    | IO_L43N_5        | AB9        |         |             |         |

| 5    | IO_L43P_5        | AA9        |         |             |         |

| 5    | IO_L39N_5        | Y9         |         |             |         |

| 5    | IO_L39P_5        | W9         |         |             |         |

| 5    | IO_L37N_5        | AF8        |         |             |         |

| 5    | IO_L37P_5        | AE8        |         |             |         |

| 5    | IO_L09N_5/VREF_5 | AB8        |         |             |         |

| 5    | IO_L09P_5        | AA8        |         |             |         |

| 5    | IO_L07N_5/VREF_5 | Y8         |         |             |         |

| 5    | IO_L07P_5        | W8         |         |             |         |

| 5    | IO_L06N_5/VRP_5  | AD7        |         |             |         |

| 5    | IO_L06P_5/VRN_5  | AC7        |         |             |         |

| 5    | IO_L05_5/No_Pair | AB7        |         |             |         |

| 5    | IO_L03N_5/D4     | AA7        |         |             |         |

| 5    | IO_L03P_5/D5     | Y7         |         |             |         |

| 5    | IO_L02N_5/D6     | AC6        |         |             |         |

| 5    | IO_L02P_5/D7     | AB6        |         |             |         |

| 5    | IO_L01N_5/RDWR_B | AC5        |         |             |         |

| 5    | IO_L01P_5/CS_B   | AB5        |         |             |         |

|      |                  |            |         |             |         |

| 6    | IO_L01P_6/VRN_6  | AE1        |         |             |         |

| 6    | IO_L01N_6/VRP_6  | AD1        |         |             |         |

| 6    | IO_L02P_6        | AD2        |         |             |         |

| 6    | IO_L02N_6        | AC3        |         |             |         |

| 6    | IO_L03P_6        | AC2        |         |             |         |

| 6    | IO_L03N_6/VREF_6 | AC1        |         |             |         |

| 6    | IO_L05P_6        | AB4        |         |             |         |

| 6    | IO_L05N_6        | AA5        |         |             |         |

| 6    | IO_L06P_6        | AB2        |         |             |         |

| 6    | IO_L06N_6        | AB1        |         |             |         |

| 6    | IO_L23P_6        | AA6        | NC      |             |         |

### Table 7: FG676/FGG676 — XC2VP20, XC2VP30, and XC2VP40

|      |                 |            |         | No Connects |         |  |

|------|-----------------|------------|---------|-------------|---------|--|

| Bank | Pin Description | Pin Number | XC2VP20 | XC2VP30     | XC2VP40 |  |

| N/A  | AVCCAUXRX21     | AE7        |         |             |         |  |

| N/A  | VTRXPAD21       | AE6        |         |             |         |  |

| N/A  | RXNPAD21        | AF7        |         |             |         |  |

| N/A  | RXPPAD21        | AF6        |         |             |         |  |

| N/A  | GNDA21          | AD6        |         |             |         |  |

| N/A  | TXPPAD21        | AF5        |         |             |         |  |

| N/A  | TXNPAD21        | AF4        |         |             |         |  |

| N/A  | VTTXPAD21       | AE4        |         |             |         |  |

| N/A  | AVCCAUXTX21     | AE5        |         |             |         |  |

| N/A  | M2              | AD4        |         |             |         |  |

| N/A  | MO              | AF3        |         |             |         |  |

| N/A  | M1              | AE3        |         |             |         |  |

| N/A  | TDI             | D3         |         |             |         |  |

|      |                 |            |         |             |         |  |

| N/A  | VCCINT          | G10        |         |             |         |  |

| N/A  | VCCINT          | G13        |         |             |         |  |

| N/A  | VCCINT          | G14        |         |             |         |  |

| N/A  | VCCINT          | G17        |         |             |         |  |

| N/A  | VCCINT          | J9         |         |             |         |  |

| N/A  | VCCINT          | J18        |         |             |         |  |

| N/A  | VCCINT          | K7         |         |             |         |  |

| N/A  | VCCINT          | K10        |         |             |         |  |

| N/A  | VCCINT          | K11        |         |             |         |  |

| N/A  | VCCINT          | K16        |         |             |         |  |

| N/A  | VCCINT          | K17        |         |             |         |  |

| N/A  | VCCINT          | K20        |         |             |         |  |

| N/A  | VCCINT          | L10        |         |             |         |  |

| N/A  | VCCINT          | L17        |         |             |         |  |

| N/A  | VCCINT          | N7         |         |             |         |  |

| N/A  | VCCINT          | N20        |         |             |         |  |

| N/A  | VCCINT          | P7         |         |             |         |  |

| N/A  | VCCINT          | P20        |         |             |         |  |

| N/A  | VCCINT          | T10        |         |             |         |  |

| N/A  | VCCINT          | T17        |         |             |         |  |

| N/A  | VCCINT          | U7         |         |             |         |  |

### Table 8: FF672 — XC2VP2, XC2VP4, and XC2VP7

|      |                  | Pin    |        | No Connects |        |

|------|------------------|--------|--------|-------------|--------|

| Bank | Pin Description  | Number | XC2VP2 | XC2VP4      | XC2VP7 |

| 1    | IO_L06N_1        | E9     |        |             |        |

| 1    | IO_L06P_1        | E8     |        |             |        |

| 1    | IO_L05_1/No_Pair | F8     |        |             |        |

| 1    | IO_L03N_1/VREF_1 | D7     |        |             |        |

| 1    | IO_L03P_1        | E7     |        |             |        |

| 1    | IO_L02N_1        | C6     |        |             |        |

| 1    | IO_L02P_1        | D6     |        |             |        |

| 1    | IO_L01N_1/VRP_1  | A3     |        |             |        |

| 1    | IO_L01P_1/VRN_1  | B3     |        |             |        |

|      |                  |        |        |             |        |

| 2    | IO_L01N_2/VRP_2  | C4     |        |             |        |

| 2    | IO_L01P_2/VRN_2  | D3     |        |             |        |

| 2    | IO_L02N_2        | A2     |        |             |        |

| 2    | IO_L02P_2        | B1     |        |             |        |

| 2    | IO_L03N_2        | C2     |        |             |        |

| 2    | IO_L03P_2        | C1     |        |             |        |

| 2    | IO_L04N_2/VREF_2 | D2     |        |             |        |

| 2    | IO_L04P_2        | D1     |        |             |        |

| 2    | IO_L05N_2        | E4     |        |             |        |

| 2    | IO_L05P_2        | E3     |        |             |        |

| 2    | IO_L06N_2        | E2     |        |             |        |

| 2    | IO_L06P_2        | E1     |        |             |        |

| 2    | IO_L40N_2/VREF_2 | F5     | NC     | NC          | NC     |

| 2    | IO_L40P_2        | F4     | NC     | NC          | NC     |

| 2    | IO_L42N_2        | F3     | NC     | NC          | NC     |

| 2    | IO_L42P_2        | F2     | NC     | NC          | NC     |

| 2    | IO_L43N_2        | G6     | NC     |             |        |

| 2    | IO_L43P_2        | G5     | NC     |             |        |

| 2    | IO_L44N_2        | G4     | NC     |             |        |

| 2    | IO_L44P_2        | G3     | NC     |             |        |

| 2    | IO_L45N_2        | F1     | NC     |             |        |

| 2    | IO_L45P_2        | G1     | NC     |             |        |

| 2    | IO_L46N_2/VREF_2 | H6     | NC     |             |        |

| 2    | IO_L46P_2        | H5     | NC     |             |        |

| 2    | IO_L47N_2        | H4     | NC     |             |        |

| 2    | IO_L47P_2        | H3     | NC     |             |        |

| 2    | IO_L48N_2        | H2     | NC     |             |        |

### Table 11: FF1148 — XC2VP40 and XC2VP50

|      |                  |            | No Co   | nnects  |

|------|------------------|------------|---------|---------|

| Bank | Pin Description  | Pin Number | XC2VP40 | XC2VP50 |

| 6    | IO_L87N_6/VREF_6 | V33        |         |         |

| 6    | IO_L88P_6        | V30        |         |         |

| 6    | IO_L88N_6        | V31        |         |         |

| 6    | IO_L89P_6        | V24        |         |         |

| 6    | IO_L89N_6        | V25        |         |         |

| 6    | IO_L90P_6        | V28        |         |         |

| 6    | IO_L90N_6        | V29        |         |         |

|      |                  |            |         |         |

| 7    | IO_L90P_7        | U32        |         |         |

| 7    | IO_L90N_7        | V32        |         |         |

| 7    | IO_L89P_7        | U28        |         |         |

| 7    | IO_L89N_7        | U29        |         |         |

| 7    | IO_L88P_7        | U30        |         |         |

| 7    | IO_L88N_7/VREF_7 | U31        |         |         |

| 7    | IO_L87P_7        | T33        |         |         |

| 7    | IO_L87N_7        | U33        |         |         |

| 7    | IO_L86P_7        | U26        |         |         |

| 7    | IO_L86N_7        | U27        |         |         |

| 7    | IO_L85P_7        | T31        |         |         |

| 7    | IO_L85N_7        | T32        |         |         |

| 7    | IO_L60P_7        | R33        |         |         |

| 7    | IO_L60N_7        | R34        |         |         |

| 7    | IO_L59P_7        | U24        |         |         |

| 7    | IO_L59N_7        | U25        |         |         |

| 7    | IO_L58P_7        | R29        |         |         |

| 7    | IO_L58N_7/VREF_7 | R30        |         |         |

| 7    | IO_L57P_7        | P33        |         |         |

| 7    | IO_L57N_7        | P34        |         |         |

| 7    | IO_L56P_7        | T28        |         |         |

| 7    | IO_L56N_7        | T29        |         |         |

| 7    | IO_L55P_7        | P32        |         |         |

| 7    | IO_L55N_7        | R32        |         |         |

| 7    | IO_L54P_7        | P29        |         |         |

| 7    | IO_L54N_7        | P30        |         |         |

| 7    | IO_L53P_7        | T24        |         |         |

| 7    | IO_L53N_7        | T25        |         |         |

| 7    | IO_L52P_7        | N32        |         |         |

| 7    | IO_L52N_7/VREF_7 | N33        |         |         |

### Table 12: FF1517 — XC2VP50 and XC2VP70

|      |                 | Pin    |         | No Connects |  |  |

|------|-----------------|--------|---------|-------------|--|--|

| Bank | Pin Description | Number | XC2VP50 | XC2VP70     |  |  |

| N/A  | TXNPAD23        | AW36   |         |             |  |  |

| N/A  | VTTXPAD23       | AV36   |         |             |  |  |

| N/A  | AVCCAUXTX23     | AV35   |         |             |  |  |

| · ·  |                 |        |         |             |  |  |

| N/A  | VCCINT          | AH28   |         |             |  |  |

| N/A  | VCCINT          | M28    |         |             |  |  |

| N/A  | VCCINT          | AG27   |         |             |  |  |

| N/A  | VCCINT          | N27    |         |             |  |  |

| N/A  | VCCINT          | AF26   |         |             |  |  |

| N/A  | VCCINT          | P26    |         |             |  |  |

| N/A  | VCCINT          | AE25   |         |             |  |  |

| N/A  | VCCINT          | AD25   |         |             |  |  |

| N/A  | VCCINT          | AC25   |         |             |  |  |

| N/A  | VCCINT          | AB25   |         |             |  |  |

| N/A  | VCCINT          | AA25   |         |             |  |  |

| N/A  | VCCINT          | Y25    |         |             |  |  |

| N/A  | VCCINT          | W25    |         |             |  |  |

| N/A  | VCCINT          | V25    |         |             |  |  |

| N/A  | VCCINT          | U25    |         |             |  |  |

| N/A  | VCCINT          | T25    |         |             |  |  |

| N/A  | VCCINT          | R25    |         |             |  |  |

| N/A  | VCCINT          | AE24   |         |             |  |  |

| N/A  | VCCINT          | AD24   |         |             |  |  |

| N/A  | VCCINT          | T24    |         |             |  |  |

| N/A  | VCCINT          | R24    |         |             |  |  |

| N/A  | VCCINT          | AE23   |         |             |  |  |

| N/A  | VCCINT          | R23    |         |             |  |  |

| N/A  | VCCINT          | AE22   |         |             |  |  |

| N/A  | VCCINT          | R22    |         |             |  |  |

| N/A  | VCCINT          | AE21   |         |             |  |  |

| N/A  | VCCINT          | R21    |         |             |  |  |

| N/A  | VCCINT          | AE20   |         |             |  |  |

| N/A  | VCCINT          | R20    |         |             |  |  |

| N/A  | VCCINT          | AE19   |         |             |  |  |

| N/A  | VCCINT          | R19    |         |             |  |  |

| N/A  | VCCINT          | AE18   |         |             |  |  |

| N/A  | VCCINT          | R18    |         |             |  |  |

| N/A  | VCCINT          | AE17   |         |             |  |  |

### Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       | on                         |            | No Connects          |          |

|------|-----------------------|----------------------------|------------|----------------------|----------|

| Bank | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 1    | IO_L30P_1             |                            | G13        |                      |          |

| 1    | IO_L29N_1             |                            | K13        |                      |          |

| 1    | IO_L29P_1             |                            | J13        |                      |          |

| 1    | IO_L28N_1             |                            | M13        |                      |          |

| 1    | IO_L28P_1             |                            | L13        |                      |          |

| 1    | IO_L27N_1/VREF_1      |                            | E12        |                      |          |

| 1    | IO_L27P_1             |                            | D12        |                      |          |

| 1    | IO_L26N_1             |                            | F12        |                      |          |

| 1    | IO_L26P_1             |                            | G12        |                      |          |

| 1    | IO_L25N_1             |                            | J12        |                      |          |

| 1    | IO_L25P_1             |                            | H12        |                      |          |

| 1    | IO_L21N_1             |                            | L12        |                      |          |

| 1    | IO_L21P_1             |                            | K12        |                      |          |

| 1    | IO_L20N_1             |                            | C11        |                      |          |

| 1    | IO_L20P_1             |                            | C10        |                      |          |

| 1    | IO_L19N_1             |                            | F11        |                      |          |

| 1    | IO_L19P_1             |                            | E11        |                      |          |

| 1    | IO_L09N_1/VREF_1      |                            | J11        |                      |          |

| 1    | IO_L09P_1             |                            | H11        |                      |          |

| 1    | IO_L08N_1             |                            | D10        |                      |          |

| 1    | IO_L08P_1             |                            | E10        |                      |          |

| 1    | IO_L07N_1             |                            | G10        |                      |          |

| 1    | IO_L07P_1             |                            | F10        |                      |          |

| 1    | IO_L06N_1             |                            | J10        |                      |          |

| 1    | IO_L06P_1             |                            | H10        |                      |          |

| 1    | IO_L05_1/No_Pair      |                            | K11        |                      |          |

| 1    | IO_L03N_1/VREF_1      |                            | D9         |                      |          |

| 1    | IO_L03P_1             |                            | C9         |                      |          |

| 1    | IO_L02N_1             |                            | E9         |                      |          |

| 1    | IO_L02P_1             |                            | F9         |                      |          |

| 1    | IO_L01N_1/VRP_1       |                            | H9         |                      |          |

| 1    | IO_L01P_1/VRN_1       |                            | G9         |                      |          |

|      |                       |                            |            |                      | ·        |

| 2    | IO_L01N_2/VRP_2       |                            | C5         |                      |          |

| 2    | IO_L01P_2/VRN_2       |                            | C6         |                      |          |

| 2    | IO_L02N_2             |                            | E7         |                      |          |

### Table 13: FF1704 — XC2VP70, XC2VPX70, and XC2VP100

|      | Pin Description       | on                         |            | No Connects          | nnects   |

|------|-----------------------|----------------------------|------------|----------------------|----------|

| Bank | Virtex-II Pro Devices | XC2VPX70<br>(if Different) | Pin Number | XC2VP70,<br>XC2VPX70 | XC2VP100 |

| 5    | VCCO_5                |                            | AH22       |                      |          |

| 6    | VCCO_6                |                            | AU38       |                      |          |

| 6    | VCCO_6                |                            | AP40       |                      |          |

| 6    | VCCO_6                |                            | AL37       |                      |          |

| 6    | VCCO_6                |                            | AJ39       |                      |          |

| 6    | VCCO_6                |                            | AH29       |                      |          |

| 6    | VCCO_6                |                            | AG34       |                      |          |

| 6    | VCCO_6                |                            | AG29       |                      |          |

| 6    | VCCO_6                |                            | AG28       |                      |          |

| 6    | VCCO_6                |                            | AF29       |                      |          |

| 6    | VCCO_6                |                            | AF28       |                      |          |

| 6    | VCCO_6                |                            | AE40       |                      |          |

| 6    | VCCO_6                |                            | AE29       |                      |          |

| 6    | VCCO_6                |                            | AE28       |                      |          |

| 6    | VCCO_6                |                            | AD29       |                      |          |

| 6    | VCCO_6                |                            | AD28       |                      |          |

| 6    | VCCO_6                |                            | AC38       |                      |          |

| 6    | VCCO_6                |                            | AC35       |                      |          |

| 6    | VCCO_6                |                            | AC29       |                      |          |

| 6    | VCCO_6                |                            | AC28       |                      |          |

| 6    | VCCO_6                |                            | AB29       |                      |          |

| 6    | VCCO_6                |                            | AB28       |                      |          |

| 7    | VCCO_7                |                            | AA29       |                      |          |

| 7    | VCCO_7                |                            | AA28       |                      |          |

| 7    | VCCO_7                |                            | Y38        |                      |          |

| 7    | VCCO_7                |                            | Y35        |                      |          |

| 7    | VCCO_7                |                            | Y29        |                      |          |

| 7    | VCCO_7                |                            | Y28        |                      |          |

| 7    | VCCO_7                |                            | W29        |                      |          |

| 7    | VCCO_7                |                            | W28        |                      |          |

| 7    | VCCO_7                |                            | V40        |                      |          |

| 7    | VCCO_7                |                            | V29        |                      |          |

| 7    | VCCO_7                |                            | V28        |                      |          |

| 7    | VCCO_7                |                            | U29        |                      |          |

| 7    | VCCO_7                |                            | U28        |                      |          |

| 7    | VCCO_7                |                            | T34        |                      |          |

### Table 14: FF1696 — XC2VP100

|      |                  |            | No Connects |

|------|------------------|------------|-------------|

| Bank | Pin Description  | Pin Number | XC2VP100    |

| 6    | IO_L15P_6        | AP39       |             |

| 6    | IO_L15N_6/VREF_6 | AP40       |             |

| 6    | IO_L16P_6        | AP36       |             |

| 6    | IO_L16N_6        | AP37       |             |

| 6    | IO_L17P_6        | AH31       |             |

| 6    | IO_L17N_6        | AG31       |             |

| 6    | IO_L18P_6        | AN41       |             |

| 6    | IO_L18N_6        | AN42       |             |

| 6    | IO_L19P_6        | AN40       |             |

| 6    | IO_L19N_6        | AM40       |             |

| 6    | IO_L20P_6        | AG34       |             |

| 6    | IO_L20N_6        | AG35       |             |

| 6    | IO_L21P_6        | AN37       |             |

| 6    | IO_L21N_6/VREF_6 | AN38       |             |

| 6    | IO_L22P_6        | AN36       |             |

| 6    | IO_L22N_6        | AM36       |             |

| 6    | IO_L23P_6        | AG32       |             |

| 6    | IO_L23N_6        | AG33       |             |

| 6    | IO_L24P_6        | AM41       |             |

| 6    | IO_L24N_6        | AM42       |             |

| 6    | IO_L25P_6        | AM38       |             |

| 6    | IO_L25N_6        | AM39       |             |

| 6    | IO_L26P_6        | AF35       |             |

| 6    | IO_L26N_6        | AF36       |             |

| 6    | IO_L27P_6        | AM37       |             |

| 6    | IO_L27N_6/VREF_6 | AL36       |             |

| 6    | IO_L28P_6        | AL41       |             |

| 6    | IO_L28N_6        | AK41       |             |

| 6    | IO_L29P_6        | AF32       |             |

| 6    | IO_L29N_6        | AF33       |             |

| 6    | IO_L30P_6        | AL39       |             |

| 6    | IO_L30N_6        | AL40       |             |

| 6    | IO_L31P_6        | AL37       |             |

| 6    | IO_L31N_6        | AL38       |             |

| 6    | IO_L32P_6        | AF31       |             |

| 6    | IO_L32N_6        | AE31       |             |

| 6    | IO_L33P_6        | AK39       |             |

### Table 14: FF1696 — XC2VP100

|      |                  |            | No Connects |  |

|------|------------------|------------|-------------|--|

| Bank | Pin Description  | Pin Number | XC2VP100    |  |

| 6    | IO_L33N_6/VREF_6 | AK40       |             |  |

| 6    | IO_L34P_6        | AK36       |             |  |

| 6    | IO_L34N_6        | AK37       |             |  |

| 6    | IO_L35P_6        | AE36       |             |  |

| 6    | IO_L35N_6        | AE37       |             |  |

| 6    | IO_L36P_6        | AJ41       |             |  |

| 6    | IO_L36N_6        | AJ42       |             |  |

| 6    | IO_L37P_6        | AJ40       |             |  |

| 6    | IO_L37N_6        | AH40       |             |  |

| 6    | IO_L38P_6        | AE34       |             |  |

| 6    | IO_L38N_6        | AE35       |             |  |

| 6    | IO_L39P_6        | AJ38       |             |  |

| 6    | IO_L39N_6/VREF_6 | AH37       |             |  |

| 6    | IO_L40P_6        | AJ36       |             |  |

| 6    | IO_L40N_6        | AJ37       |             |  |

| 6    | IO_L41P_6        | AE32       |             |  |

| 6    | IO_L41N_6        | AE33       |             |  |

| 6    | IO_L42P_6        | AH41       |             |  |

| 6    | IO_L42N_6        | AH42       |             |  |

| 6    | IO_L43P_6        | AH38       |             |  |

| 6    | IO_L43N_6        | AH39       |             |  |

| 6    | IO_L44P_6        | AD36       |             |  |

| 6    | IO_L44N_6        | AC35       |             |  |

| 6    | IO_L45P_6        | AH36       |             |  |

| 6    | IO_L45N_6/VREF_6 | AG36       |             |  |

| 6    | IO_L46P_6        | AG41       |             |  |

| 6    | IO_L46N_6        | AG42       |             |  |

| 6    | IO_L47P_6        | AD34       |             |  |

| 6    | IO_L47N_6        | AC33       |             |  |

| 6    | IO_L48P_6        | AG40       |             |  |

| 6    | IO_L48N_6        | AF39       |             |  |

| 6    | IO_L49P_6        | AG38       |             |  |

| 6    | IO_L49N_6        | AG39       |             |  |

| 6    | IO_L50P_6        | AD32       |             |  |

| 6    | IO_L50N_6        | AD33       |             |  |

| 6    | IO_L51P_6        | AG37       |             |  |

| 6    | IO_L51N_6/VREF_6 | AF37       |             |  |

### Table 14: FF1696 — XC2VP100

|      |                 |            | No Connects |

|------|-----------------|------------|-------------|

| Bank | Pin Description | Pin Number | XC2VP100    |

| N/A  | VCCINT          | AG26       |             |

| N/A  | VCCINT          | AF26       |             |

| N/A  | VCCINT          | U26        |             |

| N/A  | VCCINT          | T26        |             |

| N/A  | VCCINT          | R26        |             |

| N/A  | VCCINT          | AG25       |             |

| N/A  | VCCINT          | T25        |             |

| N/A  | VCCINT          | AG24       |             |

| N/A  | VCCINT          | T24        |             |

| N/A  | VCCINT          | AG23       |             |

| N/A  | VCCINT          | T23        |             |

| N/A  | VCCINT          | AG22       |             |

| N/A  | VCCINT          | T22        |             |

| N/A  | VCCINT          | AG21       |             |

| N/A  | VCCINT          | T21        |             |

| N/A  | VCCINT          | AG20       |             |

| N/A  | VCCINT          | T20        |             |

| N/A  | VCCINT          | AG19       |             |

| N/A  | VCCINT          | T19        |             |

| N/A  | VCCINT          | AG18       |             |

| N/A  | VCCINT          | T18        |             |

| N/A  | VCCINT          | AH17       |             |

| N/A  | VCCINT          | AG17       |             |

| N/A  | VCCINT          | AF17       |             |

| N/A  | VCCINT          | U17        |             |

| N/A  | VCCINT          | T17        |             |

| N/A  | VCCINT          | R17        |             |

| N/A  | VCCINT          | AJ16       |             |

| N/A  | VCCINT          | AH16       |             |

| N/A  | VCCINT          | AG16       |             |

| N/A  | VCCINT          | AF16       |             |

| N/A  | VCCINT          | AE16       |             |

| N/A  | VCCINT          | AD16       |             |

| N/A  | VCCINT          | AC16       |             |

| N/A  | VCCINT          | AB16       |             |

| N/A  | VCCINT          | AA16       |             |

| N/A  | VCCINT          | Y16        |             |