Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Active                                                                |

|-------------------------|-----------------------------------------------------------------------|

| Туре                    | Floating Point                                                        |

| Interface               | CAN, I <sup>2</sup> C, SPI, SPORT, UART/USART, USB                    |

| Clock Rate              | 240MHz                                                                |

| Non-Volatile Memory     | FLASH (2MB)                                                           |

| On-Chip RAM             | 384kB                                                                 |

| Voltage - I/O           | 3.30V                                                                 |

| Voltage - Core          | 1.20V                                                                 |

| Operating Temperature   | -40°C ~ 105°C (TA)                                                    |

| Mounting Type           | Surface Mount                                                         |

| Package / Case          | 176-LQFP Exposed Pad                                                  |

| Supplier Device Package | 176-LQFP-EP (24x24)                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-cm408cswz-bf |

|                         |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **ANALOG FRONT END**

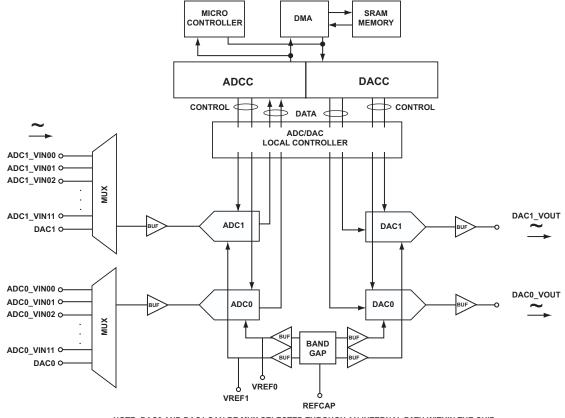

The mixed-signal controllers contain two ADCs and two DACs. Control of these data converters is simplified by a powerful onchip analog-to-digital conversion controller (ADCC) and a digital-to-analog conversion controller (DACC). The ADCC and DACC are integrated seamlessly into the software programming model, and they efficiently manage the configuration and realtime operation of the ADCs and DACs.

For technical details, see ADC/DAC Specifications on Page 68.

The ADCC provides the mechanism to precisely control execution of timing and analog sampling events on the ADCs. The ADCC supports two-channel (one each—ADC0, ADC1) simultaneous sampling of ADC inputs and can deliver 16 channels of ADC data to memory in 3  $\mu$ s. Conversion data from the ADCs may be either routed via DMA to memory, or to a destination register via the processor. The ADCC can be configured so that the two ADCs sample and convert both analog inputs

simultaneously or at different times and may be operated in asynchronous or synchronous modes. The best performance can be achieved in synchronous mode.

Likewise, the DACC interfaces to two DACs and has purpose of managing those DACs. Conversion data to the DACs may be either routed from memory through DMA, or from a source register via the processor.

Functional operation and programming for the ADCC and DACC are described in detail in the *ADSP-CM40x Mixed-Signal Control Processor with ARM Cortex-M4 Hardware Reference.*

ADC and DAC features and performance specifications differ by processor model. Simplified block diagrams of the ADCC/DACC and the ADC/DAC are shown in Figure 2 and Figure 3.

NOTE: DAC0 AND DAC1 CAN BE MUX SELECTED THROUGH AN INTERNAL PATH WITHIN THE CHIP. SEE THE HARDWARE REFERENCE MANUAL FOR PROGRAMMING DETAIL.

Figure 2. ADSP-CM402F/ADSP-CM403F/ADSP-CM409F Analog Front End Block Diagram

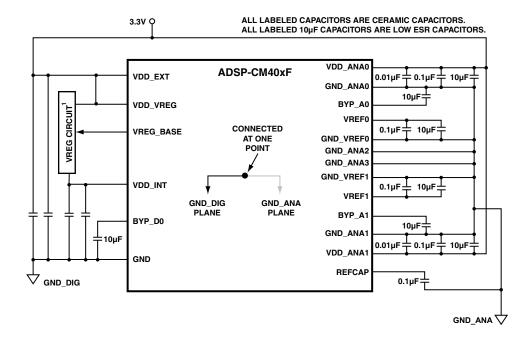

Figure 4. Typical Power Supply Configuration

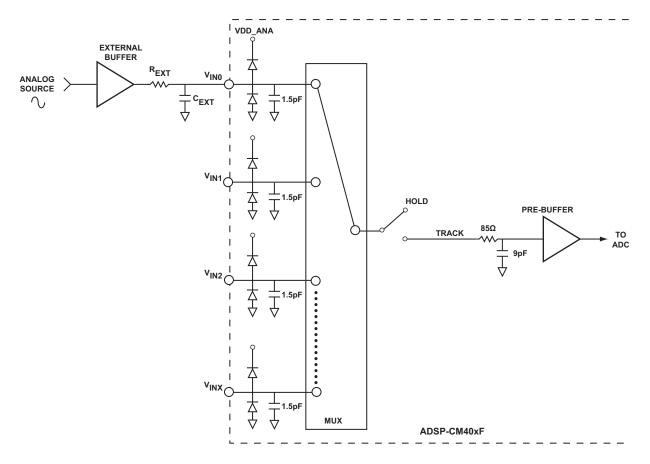

Figure 5. Equivalent Single-Ended Input (Simplified)

Rev. A | Page 6 of 124 | November 2015

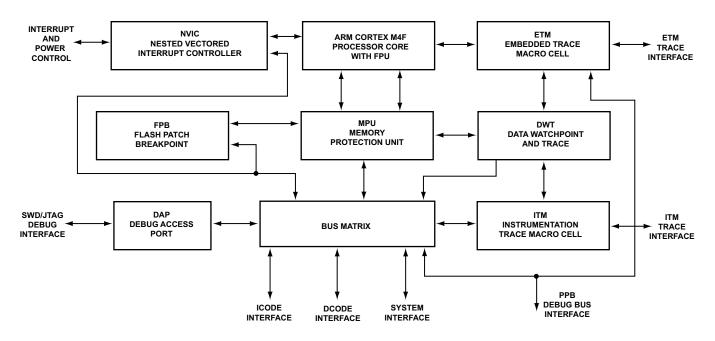

### **ARM CORTEX-M4 CORE**

The ARM Cortex-M4, core shown in Figure 6, is a 32-bit reduced instruction set computer (RISC). It uses 32-bit buses for instruction and data. The length of the data can be 8 bits, 16 bits, or 32 bits. The length of the instruction word is 16 or 32 bits. The controller has the following features.

#### **Cortex-M4 Architecture**

- Thumb-2 ISA technology

- DSP and SIMD extensions

- Single cycle MAC (Up to  $32 \times 32 + 64 \rightarrow 64$ )

- Hardware divide instructions

- Single-precision FPU

- NVIC interrupt controller (129 interrupts and 16 priorities)

- Memory protection unit (MPU)

- Full CoreSight<sup>™</sup> debug, trace, breakpoints, watchpoints, and cross-triggers

#### Microarchitecture

- 3-stage pipeline with branch speculation

- Low-latency interrupt processing with tail chaining

#### Configurable For Ultra Low Power

- Deep sleep mode, dynamic power management

- Programmable clock generator unit

### EmbeddedICE

EmbeddedICE<sup>™</sup> provides integrated on-chip support for the core. The EmbeddedICE module contains the breakpoint and watchpoint registers that allow code to be halted for debugging purposes. These registers are controlled through the JTAG test port.

When a breakpoint or watchpoint is encountered, the processor halts and enters debug state. Once in a debug state, the processor registers can be inspected as well as the Flash/EE, SRAM, and memory-mapped registers.

Figure 6. Cortex-M4 Block Diagram

The timer unit can be used in conjunction with the UARTs and the CAN controller to measure the width of the pulses in the data stream to provide a software auto-baud detect function for the respective serial channels.

The timer can generate interrupts to the processor core, providing periodic events for synchronization to either the system clock or to external signals. Timer events can also trigger other peripherals via the TRU (for instance, to signal a fault).

### Watchdog Timer (WDT)

The core includes a 32-bit timer, which may be used to implement a software watchdog function. A software watchdog can improve system availability by forcing the processor to a known state, via generation of a general-purpose interrupt, if the timer expires before being reset by software. The programmer initializes the count value of the timer, enables the appropriate interrupt, then enables the timer. Thereafter, the software must reload the counter before it counts to zero from the programmed value. This protects the system from remaining in an unknown state where software, which would normally reset the timer, has stopped running due to an external noise condition or software error. Optionally, the fault management unit (FMU) can directly initiate the processor reset upon the watchdog expiry event.

### Capture Timer (CPTMR)

The processor includes three instants of capture timers (CPTMR) to capture total on time. Each capture timer captures total on time of the input signal between two leading edges of the input trigger signal. Capture timer inputs to all the timers come from external pins and the input trigger signal comes from trigger routing unit (TRU).

The core of the timer is a 32-bit counter which is reset at leading edge of the trigger and counts when the input signal level is active. The total on time of the input signal is captured from the counter at the leading edge of the trigger pulse. Capture timer can generate data interrupts to the processor core at leading edges of trigger pulses and status interrupts to indicate counter overflow condition.

### 3-Phase Pulse Width Modulator Unit (PWM)

The pulse width modulator (PWM) unit provides duty cycle and phase control capabilities to a resolution of one system clock cycle (SCLK). The heightened precision PWM (HPPWM) module provides increased performance to the PWM unit by increasing its resolution by several bits, resulting in enhanced precision levels. Additional features include:

- 16-bit center-based PWM generation unit

- Programmable PWM pulse width

- Single/double update modes

- Programmable dead time and switching frequency

- Twos-complement implementation which permits smooth transition to full on and full off states

- Dedicated asynchronous PWM trip signal

The eight PWM output signals (per PWM unit) consist of four high-side drive signals and four low-side drive signals. The polarity of a generated PWM signal can be set with software, so that either active high or active low PWM patterns can be produced.

Each PWM block integrates a flexible and programmable 3-phase PWM waveform generator that can be programmed to generate the required switching patterns to drive a 3-phase voltage source inverter for ac induction motor (ACIM) or permanent magnet synchronous motor (PMSM) control. In addition, the PWM block contains special functions that considerably simplify the generation of the required PWM switching patterns for control of the electronically commutated motor (ECM) or permanent magnet synchronous motor (PMSM) control. Software can enable a special mode for switched reluctance motors (SRM).

Each PWM unit features a dedicated asynchronous trip pin which (when brought low) instantaneously places all PWM outputs in the off state.

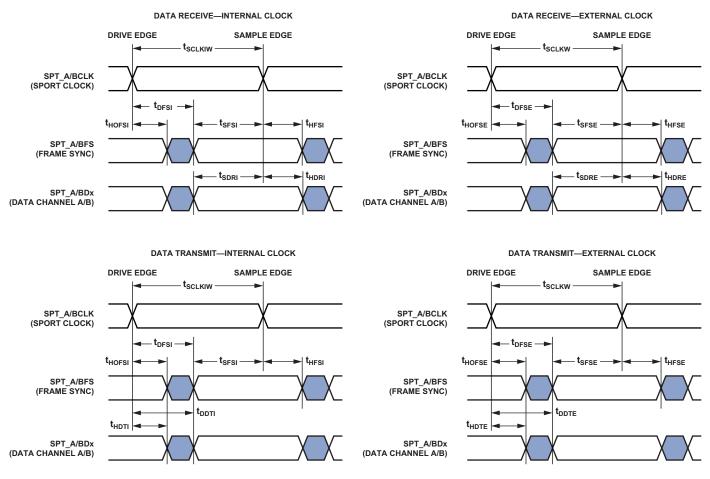

### Serial Ports (SPORTs)

The synchronous serial ports provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices such as Analog Devices, Inc., audio codecs, ADCs, and DACs. The serial ports are made up of two data lines per direction, a clock, and frame sync. The data lines can be programmed to either transmit or receive and each data line has a dedicated DMA channel.

Serial port data can be automatically transferred to and from on-chip memory/external memory via dedicated DMA channels.For full-duplex operation, two half SPORTs can work in conjunction with clock and frame sync signals shared internally through the SPMUX block. In some operation modes, SPORT supports gated clock.

Serial ports operate in six modes:

- Standard DSP serial mode

- Multichannel (TDM) mode

- I<sup>2</sup>S mode

- Packed I<sup>2</sup>S mode

- · Left-justified mode

- Right-justified mode

### **General-Purpose Counters**

The 32-bit counter can operate in general-purpose up/down count modes and can sense 2-bit quadrature or binary codes as typically emitted by industrial drives or manual thumbwheels. Count direction is either controlled by a level-sensitive input pin or by two edge detectors.

A third counter input can provide flexible zero marker support and can alternatively be used to input the push-button signal of thumb wheels. All three pins have a programmable debouncing circuit.

registers with associated hardware. These four SWU match groups operate independently, but share common event (interrupt and trigger) outputs.

### **DEVELOPMENT TOOLS**

The ADSP-CM40xF processor is supported with a set of highly sophisticated and easy-to-use development tools for embedded applications. For more information, see the Analog Devices website.

### **ADDITIONAL INFORMATION**

The following publications that describe the ADSP-CM40xF processors (and related processors) can be ordered from any Analog Devices sales office or accessed electronically on our website:

- ADSP-CM40x Mixed-Signal Control Processor with ARM Cortex-M4 Hardware Reference

- ADSP-CM402F/CM403F/CM407F/CM408F/CM409F Anomaly Sheet

This data sheet describes the ARM Cortex-M4 core and memory architecture used on the ADSP-CM40xF processor, but does not provide detailed programming information for the ARM processor. For more information about programming the ARM processor, visit the ARM Infocenter web page.

The applicable documentation for programming the ARM Cortex-M4 processor include:

- Cortex<sup>®</sup>-M4 Devices Generic User Guide

- CoreSight<sup>™</sup> ETM<sup>™</sup>-M4 Technical Reference Manual

- Cortex<sup>®</sup>-M4 Technical Reference Manual

### **RELATED SIGNAL CHAINS**

A signal chain is a series of signal-conditioning electronic components that receive input (data acquired from sampling either real-time phenomena or from stored data) in tandem, with the output of one portion of the chain supplying input to the next. Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on analysis of real-time phenomena.

Analog Devices eases signal processing system development by providing signal processing components that are designed to work together well. A tool for viewing relationships between specific applications and related components is available on the www.analog.com website.

The application signal chains page in the Circuits from the Lab<sup>®</sup> site (http://www.analog.com/circuits) provides:

- Graphical circuit block diagram presentation of signal chains for a variety of circuit types and applications

- Drill down links for components in each chain to selection guides and application information

- Reference designs applying best practice design techniques

### SECURITY FEATURES DISCLAIMER

To our knowledge, the Security Features, when used in accordance with the data sheet and hardware reference manual specifications, provide a secure method of implementing code and data safeguards. However, Analog Devices does not guarantee that this technology provides absolute security. ACCORDINGLY, ANALOG DEVICES HEREBY DISCLAIMS ANY AND ALL EXPRESS AND IMPLIED WARRANTIES THAT THE SECURITY FEATURES CANNOT BE BREACHED, COMPROMISED, OR OTHERWISE CIRCUM-VENTED AND IN NO EVENT SHALL ANALOG DEVICES BE LIABLE FOR ANY LOSS, DAMAGE, DESTRUCTION, OR RELEASE OF DATA, INFORMATION, PHYSICAL PROP-ERTY, OR INTELLECTUAL PROPERTY.

#### **Signal Name Direction** Description I/O SPT\_AFS SPORT A Channel Frame Sync. The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally. SPT\_ATDV Output SPORT A Channel Transmit Data Valid. This signal is optional and only active when SPORT is configured in multi-channel transmit mode. It is asserted during enabled slots. I/O SPT\_BCLK SPORT B Channel Clock. Data and frame sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated. SPT\_BD0 I/O SPORT B Channel Data 0. Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data. I/O SPT\_BD1 SPORT B Channel Data 1. Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data, or as an input to receive serial data. I/O SPT BFS SPORT B Channel Frame Sync. The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally. Output SPORT B Channel Transmit Data Valid. This signal is optional and only active when SPORT is configured in SPT\_BTDV multi-channel transmit mode. It is asserted during enabled slots. SYS\_BMODEn Input **Boot Mode Control n.** Selects the boot mode of the processor. n = 0, 1SYS\_CLKIN Input Processor Clock/Crystal Input. Connect to an external clock source or crystal. SYS CLKOUT Output Processor Clock Output. Outputs internal clocks. Clocks may be divided down. See the CGU chapter in the processor hardware reference for more details. SYS\_DSWAKEn Input System Deep Sleep Wakeup inputs. n = 0 to 3 SYS FAULT Output System Fault. Indicates system fault. SYS\_HWRST Input Processor Hardware Reset Control. Resets the device when asserted. SYS\_NMI Input Non-maskable Interrupt. See the processor hardware and programming references for more details. SYS\_RESOUT Output Processor Reset Output. Indicates that the device is in the reset state. SYS XTAL Output System Crystal Output. Drives an external crystal. Must be left unconnected if an external clock is driving CLKIN. Input TM\_ACIn GP Timer Alternate Capture Input n. Provides an additional input for GP Timers in WIDCAP, WATCHDOG, and PININT modes. n = 0 to 5 TM\_ACLKn Input GP Timer Alternate Clock n. Provides an additional time base for use by an individual timer. n = 0 to 5 TM\_CLK Input GP Timer Clock. Provides an additional global time base for use by all the GP timers. I/O GP Timer Timer n. The main input/output signal for each timer. n = 0 to 7. In PWM OUT mode, output is driven TM\_TMRn on this pin. In Width capture mode, it acts as input and Timer measures width and/or period of incoming signal on this pin. In EXTCLK mode, Timer counts number of incoming signal edges on this pin. Embedded Trace Module Clock. Reference clock for the Trace Unit. TRACE CLK Output TRACE\_Dn Output Embedded Trace Module Data n. Output data for clocked modes and changes on both edges of TRACE\_CLK. n = 0 to 3TWI\_SCL I/O TWI Serial Clock. Clock output when master, clock input when slave. Compatible with I<sup>2</sup>C bus standard. TWI\_SDA I/O TWI Serial Data. Receives or transmits data. Compatible with I<sup>2</sup>C bus standard. UART CTS Input **UART Clear to Send.** Input Hardware Flow control signal. Transmitter initiates the transfer only when this signal is active. UART RTS Output UART Request to Send. Output Hardware Flow control signal. Receiver activates this signal when it is ready to receive new transfers. UART\_RX Input UART Receive. Receive input. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with. UART\_TX Output UART Transmit. Transmit output. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with. USB\_DM I/O USB Data -. Bidirectional differential data line. USB DP I/O USB Data +. Bidirectional differential data line.

#### Table 6. ADSP-CM40xF Detailed Signal Description (Continued)

### Table 7. ADSP-CM402F/ADSP-CM403F 120-Lead LQFP Signal Descriptions (Continued)

| Signal Name | Description                                                                                  | Port      | Pin Name  |

|-------------|----------------------------------------------------------------------------------------------|-----------|-----------|

| PWM1_DL     | PWM1 Channel D Low Side                                                                      | В         | PB_03     |

| PWM1_SYNC   | PWM1 Sync                                                                                    | A         | PA_10     |

| PWM1_TRIP0  | PWM1 Trip Input 0                                                                            | A         | PA_11     |

| PWM2_AH     | PWM2 Channel A High Side                                                                     | В         | PB_06     |

| PWM2_AL     | PWM2 Channel A Low Side                                                                      | В         | PB_07     |

| PWM2_BH     | PWM2 Channel B High Side                                                                     | В         | PB_08     |

| PWM2_BL     | PWM2 Channel B Low Side                                                                      | В         | PB_09     |

| PWM2_CH     | PWM2 Channel C High Side                                                                     | С         | PC_03     |

| PWM2_CL     | PWM2 Channel C Low Side                                                                      | С         | PC_04     |

| PWM2_DH     | PWM2 Channel D High Side                                                                     | С         | PC_05     |

| PWM2_DL     | PWM2 Channel D Low Side                                                                      | С         | PC_06     |

| PWM2_SYNC   | PWM2 Sync                                                                                    | В         | PB_04     |

| PWM2_TRIP0  | PWM2 Trip Input 0                                                                            | В         | PB_05     |

| REFCAP      | Output of BandGap Generator Filter Node (see recommended bypass filter - Figure 4 on Page 6) | Not Muxed | REFCAP    |

| SINC0_CLK0  | SINC0 Clock 0                                                                                | В         | PB_10     |

| SINC0_CLK1  | SINC0 Clock 1                                                                                | С         | PC_07     |

| SINC0_D0    | SINC0 Data 0                                                                                 | В         | PB_11     |

| SINC0_D1    | SINC0 Data 1                                                                                 | В         | PB_12     |

| SINC0_D2    | SINC0 Data 2                                                                                 | В         | PB_13     |

| SINC0_D3    | SINC0 Data 3                                                                                 | В         | PB_14     |

| SMC0_A01    | SMC0 Address 1                                                                               | В         | PB_13     |

| SMC0_A02    | SMC0 Address 2                                                                               | В         | PB_14     |

| SMC0_A03    | SMC0 Address 3                                                                               | В         | PB_15     |

| SMC0_A04    | SMC0 Address 4                                                                               | с         | PC_00     |

| SMC0_A05    | SMC0 Address 5                                                                               | с         | PC_01     |

| SMC0_AMS0   | SMC0 Memory Select 0                                                                         | В         | PB_11     |

| SMC0_AMS2   | SMC0 Memory Select 2                                                                         | А         | PA_07     |

| SMC0_AOE    | SMC0 Output Enable                                                                           | В         | PB_12     |

| SMC0_ARDY   | SMC0 Asynchronous Ready                                                                      | В         | PB_08     |

| SMC0_ARE    | SMC0 Read Enable                                                                             | В         | PB_09     |

| SMC0_AWE    | SMC0 Write Enable                                                                            | В         | PB_10     |

| SMC0_D00    | SMC0 Data 0                                                                                  | А         | PA_08     |

| SMC0_D01    | SMC0 Data 1                                                                                  | А         | PA_09     |

| SMC0_D02    | SMC0 Data 2                                                                                  | А         | PA_10     |

| SMC0_D03    | SMC0 Data 3                                                                                  | А         | PA_11     |

| SMC0_D04    | SMC0 Data 4                                                                                  | А         | PA_12     |

| SMC0_D05    | SMC0 Data 5                                                                                  | А         | PA_13     |

| SMC0_D06    | SMC0 Data 6                                                                                  | А         | PA_14     |

| SMC0_D07    | SMC0 Data 7                                                                                  | А         | PA_15     |

| SMC0_D08    | SMC0 Data 8                                                                                  | В         | PB_00     |

| SMC0D09     | SMC0 Data 9                                                                                  | В         | <br>PB_01 |

| SMC0_D10    | SMC0 Data 10                                                                                 | В         | PB_02     |

| SMC0_D11    | SMC0 Data 11                                                                                 | В         | PB_03     |

| SMC0_D12    | SMC0 Data 12                                                                                 | В         | PB_04     |

| SMC0_D13    | SMC0 Data 13                                                                                 | В         | PB_05     |

| Signal Name | Multiplexed<br>Function 0 | Multiplexed<br>Function 1 | Multiplexed<br>Function 2 | Multiplexed<br>Function 3 | Multiplexed<br>Function Input Tap |

|-------------|---------------------------|---------------------------|---------------------------|---------------------------|-----------------------------------|

| PC_00       | CAN0_TX                   | SPT1_BTDV                 | UART1_TX                  | SMC0_A04                  |                                   |

| PC_01       | UARTO_RX                  |                           |                           | SMC0_A05                  | TM0_ACI5                          |

| PC_02       | UART0_TX                  | TRACE_D03                 | SPI0_RDY                  |                           |                                   |

| PC_03       | SPI0_CLK                  | PWM2_CH                   |                           |                           |                                   |

| PC_04       | SPI0_MISO                 | PWM2_CL                   |                           |                           |                                   |

| PC_05       | SPI0_MOSI                 | PWM2_DH                   |                           |                           |                                   |

| PC_06       | SPI0_SEL1                 | PWM2_DL                   |                           |                           | SYS_DSWAKE0                       |

| PC_07       | SINC0_CLK1                | UART2_TX                  | UART1_RTS                 |                           | SYS_DSWAKE1                       |

### Table 10. Signal Multiplexing for Port C (120-Lead LQFP)

| Ciana I Nama | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed        |

|--------------|-------------|-------------|-------------|-------------|--------------------|

| Signal Name  | Function 0  | Function 1  | Function 2  | Function 3  | Function Input Tap |

| PC_00        | CAN0_TX     | SPT1_BTDV   | UART1_TX    | SMC0_A04    |                    |

| PC_01        | UART0_RX    |             |             | SMC0_A05    | TM0_ACI5           |

| PC_02        | UART0_TX    | TRACE_D03   | SPI0_RDY    |             |                    |

| PC_03        | SPI0_CLK    | PWM2_CH     |             |             |                    |

| PC_04        | SPI0_MISO   | PWM2_CL     |             |             |                    |

| PC_05        | SPI0_MOSI   | PWM2_DH     |             |             |                    |

| PC_06        | SPI0_SEL1   | PWM2_DL     |             |             | SYS_DSWAKE0        |

| PC_07        | SINC0_CLK1  | UART2_TX    | UART1_RTS   |             | SYS_DSWAKE1        |

| PC_08        |             | SPT0_BCLK   | SMC0_D00    |             |                    |

| PC_09        |             | SPT0_BFS    | SMC0_D01    |             |                    |

| PC_10        |             | SPT0_BD0    | SMC0_D02    |             |                    |

| PC_11        | SMC0_AMS3   | SPT0_BD1    | SMC0_D03    |             |                    |

| PC_12        |             | SPI1_CLK    | SMC0_D04    |             |                    |

| PC_13        |             | SPI1_MISO   | SMC0_D05    |             |                    |

| PC_14        |             | SPI1_MOSI   | SMC0_D06    |             |                    |

| PC_15        |             | SPI1_SEL1   | SMC0_D07    |             | SPI1_SS            |

#### Table 14. Signal Multiplexing for Port C (176-Lead LQFP)

### Table 15. Signal Multiplexing for Port D (176-Lead LQFP)

|             | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed        |

|-------------|-------------|-------------|-------------|-------------|--------------------|

| Signal Name | Function 0  | Function 1  | Function 2  | Function 3  | Function Input Tap |

| PD_00       |             |             | SMC0_D08    | TM0_TMR0    |                    |

| PD_01       |             |             | SMC0_D09    | TM0_TMR1    |                    |

| PD_02       |             |             | SMC0_D10    | TM0_TMR2    |                    |

| PD_03       |             |             | SMC0_D11    | TM0_TMR3    |                    |

| PD_04       |             |             | SMC0_D12    | TM0_TMR4    |                    |

| PD_05       |             |             | SMC0_D13    | TM0_TMR5    |                    |

| PD_06       |             |             | SMC0_D14    | TM0_TMR6    |                    |

| PD_07       |             |             | SMC0_D15    | TM0_TMR7    |                    |

| PD_08       |             |             | SMC0_A06    | TM0_CLK     |                    |

| PD_09       |             |             | SMC0_A07    | TM0_ACI5    |                    |

| PD_10       |             |             | SMC0_A08    | TM0_ACI4    |                    |

| PD_11       |             |             | SMC0_A09    | TM0_ACI3    |                    |

| PD_12       |             |             | SMC0_A10    | TM0_ACI2    |                    |

| PD_13       |             |             | SMC0_A11    | TM0_ACI1    |                    |

| PD_14       |             |             | SMC0_A12    |             |                    |

| PD_15       |             |             | SMC0_A13    |             |                    |

#### Table 18. ADSP-CM409F 212-Ball BGA Signal Descriptions (Continued)

| Signal Name | Description                  | Port           | Pin Name  |

|-------------|------------------------------|----------------|-----------|

| TM0_ACLK3   | TIMER0 Alternate Clock 3     | А              | PA_10     |

| TM0_ACLK4   | TIMER0 Alternate Clock 4     | А              | PA_09     |

| TM0_ACLK5   | TIMER0 Alternate Clock 5     | А              | PA_08     |

| TM0_CLK     | TIMER0 Clock                 | В              | PB_06     |

| TM0_CLK     | TIMER0 Clock                 | D              | PD_08     |

| TM0_TMR0    | TIMER0 Timer 0               | В              | PB_07     |

| TM0_TMR0    | TIMER0 Timer 0               | D              | PD_00     |

| TM0_TMR1    | TIMER0 Timer 1               | В              | PB_08     |

| TM0_TMR1    | TIMER0 Timer 1               | D              | PD_01     |

| TM0_TMR2    | TIMER0 Timer 2               | В              | PB_09     |

| TM0_TMR2    | TIMER0 Timer 2               | D              | PD_02     |

| TM0_TMR3    | TIMER0 Timer 3               | А              | PA_15     |

| TM0_TMR3    | TIMER0 Timer 3               | D              | PD_03     |

| TM0_TMR4    | TIMER0 Timer 4               | A              | PA_12     |

| TM0_TMR4    | TIMERO Timer 4               | D              | PD_04     |

| TM0_TMR5    | TIMERO Timer 5               | A              | PA_13     |

| TM0_TMR5    | TIMERO Timer 5               | D              | PD_05     |

| TM0_TMR6    | TIMERO Timer 6               | A              | PA_14     |

| TM0_TMR6    | TIMERO Timer 6               | D              | PD_06     |

| TM0_TMR7    | TIMERO Timer 7               | В              | PB_05     |

| TM0_TMR7    | TIMERO Timer 7               | D              | PD_07     |

| TRACE_CLK   | Embedded Trace Module Clock  | В              | PB_00     |

| TRACE_D00   | Embedded Trace Module Data 0 | B              | PB_01     |

| TRACE_D01   | Embedded Trace Module Data 1 | В              | PB_02     |

| TRACE_D02   | Embedded Trace Module Data 2 | В              | PB_03     |

| TRACE_D02   | Embedded Trace Module Data 2 | C              | PC_02     |

| TRACE_D03   | Embedded Trace Module Data 3 | F              | PF_02     |

| TWI0_SCL    | TWIO Serial Clock            | '<br>Not Muxed | TWI0_SCL  |

| TWI0_SCL    | TWIO Serial Data             | Not Muxed      | TWI0_SCL  |

| UARTO_CTS   | UARTO Clear to Send          | B              | PB_05     |

| UARTO_RTS   | UARTO Request to Send        | В              | PB_04     |

| UARTO_RX    | UARTO Receive                | C              | PC_01     |

| UARTO_TX    | UARTO Transmit               | c              | PC_02     |

| UART1_CTS   | UART1 Clear to Send          |                | PA_11     |

| UART1_CTS   | UART1 Request to Send        | A<br>C         | PC_07     |

| UART1_RT3   | UART1 Receive                | В              | —         |

| UART1_RX    |                              |                | PB_08     |

|             | UART1 Receive                | В              | PB_15     |

| UART1_TX    | UART1 Transmit               | В              | PB_09     |

| UART1_TX    | UART1 Transmit               | C              | PC_00     |

| UART2_RX    | UART2 Receive                | В              | PB_12     |

| UART2_TX    | UART2 Transmit               | C              | PC_07     |

| USB0_DM     | USB0 Data –                  | Not Muxed      | USB0_DM   |

| USB0_DP     | USB0 Data +                  | Not Muxed      | USB0_DP   |

| USB0_ID     | USB0 OTG ID                  | Not Muxed      | USB0_ID   |

| USB0_VBC    | USB0 VBUS Control            | F              | PF_02     |

| USB0_VBUS   | USB0 Bus Voltage             | Not Muxed      | USB0_VBUS |

| Circuit Name | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed        |

|--------------|-------------|-------------|-------------|-------------|--------------------|

| Signal Name  | Function 0  | Function 1  | Function 2  | Function 3  | Function Input Tap |

| PC_00        | CAN0_TX     | SPT1_BTDV   | UART1_TX    | SMC0_A04    |                    |

| PC_01        | UART0_RX    |             |             | SMC0_A05    | TM0_ACI5           |

| PC_02        | UART0_TX    | TRACE_D03   | SPI0_RDY    |             |                    |

| PC_03        | SPI0_CLK    | PWM2_CH     |             |             |                    |

| PC_04        | SPI0_MISO   | PWM2_CL     |             |             |                    |

| PC_05        | SPI0_MOSI   | PWM2_DH     |             |             |                    |

| PC_06        | SPI0_SEL1   | PWM2_DL     |             |             | SYS_DSWAKE0        |

| PC_07        | SINC0_CLK1  | UART2_TX    | UART1_RTS   |             | SYS_DSWAKE1        |

| PC_08        |             | SPT0_BCLK   | SMC0_D00    |             |                    |

| PC_09        |             | SPT0_BFS    | SMC0_D01    |             |                    |

| PC_10        |             | SPT0_BD0    | SMC0_D02    |             |                    |

| PC_11        | SMC0_AMS3   | SPT0_BD1    | SMC0_D03    |             |                    |

| PC_12        |             | SPI1_CLK    | SMC0_D04    |             |                    |

| PC_13        |             | SPI1_MISO   | SMC0_D05    |             |                    |

| PC_14        |             | SPI1_MOSI   | SMC0_D06    |             |                    |

| PC_15        |             | SPI1_SEL1   | SMC0_D07    |             | SPI1_SS            |

Table 21. Signal Multiplexing for Port C (212-Ball BGA)

Table 22. Signal Multiplexing for Port D (212-Ball BGA)

|             | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed        |

|-------------|-------------|-------------|-------------|-------------|--------------------|

| Signal Name | Function 0  | Function 1  | Function 2  | Function 3  | Function Input Tap |

| PD_00       |             |             | SMC0_D08    | TM0_TMR0    |                    |

| PD_01       |             |             | SMC0_D09    | TM0_TMR1    |                    |

| PD_02       |             |             | SMC0_D10    | TM0_TMR2    |                    |

| PD_03       |             |             | SMC0_D11    | TM0_TMR3    |                    |

| PD_04       |             |             | SMC0_D12    | TM0_TMR4    |                    |

| PD_05       |             |             | SMC0_D13    | TM0_TMR5    |                    |

| PD_06       |             |             | SMC0_D14    | TM0_TMR6    |                    |

| PD_07       |             |             | SMC0_D15    | TM0_TMR7    |                    |

| PD_08       |             |             | SMC0_A06    | TM0_CLK     |                    |

| PD_09       |             |             | SMC0_A07    | TM0_ACI5    |                    |

| PD_10       |             |             | SMC0_A08    | TM0_ACI4    |                    |

| PD_11       |             |             | SMC0_A09    | TM0_ACI3    |                    |

| PD_12       |             |             | SMC0_A10    | TM0_ACI2    |                    |

| PD_13       |             |             | SMC0_A11    | TM0_ACI1    |                    |

| PD_14       |             |             | SMC0_A12    |             |                    |

| PD_15       |             |             | SMC0_A13    |             |                    |

| Signal Name | Type | Driver<br>Type | Int<br>Term   | Reset<br>Term | Reset<br>Drive | Power<br>Domain | Description<br>and Notes                                                                                                                                                                                                                                                                        |

|-------------|------|----------------|---------------|---------------|----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA_15       | 1/0  | A              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PA Position 15   PWM1 Channel B Low Side   TM0 Timer<br>3   SMC0 Data 7                                                                                                                                                                                                                   |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active.<br>The state of pull-ups can be configured by configuring the<br>PORT_INEN and PADS_PCFG0 registers.                                                                                                                             |

| PB_00       | I/O  | A              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 0   PWM0 Channel D High Side   Embedded<br>Trace Module Clock   SPORT0 Channel A Clock   SMC0 Data 8<br>  CNT0 Count Zero Marker                                                                                                                                              |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active.<br>The state of pull-ups can be configured by configuring the<br>PORT_INEN and PADS_PCFG0 registers.                                                                                                                             |

| PB_01       | I/O  | A              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 1   PWM0 Channel D Low Side   Embedded<br>Trace Module Data 0   SPORT0 Channel A Frame Sync   SMC0<br>Data 9   CNT0 Count Up and Direction                                                                                                                                    |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active.<br>The state of pull-ups can be configured by configuring the<br>PORT_INEN and PADS_PCFG0 registers.                                                                                                                             |

| PB_02       | I/O  | A              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 2   PWM1 Channel D High Side   Embedded<br>Trace Module Data 1   SPORT0 Channel A Data 0   SMC0 Data<br>10   CNT0 Count Down and Gate                                                                                                                                         |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active.<br>The state of pull-ups can be configured by configuring the<br>PORT_INEN and PADS_PCFG0 registers.                                                                                                                             |

| PB_03       | I/O  | A              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 3   PWM1 Channel D Low Side   Embedded<br>Trace Module Data 2   SPORT0 Channel A Data 1   SMC0 Data<br>11   CNT1 Count Zero Marker                                                                                                                                            |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active.<br>The state of pull-ups can be configured by configuring the<br>PORT_INEN and PADS_PCFG0 registers.                                                                                                                             |

| PB_04       | I/O  | A              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 4   PWM2 Sync   UARTO Request to Send  <br>SPORTO Channel A Transmit Data Valid   SMCO Data 12   CNT1<br>Count Up and Direction                                                                                                                                               |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active.<br>The state of pull-ups can be configured by configuring the<br>PORT_INEN and PADS_PCFG0 registers.                                                                                                                             |

| PB_05       | I/O  | A              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 5   PWM2 Trip Input 0   UART0 Clear to Send<br>  TM0 Timer 7   SMC0 Data 13   CNT1 Count Down and Gate<br>Notes: By default, the internal termination pull-up is active.<br>The state of pull-ups can be configured by configuring the<br>PORT_INEN and PADS_PCFG0 registers. |

| PB_06       | I/O  | A              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 6   PWM2 Channel A High Side   TM0<br>Common Clock   SPI1 Slave Select Output 2   SMC0 Data 14<br>Notes: By default, the internal termination pull-up is active.<br>The state of pull-ups can be configured by configuring the<br>PORT_INEN and PADS_PCFG0 registers.         |

| PB_07       | I/O  | A              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 7   PWM2 Channel A Low Side   TM0 Timer 0<br>  SPI1 Slave Select Output 3   SMC0 Data 15   Capture Timer0<br>Input 0                                                                                                                                                          |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active.<br>The state of pull-ups can be configured by configuring the<br>PORT_INEN and PADS_PCFG0 registers.                                                                                                                             |

Table 25. ADSP-CM40xF Designer Quick Reference (Continued)

### TIMING SPECIFICATIONS

Specifications are subject to change without notice.

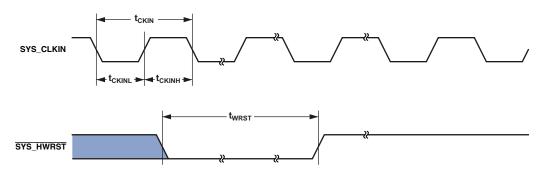

### **Clock and Reset Timing**

Table 34 and Figure 24 describe clock and reset operations related to the clock generation unit (CGU) and reset control unit (RCU). Per the CCLK, SCLK, USBCLK, and OCLK timing specifications in Table 27 Clock Related Operating Conditions, combinations of SYS\_CLKIN and clock multipliers must not select clock rates in excess of the processor's maximum instruction rate.

#### Table 34. Clock and Reset Timing

| Parameter                |                                                                     | Min                  | Max | Unit |

|--------------------------|---------------------------------------------------------------------|----------------------|-----|------|

| Timing Requ              | irements                                                            |                      |     |      |

| <b>f</b> <sub>CKIN</sub> | SYS_CLKIN Frequency (Using a Crystal) <sup>1, 2, 3</sup>            | 20                   | 50  | MHz  |

| <b>f</b> <sub>CKIN</sub> | SYS_CLKIN Frequency (Using a Crystal Oscillator) <sup>1, 2, 3</sup> | 20                   | 60  | MHz  |

| t <sub>CKINL</sub>       | SYS_CLKIN Low Pulse <sup>1</sup>                                    | 6.67                 |     | ns   |

| t <sub>CKINH</sub>       | SYS_CLKIN High Pulse <sup>1</sup>                                   | 6.67                 |     | ns   |

| t <sub>WRST</sub>        | SYS_HWRST Asserted Pulse Width Low <sup>4</sup>                     | $11 \times t_{CKIN}$ |     | ns   |

<sup>1</sup> Applies to PLL bypass mode and PLL nonbypass mode.

<sup>2</sup> The  $t_{CKIN}$  period (see Figure 24) equals  $1/f_{CKIN}$ .

$^3$  If the CGU\_CTL.DF bit is set, the minimum  $f_{\rm CKIN}$  specification is 40 MHz.

<sup>4</sup> Applies after power-up sequence is complete. See Table 35 and Figure 25 for power-up reset timing.

Figure 24. Clock and Reset Timing

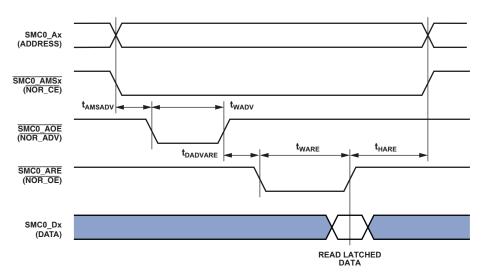

#### Asynchronous Flash Read

Table 37 and Figure 27 show asynchronous flash memory read timing, related to the static memory controller (SMC).

#### Table 37. Asynchronous Flash Read

| Parameter                 |                                                                        | Min                         | Мах | Unit |

|---------------------------|------------------------------------------------------------------------|-----------------------------|-----|------|

| Switching Characteristics |                                                                        |                             |     |      |

| t <sub>AMSADV</sub>       | SMC0_Ax (Address)/SMC0_AMSx Assertion Before SMC0_AOE Low <sup>1</sup> | $PREST \times t_{SCLK} - 2$ |     | ns   |

| t <sub>wadv</sub>         | SMC0_AOE Active Low Width <sup>2</sup>                                 | $RST \times t_{SCLK} - 3$   |     | ns   |

| DADVARE                   | SMC0_ARE Low Delay From SMC0_AOE High <sup>3</sup>                     | $PREAT \times t_{SCLK} - 3$ |     | ns   |

| HARE                      | Output <sup>4</sup> Hold After SMC0_ARE High⁵                          | $RHT \times t_{SCLK} - 2$   |     | ns   |

| t <sub>WARE</sub> 6       | SMC0_ARE Active Low Width <sup>7</sup>                                 | $RAT \times t_{SCLK} - 2$   |     | ns   |

<sup>1</sup> PREST value set using the SMC\_BxETIM.PREST bits.

<sup>2</sup> RST value set using the SMC\_BxTIM.RST bits.

<sup>3</sup> PREAT value set using the SMC\_BxETIM.PREAT bits.

<sup>4</sup> Output signals are SMC0\_Ax, <u>SMC0\_AMS</u>.

<sup>5</sup> RHT value set using the SMC\_BxTIM.RHT bits.

<sup>6</sup> SMC0\_BxCTL.ARDYEN bit = 0.

$^7\,\rm RAT$  value set using the SMC\_BxTIM.RAT bits.

Figure 27. Asynchronous Flash Read

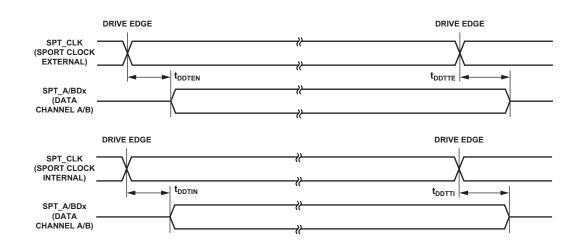

Figure 31. Serial Ports

#### Table 44. Serial Ports—Enable and Three-State

| Parameter          |                                                          | Min | Max | Unit |

|--------------------|----------------------------------------------------------|-----|-----|------|

| Switching Cl       | haracteristics                                           |     |     |      |

| t <sub>DDTEN</sub> | Data Enable from External Transmit SPT_CLK <sup>1</sup>  | 1   |     | ns   |

| t <sub>DDTTE</sub> | Data Disable from External Transmit SPT_CLK <sup>1</sup> |     | 14  | ns   |

| t <sub>DDTIN</sub> | Data Enable from Internal Transmit SPT_CLK <sup>1</sup>  | -1  |     | ns   |

| t <sub>DDTTI</sub> | Data Disable from Internal Transmit SPT_CLK <sup>1</sup> |     | 2.8 | ns   |

<sup>1</sup>Referenced to drive edge.

Figure 32. Serial Ports—Enable and Three-State

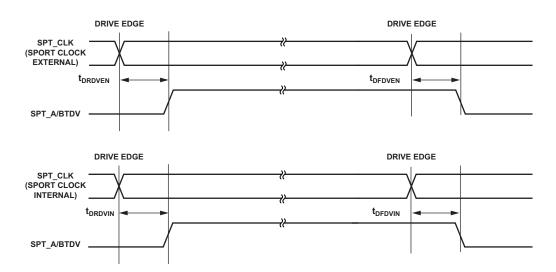

The SPT\_TDV output signal becomes active in SPORT multichannel mode. During transmit slots (enabled with active channel selection registers) the SPT\_TDV is asserted for communication with external devices.

| Table 45. | Serial Ports- | -Transmit Data | Valid (TDV) |

|-----------|---------------|----------------|-------------|

|-----------|---------------|----------------|-------------|

| Parameter           |                                                                         | Min | Max | Unit |

|---------------------|-------------------------------------------------------------------------|-----|-----|------|

| Switching C         | haracteristics                                                          |     |     |      |

| t <sub>DRDVEN</sub> | Data-Valid Enable Delay from Drive Edge of External Clock <sup>1</sup>  | 2   |     | ns   |

| t <sub>DFDVEN</sub> | Data-Valid Disable Delay from Drive Edge of External Clock <sup>1</sup> |     | 14  | ns   |

| t <sub>DRDVIN</sub> | Data-Valid Enable Delay from Drive Edge of Internal Clock <sup>1</sup>  | -1  |     | ns   |

| t <sub>DFDVIN</sub> | Data-Valid Disable Delay from Drive Edge of Internal Clock <sup>1</sup> |     | 3.5 | ns   |

<sup>1</sup>Referenced to drive edge.

Figure 33. Serial Ports—Transmit Data Valid Internal and External Clock

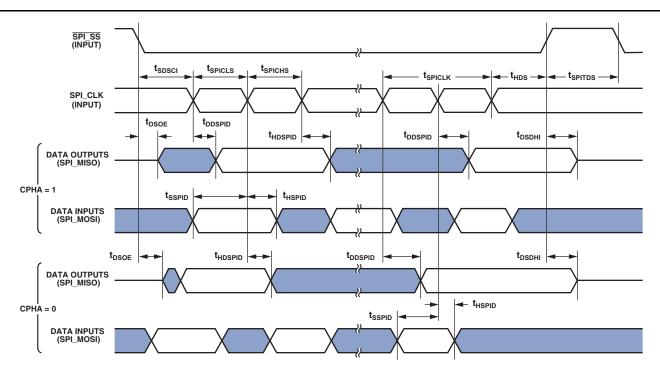

Figure 36. Serial Peripheral Interface (SPI) Port—Slave Timing

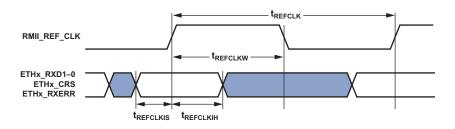

#### 10/100 Ethernet MAC Controller (EMAC) Timing

Table 61 through Table 63 and Figure 52 through Figure 54 describe the 10/100 Ethernet MAC controller operations. Note the externally generated Ethernet MAC clock is called  $f_{REFCLKEXT}$ :

$$t_{REFCLKEXT} = \frac{1}{f_{REFCLKEXT}}$$

#### Table 61. 10/100 Ethernet MAC Controller (EMAC) Timing: RMII Receive Signal

| Parameter <sup>1</sup> |                                                                 | Min                         | Max                         | Unit |

|------------------------|-----------------------------------------------------------------|-----------------------------|-----------------------------|------|

| Timing Requi           | irements                                                        |                             |                             |      |

| t <sub>REFCLK</sub>    | ETHx_REFCLK Period <sup>2</sup>                                 | t <sub>refclkext</sub> – 1% |                             | ns   |

| t <sub>refclkw</sub>   | ETHx_REFCLK Width <sup>2</sup>                                  | $t_{REFCLKEXT} \times 35\%$ | $t_{REFCLKEXT} \times 65\%$ | ns   |

| t <sub>REFCLKIS</sub>  | Rx Input Valid to RMII ETHx_REFCLK Rising Edge (Data In Setup)  | 4                           |                             | ns   |

| t <sub>refclkih</sub>  | RMII ETHx_REFCLK Rising Edge to Rx Input Invalid (Data In Hold) | 2.0                         |                             | ns   |

<sup>1</sup> RMII inputs synchronous to RMII REF\_CLK are ERxDx, RMII CRS\_DV, and ERxER.

<sup>2</sup> This specification indicates the minimum instantaneous width or period that can be tolerated due to duty cycle variation or jitter on the external REF\_CLK. For the external REF\_CLK maximum frequency see the t<sub>REFCLKEXT</sub> specification in Table 27 Clock Related Operating Conditions.

*Figure 52.* 10/100 *Ethernet MAC Controller Timing: RMII Receive Signal*

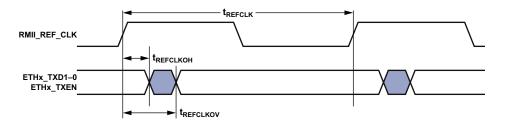

### Table 62. 10/100 Ethernet MAC Controller (EMAC) Timing: RMII Transmit Signal

| Parameter <sup>1</sup> |                                                                         | Min | Max | Unit |

|------------------------|-------------------------------------------------------------------------|-----|-----|------|

| Switching Cha          | aracteristics                                                           |     |     |      |

| t <sub>REFCLKOV</sub>  | RMII ETHx_REFCLK Rising Edge to Transmit Output Valid (Data Out Valid)  |     | 14  | ns   |

| t <sub>REFCLKOH</sub>  | RMII ETHx_REFCLK Rising Edge to Transmit Output Invalid (Data Out Hold) | 2   |     | ns   |

<sup>1</sup> RMII outputs synchronous to RMII REF\_CLK are ETxDx.

Figure 53. 10/100 Ethernet MAC Controller Timing: RMII Transmit Signal

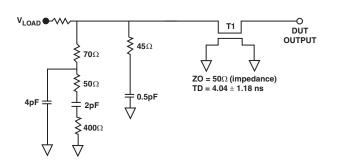

NOTES:

THE WORST CASE TRANSMISSION LINE DELAY IS SHOWN AND CAN BE USED FOR THE OUTPUT TIMING ANALYSIS TO REFELECT THE TRANSMISSION LINE EFFECT AND MUST BE CONSIDERED. THE TRANSMISSION LINE (TD), IS FOR LOAD ONLY AND DOES NOT AFFECT THE DATA SHEET TIMING SPECIFICATIONS.

ANALOG DEVICES RECOMMENDS USING THE IBIS MODEL TIMING FOR A GIVEN SYSTEM REQUIREMENT. IF NECESSARY, A SYSTEM MAY INCORPORATE EXTERNAL DRIVERS TO COMPENSATE FOR ANY TIMING DIFFERENCES.

#### Figure 63. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

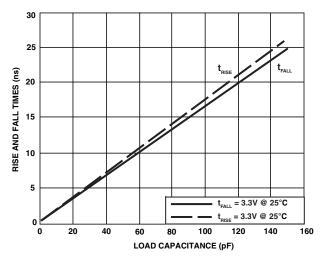

The graph of Figure 64 shows how output rise and fall times vary with capacitance. The delay and hold specifications given should be derated by a factor derived from these figures. The graphs in these figures may not be linear outside the ranges shown.

Figure 64. Driver Type A Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance

### **ENVIRONMENTAL CONDITIONS**

To determine the junction temperature on the application printed circuit board, use the following equation:

$$T_I = T_{CASE} + (\Psi_{IT} \times P_D)$$

where:

$T_I$  = Junction temperature (°C).

$T_{CASE}$  = Case temperature (°C) measured by customer at top center of package.

$\Psi_{JT}$  = From Table 68, Table 69, and Table 70.

$P_D$  = Power dissipation (see Total Power Dissipation (PD) on Page 67 for the method to calculate  $P_D$ ).

| Table 68. | <b>Thermal Characteristics</b> | (120-Lead LQFP) |

|-----------|--------------------------------|-----------------|

|-----------|--------------------------------|-----------------|

| Parameter          | Condition             | Typical | Unit |

|--------------------|-----------------------|---------|------|

| $\theta_{JA}$      | 0 linear m/s air flow | 21.5    | °C/W |

| $\theta_{JA}$      | 1 linear m/s air flow | 19.2    | °C/W |

| $\theta_{JA}$      | 2 linear m/s air flow | 18.4    | °C/W |

| $\theta_{JC}$      |                       | 9.29    | °C/W |

| $\Psi_{ m JT}$     | 0 linear m/s air flow | 0.25    | °C/W |

| $\Psi_{\text{JT}}$ | 1 linear m/s air flow | 0.40    | °C/W |

| $\Psi_{JT}$        | 2 linear m/s air flow | 0.56    | °C/W |

Table 69. Thermal Characteristics (176-Lead LQFP)

| Parameter            | Condition             | Typical | Unit |

|----------------------|-----------------------|---------|------|

| $\theta_{JA}$        | 0 linear m/s air flow | 21.5    | °C/W |

| $\theta_{JA}$        | 1 linear m/s air flow | 19.3    | °C/W |

| $\theta_{JA}$        | 2 linear m/s air flow | 18.5    | °C/W |

| $\theta_{\text{JC}}$ |                       | 9.24    | °C/W |

| $\Psi_{JT}$          | 0 linear m/s air flow | 0.25    | °C/W |

| $\Psi_{JT}$          | 1 linear m/s air flow | 0.37    | °C/W |

| $\Psi_{JT}$          | 2 linear m/s air flow | 0.48    | °C/W |

Table 70. Thermal Characteristics (212-Ball BGA)

| Parameter            | Condition             | Typical | Unit |

|----------------------|-----------------------|---------|------|

| $\theta_{JA}$        | 0 linear m/s air flow | 30.0    | °C/W |

| $\theta_{JA}$        | 1 linear m/s air flow | 27.5    | °C/W |

| $\theta_{JA}$        | 2 linear m/s air flow | 26.5    | °C/W |

| $\theta_{\text{JC}}$ |                       | 9.2     | °C/W |

| $\Psi_{ m JT}$       | 0 linear m/s air flow | 0.15    | °C/W |

| $\Psi_{\text{JT}}$   | 1 linear m/s air flow | 0.24    | °C/W |

| $\Psi_{ m JT}$       | 2 linear m/s air flow | 0.27    | °C/W |