Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                       |

|-------------------------|-----------------------------------------------------------------------|

| Product Status          | Active                                                                |

| Туре                    | Floating Point                                                        |

| Interface               | CAN, Ethernet, I <sup>2</sup> C, SPI, SPORT, UART/USART, USB          |

| Clock Rate              | 240MHz                                                                |

| Non-Volatile Memory     | FLASH (2MB)                                                           |

| On-Chip RAM             | 384kB                                                                 |

| Voltage - I/O           | 3.30V                                                                 |

| Voltage - Core          | 1.20V                                                                 |

| Operating Temperature   | -40°C ~ 105°C (TA)                                                    |

| Mounting Type           | Surface Mount                                                         |

| Package / Case          | 212-LBGA, CSPBGA                                                      |

| Supplier Device Package | 212-CSPBGA (19x19)                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-cm409cbcz-af |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **GENERAL DESCRIPTION**

The ADSP-CM40xF family of mixed-signal control processors is based on the ARM® Cortex-M4™ processor core with floating-point unit operating at frequencies up to 240 MHz and integrating up to 384 kB of SRAM memory, 2 MB of flash memory, accelerators and peripherals optimized for motor control and photo-voltaic (PV) inverter control and an analog module consisting of two 16-bit SAR ADCs and two 12-bit DACs. The ADSP-CM40xF family operates from a single voltage supply (VDD\_EXT/VDD\_ANA), generating its own internal voltage supplies using internal voltage regulators and an external pass transistor.

This family of mixed-signal control processors offers low static power consumption and is produced with a low power and low voltage design methodology, delivering world class processor and ADC performance with lower power consumption.

By integrating a rich set of industry-leading system peripherals and memory (shown in Table 1), the ADSP-CM40xF mixed-signal control processors are the platform of choice for next-generation applications that require RISC programmability, advanced communications and leading-edge signal processing in one integrated package. These applications span a wide array of markets including power/motor control, embedded industrial, instrumentation, medical and consumer.

Each ADSP-CM40xF family member contains the following modules.

- 8 GP timers with PWM output

- 3-phase PWM units with up to 4 output pairs per unit

- 2 CAN modules

- 1 two-wire interface (TWI) module

- 3 UARTs

- 1 ADC controller (ADCC) to control on-chip ADCs

- 1 DAC controller (DACC) to control on-chip DACs

- 4 Sinus Cardinalis (SINC) filter pairs

- 1 harmonic analysis engine (HAE)

- 2 SPI (1 connected to internal SPI flash memory)

- 3 half-SPORTs

- 1 watchdog timer unit

- 3 capture timer units

- 1 cyclic redundancy check (CRC)

Table 1 provides the additional product features shown by model

Table 1. ADSP-CM4 0xF Family Product Features

| Generic                 | ADSP-0            | CM402F            | AC                | SP-CM4            | 03F               | AC                | SP-CM4            | 07F               | ADSP-             | CM408F            | ADSP-CM409F       |

|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Package                 |                   | 12                | 0-Lead LO         | QFP               |                   | 176-Lead LQFP     |                   |                   |                   |                   | 212-Ball BGA      |

| GPIOs                   |                   | 40                |                   |                   |                   |                   | 91                |                   |                   |                   |                   |

| SMC                     | 10                | б-Bit Asyr        | nchronou          | s/5 Addr          | ess               |                   | 16                | -Bit Asyn         | chronous          | /24 Addr          | ess               |

| ADC ENOB (No Averaging) | 1                 | 1+                |                   | 13+               |                   |                   | 11+               |                   |                   | 13                | 3+                |

| ADC Inputs              |                   |                   | 24                |                   |                   |                   |                   | 16                |                   |                   | 24                |

| DAC Outputs             |                   |                   | 2                 |                   |                   |                   |                   | N/A               |                   |                   | 2                 |

| SPORTs                  |                   | 3                 | Half-SPOI         | RTs               |                   |                   |                   | 4 l               | Half-SPOF         | RTs               |                   |

| Ethernet                |                   |                   | N/A               |                   |                   | 1                 | N/A               | N/A               | 1                 | N/A               | 1                 |

| USB                     |                   |                   | N/A               |                   |                   | 1                 | 1                 | N/A               | 1                 | 1                 | 1                 |

| External SPI            |                   |                   | 1                 |                   |                   | 2                 |                   |                   |                   |                   |                   |

| HAE                     |                   |                   |                   |                   |                   |                   | 1                 |                   |                   |                   |                   |

| CAN                     |                   |                   |                   |                   |                   | 2                 | 2                 |                   |                   |                   |                   |

| UART                    |                   |                   |                   |                   |                   | 3                 | 3                 |                   |                   |                   |                   |

| Feature Set Code        | Е                 | F                 | С                 | Е                 | F                 | Α                 | В                 | D                 | Α                 | В                 | Α                 |

| L1 SRAM (kB)            | 128               | 128               | 384               | 128               | 128               | 384               | 384               | 128               | 384               | 384               | 384               |

| Flash (kB)              | 512               | 256               | 2048              | 512               | 256               | 2048              | 2048              | 1024              | 2048              | 2048              | 2048              |

| Core Clock (MHz)        | 150               | 100               | 240               | 150               | 100               | 240               | 240               | 150               | 240               | 240               | 240               |

| Model                   | ADSP-CM402CSWZ-EF | ADSP-CM402CSWZ-FF | ADSP-CM403CSWZ-CF | ADSP-CM403CSWZ-EF | ADSP-CM403CSWZ-FF | ADSP-CM407CSWZ-AF | ADSP-CM407CSWZ-BF | ADSP-CM407CSWZ-DF | ADSP-CM408CSWZ-AF | ADSP-CM408CSWZ-BF | ADSP-CM409CBCZ-AF |

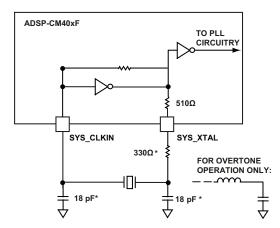

NOTE: VALUES MARKED WITH \* MUST BE CUSTOMIZED, DEPENDING ON THE CRYSTAL AND LAYOUT. ANALYZE CAREFULLY. FOR FREQUENCIES ABOVE 33 MHz, THE SUGGESTED CAPACITOR VALUE OF 18pf should be treated as a maximum, and the suggested resistor value should be reduced to 0  $\Omega_{\rm c}$

Figure 8. External Crystal Connection

The two capacitors and the 330  $\Omega$  series resistor shown in Figure 8 fine tune phase and amplitude of the sine frequency. The capacitor and resistor values shown in Figure 8 are typical values only. The capacitor values are dependent upon the crystal manufacturers' load capacitance recommendations and the PCB physical layout. The resistor value depends on the drive level specified by the crystal manufacturer. The user should verify the customized values based on careful investigations on multiple devices over temperature range.

A third-overtone crystal can be used for frequencies above 25 MHz. The circuit is then modified to ensure crystal operation only at the third overtone by adding a tuned inductor circuit as shown in Figure 8. A design procedure for third-overtone operation is discussed in detail in application note (EE-168) "Using Third Overtone Crystals with the ADSP-218x DSP" (www.analog.com/ee-168).

#### **Oscillator Watchdog**

A programmable oscillator watchdog unit is provided to allow verification of proper startup and harmonic mode of the external crystal. This allows the user to specify the expected frequency of oscillation, and to enable detection of non-oscillation and improper-oscillation faults. These events can be routed to the  $\overline{\rm SYS\_FAULT}$  output pin and/or to cause a reset of the part.

#### **Clock Generation Unit (CGU)**

The clock generation unit (CGU) generates all on-chip clocks and synchronization signals. Multiplication factors are programmed to the PLLs to define the PLLCLK frequency. Programmable values divide the PLLCLK frequency to generate the core clock (CCLK), the system clocks (SCLK), and the output clock (OCLK). This is illustrated in Figure 10 on Page 64.

Writing to the CGU control registers does not affect the behavior of the PLL immediately. Registers are first programmed with a new value, and the PLL logic executes the changes so that it transitions smoothly from the current conditions to the new ones.

SYS\_CLKIN oscillations start when power is applied to the VDD\_EXT pins. The rising edge of SYS\_HWRST can be applied as soon as all voltage supplies are within specifications (see Operating Conditions on Page 64), and SYS\_CLKIN oscillations are stable.

#### Clock Out/External Clock

A SYS\_CLKOUT output pin has programmable options to output divided-down versions of the on-chip clocks, including USB clocks. By default, the SYS\_CLKOUT pin drives a buffered version of the SYS\_CLKIN input. Clock generation faults (for example PLL unlock) may trigger a reset by hardware.

SYS\_CLKOUT can be used to output one of several different clocks used on the processor. The clocks shown in Table 4 can be outputs from SYS\_CLKOUT.

Table 4. SYS\_CLKOUT Source and Divider Options

| Clock Source        | Divider                     |

|---------------------|-----------------------------|

| CCLK (Core Clock)   | By 4                        |

| OCLK (Output Clock) | Programmable                |

| USBCLK              | Programmable                |

| CLKBUF              | None, direct from SYS_CLKIN |

#### **Power Management**

As shown in Table 5 and Figure 4 on Page 6, the processor requires three different power domains, VDD\_INT, VDD\_EXT, and VDD\_ANA. By isolating the internal logic of the processor into its own power domain, separate from other I/O, the processor can take advantage of dynamic power management without affecting the other I/O devices. There are no sequencing requirements for the various power domains, but all domains must be powered according to the appropriate Specifications table for processor operating conditions; even if the feature/peripheral is not used.

The dynamic power management feature of the processor allows the processor's core clock frequency ( $f_{\text{CCLK}}$ ) to be dynamically controlled.

**Table 5. Power Domains**

| Power Domain       | V <sub>DD</sub> Range |

|--------------------|-----------------------|

| All Internal Logic | $V_{DD\_INT}$         |

| Digital I/O        | $V_{DD\_EXT}$         |

| Analog             | $V_{DD\_ANA}$         |

The power dissipated by a processor is largely a function of its clock frequency and the square of the operating voltage. For example, reducing the clock frequency by 25% results in a 25% reduction in dynamic power dissipation. For more information on power pins, see Operating Conditions on Page 64.

Table 6. ADSP-CM40xF Detailed Signal Description (Continued)

| Signal Name | Direction | Description                                                                                                                                                                                                                                                                                  |

|-------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB_ID      | Input     | <b>USB OTG ID.</b> Senses whether the controller is a host or device. This signal is pulled low when an A-type plug is sensed (signifying that the USB controller is the A device), but the input is high when a B-type plug is sensed (signifying that the USB controller is the B device). |

| USB_VBC     | Output    | <b>USB VBUS Control.</b> Controls an external voltage source to supply VBUS when in host mode. May be configured as open drain. Polarity is configurable as well.                                                                                                                            |

| USB_VBUS    | I/O       | USB Bus Voltage. Connects to bus voltage in host and device modes.                                                                                                                                                                                                                           |

| VREFn       | I/O       | <b>Voltage Reference for ADC.</b> When internal reference is selected for ADC, the VREF pin is used for connecting bypass caps. When external reference is selected, an external reference device should be connected to these pins to supply the external reference voltage. n=0,1.         |

| VREG_BASE   | Output    | <b>Voltage Regulator Base Node.</b> Connected to Base of PNP transistor when using internal VDD_INT reference.                                                                                                                                                                               |

### ADSP-CM402F/ADSP-CM403F GPIO MULTIPLEXING FOR 120-LEAD LQFP

Table 8 through Table 10 identify the pin functions that are multiplexed on the general-purpose I/O pins of the 120-lead LQFP package.

Table 8. Signal Multiplexing for Port A (120-Lead LQFP)

| Signal Name | Multiplexed<br>Function 0 | Multiplexed<br>Function 1 | Multiplexed<br>Function 2 | Multiplexed<br>Function 3 | Multiplexed<br>Function Input Tap |

|-------------|---------------------------|---------------------------|---------------------------|---------------------------|-----------------------------------|

| PA_00       | PWM0_SYNC                 |                           | SPT1_ACLK                 |                           |                                   |

| PA_01       | PWM0_TRIP0                |                           | SPT1_AFS                  |                           |                                   |

| PA_02       | PWM0_AH                   |                           | SPT1_AD0                  |                           |                                   |

| PA_03       | PWM0_AL                   |                           | SPT1_AD1                  |                           |                                   |

| PA_04       | PWM0_BH                   |                           | SPT1_BCLK                 |                           |                                   |

| PA_05       | PWM0_BL                   |                           | SPT1_BFS                  |                           |                                   |

| PA_06       | PWM0_CH                   |                           | SPT1_BD0                  |                           |                                   |

| PA_07       | PWM0_CL                   | SMC0_AMS2                 | SPT1_BD1                  |                           |                                   |

| PA_08       | PWM1_CH                   |                           | SMC0_D00                  |                           | TM0_ACLK5                         |

| PA_09       | PWM1_CL                   |                           | SMC0_D01                  |                           | TM0_ACLK4                         |

| PA_10       | PWM1_SYNC                 |                           | SMC0_D02                  |                           | TM0_ACLK3                         |

| PA_11       | PWM1_TRIP0                | UART1_CTS                 | SMC0_D03                  |                           | TM0_ACLK2                         |

| PA_12       | PWM1_AH                   | TM0_TMR4                  | SMC0_D04                  |                           |                                   |

| PA_13       | PWM1_AL                   | TM0_TMR5                  | SMC0_D05                  |                           |                                   |

| PA_14       | PWM1_BH                   | TM0_TMR6                  | SMC0_D06                  |                           |                                   |

| PA_15       | PWM1_BL                   | TM0_TMR3                  | SMC0_D07                  |                           |                                   |

Table 9. Signal Multiplexing for Port B (120-Lead LQFP)

| Signal Name | Multiplexed<br>Function 0 | Multiplexed<br>Function 1 | Multiplexed<br>Function 2 | Multiplexed<br>Function 3 | Multiplexed<br>Function Input Tap |

|-------------|---------------------------|---------------------------|---------------------------|---------------------------|-----------------------------------|

| PB_00       | PWM0_DH                   | TRACE_CLK                 | SPT0_ACLK                 | SMC0_D08                  | CNT0_ZM                           |

| PB_01       | PWM0_DL                   | TRACE_D00                 | SPT0_AFS                  | SMC0_D09                  | CNT0_UD                           |

| PB_02       | PWM1_DH                   | TRACE_D01                 | SPT0_AD0                  | SMC0_D10                  | CNT0_DG                           |

| PB_03       | PWM1_DL                   | TRACE_D02                 | SPT0_AD1                  | SMC0_D11                  | CNT1_ZM                           |

| PB_04       | PWM2_SYNC                 | UARTO_RTS                 | SPT0_ATDV                 | SMC0_D12                  | CNT1_UD                           |

| PB_05       | PWM2_TRIP0                | UARTO_CTS                 | TM0_TMR7                  | SMC0_D13                  | CNT1_DG                           |

| PB_06       | PWM2_AH                   | TM0_CLK                   |                           | SMC0_D14                  |                                   |

| PB_07       | PWM2_AL                   | TM0_TMR0                  |                           | SMC0_D15                  | CPTMR0_IN0                        |

| PB_08       | PWM2_BH                   | TM0_TMR1                  | UART1_RX                  | SMC0_ARDY                 | TM0_ACI2/<br>CPTMR0_IN1           |

| PB_09       | PWM2_BL                   | TM0_TMR2                  | UART1_TX                  | SMC0_ARE                  | CPTMR0_IN2                        |

| PB_10       | SINC0_CLK0                | SPI0_D2                   | CAN1_RX                   | SMC0_AWE                  | TM0_ACI1                          |

| PB_11       | SINC0_D0                  | SPI0_D3                   | CAN1_TX                   | SMC0_AMS0                 | TM0_ACLK1                         |

| PB_12       | SINC0_D1                  |                           | UART2_RX                  | SMC0_AOE                  | TM0_ACI3                          |

| PB_13       | SINC0_D2                  | CNT0_OUTA                 | SPI0_SEL2                 | SMC0_A01                  | TM0_ACLK0/<br>SYS_DSWAKE3         |

| PB_14       | SINC0_D3                  | CNT0_OUTB                 | SPI0_SEL3                 | SMC0_A02                  | SPIO_SS/<br>SYS_DSWAKE2           |

| PB_15       | CAN0_RX                   | SPT1_ATDV                 | UART1_RX                  | SMC0_A03                  | TM0_ACI4                          |

Table 11. ADSP-CM407F/ADSP-CM408F 176-Lead LQFP Signal Descriptions (Continued)

| Signal Name  | Description                        | Port      | Pin Name       |

|--------------|------------------------------------|-----------|----------------|

| SMC0_A06     | SMC0 Address 6                     | D         | PD_08          |

| SMC0_A07     | SMC0 Address 7                     | D         | PD_09          |

| SMC0_A08     | SMC0 Address 8                     | D         | PD_10          |

| SMC0_A09     | SMC0 Address 9                     | D         | PD_11          |

| SMC0_A10     | SMC0 Address 10                    | D         | PD_12          |

| SMC0_A11     | SMC0 Address 11                    | D         | PD_13          |

| SMC0_A12     | SMC0 Address 12                    | D         | PD_14          |

| <br>SMC0_A13 | SMC0 Address 13                    | D         | PD_15          |

| SMC0_A14     | SMC0 Address 14                    | E         | PE_00          |

| SMC0_A15     | SMC0 Address 15                    | E         | PE_01          |

| SMC0_A16     | SMC0 Address 16                    | E         | PE_02          |

| SMC0_A17     | SMC0 Address 17                    | E         | PE_03          |

| SMC0_A18     | SMC0 Address 18                    | E         | PE_04          |

| SMC0_A19     | SMC0 Address 19                    | E         | PE_05          |

|              | SMC0 Address 20                    | E         | PE_06          |

| SMC0_A20     | SMC0 Address 21                    | E         | PE_07          |

| SMC0_A21     | SMC0 Address 21<br>SMC0 Address 22 | E         | PE_07<br>PE_08 |

| SMC0_A22     |                                    | E         |                |

| SMC0_A23     | SMC0 Address 23                    |           | PE_09          |

| SMC0_A24     | SMC0 Address 24                    | E         | PE_11          |

| SMC0_ABE0    | SMC0 Byte Enable 0                 | F         | PF_10          |

| SMC0_ABE1    | SMC0 Byte Enable 1                 | F         | PF_02          |

| SMC0_AMS0    | SMC0 Memory Select 0               | В         | PB_11          |

| SMC0_AMS0    | SMC0 Memory Select 0               | Not Muxed | SMC0_AMS0      |

| SMC0_AMS1    | SMC0 Memory Select 1               | E         | PE_10          |

| SMC0_AMS2    | SMC0 Memory Select 2               | Α         | PA_07          |

| SMC0_AMS3    | SMC0 Memory Select 3               | C         | PC_11          |

| SMC0_AOE     | SMC0 Output Enable                 | В         | PB_12          |

| SMC0_AOE     | SMC0 Output Enable                 | F         | PF_03          |

| SMC0_ARDY    | SMC0 Asynchronous Ready            | В         | PB_08          |

| SMC0_ARDY    | SMC0 Asynchronous Ready            | F         | PF_04          |

| SMC0_ARE     | SMC0 Read Enable                   | В         | PB_09          |

| SMC0_ARE     | SMC0 Read Enable                   | Not Muxed | SMC0_ARE       |

| SMC0_AWE     | SMC0 Write Enable                  | В         | PB_10          |

| SMC0_AWE     | SMC0 Write Enable                  | Not Muxed | SMC0_AWE       |

| SMC0_D00     | SMC0 Data 0                        | Α         | PA_08          |

| SMC0_D00     | SMC0 Data 0                        | C         | PC_08          |

| SMC0_D01     | SMC0 Data 1                        | Α         | PA_09          |

| SMC0_D01     | SMC0 Data 1                        | С         | PC_09          |

| SMC0_D02     | SMC0 Data 2                        | A         | PA_10          |

| SMC0_D02     | SMC0 Data 2                        | С         | PC_10          |

| SMC0_D03     | SMC0 Data 3                        | A         | PA_11          |

| SMC0_D03     | SMC0 Data 3                        | c         | PC_11          |

| SMC0_D04     | SMC0 Data 4                        | А         | PA_12          |

| SMC0_D04     | SMC0 Data 4                        | c         | PC_12          |

| SMC0_D05     | SMC0 Data 5                        | A         | PA_13          |

| SMC0_D05     | SMC0 Data 5                        | C         | PC_13          |

Table 11. ADSP-CM407F/ADSP-CM408F 176-Lead LQFP Signal Descriptions (Continued)

| Signal Name | Description                          | Port | Pin Name |

|-------------|--------------------------------------|------|----------|

| SMC0_D06    | SMC0 Data 6                          | A    | PA_14    |

| SMC0_D06    | SMC0 Data 6                          | С    | PC_14    |

| SMC0_D07    | SMC0 Data 7                          | Α    | PA_15    |

| SMC0_D07    | SMC0 Data 7                          | С    | PC_15    |

| SMC0_D08    | SMC0 Data 8                          | В    | PB_00    |

| SMC0_D08    | SMC0 Data 8                          | D    | PD_00    |

| SMC0_D09    | SMC0 Data 9                          | В    | PB_01    |

| SMC0_D09    | SMC0 Data 9                          | D    | PD_01    |

| SMC0_D10    | SMC0 Data 10                         | В    | PB_02    |

| SMC0_D10    | SMC0 Data 10                         | D    | PD_02    |

| SMC0_D11    | SMC0 Data 11                         | В    | PB_03    |

| SMC0_D11    | SMC0 Data 11                         | D    | PD_03    |

| SMC0_D12    | SMC0 Data 12                         | В    | PB_04    |

| SMC0_D12    | SMC0 Data 12                         | D    | PD_04    |

| SMC0_D13    | SMC0 Data 13                         | В    | PB_05    |

| SMC0_D13    | SMC0 Data 13                         | D    | PD_05    |

| SMC0_D14    | SMC0 Data 14                         | В    | PB_06    |

| SMC0_D14    | SMC0 Data 14                         | D    | PD_06    |

| SMC0_D15    | SMC0 Data 15                         | В    | PB_07    |

| SMC0_D15    | SMC0 Data 15                         | D    | PD_07    |

| SPI0_CLK    | SPI0 Clock                           | С    | PC_03    |

| SPI0_D2     | SPI0 Data 2                          | В    | PB_10    |

| SPI0_D3     | SPI0 Data 3                          | В    | PB_11    |

| SPI0_MISO   | SPI0 Master In, Slave Out            | С    | PC_04    |

| SPI0_MOSI   | SPI0 Master Out, Slave In            | С    | PC_05    |

| SPI0_RDY    | SPI0 Ready                           | С    | PC_02    |

| SPI0_SEL1   | SPI0 Slave Select Output 1           | С    | PC_06    |

| SPI0_SEL2   | SPI0 Slave Select Output 2           | В    | PB_13    |

| SPI0_SEL3   | SPI0 Slave Select Output 3           | В    | PB_14    |

| SPIO_SS     | SPI0 Slave Select Input              | В    | PB_14    |

| SPI1_CLK    | SPI1 Clock                           | С    | PC_12    |

| SPI1_MISO   | SPI1 Master In, Slave Out            | С    | PC_13    |

| SPI1_MOSI   | SPI1 Master Out, Slave In            | С    | PC_14    |

| SPI1_SEL1   | SPI1 Slave Select Output 1           | С    | PC_15    |

| SPI1_SEL2   | SPI1 Slave Select Output 2           | В    | PB_06    |

| SPI1_SEL3   | SPI1 Slave Select Output 3           | В    | PB_07    |

| SPI1_SS     | SPI1 Slave Select Input              | C    | PC_15    |

| SPT0_ACLK   | SPORTO Channel A Clock               | В    | PB_00    |

| SPT0_ACLK   | SPORT0 Channel A Clock               | E    | PE_00    |

| SPT0_AD0    | SPORT0 Channel A Data 0              | В    | PB_02    |

| SPT0_AD0    | SPORT0 Channel A Data 0              | E    | PE_02    |

| SPT0_AD1    | SPORT0 Channel A Data 1              | В    | PB_03    |

| SPT0_AD1    | SPORT0 Channel A Data 1              | E    | PE_03    |

| SPT0_AFS    | SPORT0 Channel A Frame Sync          | В    | PB_01    |

| SPT0_AFS    | SPORT0 Channel A Frame Sync          | E    | PE_01    |

| SPT0_ATDV   | SPORTO Channel A Transmit Data Valid | В    | PB_04    |

Table 18. ADSP-CM409F 212-Ball BGA Signal Descriptions (Continued)

| Signal Name             | Description                          | Port      | Pin Name   |

|-------------------------|--------------------------------------|-----------|------------|

| SPT0_AD1                | SPORT0 Channel A Data 1              | В         | PB_03      |

| SPT0_AD1                | SPORT0 Channel A Data 1              | E         | PE_03      |

| SPTO_AFS                | SPORT0 Channel A Frame Sync          | В         | PB_01      |

| SPT0_AFS                | SPORTO Channel A Frame Sync          | E         | PE_01      |

| SPT0_ATDV               | SPORTO Channel A Transmit Data Valid | В         | PB_04      |

| SPT0_BCLK               | SPORTO Channel B Clock               | С         | PC_08      |

| SPT0_BD0                | SPORT0 Channel B Data 0              | С         | PC_10      |

| SPT0_BD1                | SPORT0 Channel B Data 1              | С         | PC_11      |

| SPT0_BFS                | SPORTO Channel B Frame Sync          | С         | PC_09      |

| SPT0_BTDV               | SPORTO Channel B Transmit Data Valid | В         | PB_12      |

| SPT1_ACLK               | SPORT1 Channel A Clock               | A         | PA_00      |

| _<br>SPT1_AD0           | SPORT1 Channel A Data 0              | A         | PA_02      |

| SPT1_AD1                | SPORT1 Channel A Data 1              | A         | PA_03      |

| SPT1_AFS                | SPORT1 Channel A Frame Sync          | A         | PA_01      |

| SPT1_ATDV               | SPORT1 Channel A Transmit Data Valid | В         | PB_15      |

| SPT1_BCLK               | SPORT1 Channel B Clock               | A         | PA_04      |

| SPT1_BD0                | SPORT1 Channel B Data 0              | A         | PA_06      |

| SPT1_BD0<br>SPT1_BD1    | SPORT1 Channel B Data 1              | A         | PA_07      |

| SPT1_BFS                | SPORT1 Channel B Frame Sync          | A         | PA_05      |

| SPT1_BTDV               | SPORT1 Channel B Transmit Data Valid | C         | PC_00      |

| SYS_BMODE0              | Boot Mode Control 0                  | Not Muxed | SYS_BMODE0 |

| SYS_BMODE0              | Boot Mode Control 1                  | Not Muxed | SYS_BMODE1 |

|                         | Clock/Crystal Input                  | Not Muxed | SYS_CLKIN  |

| SYS_CLKIN<br>SYS_CLKOUT | Processor Clock Output               | Not Muxed | SYS_CLKOUT |

| _                       | Deep Sleep Wake-up 0                 | C         | PC_06      |

| SYS_DSWAKE0             |                                      | C         |            |

| SYS_DSWAKE1             | Deep Sleep Wake-up 1                 | В         | PC_07      |

| SYS_DSWAKE2             | Deep Sleep Wake-up 2                 | В         | PB_14      |

| SYS_DSWAKE3             | Deep Sleep Wake-up 3                 | _         | PB_13      |

| SYS_FAULT               | System Fault Output                  | Not Muxed | SYS_FAULT  |

| SYS_HWRST               | Processor Hardware Reset Control     | Not Muxed | SYS_HWRST  |

| SYS_NMI                 | Nonmaskable Interrupt                | Not Muxed | SYS_NMI    |

| SYS_RESOUT              | Reset Output                         | Not Muxed | SYS_RESOUT |

| SYS_XTAL                | Crystal Output                       | Not Muxed | SYS_XTAL   |

| ΓM0_ACI1                | TIMERO Alternate Capture Input 1     | В         | PB_10      |

| ΓM0_ACI1                | TIMERO Alternate Capture Input 1     | D         | PD_13      |

| TM0_ACI2                | TIMERO Alternate Capture Input 2     | В         | PB_08      |

| ΓM0_ACI2                | TIMERO Alternate Capture Input 2     | D         | PD_12      |

| ΓM0_ACI3                | TIMERO Alternate Capture Input 3     | В         | PB_12      |

| ΓM0_ACI3                | TIMERO Alternate Capture Input 3     | D         | PD_11      |

| ΓM0_ACI4                | TIMERO Alternate Capture Input 4     | В         | PB_15      |

| TM0_ACI4                | TIMERO Alternate Capture Input 4     | D         | PD_10      |

| TM0_ACI5                | TIMERO Alternate Capture Input 5     | C         | PC_01      |

| TM0_ACI5                | TIMERO Alternate Capture Input 5     | D         | PD_09      |

| TM0_ACLK0               | TIMER0 Alternate Clock 0             | В         | PB_13      |

| TM0_ACLK1               | TIMERO Alternate Clock 1             | В         | PB_11      |

| TM0_ACLK2               | TIMERO Alternate Clock 2             | Α         | PA_11      |

Table 25. ADSP-CM40xF Designer Quick Reference (Continued)

| Signal Name | Туре | Driver<br>Type | Int<br>Term   | Reset<br>Term | Reset<br>Drive | Power<br>Domain | Description and Notes                                                                                                                                                                |

|-------------|------|----------------|---------------|---------------|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA_15       | I/O  | А              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PA Position 15   PWM1 Channel B Low Side   TM0 Timer 3   SMC0 Data 7                                                                                                           |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.                        |

| PB_00       | I/O  | А              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 0   PWM0 Channel D High Side   Embedded<br>Trace Module Clock   SPORT0 Channel A Clock   SMC0 Data 8<br>  CNT0 Count Zero Marker                                   |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.                        |

| PB_01       | I/O  | А              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 1   PWM0 Channel D Low Side   Embedded Trace Module Data 0   SPORT0 Channel A Frame Sync   SMC0 Data 9   CNT0 Count Up and Direction                               |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.                        |

| PB_02       | I/O  | А              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 2   PWM1 Channel D High Side   Embedded Trace Module Data 1   SPORT0 Channel A Data 0   SMC0 Data 10   CNT0 Count Down and Gate                                    |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.                        |

| PB_03       | I/O  | А              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 3   PWM1 Channel D Low Side   Embedded<br>Trace Module Data 2   SPORT0 Channel A Data 1   SMC0 Data<br>11   CNT1 Count Zero Marker                                 |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.                        |

| PB_04       | I/O  | А              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 4   PWM2 Sync   UARTO Request to Send   SPORTO Channel A Transmit Data Valid   SMC0 Data 12   CNT1 Count Up and Direction                                          |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.                        |

| PB_05       | I/O  | А              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 5   PWM2 Trip Input 0   UARTO Clear to Send   TM0 Timer 7   SMC0 Data 13   CNT1 Count Down and Gate Notes: By default, the internal termination pull-up is active. |

|             |      |                |               |               |                |                 | The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.                                                                                       |

| PB_06       | I/O  | Α              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 6   PWM2 Channel A High Side   TM0<br>Common Clock   SPI1 Slave Select Output 2   SMC0 Data 14                                                                     |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.                        |

| PB_07       | I/O  | А              | pu or<br>none | pu            | none           | VDD_EXT         | Desc: PB Position 7   PWM2 Channel A Low Side   TM0 Timer 0   SPI1 Slave Select Output 3   SMC0 Data 15   Capture Timer0 Input 0                                                     |

|             |      |                |               |               |                |                 | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.                        |

Table 25. ADSP-CM40xF Designer Quick Reference (Continued)

|             |      | Driver | Int           | Reset | Reset | Power   | Description                                                                                                                                                          |

|-------------|------|--------|---------------|-------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Type | Type   | Term          | Term  | Drive | Domain  | and Notes                                                                                                                                                            |

| PB_08       | I/O  | A      | pu or<br>none | pu    | none  | VDD_EXT | Desc: PB Position 8   PWM2 Channel B High Side   TM0 Timer 1   UART1 Receive   SMC0 Asynchronous Ready   TM0 Timer2 Alternate Capture Input   Capture Timer0 Input 1 |

|             |      |        |               |       |       |         | Notes: By default, the internal termination pull-up is active.                                                                                                       |

|             |      |        |               |       |       |         | The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.                                                                       |

| PB_09       | I/O  | Α      | pu or<br>none | pu    | none  | VDD_EXT | Desc: PB Position 9   PWM2 Channel B Low Side   TM0 Timer 2   UART1 Transmit   SMC0 Read Enable   Capture Timer 0 Input 2                                            |

|             |      |        |               |       |       |         | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.        |

| PB_10       | I/O  | A      | pu or<br>none | pu    | none  | VDD_EXT | Desc: PB Position 10   SINCO Clock 0   SPI0 Data 2   CAN1<br>Receive   SMC0 Write Enable   TM0 Timer1 Alternate Capture<br>Input                                     |

|             |      |        |               |       |       |         | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.        |

| PB_11       | I/O  | A      | pu or<br>none | pu    | none  | VDD_EXT | Desc: PB Position 11   SINC0 Data 0   SPI0 Data 3   CAN1<br>Transmit   SMC0 Memory Select 0   TM0 Timer1 Alternate<br>Clock                                          |

|             |      |        |               |       |       |         | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.        |

| PB_12       | I/O  | A      | pu or<br>none | pu    | none  | VDD_EXT | Desc: PB Position 12   SINCO Data 1   SPORTO Channel B<br>Transmit Data Valid   UART2 Receive   SMCO Output Enable  <br>TMO Timer3 Alternate Capture Input           |

|             |      |        |               |       |       |         | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.        |

| PB_13       | I/O  | A      | pu or<br>none | pu    | none  | VDD_EXT | Desc: PB Position 13   SINCO Data 2   CNTO Output Divider A   SPIO Slave Select Output 2   SMCO Address 1   SYSO Deep Sleep Wakeup 3   TMO TimerO Alternate Clock    |

|             |      |        |               |       |       |         | Notes: By default, the internal termination pull-up is active.<br>The state of pull-ups can be configured by configuring the                                         |

|             |      |        |               |       |       |         | PORT_INEN and PADS_PCFG0 registers.                                                                                                                                  |

| PB_14       | I/O  | A      | pu or<br>none | pu    | none  | VDD_EXT | Desc: PB Position 14   SINCO Data 3   CNTO Output Divider B   SPIO Slave Select Output 3   SMCO Address 2   SYSO Deep Sleep Wakeup 2   SPIO Slave Select Input       |

|             |      |        |               |       |       |         | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.        |

| PB_15       | I/O  | A      | pu or<br>none | pu    | none  | VDD_EXT | Desc: PB Position 15   CANO Receive   SPORT1 Channel A Transmit Data Valid   UART1 Receive   SMC0 Address 3   TM0 Timer4 Alternate Capture Input                     |

|             |      |        |               |       |       |         | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.        |

| PC_00       | I/O  | Α      | pu or<br>none | pu    | none  | VDD_EXT | Desc: PC Position 0   CAN0 Transmit   SPORT1 Channel B<br>Transmit Data Valid   UART1 Transmit   SMC0 Address 4                                                      |

|             |      |        |               |       |       |         | Notes: By default, the internal termination pull-up is active. The state of pull-ups can be configured by configuring the PORT_INEN and PADS_PCFG0 registers.        |

Table 27. Clock Related Operating Conditions

| Parameter                   |                                                                          | Restriction                                 | Min | Тур | Max | Unit |

|-----------------------------|--------------------------------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

| f <sub>PLLCLK</sub>         | PLL Clock Frequency                                                      |                                             | 250 |     | 960 | MHz  |

| $f_{\text{CCLK}}$           | Core Clock Frequency                                                     | $f_{CCLK} \ge f_{SCLK}$                     |     |     | 240 | MHz  |

| $f_{\text{SCLK}}$           | SCLK Frequency <sup>1, 2</sup>                                           |                                             |     |     | 100 | MHz  |

| $f_{\text{USBCLK}}$         | USBCLK Frequency <sup>3, 4</sup>                                         | $f_{SCLK} \ge f_{USBCLK}$                   |     |     | 60  | MHz  |

| $f_{OCLK}$                  | Output Clock Frequency                                                   |                                             |     |     | 50  | MHz  |

| $f_{TCK}$                   | JTG_TCK Frequency                                                        | $f_{TCK} \le f_{SCLK}/2$                    |     |     | 50  | MHz  |

| f <sub>SYS_CLKOUTJ</sub>    | SYS_CLKOUT Period Jitter <sup>5, 6</sup>                                 |                                             |     | ±1  |     | %    |

| f <sub>ADCC_ACLK_PROG</sub> | Programmed ADCC ADC0 (A) Clock                                           |                                             |     |     | 50  | MHz  |

| f <sub>ADCC_BCLK_PROG</sub> | Programmed ADCC ADC1 (B) Clock                                           |                                             |     |     | 50  | MHz  |

| f <sub>DACC_ACLK_PROG</sub> | Programmed DACC DAC0 (A) Clock                                           |                                             |     |     | 50  | MHz  |

| f <sub>DACC_BCLK_PROG</sub> | Programmed DACC DAC1 (B) Clock                                           |                                             |     |     | 50  | MHz  |

| f <sub>SPTCLKPROG</sub>     | Programmed SPT Clock When Transmitting<br>Data and Frame Sync            |                                             |     |     | 50  | MHz  |

| f <sub>SPTCLKPROG</sub>     | Programmed SPT Clock When Receiving<br>Data and Frame Sync               |                                             |     |     | 50  | MHz  |

| f <sub>SPTCLKEXT</sub>      | External SPT Clock When Transmitting Data and Frame Sync <sup>7, 8</sup> | $f_{SPTCLKEXT} \leq f_{SCLK}$               |     |     | 50  | MHz  |

| f <sub>SPTCLKEXT</sub>      | External SPT Clock When Receiving Data and Frame Sync <sup>7, 8</sup>    | $f_{SPTCLKEXT} \leq f_{SCLK}$               |     |     | 50  | MHz  |

| f <sub>SPICLKPROG</sub>     | Programmed SPI Clock When Transmitting Data <sup>7, 8</sup>              |                                             |     |     | 50  | MHz  |

| f <sub>SPICLKPROG</sub>     | Programmed SPI Clock When Receiving Data                                 |                                             |     |     | 50  | MHz  |

| f <sub>SPICLKEXT</sub>      | External SPI Clock When Transmitting Data <sup>7, 8</sup>                | $f_{\text{SPICLKEXT}} \leq f_{\text{SCLK}}$ |     |     | 50  | MHz  |

| f <sub>SPICLKEXT</sub>      | External SPI Clock When Receiving Data <sup>7, 8</sup>                   | $f_{SPICLKEXT} \leq f_{SCLK}$               |     |     | 50  | MHz  |

| f <sub>TMRCLKEXT</sub>      | External TMR Clock                                                       | $f_{TMRCLKEXT} \leq f_{SCLK}/4$             |     |     | 25  | MHz  |

| f <sub>SINCLKPROG</sub>     | Programmed SINC Clock                                                    | $f_{SINCLKPROG} \leq f_{SCLK}/4$            |     |     | 20  | MHz  |

| f <sub>REFCLKEXT</sub>      | External Ethernet MAC Clock                                              | $f_{REFCLKEXT} \leq f_{SCLK}$               |     |     | 50  | MHz  |

<sup>&</sup>lt;sup>1</sup> Supporting documents may use either SCLK or SYSCLK when referring to system clock frequency.

<sup>&</sup>lt;sup>2</sup> SCLK is the clock for the system logic. Documentation may interchangeably refer to this clock as SYSCLK, for example, for PLL configuration MMR accesses.

<sup>&</sup>lt;sup>3</sup> Supporting documents may use either USBCLK or DCLK when referring to USB clock frequency.

<sup>&</sup>lt;sup>4</sup> USBCLK is the clock for the USB peripheral. Documentation may interchangeably refer to this clock as DCLK, for example, for PLL configuration MMR accesses.

<sup>&</sup>lt;sup>5</sup> SYS\_CLKOUT jitter is dependent on the application system design including pin switching activity, board layout, and the jitter characteristics of the SYS\_CLKIN source. Due to the dependency on these factors the measured jitter may be higher or lower than this specification for each end application.

$<sup>^6\,\</sup>mathrm{The}$  value in the Typ field is the percentage of the SYS\_CLKOUT period.

<sup>&</sup>lt;sup>7</sup> The maximum achievable frequency for any peripheral in external clock mode is dependent on being able to meet the setup and hold times in the ac timing specifications for that peripheral.

$<sup>^8</sup>$  The peripheral external clock frequency must also be less than or equal to  $f_{SCLK}$  that clocks the peripheral.

#### **Total Power Dissipation (PD)**

Total power dissipation is the sum of power dissipation for each  $V_{\rm DD}$  domain, shown in the following equation.

$$P_D = P_{D\_INT} + P_{D\_ANA} + P_{D\_EXT}$$

where:

$P_{D\_INT} = V_{DD\_INT} \times I_{DD\_INT}$  – Internal voltage domain power dissipation

$P_{D\_ANA} = V_{DD\_ANA} \times I_{DD\_ANA} - Analog~3.3~V~voltage~domain~power~dissipation$

$P_{D\_EXT} = V_{DD\_EXT} \times I_{DD\_EXT} - Digital 3.3 \ V$  voltage domain power dissipation

#### Total External Power Dissipation (IDD\_EXT)

There are three different items that contribute to the digital 3.3 V supply power dissipation: I/O switching, flash subsystem, and analog subsystem (digital portion), shown in the following equation.

$I_{DDEXT\_TOT} = I_{DDEXT\_IO} + I_{DDEXT\_FLASH} + I_{DDEXT\_ANA}$

where:

$I_{DDEXT\_IO/ANA} \text{ (mA)} = \Sigma \{V_{DD\_EXT} \times C_L f/2 \times (O \times TR) \times U\} - I/O$  switching current

The I/O switching current is the sum of the switching current for all of the enabled peripherals. For each peripheral the capacitive load of each pin in Farads ( $C_L$ ), operating frequency in MHz (f), number of output pins (O), toggle ratio for each pin (TR), and peripheral utilization (U) are considered.

$I_{DDEXT\ FLASH}$  (mA) = 25 mA – maximum flash subsystem current

#### Total Processor Internal Power Dissipation (IDD\_INT)

Many operating conditions affect power dissipation, including temperature, voltage, operating frequency, and processor activity. Total internal power dissipation for the processor subsystem has two components:

- 1. Static, including leakage current

- 2. Dynamic, due to transistors switching characteristics for each clock domain. Application-dependent currents, clock currents, and data transmission currents all contribute to dynamic power dissipation.

The following equation describes the internal current consumption.

$$\begin{split} I_{DDINT\_TOT} = I_{DDINT\_CCLK\_DYN} + I_{DDINT\_SCLK\_DYN} + \\ I_{DDINT\_DMA\_DR\_DYN} + I_{DDINT\_STATIC} \end{split}$$

#### **Static Current**

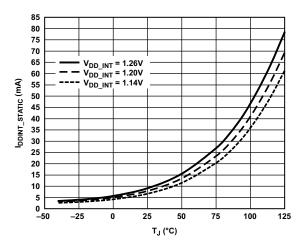

$I_{DDINT\_STATIC}$  is the current present in the device with all clocks stopped.  $I_{DDINT\_STATIC}$  is specified as a function of temperature (see Figure 11).

Figure 11. Static Current—I<sub>DDINT STATIC</sub> (mA)

#### **Core Clock Application-Dependent Current**

Core clock (CCLK) use is subject to an activity scaling factor (ASF) that represents application code running on the processor core and L1 memory (Table 28). The ASF is combined with the CCLK frequency to calculate this portion.

$I_{DDINT\ CCLK\ DYN}$  (mA) =  $0.192 \times f_{CCLK}$  (MHz)  $\times ASF \times V_{DD\ INT}$  (V)

Table 28. Activity Scaling Factors (ASF)

| I <sub>DD_INT</sub> Power Vector   | ASF  |

|------------------------------------|------|

| I <sub>DD-PEAK</sub>               | 1.85 |

| I <sub>DD-COREMARK</sub> (typical) | 1.0  |

| I <sub>DD-IDLE</sub>               | 0.31 |

#### **System Clock Current**

The power dissipated by the system clock domain is dependent on operating frequency and a unique scaling factor.

$I_{DDINT\ SCLK\ DYN}$  (mA) = 0.308 ×  $f_{SCLK}$  (MHz) ×  $V_{DD\ INT}$  (V)

#### **Data Transmission Current**

The data transmission current represents the power dissipated when transmitting data. This current is expressed in terms of data rate. The calculation is performed by adding the data rate (MB/s) of each DMA and core driven access to peripherals and L2/external memory. This number is then multiplied by a coefficient. The following equation provides an estimate of all data transmission current.

$I_{DDINT\ DMA\ DR\ DYN}$  (mA) = 0.0475 × data rate (MB/s) ×  $V_{DD\ INT}$  (V)

| Parameter                                                 | Min   | Тур        | Max  | Unit | Test Conditions/Comments                                                                            |

|-----------------------------------------------------------|-------|------------|------|------|-----------------------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                                       |       |            |      |      |                                                                                                     |

| Throughput                                                |       |            |      |      | ADC0_V <sub>IN, 00-11</sub> , ADC1_V <sub>IN, 00-11</sub>                                           |

| Conversion Rate                                           |       |            | 2.63 | MSPS |                                                                                                     |

| Acquisition time                                          |       | 150        |      | ns   |                                                                                                     |

| AC ACCURACY                                               |       |            |      |      | ADC0_V <sub>IN, 00-11</sub> , ADC1_V <sub>IN, 00-11</sub>                                           |

| Characteristic                                            |       |            |      |      |                                                                                                     |

| ADSP-CM403F/ADSP-CM408F/<br>ADSP-CM409F                   |       |            |      |      |                                                                                                     |

| Signal-to-Noise Ratio (SNR) <sup>1</sup>                  | 80.25 | 81.25      |      | dB   |                                                                                                     |

| Signal-to-(Noise + Distortion) Ratio (SINAD) <sup>1</sup> | 80    | 81         |      | dB   |                                                                                                     |

| Total Harmonic Distortion (THD) <sup>1</sup>              |       | -92        |      | dB   |                                                                                                     |

| Spurious-Free Dynamic Range<br>(SFDR) <sup>1</sup>        |       | 90         |      | dBc  |                                                                                                     |

| Dynamic Range                                             | 82    | 83         |      | dB   | $V_{IN} = V_{REF}/2 (dc)$                                                                           |

| Effective Number of Bits (ENOB)                           | 13.0  | 13.2       |      | Bits |                                                                                                     |

| ADSP-CM402F/ADSP-CM407F                                   |       |            |      |      |                                                                                                     |

| Signal-to-Noise Ratio (SNR) <sup>1</sup>                  | 73    | 74         |      | dB   |                                                                                                     |

| Signal-to-(Noise + Distortion) Ratio (SINAD) <sup>1</sup> | 72    | 73         |      | dB   |                                                                                                     |

| Total Harmonic Distortion (THD) <sup>1</sup>              |       | -88        |      | dB   |                                                                                                     |

| Spurious-Free Dynamic Range<br>(SFDR) <sup>1</sup>        |       | 88         |      | dBc  |                                                                                                     |

| Dynamic Range                                             | 74.5  | 75.5       |      | dB   | $V_{IN} = V_{REF}/2 (dc)$                                                                           |

| Effective Number of Bits (ENOB)                           | 11.6  | 11.8       |      | Bits |                                                                                                     |

| Channel-to-Channel Isolation                              |       | <b>-95</b> |      | dB   | Any channel pair referenced on same ADC<br>Selected channel = 1 kHz, unselected<br>channel = 10 kHz |

| ADC-to-ADC Isolation                                      |       | -100       |      | dB   | Any channel pair referenced on opposite ADC                                                         |

$<sup>^1\,</sup>f_{\rm IN}$  = 1 kHz, 0 V to 2.5 V input, 2.63 MSPS.

#### **FLASH SPECIFICATIONS**

The Flash features include:

- 100,000 ERASE cycles per sector

- 20 years data retention

#### Flash PROGRAM/ERASE SUSPEND Command

Table 29 lists parameters for the Flash suspend command.

Table 29. Suspend Parameters

| Parameter                               | Condition                                                  | Тур | Max | Unit |

|-----------------------------------------|------------------------------------------------------------|-----|-----|------|

| Erase to Suspend <sup>1</sup>           | Sector erase or erase resume to erase suspend              | 700 | -   | μs   |

| Program to Suspend <sup>1</sup>         | Program resume to program suspend                          | 5   | -   | μs   |

| Subsector Erase to Suspend <sup>1</sup> | Subsector erase or subsector erase resume to erase suspend | 50  | _   | μs   |

| Suspend Latency <sup>2</sup>            | Program                                                    | 7   | -   | μs   |

| Suspend Latency <sup>2</sup>            | Subsector erase                                            | 15  | -   | μs   |

| Suspend Latency <sup>3</sup>            | Erase                                                      | 15  | _   | μs   |

<sup>&</sup>lt;sup>1</sup>Timing is not internally controlled.

#### Flash AC Characteristics and Operating Conditions

Table 30 identifies Flash specific operating conditions.

Table 30. AC Characteristics and Operating Conditions

| Parameter                                                                                                | Symbol           | Min | Typ <sup>1</sup>        | Max | Unit |

|----------------------------------------------------------------------------------------------------------|------------------|-----|-------------------------|-----|------|

| Clock Frequency for All Commands other than Read (SPI-ER, QIO-SPI Protocol), $T_J = 105^{\circ}C$        | f <sub>C</sub>   | DC  | _                       | 100 | MHz  |

| Clock Frequency for All Commands other than Read (SPI-ER, QIO-SPI Protocol), $T_J = 125^{\circ}\text{C}$ | $f_C$            | DC  | -                       | 97  | MHz  |

| Clock Frequency for Read Commands, T <sub>J</sub> = 105°C                                                | $f_R$            | DC  | _                       | 50  | MHz  |

| Clock Frequency for Read Commands, $T_J = 125^{\circ}C$                                                  | $f_R$            | DC  | _                       | 45  | MHz  |

| Page Program Cycle Time (256 bytes) <sup>2</sup>                                                         | t <sub>PP</sub>  | _   | 0.5                     | 5   | ms   |

| Page Program Cycle Time (n bytes) <sup>2, 3</sup>                                                        | t <sub>PP</sub>  | _   | $int(n/8) \times 0.015$ | 5   | ms   |

| Subsector Erase Cycle Time                                                                               | t <sub>SSE</sub> | _   | 0.3                     | 1.5 | sec  |

| Sector Erase Cycle Time                                                                                  | t <sub>SE</sub>  | -   | 0.7                     | 3   | sec  |

| Bulk Erase Cycle Time                                                                                    | t <sub>BE</sub>  | _   | 170                     | 250 | sec  |

<sup>&</sup>lt;sup>1</sup> Typical values given for  $T_J = 25$ °C.

<sup>&</sup>lt;sup>2</sup> Any read command accepted.

<sup>&</sup>lt;sup>3</sup> Any command except the following are accepted: sector, subsector, or bulk erase; write status register.

<sup>&</sup>lt;sup>2</sup> When using the page program command to program consecutive bytes, optimized timings are obtained with one sequence including all the bytes vs. several sequences of only a few bytes (1 < n < 256).

$<sup>^{3}</sup>$  int(A) corresponds to the upper integer part of A. For example int(12/8) = 2, int(32/8) = 4 int(15.3) = 16.

#### TIMING SPECIFICATIONS

Specifications are subject to change without notice.

#### Clock and Reset Timing

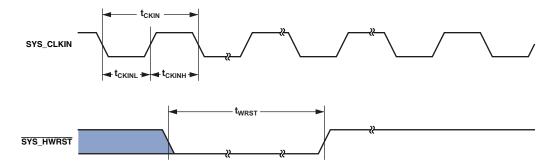

Table 34 and Figure 24 describe clock and reset operations related to the clock generation unit (CGU) and reset control unit (RCU). Per the CCLK, SCLK, USBCLK, and OCLK timing specifications in Table 27 Clock Related Operating Conditions, combinations of SYS\_CLKIN and clock multipliers must not select clock rates in excess of the processor's maximum instruction rate.

Table 34. Clock and Reset Timing

| Parameter          |                                                                     | Min                  | Max | Unit |

|--------------------|---------------------------------------------------------------------|----------------------|-----|------|

| Timing Requ        | Timing Requirements                                                 |                      |     |      |

| $f_{CKIN}$         | SYS_CLKIN Frequency (Using a Crystal) <sup>1, 2, 3</sup>            | 20                   | 50  | MHz  |

| $f_{CKIN}$         | SYS_CLKIN Frequency (Using a Crystal Oscillator) <sup>1, 2, 3</sup> | 20                   | 60  | MHz  |

| $t_{CKINL}$        | SYS_CLKIN Low Pulse <sup>1</sup>                                    | 6.67                 |     | ns   |

| t <sub>CKINH</sub> | SYS_CLKIN High Pulse <sup>1</sup>                                   | 6.67                 |     | ns   |

| $t_{WRST}$         | SYS_HWRST Asserted Pulse Width Low <sup>4</sup>                     | $11 \times t_{CKIN}$ |     | ns   |

$<sup>^{\</sup>rm 1}\,\mathrm{Applies}$  to PLL bypass mode and PLL nonbypass mode.

<sup>&</sup>lt;sup>4</sup> Applies after power-up sequence is complete. See Table 35 and Figure 25 for power-up reset timing.

Figure 24. Clock and Reset Timing

$<sup>^2</sup>$  The  $t_{\text{CKIN}}$  period (see Figure 24) equals  $1/f_{\text{CKIN}}$ .

$<sup>^3</sup>$  If the CGU\_CTL.DF bit is set, the minimum  $f_{CKIN}$  specification is 40 MHz.

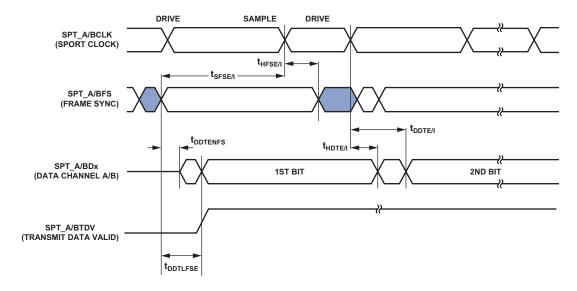

Table 46. Serial Ports—External Late Frame Sync

| Parameter            |                                                                                                                                  | Min | Max | Unit |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| Switching Cha        | aracteristics                                                                                                                    |     |     |      |

| t <sub>DDTLFSE</sub> | Data and Data-Valid Enable Delay from Late External Transmit Frame Sync or External Receive Frame Sync with MCE = 1, MFD = $0^1$ |     | 14  | ns   |

| t <sub>DDTENFS</sub> | Data Enable for MCE = 1, MFD = $0^1$                                                                                             | 0.5 |     | ns   |

$<sup>^1</sup>$  The  $t_{

m DDTLFSE}$  and  $t_{

m DDTENFS}$  parameters apply to left-justified as well as standard serial mode, and MCE = 1, MFD = 0.

Figure 34. External Late Frame Sync

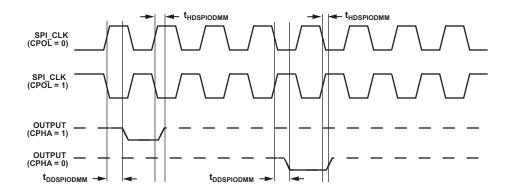

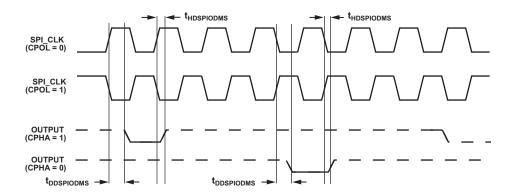

#### Serial Peripheral Interface (SPI) Port—Open Drain Mode (ODM) Timing

In Figure 39 and Figure 40, the outputs can be SPI\_MOSI, SPI\_MISO, SPI\_D2, and/or SPI\_D3 depending on the mode of operation.

Table 50. SPI Port—ODM Master Mode

| Parameter              |                                                    | Min | Max | Unit |

|------------------------|----------------------------------------------------|-----|-----|------|

| Switching Chai         | racteristics                                       |     |     |      |

| t <sub>HDSPIODMM</sub> | SPI_CLK Edge to High Impedance from Data Out Valid | -1  |     | ns   |

| t <sub>DDSPIODMM</sub> | SPI_CLK Edge to Data Out Valid from High Impedance |     | 6   | ns   |

Figure 39. ODM Master

Table 51. SPI Port—ODM Slave Mode

| Parameter              |                                                    | Min | Max | Unit |

|------------------------|----------------------------------------------------|-----|-----|------|

| Timing Requ            | irements                                           |     |     |      |

| t <sub>HDSPIODMS</sub> | SPI_CLK Edge to High Impedance from Data Out Valid | 0   |     | ns   |

| t <sub>DDSPIODMS</sub> | SPI_CLK Edge to Data Out Valid from High Impedance |     | 11  | ns   |

Figure 40. ODM Slave

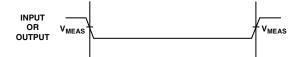

#### PROCESSOR TEST CONDITIONS

All timing parameters appearing in this data sheet were measured under the conditions described in this section. Figure 59 shows the measurement point for ac measurements (except output enable/disable). The measurement point  $V_{\text{MEAS}}$  is  $V_{\text{DD\_EXT}}/2$  for  $V_{\text{DD}}$   $_{\text{EXT}}$  (nominal) = 3.3 V.

Figure 59. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable)

#### **Output Enable Time Measurement**

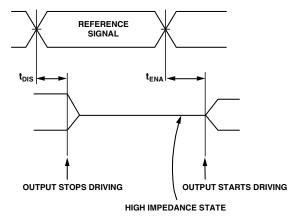

Output pins are considered to be enabled when they have made a transition from a high impedance state to the point when they start driving.

The output enable time,  $t_{\rm ENA}$ , is the interval from the point when a reference signal reaches a high or low voltage level to the point when the output starts driving as shown on the right side of Figure 60. If multiple pins are enabled, the measurement value is that of the first pin to start driving.

Figure 60. Output Enable/Disable

#### **Output Disable Time Measurement**

Output pins are considered to be disabled when they stop driving, go into a high impedance state, and start to decay from their output high or low voltage. The output disable time,  $t_{DIS}$ , is the interval from when a reference signal reaches a high or low voltage level to the point when the output stops driving as shown on the left side of Figure 60.

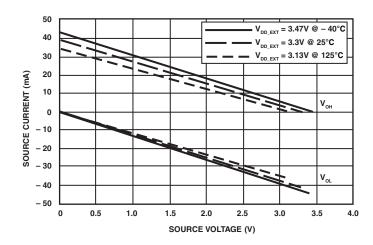

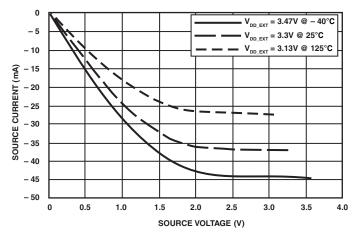

#### **OUTPUT DRIVE CURRENTS**

Figure 61 and Figure 62 show typical current-voltage characteristics for the output drivers of the processors. The curves represent the current drive capability of the output drivers as a function of output voltage.

Figure 61. Driver Type A Current

Figure 62. Driver Type B Current

#### **Capacitive Loading**

Output delay, hold, enable, and disable times are based on standard capacitive loads of an average of 6 pF on all pins (see Figure 63).  $V_{LOAD}$  is equal to  $(V_{DD\_EXT})/2$ .

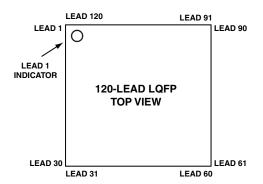

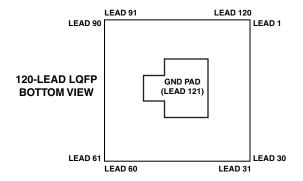

Figure 65 shows the top view of the 120-lead LQFP package lead configuration and Figure 66 shows the bottom view of the 120-lead LQFP package lead configuration.

Figure 65. 120-Lead LQFP Lead Configuration (Top View)

Figure 66. 120-Lead LQFP Lead Configuration (Bottom View)

Table 74. ADSP-CM407F/ADSP-CM408F 176-Lead LQFP Lead Assignments (Alphabetical by Pin Name) (Continued)

| Pin Name      | Lead No. | Pin Name | Lead No. | Pin Name   | Lead No. | Pin Name  | Lead No. |

|---------------|----------|----------|----------|------------|----------|-----------|----------|

| GND_ANA2      | 124      | PC_04    | 54       | PF_01      | 70       | VDD_EXT   | 125      |

| GND_ANA3      | 96       | PC_05    | 51       | PF_02      | 69       | VDD_EXT   | 129      |

| GND_VREF0     | 111      | PC_06    | 52       | PF_03      | 68       | VDD_EXT   | 136      |

| GND_VREF1     | 109      | PC_07    | 49       | PF_04      | 67       | VDD_EXT   | 137      |

| JTG_TCK/SWCLK | 45       | PC_08    | 39       | PF_05      | 61       | VDD_EXT   | 144      |

| JTG_TDI       | 44       | PC_09    | 40       | PF_06      | 58       | VDD_EXT   | 150      |

| JTG_TDO/SWO   | 47       | PC_10    | 38       | PF_07      | 59       | VDD_EXT   | 158      |

| JTG_TMS/SWDIO | 48       | PC_11    | 10       | PF_08      | 55       | VDD_EXT   | 165      |

| JTG_TRST      | 46       | PC_12    | 11       | PF_09      | 56       | VDD_EXT   | 172      |

| PA_00         | 25       | PC_13    | 9        | PF_10      | 53       | VDD_INT   | 22       |

| PA_01         | 21       | PC_14    | 7        | REFCAP     | 110      | VDD_INT   | 65       |

| PA_02         | 20       | PC_15    | 5        | SMC0_AMS0  | 147      | VDD_INT   | 94       |

| PA_03         | 19       | PD_00    | 169      | SMC0_ARE   | 149      | VDD_INT   | 128      |

| PA_04         | 18       | PD_01    | 166      | SMC0_AWE   | 148      | VDD_INT   | 157      |

| PA_05         | 17       | PD_02    | 167      | SYS_BMODE0 | 176      | VDD_VREG  | 32       |

| PA_06         | 16       | PD_03    | 163      | SYS_BMODE1 | 175      | VREF0     | 112      |

| PA_07         | 14       | PD_04    | 164      | SYS_CLKIN  | 30       | VREF1     | 108      |

| PA_08         | 13       | PD_05    | 161      | SYS_CLKOUT | 174      | VREG_BASE | 31       |

| PA_09         | 12       | PD_06    | 146      | SYS_FAULT  | 26       |           |          |

| PA_10         | 6        | PD_07    | 145      | SYS_HWRST  | 27       |           |          |

| PA_11         | 4        | PD_08    | 142      | SYS_NMI    | 132      |           |          |

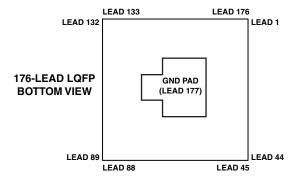

<sup>\*</sup> Pin no. 177 is the GND supply (see Figure 68) for the processor; this pad **must** connect to GND.

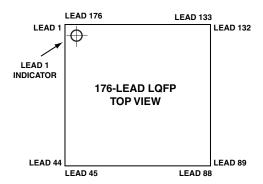

Figure 67 shows the top view of the 176-lead LQFP lead configuration and Figure 68 shows the bottom view of the 176-lead LQFP lead configuration.

Figure 67. 176-Lead LQFP Lead Configuration (Top View)

Figure 68. 176-Lead LQFP Lead Configuration (Bottom View)