Welcome to **E-XFL.COM**

### Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 88                                                         |

| Number of Logic Elements/Cells | 880                                                        |

| Total RAM Bits                 | -                                                          |

| Number of I/O                  | 171                                                        |

| Number of Gates                | 10000                                                      |

| Voltage - Supply               | 3V ~ 3.6V                                                  |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 256-BGA                                                    |

| Supplier Device Package        | 256-FBGA (17x17)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf6010afc256-2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## General Description

The Altera® FLEX 6000 programmable logic device (PLD) family provides a low-cost alternative to high-volume gate array designs. FLEX 6000 devices are based on the OptiFLEX architecture, which minimizes die size while maintaining high performance and routability. The devices have reconfigurable SRAM elements, which give designers the flexibility to quickly change their designs during prototyping and design testing. Designers can also change functionality during operation via in-circuit reconfiguration.

FLEX 6000 devices are reprogrammable, and they are 100% tested prior to shipment. As a result, designers are not required to generate test vectors for fault coverage purposes, allowing them to focus on simulation and design verification. In addition, the designer does not need to manage inventories of different gate array designs. FLEX 6000 devices are configured on the board for the specific functionality required.

Table 3 shows FLEX 6000 performance for some common designs. All performance values shown were obtained using Synopsys DesignWare or LPM functions. Special design techniques are not required to implement the applications; the designer simply infers or instantiates a function in a Verilog HDL, VHDL, Altera Hardware Description Language (AHDL), or schematic design file.

| Application                                | LEs Used |                   | Performance       |                   |     |

|--------------------------------------------|----------|-------------------|-------------------|-------------------|-----|

|                                            |          | -1 Speed<br>Grade | -2 Speed<br>Grade | -3 Speed<br>Grade |     |

| 16-bit loadable counter                    | 16       | 172               | 153               | 133               | MHz |

| 16-bit accumulator                         | 16       | 172               | 153               | 133               | MHz |

| 24-bit accumulator                         | 24       | 136               | 123               | 108               | MHz |

| 16-to-1 multiplexer (pin-to-pin) (1)       | 10       | 12.1              | 13.4              | 16.6              | ns  |

| 16 × 16 multiplier with a 4-stage pipeline | 592      | 84                | 67                | 58                | MHz |

#### Note:

(1) This performance value is measured as a pin-to-pin delay.

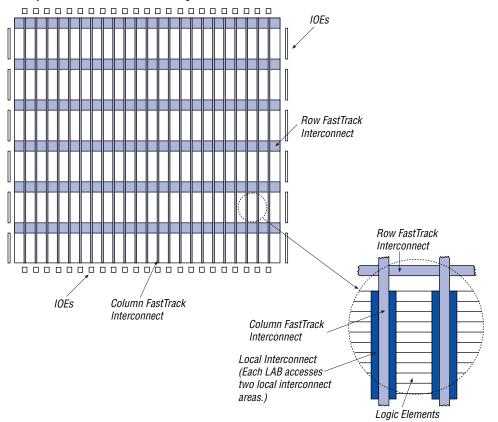

Figure 1. OptiFLEX Architecture Block Diagram

FLEX 6000 devices provide four dedicated, global inputs that drive the control inputs of the flipflops to ensure efficient distribution of high-speed, low-skew control signals. These inputs use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect. These inputs can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device. The dedicated global routing structure is built into the device, eliminating the need to create a clock tree.

#### **Logic Array Block**

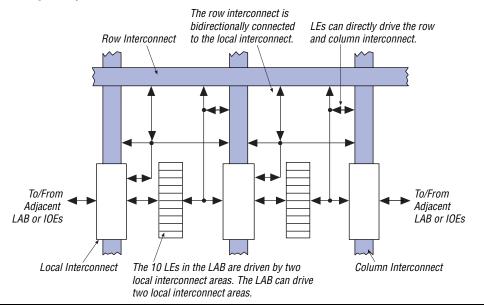

An LAB consists of ten LEs, their associated carry and cascade chains, the LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure of the FLEX 6000 architecture, and facilitates efficient routing with optimum device utilization and high performance.

The interleaved LAB structure—an innovative feature of the FLEX 6000 architecture—allows each LAB to drive two local interconnects. This feature minimizes the use of the FastTrack Interconnect, providing higher performance. An LAB can drive 20 LEs in adjacent LABs via the local interconnect, which maximizes fitting flexibility while minimizing die size. See Figure 2.

Figure 2. Logic Array Block

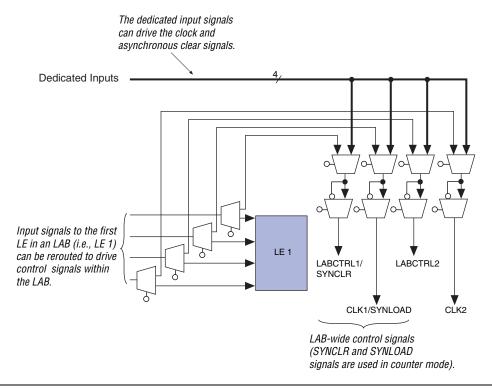

In most designs, the registers only use global clock and clear signals. However, in some cases, other clock or asynchronous clear signals are needed. In addition, counters may also have synchronous clear or load signals. In a design that uses non-global clock and clear signals, inputs from the first LE in an LAB are re-routed to drive the control signals for that LAB. See Figure 3.

Figure 3. LAB Control Signals

#### **Logic Element**

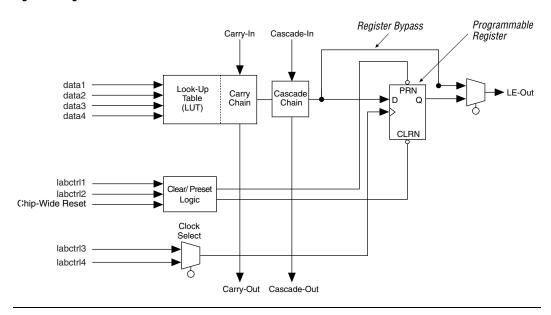

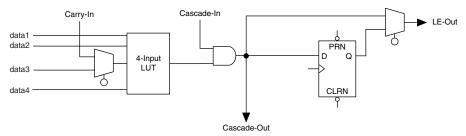

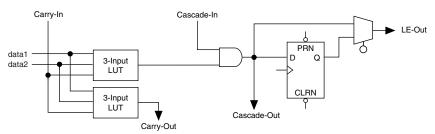

An LE, the smallest unit of logic in the FLEX 6000 architecture, has a compact size that provides efficient logic usage. Each LE contains a four-input LUT, which is a function generator that can quickly implement any function of four variables. An LE contains a programmable flipflop, carry and cascade chains. Additionally, each LE drives both the local and the FastTrack Interconnect. See Figure 4.

Figure 4. Logic Element

The programmable flipflop in the LE can be configured for D, T, JK, or SR operation. The clock and clear control signals on the flipflop can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the flipflop is bypassed and the output of the LUT drives the outputs of the LE. The LE output can drive both the local interconnect and the FastTrack Interconnect.

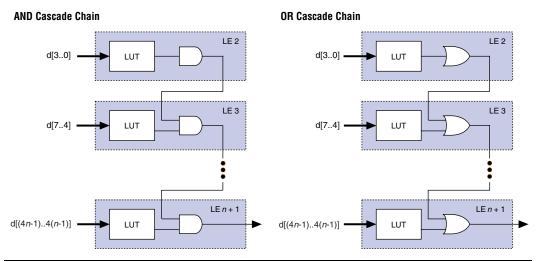

The FLEX 6000 architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. A carry chain supports high-speed arithmetic functions such as counters and adders, while a cascade chain implements wide-input functions such as equivalent comparators with minimum delay. Carry and cascade chains connect LEs 2 through 10 in an LAB and all LABs in the same half of the row. Because extensive use of carry and cascade chains can reduce routing flexibility, these chains should be limited to speed-critical portions of a design.

Figure 6. Cascade Chain Operation

#### LE Operating Modes

The FLEX 6000 LE can operate in one of the following three modes:

- Normal mode

- Arithmetic mode

- Counter mode

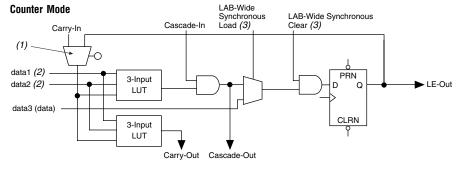

Each of these modes uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, synchronous clear, and synchronous load control for the register. The Altera software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions to use an LE operating mode for optimal performance.

Figure 7 shows the LE operating modes.

Figure 7. LE Operating Modes

#### **Normal Mode**

#### **Arithmetic Mode**

#### Notes:

- (1) The register feedback multiplexer is available on LE 2 of each LAB.

- (2) The data1 and data2 input signals can supply a clock enable, up or down control, or register feedback signals for all LEs other than the second LE in an LAB.

- (3) The LAB-wide synchronous clear and LAB-wide synchronous load affect all registers in an LAB.

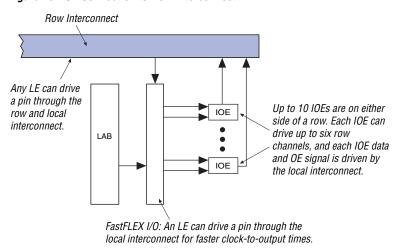

A row channel can be driven by an LE or by one of two column channels. These three signals feed a 3-to-1 multiplexer that connects to six specific row channels. Row channels drive into the local interconnect via multiplexers.

Each column of LABs is served by a dedicated column interconnect. The LEs in an LAB can drive the column interconnect. The LEs in an LAB, a column IOE, or a row interconnect can drive the column interconnect. The column interconnect can then drive another row's interconnect to route the signals to other LABs in the device. A signal from the column interconnect must be routed to the row interconnect before it can enter an LAB.

Each LE has a FastTrack Interconnect output and a local output. The FastTrack interconnect output can drive six row and two column lines directly; the local output drives the local interconnect. Each local interconnect channel driven by an LE can drive four row and two column channels. This feature provides additional flexibility, because each LE can drive any of ten row lines and four column lines.

In addition, LEs can drive global control signals. This feature is useful for distributing internally generated clock, asynchronous clear, and asynchronous preset signals. A pin-driven global signal can also drive data signals, which is useful for high-fan-out data signals.

Each LAB drives two groups of local interconnects, which allows an LE to drive two LABs, or 20 LEs, via the local interconnect. The row-to-local multiplexers are used more efficiently, because the multiplexers can now drive two LABs. Figure 10 shows how an LAB connects to row and column interconnects.

Table 5 summarizes the FastTrack Interconnect resources available in each FLEX 6000 device.

| Table 5. FLEX 6000 FastTrack Interconnect Resources |      |                     |         |                        |  |  |

|-----------------------------------------------------|------|---------------------|---------|------------------------|--|--|

| Device                                              | Rows | Channels per<br>Row | Columns | Channels per<br>Column |  |  |

| EPF6010A                                            | 4    | 144                 | 22      | 20                     |  |  |

| EPF6016<br>EPF6016A                                 | 6    | 144                 | 22      | 20                     |  |  |

| EPF6024A                                            | 7    | 186                 | 28      | 30                     |  |  |

In addition to general-purpose I/O pins, FLEX 6000 devices have four dedicated input pins that provide low-skew signal distribution across the device. These four inputs can be used for global clock and asynchronous clear control signals. These signals are available as control signals for all LEs in the device. The dedicated inputs can also be used as general-purpose data inputs because they can feed the local interconnect of each LAB in the device. Using dedicated inputs to route data signals provides a fast path for high fan-out signals.

The local interconnect from LABs located at either end of two rows can drive a global control signal. For instance, in an EPF6016 device, LABs C1, D1, C22, and D22 can all drive global control signals. When an LE drives a global control signal, the dedicated input pin that drives that signal cannot be used. Any LE in the device can drive a global control signal by driving the FastTrack Interconnect into the appropriate LAB. To minimize delay, however, the Altera software places the driving LE in the appropriate LAB. The LE-driving-global signal feature is optimized for speed for control signals; regular data signals are better routed on the FastTrack Interconnect and do not receive any advantage from being routed on global signals. This LE-driving-global control signal feature is controlled by the designer and is not used automatically by the Altera software. See Figure 11.

Each IOE drives a row or column interconnect when used as an input or bidirectional pin. A row IOE can drive up to six row lines; a column IOE can drive up to two column lines. The input path from the I/O pad to the FastTrack Interconnect has a programmable delay element that can be used to guarantee a zero hold time. Depending on the placement of the IOE relative to what it is driving, the designer may choose to turn on the programmable delay to ensure a zero hold time. Figure 13 shows how an IOE connects to a row interconnect, and Figure 14 shows how an IOE connects to a column interconnect.

Figure 13. IOE Connection to Row Interconnect

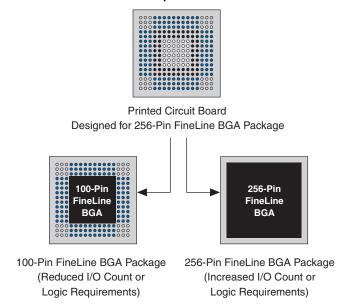

Figure 15. SameFrame Pin-Out Example

Table 6 lists the 3.3-V FLEX 6000 devices with the Same Frame pin-out feature.

| Table 6. 3.3-V FLEX 6000 Devices with SameFrame Pin-Outs |   |   |  |  |  |  |

|----------------------------------------------------------|---|---|--|--|--|--|

| Device 100-Pin FineLine BGA 256-Pin FineLine BGA         |   |   |  |  |  |  |

| EPF6016A                                                 | V | v |  |  |  |  |

| EPF6024A                                                 |   | V |  |  |  |  |

# Output Configuration

This section discusses slew-rate control, the MultiVolt I/O interface, power sequencing, and hot-socketing for FLEX 6000 devices.

#### **Slew-Rate Control**

The output buffer in each IOE has an adjustable output slew-rate that can be configured for low-noise or high-speed performance. A slower slew-rate reduces system noise and adds a maximum delay of 6.8 ns. The fast slew-rate should be used for speed-critical outputs in systems that are adequately protected against noise. Designers can specify the slew-rate on a pin-by-pin basis during design entry or assign a default slew rate to all pins on a device-wide basis. The slew-rate setting affects only the falling edge of the output.

#### MultiVolt I/O Interface

The FLEX 6000 device architecture supports the MultiVolt I/O interface feature, which allows FLEX 6000 devices to interface with systems of differing supply voltages. The EPF6016 device can be set for 3.3-V or 5.0-V I/O pin operation. This device has one set of  $V_{\rm CC}$  pins for internal operation and input buffers (VCCINT), and another set for output drivers (VCCIO).

The VCCINT pins on 5.0-V FLEX 6000 devices must always be connected to a 5.0-V power supply. With a 5.0-V  $V_{CCINT}$  level, input voltages are at TTL levels and are therefore compatible with 3.3-V and 5.0-V inputs.

The VCCIO pins on 5.0-V FLEX 6000 devices can be connected to either a 3.3-V or 5.0-V power supply, depending on the output requirements. When the VCCIO pins are connected to a 5.0-V power supply, the output levels are compatible with 5.0-V systems. When the VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is therefore compatible with 3.3-V or 5.0-V systems. Devices operating with VCCIO levels lower than 4.75 V incur a nominally greater timing delay of  $t_{OD2}$  instead of  $t_{OD1}$ .

On 3.3-V FLEX 6000 devices, the VCCINT pins must be connected to a 3.3-V power supply. Additionally, 3.3-V FLEX 6000A devices can interface with 2.5-V, 3.3-V, or 5.0-V systems when the VCCIO pins are tied to 2.5 V. The output can drive 2.5-V systems, and the inputs can be driven by 2.5-V, 3.3-V, or 5.0-V systems. When the VCCIO pins are tied to 3.3 V, the output can drive 3.3-V or 5.0-V systems. MultiVolt I/Os are not supported on 100-pin TQFP or 100-pin FineLine BGA packages.

| Table 7 d | lescribes  | FLFX 600 | MultiV  | /olt I/ | O suppoi | rt |

|-----------|------------|----------|---------|---------|----------|----|

| Table / G | ICSCITUCS. |          | o widiu | OILI    | O Subboi | ι. |

| Table 7.                                                                | Table 7. FLEX 6000 MultiVolt I/O Support |     |     |     |       |     |       |  |

|-------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|-----|-------|--|

| V <sub>CCINT</sub> V <sub>CCIO</sub> Input Signal (V) Output Signal (V) |                                          |     |     |     |       |     | l (V) |  |

| (V)                                                                     | (V)                                      | 2.5 | 3.3 | 5.0 | 2.5   | 3.3 | 5.0   |  |

| 3.3                                                                     | 2.5                                      | v   | V   | v   | V     |     |       |  |

| 3.3                                                                     | 3.3                                      | v   | v   | v   | v (1) | v   | v     |  |

| 5.0                                                                     | 3.3                                      |     | v   | v   |       | v   | v     |  |

| 5.0                                                                     | 5.0                                      |     | V   | v   |       |     | V     |  |

#### Note:

(1) When  $V_{\rm CCIO} = 3.3~{\rm V}$ , a FLEX 6000 device can drive a 2.5-V device that has 3.3-V tolerant inputs.

| Symbol          | Parameter                                | Conditions                                                   | Min                     | Тур | Max  | Unit |

|-----------------|------------------------------------------|--------------------------------------------------------------|-------------------------|-----|------|------|

| V <sub>IH</sub> | High-level input voltage                 |                                                              | 1.7                     |     | 5.75 | ٧    |

| V <sub>IL</sub> | Low-level input voltage                  |                                                              | -0.5                    |     | 0.8  | ٧    |

| V <sub>OH</sub> | 3.3-V high-level TTL output voltage      | $I_{OH} = -8 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7)   | 2.4                     |     |      | V    |

|                 | 3.3-V high-level CMOS output voltage     | $I_{OH} = -0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7) | V <sub>CCIO</sub> - 0.2 |     |      | V    |

|                 | 2.5-V high-level output voltage          | $I_{OH} = -100 \mu A DC, V_{CCIO} = 2.30 V (7)$              | 2.1                     |     |      | ٧    |

|                 |                                          | I <sub>OH</sub> = -1 mA DC, V <sub>CCIO</sub> = 2.30 V (7)   | 2.0                     |     |      | ٧    |

|                 |                                          | $I_{OH} = -2 \text{ mA DC}, V_{CCIO} = 2.30 \text{ V}$ (7)   | 1.7                     |     |      | ٧    |

| V <sub>OL</sub> | 3.3-V low-level TTL output voltage       | $I_{OL}$ = 8 mA DC, $V_{CCIO}$ = 3.00 V (8)                  |                         |     | 0.45 | V    |

|                 | 3.3-V low-level CMOS output voltage      | $I_{OL} = 0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V } (8)$ |                         |     | 0.2  | V    |

|                 | 2.5-V low-level output voltage           | $I_{OL} = 100 \mu A DC, V_{CCIO} = 2.30 V (8)$               |                         |     | 0.2  | ٧    |

|                 |                                          | I <sub>OL</sub> = 1 mA DC, V <sub>CCIO</sub> = 2.30 V (8)    |                         |     | 0.4  | ٧    |

|                 |                                          | I <sub>OL</sub> = 2 mA DC, V <sub>CCIO</sub> = 2.30 V (8)    |                         |     | 0.7  | ٧    |

| I <sub>I</sub>  | Input pin leakage current                | V <sub>1</sub> = 5.3 V to ground (8)                         | -10                     |     | 10   | μΑ   |

| l <sub>OZ</sub> | Tri-stated I/O pin leakage current       | $V_O = 5.3 \text{ V to ground } (8)$                         | -10                     |     | 10   | μΑ   |

| Icco            | V <sub>CC</sub> supply current (standby) | V <sub>I</sub> = ground, no load                             |                         | 0.5 | 5    | mA   |

| Table 1            | Table 18. FLEX 6000 3.3-V Device CapacitanceNote (9) |                                     |     |     |      |  |

|--------------------|------------------------------------------------------|-------------------------------------|-----|-----|------|--|

| Symbol             | Parameter                                            | Conditions                          | Min | Max | Unit |  |

| C <sub>IN</sub>    | Input capacitance for I/O pin                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |

| C <sub>INCLK</sub> | Input capacitance for dedicated input                | $V_{IN} = 0 V$ , $f = 1.0 MHz$      |     | 12  | pF   |  |

| C <sub>OUT</sub>   | Output capacitance                                   | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) The minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum V<sub>CC</sub> rise time is 100 ms. V<sub>CC</sub> must rise monotonically.

(5) Typical values are for T<sub>A</sub> = 25° C and V<sub>CC</sub> = 3.3 V.

(6) These values are specified under Table 16 on page 33.

(7) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current.

- (8) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (9) Capacitance is sample-tested only.

Tables 19 through 21 describe the FLEX 6000 internal timing microparameters, which are expressed as worst-case values. Using hand calculations, these parameters can be used to estimate design performance. However, before committing designs to silicon, actual worst-case performance should be modeled using timing simulation and timing analysis. Tables 22 and 23 describe FLEX 6000 external timing parameters.

| Symbol                      | Parameter                                                                               | Conditions |

|-----------------------------|-----------------------------------------------------------------------------------------|------------|

| t <sub>REG_TO_REG</sub>     | LUT delay for LE register feedback in carry chain                                       |            |

| t <sub>CASC_TO_REG</sub>    | Cascade-in to register delay                                                            |            |

| t <sub>CARRY_TO_REG</sub>   | Carry-in to register delay                                                              |            |

| t <sub>DATA_TO_REG</sub>    | LE input to register delay                                                              |            |

| t <sub>CASC_TO_OUT</sub>    | Cascade-in to LE output delay                                                           |            |

| t <sub>CARRY_TO_OUT</sub>   | Carry-in to LE output delay                                                             |            |

| t <sub>DATA_TO_OUT</sub>    | LE input to LE output delay                                                             |            |

| t <sub>REG_TO_OUT</sub>     | Register output to LE output delay                                                      |            |

| t <sub>SU</sub>             | LE register setup time before clock; LE register recovery time after asynchronous clear |            |

| t <sub>H</sub>              | LE register hold time after clock                                                       |            |

| $t_{CO}$                    | LE register clock-to-output delay                                                       |            |

| t <sub>CLR</sub>            | LE register clear delay                                                                 |            |

| $t_C$                       | LE register control signal delay                                                        |            |

| t <sub>LD_CLR</sub>         | Synchronous load or clear delay in counter mode                                         |            |

| t <sub>CARRY_TO_CARRY</sub> | Carry-in to carry-out delay                                                             |            |

| t <sub>REG_TO_CARRY</sub>   | Register output to carry-out delay                                                      |            |

| t <sub>DATA_TO_CARRY</sub>  | LE input to carry-out delay                                                             |            |

| t <sub>CARRY_TO_CASC</sub>  | Carry-in to cascade-out delay                                                           |            |

| t <sub>CASC_TO_CASC</sub>   | Cascade-in to cascade-out delay                                                         |            |

| t <sub>REG_TO_CASC</sub>    | Register-out to cascade-out delay                                                       |            |

| t <sub>DATA_TO_CASC</sub>   | LE input to cascade-out delay                                                           |            |

| t <sub>CH</sub>             | LE register clock high time                                                             |            |

| $t_{CL}$                    | LE register clock low time                                                              |            |

|                             | +                                                                                       | -          |

| Symbol                | Parameter                                                                                 | Conditions     |

|-----------------------|-------------------------------------------------------------------------------------------|----------------|

| t <sub>OD1</sub>      | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = V <sub>CCINT</sub> | C1 = 35 pF (2) |

| t <sub>OD2</sub>      | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = low voltage        | C1 = 35 pF (3) |

| t <sub>OD3</sub>      | Output buffer and pad delay, slow slew rate = on                                          | C1 = 35 pF (4) |

| $t_{XZ}$              | Output buffer disable delay                                                               | C1 = 5 pF      |

| t <sub>ZX1</sub>      | Output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = V <sub>CCINT</sub>  | C1 = 35 pF (2) |

| $t_{ZX2}$             | Output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = low voltage         | C1 = 35 pF (3) |

| t <sub>ZX3</sub>      | IOE output buffer enable delay, slow slew rate = on                                       | C1 = 35 pF (4) |

| t <sub>IOE</sub>      | Output enable control delay                                                               |                |

| t <sub>IN</sub>       | Input pad and buffer to FastTrack Interconnect delay                                      |                |

| t <sub>IN_DELAY</sub> | Input pad and buffer to FastTrack Interconnect delay with additional delay turned on      |                |

| Table 21. Interconnect Timing Microparameters      Note (1) |                                                                                                                      |            |  |  |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Symbol                                                      | Parameter                                                                                                            | Conditions |  |  |

| t <sub>LOCAL</sub>                                          | LAB local interconnect delay                                                                                         |            |  |  |

| t <sub>ROW</sub>                                            | Row interconnect routing delay                                                                                       | (5)        |  |  |

| t <sub>COL</sub>                                            | Column interconnect routing delay                                                                                    | (5)        |  |  |

| t <sub>DIN_D</sub>                                          | Dedicated input to LE data delay                                                                                     | (5)        |  |  |

| t <sub>DIN_C</sub>                                          | Dedicated input to LE control delay                                                                                  |            |  |  |

| t <sub>LEGLOBAL</sub>                                       | LE output to LE control via internally-generated global signal delay                                                 | (5)        |  |  |

| t <sub>LABCARRY</sub>                                       | Routing delay for the carry-out of an LE driving the carry-in signal of a different LE in a different LAB            |            |  |  |

| t <sub>LABCASC</sub>                                        | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |            |  |  |

| Table 22. External Reference Timing Parameters |                                                                                      |            |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------|------------|--|--|

| Symbol                                         | Parameter                                                                            | Conditions |  |  |

| t <sub>1</sub>                                 | Register-to-register test pattern                                                    | (6)        |  |  |

| t <sub>DRR</sub>                               | Register-to-register delay via 4 LEs, 3 row interconnects, and 4 local interconnects | (7)        |  |  |

| Parameter             | Speed Grade |     |     |     |     |     |    |  |  |

|-----------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                       | -1          |     | -2  |     | -3  |     |    |  |  |

|                       | Min         | Max | Min | Max | Min | Max |    |  |  |

| t <sub>LOCAL</sub>    |             | 0.7 |     | 0.7 |     | 1.0 | ns |  |  |

| t <sub>ROW</sub>      |             | 2.9 |     | 3.2 |     | 3.2 | ns |  |  |

| t <sub>COL</sub>      |             | 1.2 |     | 1.3 |     | 1.4 | ns |  |  |

| t <sub>DIN_D</sub>    |             | 5.4 |     | 5.7 |     | 6.4 | ns |  |  |

| t <sub>DIN_C</sub>    |             | 4.3 |     | 5.0 |     | 6.1 | ns |  |  |

| t<br>LEGLOBAL         |             | 2.6 |     | 3.0 |     | 3.7 | ns |  |  |

| t <sub>LABCARRY</sub> |             | 0.7 |     | 0.8 |     | 0.9 | ns |  |  |

| t <sub>LABCASC</sub>  |             | 1.3 |     | 1.4 |     | 1.8 | ns |  |  |

| Table 27. External Reference Timing Parameters for EPF6010A & EPF6016A Devices |          |             |      |     |      |     |      |    |  |

|--------------------------------------------------------------------------------|----------|-------------|------|-----|------|-----|------|----|--|

| Parameter                                                                      | Device   | Speed Grade |      |     |      |     |      |    |  |

|                                                                                |          | -           | 1    | -2  |      |     | -3   |    |  |

|                                                                                |          | Min         | Max  | Min | Max  | Min | Max  |    |  |

| t <sub>1</sub>                                                                 | EPF6010A |             | 37.6 |     | 43.6 |     | 53.7 | ns |  |

|                                                                                | EPF6016A |             | 38.0 |     | 44.0 |     | 54.1 | ns |  |

| Table 28. External Timing Parameters for EPF6010A & EPF6016A Devices |             |     |         |     |         |      |    |  |

|----------------------------------------------------------------------|-------------|-----|---------|-----|---------|------|----|--|

| Parameter                                                            | Speed Grade |     |         |     |         |      |    |  |

|                                                                      | -1          |     | -2      | l.  | -3      |      |    |  |

|                                                                      | Min         | Max | Min     | Max | Min     | Max  |    |  |

| t <sub>INSU</sub>                                                    | 2.1 (1)     |     | 2.4 (1) |     | 3.3 (1) |      | ns |  |

| t <sub>INH</sub>                                                     | 0.2 (2)     |     | 0.3 (2) |     | 0.1 (2) |      | ns |  |

| t <sub>оитсо</sub>                                                   | 2.0         | 7.1 | 2.0     | 8.2 | 2.0     | 10.1 | ns |  |

#### Notes:

Setup times are longer when the *Increase Input Delay* option is turned on. The setup time values are shown with the *Increase Input Delay* option turned off.

Hold time is zero when the *Increase Input Delay* option is turned on.

| Table 33. External Timing Parameters for EPF6016 Devices |     |             |     |     |    |  |  |  |

|----------------------------------------------------------|-----|-------------|-----|-----|----|--|--|--|

| Parameter                                                |     | Speed Grade |     |     |    |  |  |  |

|                                                          |     | -2          |     |     |    |  |  |  |

|                                                          | Min | Max         | Min | Max |    |  |  |  |

| t <sub>INSU</sub>                                        | 3.2 |             | 4.1 |     | ns |  |  |  |

| t <sub>INH</sub>                                         | 0.0 |             | 0.0 |     | ns |  |  |  |

| t <sub>оитсо</sub>                                       | 2.0 | 7.9         | 2.0 | 9.9 | ns |  |  |  |

Tables 34 through 38 show the timing information for EPF6024A devices.

| Parameter                   | Speed Grade |     |     |     |     |     |    |  |

|-----------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                             | -1          |     | -2  |     | -3  |     | 1  |  |

|                             | Min         | Max | Min | Max | Min | Max |    |  |

| t <sub>REG_TO_REG</sub>     |             | 1.2 |     | 1.3 |     | 1.6 | ns |  |

| t <sub>CASC_TO_REG</sub>    |             | 0.7 |     | 0.8 |     | 1.0 | ns |  |

| t <sub>CARRY_TO_REG</sub>   |             | 1.6 |     | 1.8 |     | 2.2 | ns |  |

| t <sub>DATA_TO_REG</sub>    |             | 1.3 |     | 1.4 |     | 1.7 | ns |  |

| t <sub>CASC_TO_OUT</sub>    |             | 1.2 |     | 1.3 |     | 1.6 | ns |  |

| t <sub>CARRY_TO_OUT</sub>   |             | 2.0 |     | 2.2 |     | 2.6 | ns |  |

| t <sub>DATA_TO_OUT</sub>    |             | 1.8 |     | 2.1 |     | 2.6 | ns |  |

| t <sub>REG_TO_OUT</sub>     |             | 0.3 |     | 0.3 |     | 0.4 | ns |  |

| t <sub>SU</sub>             | 0.9         |     | 1.0 |     | 1.2 |     | ns |  |

| t <sub>H</sub>              | 1.3         |     | 1.4 |     | 1.7 |     | ns |  |

| $t_{CO}$                    |             | 0.2 |     | 0.3 |     | 0.3 | ns |  |

| t <sub>CLR</sub>            |             | 0.3 |     | 0.3 |     | 0.4 | ns |  |

| $t_C$                       |             | 1.9 |     | 2.1 |     | 2.5 | ns |  |

| t <sub>LD_CLR</sub>         |             | 1.9 |     | 2.1 |     | 2.5 | ns |  |

| t <sub>CARRY_TO_CARRY</sub> |             | 0.2 |     | 0.2 |     | 0.3 | ns |  |

| t <sub>REG_TO_CARRY</sub>   |             | 1.4 |     | 1.6 |     | 1.9 | ns |  |

| t <sub>DATA_TO_CARRY</sub>  |             | 1.3 | _   | 1.4 |     | 1.7 | ns |  |

| t <sub>CARRY_TO_CASC</sub>  |             | 1.1 |     | 1.2 |     | 1.4 | ns |  |

| t <sub>CASC_TO_CASC</sub>   |             | 0.7 |     | 0.8 |     | 1.0 | ns |  |

| t <sub>REG_TO_CASC</sub>    |             | 1.4 |     | 1.6 |     | 1.9 | ns |  |

| t <sub>DATA_TO_CASC</sub>   |             | 1.0 |     | 1.1 |     | 1.3 | ns |  |

| t <sub>CH</sub>             | 2.5         |     | 3.0 |     | 3.5 |     | ns |  |

| t <sub>CL</sub>             | 2.5         |     | 3.0 |     | 3.5 |     | ns |  |

| Parameter             | Speed Grade |     |     |      |     |      |    |  |  |

|-----------------------|-------------|-----|-----|------|-----|------|----|--|--|

|                       | -1          |     | -2  |      | -3  |      |    |  |  |

|                       | Min         | Max | Min | Max  | Min | Max  |    |  |  |

| t <sub>OD1</sub>      |             | 1.9 |     | 2.1  |     | 2.5  | ns |  |  |

| t <sub>OD2</sub>      |             | 4.0 |     | 4.4  |     | 5.3  | ns |  |  |

| t <sub>OD3</sub>      |             | 7.0 |     | 7.8  |     | 9.3  | ns |  |  |

| $t_{XZ}$              |             | 4.3 |     | 4.8  |     | 5.8  | ns |  |  |

| $t_{XZ1}$             |             | 4.3 |     | 4.8  |     | 5.8  | ns |  |  |

| t <sub>XZ2</sub>      |             | 6.4 |     | 7.1  |     | 8.6  | ns |  |  |

| t <sub>XZ3</sub>      |             | 9.4 |     | 10.5 |     | 12.6 | ns |  |  |

| IOE                   |             | 0.5 |     | 0.6  |     | 0.7  | ns |  |  |

| İN                    |             | 3.3 |     | 3.7  |     | 4.4  | ns |  |  |

| t <sub>IN DELAY</sub> |             | 5.3 |     | 5.9  |     | 7.0  | ns |  |  |

| Parameter             | Speed Grade |     |     |     |     |     |    |  |  |

|-----------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                       | -1          |     | -2  |     | -3  |     |    |  |  |

|                       | Min         | Max | Min | Max | Min | Max | 1  |  |  |

| t <sub>LOCAL</sub>    |             | 0.8 |     | 0.8 |     | 1.1 | ns |  |  |

| t <sub>ROW</sub>      |             | 3.0 |     | 3.1 |     | 3.3 | ns |  |  |

| t <sub>COL</sub>      |             | 3.0 |     | 3.2 |     | 3.4 | ns |  |  |

| t <sub>DIN_D</sub>    |             | 5.4 |     | 5.6 |     | 6.2 | ns |  |  |

| t <sub>DIN_C</sub>    |             | 4.6 |     | 5.1 |     | 6.1 | ns |  |  |

| t <sub>LEGLOBAL</sub> |             | 3.1 |     | 3.5 |     | 4.3 | ns |  |  |

| t <sub>LABCARRY</sub> |             | 0.6 |     | 0.7 |     | 0.8 | ns |  |  |

| t <sub>LABCASC</sub>  |             | 0.3 |     | 0.3 |     | 0.4 | ns |  |  |

| Table 37. External Reference Timing Parameters for EPF6024A Devices |     |                 |     |      |     |      |    |  |

|---------------------------------------------------------------------|-----|-----------------|-----|------|-----|------|----|--|

| Parameter                                                           |     | Speed Grade Uni |     |      |     |      |    |  |

|                                                                     | -   | 1               | -2  |      | -3  |      |    |  |

|                                                                     | Min | Max             | Min | Max  | Min | Max  |    |  |

| t <sub>1</sub>                                                      |     | 45.0            |     | 50.0 |     | 60.0 | ns |  |

### Device Pin-Outs

See the Altera web site (http://www.altera.com) or the *Altera Digital Library* for pin-out information.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Customer Marketing: (408) 544-7104 Literature Services: (888) 3-ALTERA lit\_req@altera.com Altera, BitBlaster, ByteBlasterMV, FastFlex, FastTrack, FineLine BGA, FLEX, MasterBlaster, MAX+PLUS II, MegaCore, MultiVolt, OptiFLEX, Quartus, SameFrame, and specific device designations are trademarks and/or service marks of Altera Corporation in the United States and other countries. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document, specifically: Verilog is a registered trademark of and Verilog-XL is a trademarks of Cadence Design Systems, Inc. DATA I/O is a registered trademark of Data I/O Corporation. HP is a registered trademark of Hewlett-Packard Company. Exemplar Logic is a registered trademark of Exemplar Logic, Inc. Pentium is a registered trademark of Intel Corporation. Mentor Graphics is a registered trademark of Mentor Graphics Corporation. OrCAD is a registered trademark of OrCAD Systems, Corporation. SPARCstation is a registered trademark of SPARC International, Inc. and is licensed exclusively to Sun Microsystems, Inc. Sun Workstation is a registered trademark on DesignTime, HDL Compiler, and DesignWare are trademarks of Synopsys is a registered trademark of Viewlogic Systems, Inc. Viewlogic is a registered trademark of Viewlogic Systems, Inc. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Copyright © 2001 Altera Corporation. All rights reserved.

LS EN ISO 900