Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 132                                                        |

| Number of Logic Elements/Cells | 1320                                                       |

| Total RAM Bits                 | -                                                          |

| Number of I/O                  | 199                                                        |

| Number of Gates                | 16000                                                      |

| Voltage - Supply               | 4.75V ~ 5.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 240-BFQFP                                                  |

| Supplier Device Package        | 240-PQFP (32x32)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf6016qc240-2n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## ...and More Features

- Powerful I/O pins

- Individual tri-state output enable control for each pin

- Programmable output slew-rate control to reduce switching noise

- Fast path from register to I/O pin for fast clock-to-output time

- Flexible interconnect

- FastTrack<sup>®</sup> Interconnect continuous routing structure for fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fanin logic functions (automatically used by software tools and megafunctions)

- Tri-state emulation that implements internal tri-state networks

- Four low-skew global paths for clock, clear, preset, or logic signals

- Software design support and automatic place-and-route provided by Altera's development system for Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800

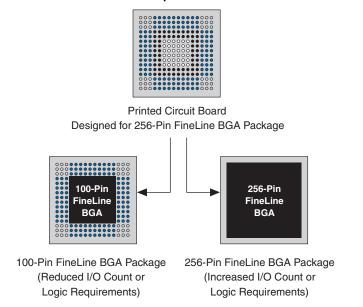

- Flexible package options

- Available in a variety of packages with 100 to 256 pins, including the innovative FineLine BGA<sup>TM</sup> packages (see Table 2)

- SameFrame<sup>TM</sup> pin-compatibility (with other FLEX® 6000 devices) across device densities and pin counts

- Thin quad flat pack (TQFP), plastic quad flat pack (PQFP), and ball-grid array (BGA) packages (see Table 2)

- Footprint- and pin-compatibility with other FLEX 6000 devices in the same package

- Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, the library of parameterized modules (LPM), Verilog HDL, VHDL, DesignWare components, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, VeriBest, and Viewlogic

| Table 2. FLEX 6000 Package Options & I/O Pin Count |                 |                         |                 |                 |                 |                |                         |

|----------------------------------------------------|-----------------|-------------------------|-----------------|-----------------|-----------------|----------------|-------------------------|

| Device                                             | 100-Pin<br>TQFP | 100-Pin<br>FineLine BGA | 144-Pin<br>TQFP | 208-Pin<br>PQFP | 240-Pin<br>PQFP | 256-Pin<br>BGA | 256-pin<br>FineLine BGA |

| EPF6010A                                           | 71              |                         | 102             |                 |                 |                |                         |

| EPF6016                                            |                 |                         | 117             | 171             | 199             | 204            |                         |

| EPF6016A                                           | 81              | 81                      | 117             | 171             |                 |                | 171                     |

| EPF6024A                                           |                 |                         | 117             | 171             | 199             | 218            | 219                     |

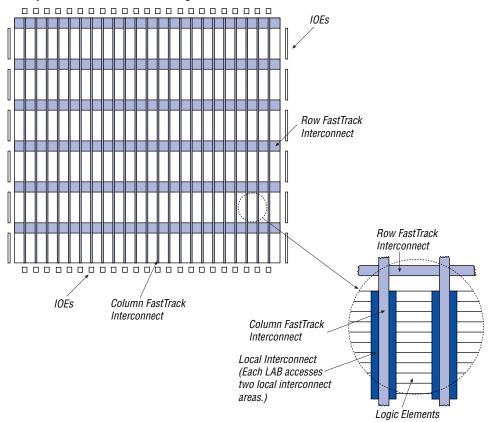

Figure 1. OptiFLEX Architecture Block Diagram

FLEX 6000 devices provide four dedicated, global inputs that drive the control inputs of the flipflops to ensure efficient distribution of high-speed, low-skew control signals. These inputs use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect. These inputs can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device. The dedicated global routing structure is built into the device, eliminating the need to create a clock tree.

### **Logic Array Block**

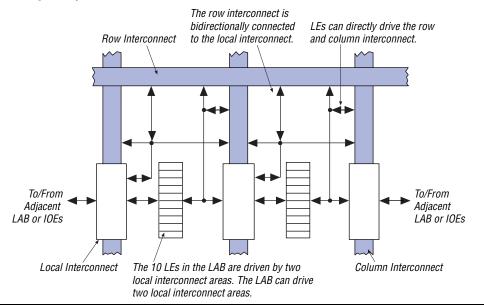

An LAB consists of ten LEs, their associated carry and cascade chains, the LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure of the FLEX 6000 architecture, and facilitates efficient routing with optimum device utilization and high performance.

The interleaved LAB structure—an innovative feature of the FLEX 6000 architecture—allows each LAB to drive two local interconnects. This feature minimizes the use of the FastTrack Interconnect, providing higher performance. An LAB can drive 20 LEs in adjacent LABs via the local interconnect, which maximizes fitting flexibility while minimizing die size. See Figure 2.

Figure 2. Logic Array Block

In most designs, the registers only use global clock and clear signals. However, in some cases, other clock or asynchronous clear signals are needed. In addition, counters may also have synchronous clear or load signals. In a design that uses non-global clock and clear signals, inputs from the first LE in an LAB are re-routed to drive the control signals for that LAB. See Figure 3.

#### Cascade Chain

The cascade chain enables the FLEX 6000 architecture to implement very wide fan-in functions. Adjacent LUTs can be used to implement portions of the function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR gate (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a delay as low as 0.5 ns per LE. Cascade chain logic can be created automatically by the Altera software during design processing, or manually by the designer during design entry. Parameterized functions such as LPM and DesignWare functions automatically take advantage of cascade chains for the appropriate functions.

A cascade chain implementing an AND gate can use the register in the last LE; a cascade chain implementing an OR gate cannot use this register because of the inversion required to implement the OR gate.

Because the first LE of an LAB can generate control signals for that LAB, the first LE in each LAB is not included in cascade chains. Moreover, cascade chains longer than nine bits are automatically implemented by linking several LABs together. For easier routing, a long cascade chain skips every other LAB in a row. A cascade chain longer than one LAB skips either from an even-numbered LAB to another even-numbered LAB, or from an odd-numbered LAB to another odd-numbered LAB. For example, the last LE of the first LAB in a row cascades to the second LE of the third LAB. The cascade chain does not cross the center of the row. For example, in an EPF6016 device, the cascade chain stops at the 11th LAB in a row and a new cascade chain begins at the 12th LAB.

Figure 6 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in. In this example, functions of 4n variables are implemented with n LEs. The cascade chain requires 3.4 ns to decode a 16-bit address.

Either the counter enable or the up/down control may be used for a given counter. Moreover, the synchronous load can be used as a count enable by routing the register output into the data input automatically when requested by the designer.

The second LE of each LAB has a special function for counter mode; the carry-in of the LE can be driven by a fast feedback path from the register. This function gives a faster counter speed for counter carry chains starting in the second LE of an LAB.

The Altera software implements functions to use the counter mode automatically where appropriate. The designer does not have to decide how the carry chain will be used.

#### Internal Tri-State Emulation

Internal tri-state emulation provides internal tri-states without the limitations of a physical tri-state bus. In a physical tri-state bus, the tri-state buffers' output enable (OE) signals select which signal drives the bus. However, if multiple OE signals are active, contending signals can be driven onto the bus. Conversely, if no OE signals are active, the bus will float. Internal tri-state emulation resolves contending tri-state buffers to a low value and floating buses to a high value, thereby eliminating these problems. The Altera software automatically implements tri-state bus functionality with a multiplexer.

#### Clear & Preset Logic Control

Logic for the programmable register's clear and preset functions is controlled by the LAB-wide signals LABCTRL1 and LABCTRL2. The LE register has an asynchronous clear that can implement an asynchronous preset. Either LABCTRL1 or LABCTRL2 can control the asynchronous clear or preset. Because the clear and preset functions are active-low, the Altera software automatically assigns a logic high to an unused clear or preset signal. The clear and preset logic is implemented in either the asynchronous clear or asynchronous preset mode, which is chosen during design entry (see Figure 8).

A row channel can be driven by an LE or by one of two column channels. These three signals feed a 3-to-1 multiplexer that connects to six specific row channels. Row channels drive into the local interconnect via multiplexers.

Each column of LABs is served by a dedicated column interconnect. The LEs in an LAB can drive the column interconnect. The LEs in an LAB, a column IOE, or a row interconnect can drive the column interconnect. The column interconnect can then drive another row's interconnect to route the signals to other LABs in the device. A signal from the column interconnect must be routed to the row interconnect before it can enter an LAB.

Each LE has a FastTrack Interconnect output and a local output. The FastTrack interconnect output can drive six row and two column lines directly; the local output drives the local interconnect. Each local interconnect channel driven by an LE can drive four row and two column channels. This feature provides additional flexibility, because each LE can drive any of ten row lines and four column lines.

In addition, LEs can drive global control signals. This feature is useful for distributing internally generated clock, asynchronous clear, and asynchronous preset signals. A pin-driven global signal can also drive data signals, which is useful for high-fan-out data signals.

Each LAB drives two groups of local interconnects, which allows an LE to drive two LABs, or 20 LEs, via the local interconnect. The row-to-local multiplexers are used more efficiently, because the multiplexers can now drive two LABs. Figure 10 shows how an LAB connects to row and column interconnects.

#### I/O Elements

An IOE contains a bidirectional I/O buffer and a tri-state buffer. IOEs can be used as input, output, or bidirectional pins. An IOE receives its data signals from the adjacent local interconnect, which can be driven by a row or column interconnect (allowing any LE in the device to drive the IOE) or by an adjacent LE (allowing fast clock-to-output delays). A FastFLEX<sup>TM</sup> I/O pin is a row or column output pin that receives its data signals from the adjacent local interconnect driven by an adjacent LE. The IOE receives its output enable signal through the same path, allowing individual output enables for every pin and permitting emulation of open-drain buffers. The Altera Compiler uses programmable inversion to invert the data or output enable signals automatically where appropriate. Open-drain emulation is provided by driving the data input low and toggling the OE of each IOE. This emulation is possible because there is one OE per pin.

A chip-wide output enable feature allows the designer to disable all pins of the device by asserting one pin (DEV\_OE). This feature is useful during board debugging or testing.

Figure 12 shows the IOE block diagram.

To Row or Column Interconnect

Chip-Wide Output Enable

From LAB Local Interconnect

Slew-Rate

Control

Figure 12. IOE Block Diagram

Figure 15. SameFrame Pin-Out Example

Table 6 lists the 3.3-V FLEX 6000 devices with the Same Frame pin-out feature.

| Table 6. 3.3-V FLEX 6000 Devices with SameFrame Pin-Outs |   |   |  |  |  |

|----------------------------------------------------------|---|---|--|--|--|

| Device 100-Pin FineLine BGA 256-Pin FineLine BGA         |   |   |  |  |  |

| EPF6016A                                                 | V | v |  |  |  |

| EPF6024A                                                 |   | V |  |  |  |

# Output Configuration

This section discusses slew-rate control, the MultiVolt I/O interface, power sequencing, and hot-socketing for FLEX 6000 devices.

#### **Slew-Rate Control**

The output buffer in each IOE has an adjustable output slew-rate that can be configured for low-noise or high-speed performance. A slower slew-rate reduces system noise and adds a maximum delay of 6.8 ns. The fast slew-rate should be used for speed-critical outputs in systems that are adequately protected against noise. Designers can specify the slew-rate on a pin-by-pin basis during design entry or assign a default slew rate to all pins on a device-wide basis. The slew-rate setting affects only the falling edge of the output.

Open-drain output pins on 5.0-V or 3.3-V FLEX 6000 devices (with a pull-up resistor to the 5.0-V supply) can drive 5.0-V CMOS input pins that require a  $V_{\rm IH}$  of 3.5 V. When the open-drain pin is active, it will drive low. When the pin is inactive, the trace will be pulled up to 5.0 V by the resistor. The open-drain pin will only drive low or tri-state; it will never drive high. The rise time is dependent on the value of the pull-up resistor and load impedance. The  $I_{\rm OL}$  current specification should be considered when selecting a pull-up resistor.

Output pins on 5.0-V FLEX 6000 devices with  $V_{CCIO}$  = 3.3 V or 5.0 V (with a pull-up resistor to the 5.0-V supply) can also drive 5.0-V CMOS input pins. In this case, the pull-up transistor will turn off when the pin voltage exceeds 3.3 V. Therefore, the pin does not have to be open-drain.

#### **Power Sequencing & Hot-Socketing**

Because FLEX 6000 family devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The  $\rm V_{CCIO}$  and  $\rm V_{CCINT}$  power planes can be powered in any order.

Signals can be driven into 3.3-V FLEX 6000 devices before and during power up without damaging the device. Additionally, FLEX 6000 devices do not drive out during power up. Once operating conditions are reached, FLEX 6000 devices operate as specified by the user.

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All FLEX 6000 devices provide JTAG BST circuitry that comply with the IEEE Std. 1149.1-1990 specification. Table 8 shows JTAG instructions for FLEX 6000 devices. JTAG BST can be performed before or after configuration, but not during configuration (except when you disable JTAG support in user mode).

See Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices) for more information on JTAG BST circuitry.

| Table 8. FLEX 6000           | Table 8. FLEX 6000 JTAG Instructions                                                                                                                                                           |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JTAG Instruction Description |                                                                                                                                                                                                |  |  |  |

| SAMPLE/PRELOAD               | Allows a snapshot of the signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins.           |  |  |  |

| EXTEST                       | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test result at the input pins.                          |  |  |  |

| BYPASS                       | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through the selected device to adjacent devices during normal device operation. |  |  |  |

The instruction register length for FLEX 6000 devices is three bits. Table 9 shows the boundary-scan register length for FLEX 6000 devices.

| Table 9. FLEX 6000 Device Boundary-Scan Register Length |                               |  |  |

|---------------------------------------------------------|-------------------------------|--|--|

| Device                                                  | Boundary-Scan Register Length |  |  |

| EPF6010A                                                | 522                           |  |  |

| EPF6016                                                 | 621                           |  |  |

| EPF6016A                                                | 522                           |  |  |

| EPF6024A                                                | 666                           |  |  |

FLEX 6000 devices include a weak pull-up on JTAG pins.

f See Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices) for more information.

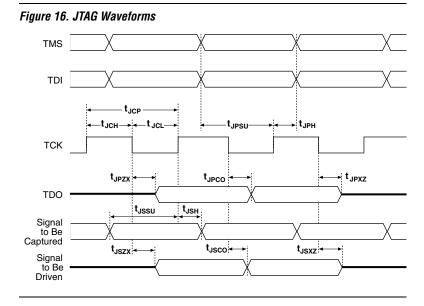

Figure 16 shows the timing requirements for the JTAG signals.

Table 10 shows the JTAG timing parameters and values for FLEX 6000 devices.

# Operating Conditions

Tables 11 through 18 provide information on absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for 5.0-V and 3.3-V FLEX 6000 devices.

| Table 1          | Table 11. FLEX 6000 5.0-V Device Absolute Maximum Ratings Note (1) |                              |      |     |      |  |  |

|------------------|--------------------------------------------------------------------|------------------------------|------|-----|------|--|--|

| Symbol           | Parameter                                                          | Conditions                   | Min  | Max | Unit |  |  |

| V <sub>CC</sub>  | Supply voltage                                                     | With respect to ground (2)   | -2.0 | 7.0 | ٧    |  |  |

| VI               | DC input voltage                                                   |                              | -2.0 | 7.0 | V    |  |  |

| I <sub>OUT</sub> | DC output current, per pin                                         |                              | -25  | 25  | mA   |  |  |

| T <sub>STG</sub> | Storage temperature                                                | No bias                      | -65  | 150 | ° C  |  |  |

| T <sub>AMB</sub> | Ambient temperature                                                | Under bias                   | -65  | 135 | ° C  |  |  |

| TJ               | Junction temperature                                               | PQFP, TQFP, and BGA packages |      | 135 | ° C  |  |  |

| Symbol             | Parameter                                           | Conditions         | Min         | Max                      | Unit |

|--------------------|-----------------------------------------------------|--------------------|-------------|--------------------------|------|

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)           | 4.75 (4.50) | 5.25 (5.50)              | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 5.0-V operation  | (3), (4)           | 4.75 (4.50) | 5.25 (5.50)              | V    |

|                    | Supply voltage for output buffers, 3.3-V operation  | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)              | V    |

| V <sub>I</sub>     | Input voltage                                       |                    | -0.5        | V <sub>CCINT</sub> + 0.5 | V    |

| Vo                 | Output voltage                                      |                    | 0           | V <sub>CCIO</sub>        | V    |

| TJ                 | Operating temperature                               | For commercial use | 0           | 85                       | ° C  |

|                    |                                                     | For industrial use | -40         | 100                      | ° C  |

| t <sub>R</sub>     | Input rise time                                     |                    |             | 40                       | ns   |

| t <sub>F</sub>     | Input fall time                                     |                    |             | 40                       | ns   |

| Table 15. FLEX 6000 3.3-V Device Absolute Maximum Ratings Note (1) |                            |                              |      |      |      |  |

|--------------------------------------------------------------------|----------------------------|------------------------------|------|------|------|--|

| Symbol                                                             | Parameter                  | Conditions                   | Min  | Max  | Unit |  |

| V <sub>CC</sub>                                                    | Supply voltage             | With respect to ground (2)   | -0.5 | 4.6  | V    |  |

| V <sub>I</sub>                                                     | DC input voltage           |                              | -2.0 | 5.75 | ٧    |  |

| I <sub>OUT</sub>                                                   | DC output current, per pin |                              | -25  | 25   | mA   |  |

| T <sub>STG</sub>                                                   | Storage temperature        | No bias                      | -65  | 150  | ° C  |  |

| T <sub>AMB</sub>                                                   | Ambient temperature        | Under bias                   | -65  | 135  | ° C  |  |

| T <sub>J</sub>                                                     | Junction temperature       | PQFP, PLCC, and BGA packages |      | 135  | ° C  |  |

| Table 1            | Table 16. FLEX 6000 3.3-V Device Recommended Operating Conditions |                    |             |                   |      |  |  |

|--------------------|-------------------------------------------------------------------|--------------------|-------------|-------------------|------|--|--|

| Symbol             | Parameter                                                         | Conditions         | Min         | Max               | Unit |  |  |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers               | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | V    |  |  |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 3.3-V operation                | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | V    |  |  |

|                    | Supply voltage for output buffers, 2.5-V operation                | (3), (4)           | 2.30 (2.30) | 2.70 (2.70)       | V    |  |  |

| VI                 | Input voltage                                                     |                    | -0.5        | 5.75              | ٧    |  |  |

| Vo                 | Output voltage                                                    |                    | 0           | V <sub>CCIO</sub> | V    |  |  |

| $T_J$              | Operating temperature                                             | For commercial use | 0           | 85                | ° C  |  |  |

|                    |                                                                   | For industrial use | -40         | 100               | °C   |  |  |

| t <sub>R</sub>     | Input rise time                                                   |                    |             | 40                | ns   |  |  |

| t <sub>F</sub>     | Input fall time                                                   |                    |             | 40                | ns   |  |  |

| Symbol           | Parameter                                | Conditions                                                   | Min                     | Тур | Max  | Unit |

|------------------|------------------------------------------|--------------------------------------------------------------|-------------------------|-----|------|------|

| V <sub>IH</sub>  | High-level input voltage                 |                                                              | 1.7                     |     | 5.75 | ٧    |

| V <sub>IL</sub>  | Low-level input voltage                  |                                                              | -0.5                    |     | 0.8  | ٧    |

| V <sub>OH</sub>  | 3.3-V high-level TTL output voltage      | $I_{OH} = -8 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7)   | 2.4                     |     |      | V    |

|                  | 3.3-V high-level CMOS output voltage     | $I_{OH} = -0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7) | V <sub>CCIO</sub> - 0.2 |     |      | V    |

|                  | 2.5-V high-level output voltage          | $I_{OH} = -100 \mu A DC, V_{CCIO} = 2.30 V (7)$              | 2.1                     |     |      | ٧    |

|                  |                                          | I <sub>OH</sub> = -1 mA DC, V <sub>CCIO</sub> = 2.30 V (7)   | 2.0                     |     |      | ٧    |

|                  |                                          | $I_{OH} = -2 \text{ mA DC}, V_{CCIO} = 2.30 \text{ V}$ (7)   | 1.7                     |     |      | ٧    |

| V <sub>OL</sub>  | 3.3-V low-level TTL output voltage       | $I_{OL} = 8 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V } (8)$   |                         |     | 0.45 | V    |

|                  | 3.3-V low-level CMOS output voltage      | $I_{OL} = 0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V } (8)$ |                         |     | 0.2  | V    |

|                  | 2.5-V low-level output voltage           | I <sub>OL</sub> = 100 μA DC, V <sub>CCIO</sub> = 2.30 V (8)  |                         |     | 0.2  | ٧    |

|                  |                                          | I <sub>OL</sub> = 1 mA DC, V <sub>CCIO</sub> = 2.30 V (8)    |                         |     | 0.4  | ٧    |

|                  |                                          | I <sub>OL</sub> = 2 mA DC, V <sub>CCIO</sub> = 2.30 V (8)    |                         |     | 0.7  | ٧    |

| I <sub>I</sub>   | Input pin leakage current                | V <sub>I</sub> = 5.3 V to ground (8)                         | -10                     |     | 10   | μΑ   |

| I <sub>OZ</sub>  | Tri-stated I/O pin leakage current       | $V_O = 5.3 \text{ V to ground } (8)$                         | -10                     |     | 10   | μΑ   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby) | V <sub>I</sub> = ground, no load                             |                         | 0.5 | 5    | mA   |

| Table 1            | Table 18. FLEX 6000 3.3-V Device CapacitanceNote (9) |                                     |     |     |      |

|--------------------|------------------------------------------------------|-------------------------------------|-----|-----|------|

| Symbol             | Parameter                                            | Conditions                          | Min | Max | Unit |

| C <sub>IN</sub>    | Input capacitance for I/O pin                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |

| C <sub>INCLK</sub> | Input capacitance for dedicated input                | $V_{IN} = 0 V$ , $f = 1.0 MHz$      |     | 12  | pF   |

| C <sub>OUT</sub>   | Output capacitance                                   | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) The minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum V<sub>CC</sub> rise time is 100 ms. V<sub>CC</sub> must rise monotonically.

(5) Typical values are for T<sub>A</sub> = 25° C and V<sub>CC</sub> = 3.3 V.

(6) These values are specified under Table 16 on page 33.

(7) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current.

- (8) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (9) Capacitance is sample-tested only.

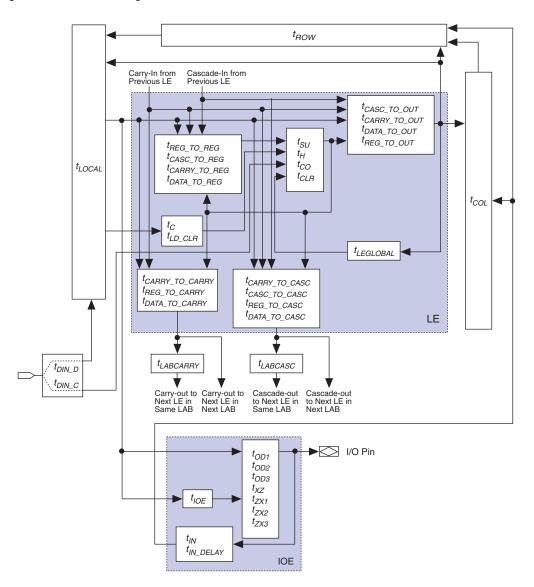

### **Timing Model**

The continuous, high-performance FastTrack Interconnect routing resources ensure predictable performance and accurate simulation and timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

Device performance can be estimated by following the signal path from a source, through the interconnect, to the destination. For example, the registered performance between two LEs on the same row can be calculated by adding the following parameters:

- LE register clock-to-output delay ( $t_{CO} + t_{REG\_TO\_OUT}$ )

- Routing delay  $(t_{ROW} + t_{LOCAL})$

- LE LUT delay ( $t_{DATA\_TO\_REG}$ )

- LE register setup time  $(t_{SU})$

The routing delay depends on the placement of the source and destination LEs. A more complex registered path may involve multiple combinatorial LEs between the source and destination LEs.

Timing simulation and delay prediction are available with the Simulator and Timing Analyzer, or with industry-standard EDA tools. The Simulator offers both pre-synthesis functional simulation to evaluate logic design accuracy and post-synthesis timing simulation with 0.1-ns resolution. The Timing Analyzer provides point-to-point timing delay information, setup and hold time analysis, and device-wide performance analysis.

Figure 19 shows the overall timing model, which maps the possible routing paths to and from the various elements of the FLEX 6000 device.

Figure 19. FLEX 6000 Timing Model

| Table 23. External Timing Parameters |                                                                                 |            |  |  |

|--------------------------------------|---------------------------------------------------------------------------------|------------|--|--|

| Symbol                               | Parameter                                                                       | Conditions |  |  |

| t <sub>INSU</sub>                    | Setup time with global clock at LE register                                     | (8)        |  |  |

| t <sub>INH</sub>                     | Hold time with global clock at LE register                                      | (8)        |  |  |

| t <sub>оитсо</sub>                   | Clock-to-output delay with global clock with LE register using FastFLEX I/O pin | (8)        |  |  |

#### *Notes to tables:*

- Microparameters are timing delays contributed by individual architectural elements and cannot be measured explicitly.

- (2) Operating conditions:

- $\hat{V_{CCIO}} = \widecheck{5}.0~V \pm 5\%$  for commercial use in 5.0-V FLEX 6000 devices.

- $V_{CCIO} = 5.0 \text{ V} \pm 10\%$  for industrial use in 5.0-V FLEX 6000 devices.

- $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial or industrial use in 3.3-V FLEX 6000 devices.

- (3) Operating conditions:

- $\hat{V_{CCIO}} = 3.3 \text{ V} \pm 10\%$  for commercial or industrial use in 5.0-V FLEX 6000 devices.

- $V_{CCIO}$  = 2.5 V ±0.2 V for commercial or industrial use in 3.3-V FLEX 6000 devices.

- (4) Operating conditions:

- $V_{\text{CCIO}} = 2.5 \text{ V}, 3.3 \text{ V}, \text{ or } 5.0 \text{ V}.$

- (5) These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing analysis are required to determine actual worst-case performance.

- (6) This timing parameter shows the delay of a register-to-register test pattern and is used to determine speed grades. There are 12 LEs, including source and destination registers. The row and column interconnects between the registers vary in length.

- 7) This timing parameter is shown for reference and is specified by characterization.

- (8) This timing parameter is specified by characterization.

Tables 24 through 28 show the timing information for EPF6010A and EPF6016A devices.

| Parameter                 | Speed Grade |     |     |     |     |     |    |  |  |

|---------------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                           | -1          |     | -2  |     | -3  |     |    |  |  |

|                           | Min         | Max | Min | Max | Min | Max |    |  |  |

| treg_to_reg               |             | 1.2 |     | 1.3 |     | 1.7 | ns |  |  |

| t <sub>CASC_TO_REG</sub>  |             | 0.9 |     | 1.0 |     | 1.2 | ns |  |  |

| t <sub>CARRY_TO_REG</sub> |             | 0.9 |     | 1.0 |     | 1.2 | ns |  |  |

| t <sub>DATA_TO_REG</sub>  |             | 1.1 |     | 1.2 |     | 1.5 | ns |  |  |

| t <sub>CASC_TO_OUT</sub>  |             | 1.3 |     | 1.4 |     | 1.8 | ns |  |  |

| t <sub>CARRY_TO_OUT</sub> |             | 1.6 |     | 1.8 |     | 2.3 | ns |  |  |

| <sup>t</sup> DATA_TO_OUT  |             | 1.7 |     | 2.0 |     | 2.5 | ns |  |  |

| t <sub>REG_TO_OUT</sub>   |             | 0.4 |     | 0.4 |     | 0.5 | ns |  |  |

| t <sub>su</sub>           | 0.9         |     | 1.0 |     | 1.3 |     | ns |  |  |

| t <sub>H</sub>            | 1.4         |     | 1.7 |     | 2.1 |     | ns |  |  |

| Parameter                 | Speed Grade |     |     |     |     |     |    |  |  |

|---------------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                           | -1          |     | -2  |     | -3  |     |    |  |  |

|                           | Min         | Max | Min | Max | Min | Max |    |  |  |

| t <sub>co</sub>           |             | 0.3 |     | 0.4 |     | 0.4 | ns |  |  |

| t <sub>CLR</sub>          |             | 0.4 |     | 0.4 |     | 0.5 | ns |  |  |

| t <sub>C</sub>            |             | 1.8 |     | 2.1 |     | 2.6 | ns |  |  |

| t <sub>LD_CLR</sub>       |             | 1.8 |     | 2.1 |     | 2.6 | ns |  |  |

| tCARRY_TO_CARRY           |             | 0.1 |     | 0.1 |     | 0.1 | ns |  |  |

| tREG_TO_CARRY             |             | 1.6 |     | 1.9 |     | 2.3 | ns |  |  |

| tDATA_TO_CARRY            |             | 2.1 |     | 2.5 |     | 3.0 | ns |  |  |

| tCARRY_TO_CASC            |             | 1.0 |     | 1.1 |     | 1.4 | ns |  |  |

| tcasc_to_casc             |             | 0.5 |     | 0.6 |     | 0.7 | ns |  |  |

| tREG_TO_CASC              |             | 1.4 |     | 1.7 |     | 2.1 | ns |  |  |

| t <sub>DATA_TO_CASC</sub> |             | 1.1 |     | 1.2 |     | 1.5 | ns |  |  |

| <sup>t</sup> ch           | 2.5         |     | 3.0 |     | 3.5 |     | ns |  |  |

| <sup>t</sup> CL           | 2.5         |     | 3.0 |     | 3.5 |     | ns |  |  |

| Parameter             | Speed Grade |     |     |     |     |     |    |  |  |

|-----------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                       | -1          |     | -2  |     | -3  |     |    |  |  |

|                       | Min         | Max | Min | Max | Min | Max |    |  |  |

| t <sub>OD1</sub>      |             | 1.9 |     | 2.2 |     | 2.7 | ns |  |  |

| t <sub>OD2</sub>      |             | 4.1 |     | 4.8 |     | 5.8 | ns |  |  |

| t <sub>OD3</sub>      |             | 5.8 |     | 6.8 |     | 8.3 | ns |  |  |

| $t_{XZ}$              |             | 1.4 |     | 1.7 |     | 2.1 | ns |  |  |

| t <sub>XZ1</sub>      |             | 1.4 |     | 1.7 |     | 2.1 | ns |  |  |

| t <sub>XZ2</sub>      |             | 3.6 |     | 4.3 |     | 5.2 | ns |  |  |

| t <sub>XZ3</sub>      |             | 5.3 |     | 6.3 |     | 7.7 | ns |  |  |

| t <sub>IOE</sub>      |             | 0.5 |     | 0.6 |     | 0.7 | ns |  |  |

| t <sub>IN</sub>       |             | 3.6 |     | 4.1 |     | 5.1 | ns |  |  |

| <sup>t</sup> IN DELAY |             | 4.8 |     | 5.4 |     | 6.7 | ns |  |  |

| Parameter             | Speed Grade |     |     |     |     |     |    |  |  |

|-----------------------|-------------|-----|-----|-----|-----|-----|----|--|--|

|                       | -1          |     | -2  |     | -3  |     |    |  |  |

|                       | Min         | Max | Min | Max | Min | Max |    |  |  |

| t <sub>LOCAL</sub>    |             | 0.7 |     | 0.7 |     | 1.0 | ns |  |  |

| t <sub>ROW</sub>      |             | 2.9 |     | 3.2 |     | 3.2 | ns |  |  |

| t <sub>COL</sub>      |             | 1.2 |     | 1.3 |     | 1.4 | ns |  |  |

| t <sub>DIN_D</sub>    |             | 5.4 |     | 5.7 |     | 6.4 | ns |  |  |

| t <sub>DIN_C</sub>    |             | 4.3 |     | 5.0 |     | 6.1 | ns |  |  |

| t<br>LEGLOBAL         |             | 2.6 |     | 3.0 |     | 3.7 | ns |  |  |

| t <sub>LABCARRY</sub> |             | 0.7 |     | 0.8 |     | 0.9 | ns |  |  |

| t <sub>LABCASC</sub>  |             | 1.3 |     | 1.4 |     | 1.8 | ns |  |  |

| Table 27. External Reference Timing Parameters for EPF6010A & EPF6016A Devices |          |             |      |     |      |     |      |    |  |

|--------------------------------------------------------------------------------|----------|-------------|------|-----|------|-----|------|----|--|

| Parameter                                                                      | Device   | Speed Grade |      |     |      |     |      |    |  |

|                                                                                | -1       |             | -2   |     | -3   |     |      |    |  |

|                                                                                |          | Min         | Max  | Min | Max  | Min | Max  |    |  |

| t <sub>1</sub>                                                                 | EPF6010A |             | 37.6 |     | 43.6 |     | 53.7 | ns |  |

|                                                                                | EPF6016A |             | 38.0 |     | 44.0 |     | 54.1 | ns |  |

| Table 28. Externa  | Table 28. External Timing Parameters for EPF6010A & EPF6016A Devices |     |         |     |         |      |    |  |

|--------------------|----------------------------------------------------------------------|-----|---------|-----|---------|------|----|--|

| Parameter          | Speed Grade                                                          |     |         |     |         |      |    |  |

|                    | -1                                                                   |     | -2      |     | -3      |      |    |  |

|                    | Min                                                                  | Max | Min     | Max | Min     | Max  |    |  |

| t <sub>INSU</sub>  | 2.1 (1)                                                              |     | 2.4 (1) |     | 3.3 (1) |      | ns |  |

| t <sub>INH</sub>   | 0.2 (2)                                                              |     | 0.3 (2) |     | 0.1 (2) |      | ns |  |

| t <sub>оитсо</sub> | 2.0                                                                  | 7.1 | 2.0     | 8.2 | 2.0     | 10.1 | ns |  |

#### Notes:

Setup times are longer when the *Increase Input Delay* option is turned on. The setup time values are shown with the *Increase Input Delay* option turned off.

Hold time is zero when the *Increase Input Delay* option is turned on.

Tables 29 through 33 show the timing information for EPF6016 devices.

| Parameter                   | Speed Grade |     |     |     |    |  |  |

|-----------------------------|-------------|-----|-----|-----|----|--|--|

|                             | -           | 2   | -;  |     |    |  |  |

|                             | Min         | Max | Min | Max |    |  |  |

| t <sub>REG_TO_REG</sub>     |             | 2.2 |     | 2.8 | ns |  |  |

| t <sub>CASC_TO_REG</sub>    |             | 0.9 |     | 1.2 | ns |  |  |

| t <sub>CARRY_TO_REG</sub>   |             | 1.6 |     | 2.1 | ns |  |  |

| t <sub>DATA_TO_REG</sub>    |             | 2.4 |     | 3.0 | ns |  |  |

| t <sub>CASC_TO_OUT</sub>    |             | 1.3 |     | 1.7 | ns |  |  |

| t <sub>CARRY_TO_OUT</sub>   |             | 2.4 |     | 3.0 | ns |  |  |

| t <sub>DATA_TO_OUT</sub>    |             | 2.7 |     | 3.4 | ns |  |  |

| t <sub>REG_TO_OUT</sub>     |             | 0.3 |     | 0.5 | ns |  |  |

| $t_{SU}$                    | 1.1         |     | 1.6 |     | ns |  |  |

| t <sub>H</sub>              | 1.8         |     | 2.3 |     | ns |  |  |

| $t_{CO}$                    |             | 0.3 |     | 0.4 | ns |  |  |

| t <sub>CLR</sub>            |             | 0.5 |     | 0.6 | ns |  |  |

| $t_C$                       |             | 1.2 |     | 1.5 | ns |  |  |

| t <sub>LD_CLR</sub>         |             | 1.2 |     | 1.5 | ns |  |  |

| t <sub>CARRY_TO_CARRY</sub> |             | 0.2 |     | 0.4 | ns |  |  |

| t <sub>REG_TO_CARRY</sub>   |             | 0.8 |     | 1.1 | ns |  |  |

| t <sub>DATA_TO_CARRY</sub>  |             | 1.7 |     | 2.2 | ns |  |  |

| t <sub>CARRY_TO_CASC</sub>  |             | 1.7 |     | 2.2 | ns |  |  |

| t <sub>CASC_TO_CASC</sub>   |             | 0.9 |     | 1.2 | ns |  |  |

| t <sub>REG_TO_CASC</sub>    |             | 1.6 |     | 2.0 | ns |  |  |

| t <sub>DATA_TO_CASC</sub>   |             | 1.7 |     | 2.1 | ns |  |  |

| t <sub>CH</sub>             | 4.0         |     | 4.0 |     | ns |  |  |

| $t_{CL}$                    | 4.0         |     | 4.0 |     | ns |  |  |

| Parameter        | Speed Grade |     |     |     |    |  |

|------------------|-------------|-----|-----|-----|----|--|

|                  | -2          |     | -   | 1   |    |  |

|                  | Min         | Max | Min | Max |    |  |

| t <sub>OD1</sub> |             | 2.3 |     | 2.8 | ns |  |

| t <sub>OD2</sub> |             | 4.6 |     | 5.1 | ns |  |

This calculation provides an  $I_{CC}$  estimate based on typical conditions with no output load. The actual  $I_{CC}$  should be verified during operation because this measurement is sensitive to the actual pattern in the device and the environmental operating conditions.

To better reflect actual designs, the power model (and the constant K in the power calculation equations shown above) for continuous interconnect FLEX devices assumes that LEs drive FastTrack Interconnect channels. In contrast, the power model of segmented FPGAs assumes that all LEs drive only one short interconnect segment. This assumption may lead to inaccurate results, compared to measured power consumption for an actual design in a segmented interconnect FPGA.

Figure 20 shows the relationship between the current and operating frequency for EPF6010A, EPF6016, EPF6016A, and EPF6024A devices.