Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 196                                                        |

| Number of Logic Elements/Cells | 1960                                                       |

| Total RAM Bits                 | -                                                          |

| Number of I/O                  | 199                                                        |

| Number of Gates                | 24000                                                      |

| Voltage - Supply               | 3V ~ 3.6V                                                  |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 240-BFQFP                                                  |

| Supplier Device Package        | 240-PQFP (32x32)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf6024aqc240-1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

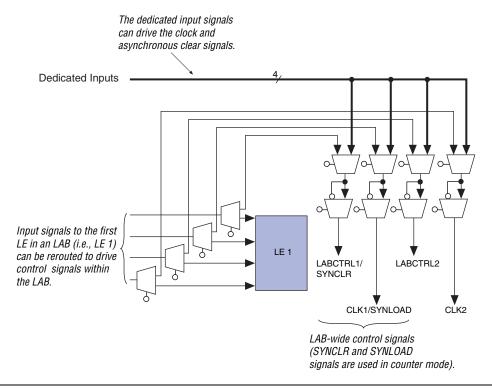

Figure 3. LAB Control Signals

#### **Logic Element**

An LE, the smallest unit of logic in the FLEX 6000 architecture, has a compact size that provides efficient logic usage. Each LE contains a four-input LUT, which is a function generator that can quickly implement any function of four variables. An LE contains a programmable flipflop, carry and cascade chains. Additionally, each LE drives both the local and the FastTrack Interconnect. See Figure 4.

#### Carry Chain

The carry chain provides a very fast (0.1 ns) carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the FLEX 6000 architecture to implement high-speed counters, adders, and comparators of arbitrary width. Carry chain logic can be created automatically by the Altera software during design processing, or manually by the designer during design entry. Parameterized functions such as LPM and DesignWare functions automatically take advantage of carry chains for the appropriate functions.

Because the first LE of each LAB can generate control signals for that LAB, the first LE in each LAB is not included in carry chains. In addition, the inputs of the first LE in each LAB may be used to generate synchronous clear and load enable signals for counters implemented with carry chains.

Carry chains longer than nine LEs are implemented automatically by linking LABs together. For enhanced fitting, a long carry chain skips alternate LABs in a row. A carry chain longer than one LAB skips either from an even-numbered LAB to another even-numbered LAB, or from an odd-numbered LAB to another odd-numbered LAB. For example, the last LE of the first LAB in a row carries to the second LE of the third LAB in the row. In addition, the carry chain does not cross the middle of the row. For instance, in the EPF6016 device, the carry chain stops at the 11th LAB in a row and a new carry chain begins at the 12th LAB.

Figure 5 shows how an n-bit full adder can be implemented in n+1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. Although the register can be bypassed for simple adders, it can be used for an accumulator function. Another portion of the LUT and the carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is driven onto the FastTrack Interconnect.

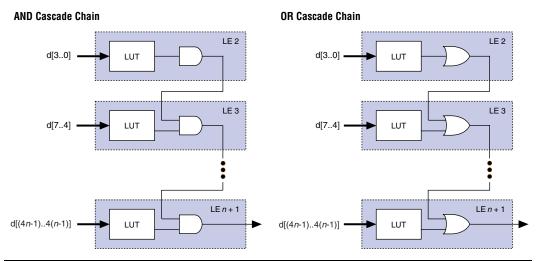

Figure 6. Cascade Chain Operation

#### LE Operating Modes

The FLEX 6000 LE can operate in one of the following three modes:

- Normal mode

- Arithmetic mode

- Counter mode

Each of these modes uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, synchronous clear, and synchronous load control for the register. The Altera software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions to use an LE operating mode for optimal performance.

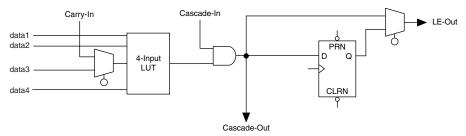

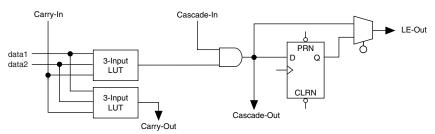

Figure 7 shows the LE operating modes.

Figure 7. LE Operating Modes

#### **Normal Mode**

#### **Arithmetic Mode**

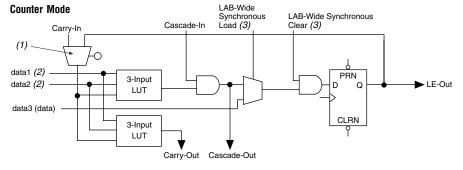

#### Notes:

- (1) The register feedback multiplexer is available on LE 2 of each LAB.

- (2) The data1 and data2 input signals can supply a clock enable, up or down control, or register feedback signals for all LEs other than the second LE in an LAB.

- (3) The LAB-wide synchronous clear and LAB-wide synchronous load affect all registers in an LAB.

#### **Normal Mode**

The normal mode is suitable for general logic applications, combinatorial functions, or wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a 4-input LUT. The Altera software automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal.

#### Arithmetic Mode

The arithmetic mode is ideal for implementing adders, accumulators, and comparators. An LE in arithmetic mode uses two 3-input LUTs. One LUT computes a 3-input function; the other generates a carry output. As shown in Figure 7, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, when implementing an adder, this output is the sum of three signals: DATA1, DATA2, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain.

The Altera software implements logic functions to use the arithmetic mode automatically where appropriate; the designer does not have to decide how the carry chain will be used.

#### **Counter Mode**

The counter mode offers counter enable, synchronous up/down control, synchronous clear, and synchronous load options. The counter enable and synchronous up/down control signals are generated from the data inputs of the LAB local interconnect. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. Consequently, if any of the LEs in a LAB use counter mode, other LEs in that LAB must be used as part of the same counter or be used for a combinatorial function. In addition, the Altera software automatically places registers that are not in the counter into other LABs.

The counter mode uses two 3-input LUTs: one generates the counter data and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading, and another AND gate provides synchronous clearing. If the cascade function is used by an LE in counter mode, the synchronous clear or load will override any signal carried on the cascade chain. The synchronous clear overrides the synchronous load.

Either the counter enable or the up/down control may be used for a given counter. Moreover, the synchronous load can be used as a count enable by routing the register output into the data input automatically when requested by the designer.

The second LE of each LAB has a special function for counter mode; the carry-in of the LE can be driven by a fast feedback path from the register. This function gives a faster counter speed for counter carry chains starting in the second LE of an LAB.

The Altera software implements functions to use the counter mode automatically where appropriate. The designer does not have to decide how the carry chain will be used.

#### Internal Tri-State Emulation

Internal tri-state emulation provides internal tri-states without the limitations of a physical tri-state bus. In a physical tri-state bus, the tri-state buffers' output enable (OE) signals select which signal drives the bus. However, if multiple OE signals are active, contending signals can be driven onto the bus. Conversely, if no OE signals are active, the bus will float. Internal tri-state emulation resolves contending tri-state buffers to a low value and floating buses to a high value, thereby eliminating these problems. The Altera software automatically implements tri-state bus functionality with a multiplexer.

#### Clear & Preset Logic Control

Logic for the programmable register's clear and preset functions is controlled by the LAB-wide signals LABCTRL1 and LABCTRL2. The LE register has an asynchronous clear that can implement an asynchronous preset. Either LABCTRL1 or LABCTRL2 can control the asynchronous clear or preset. Because the clear and preset functions are active-low, the Altera software automatically assigns a logic high to an unused clear or preset signal. The clear and preset logic is implemented in either the asynchronous clear or asynchronous preset mode, which is chosen during design entry (see Figure 8).

Each LE FastTrack Interconnect output can drive six row channels. Each local channel driven by an LE can Each LE output signal driving drive two column the FastTrack Interconnect can channels. drive two column channels. At each intersection, four row channels can Row drive column channels. Interconnect Each local channel driven by an LE can drive four row channels. Row interconnect drives the local interconnect. From Adjacent Local Interconnect Local Interconnect Column Interconnect Any column channel can drive six row channels.

An LE can be driven by any signal from two local interconnect areas.

Figure 10. LAB Connections to Row & Column Interconnects

For improved routability, the row interconnect consists of full-length and half-length channels. The full-length channels connect to all LABs in a row; the half-length channels connect to the LABs in half of the row. In addition to providing a predictable, row-wide interconnect, this architecture provides increased routing resources. Two neighboring LABs can be connected using a half-length channel, which saves the other half of the channel for the other half of the row. One-third of the row channels are half-length channels.

Table 5 summarizes the FastTrack Interconnect resources available in each FLEX 6000 device.

| Table 5. FLEX 600   | Table 5. FLEX 6000 FastTrack Interconnect Resources |                     |         |                        |  |  |

|---------------------|-----------------------------------------------------|---------------------|---------|------------------------|--|--|

| Device              | Rows                                                | Channels per<br>Row | Columns | Channels per<br>Column |  |  |

| EPF6010A            | 4                                                   | 144                 | 22      | 20                     |  |  |

| EPF6016<br>EPF6016A | 6                                                   | 144                 | 22      | 20                     |  |  |

| EPF6024A            | 7                                                   | 186                 | 28      | 30                     |  |  |

In addition to general-purpose I/O pins, FLEX 6000 devices have four dedicated input pins that provide low-skew signal distribution across the device. These four inputs can be used for global clock and asynchronous clear control signals. These signals are available as control signals for all LEs in the device. The dedicated inputs can also be used as general-purpose data inputs because they can feed the local interconnect of each LAB in the device. Using dedicated inputs to route data signals provides a fast path for high fan-out signals.

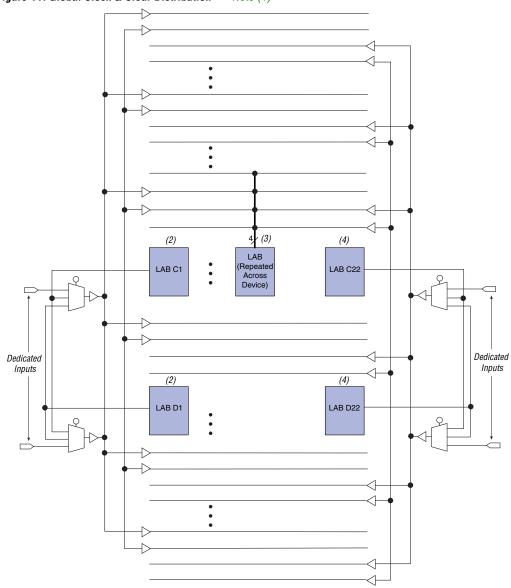

The local interconnect from LABs located at either end of two rows can drive a global control signal. For instance, in an EPF6016 device, LABs C1, D1, C22, and D22 can all drive global control signals. When an LE drives a global control signal, the dedicated input pin that drives that signal cannot be used. Any LE in the device can drive a global control signal by driving the FastTrack Interconnect into the appropriate LAB. To minimize delay, however, the Altera software places the driving LE in the appropriate LAB. The LE-driving-global signal feature is optimized for speed for control signals; regular data signals are better routed on the FastTrack Interconnect and do not receive any advantage from being routed on global signals. This LE-driving-global control signal feature is controlled by the designer and is not used automatically by the Altera software. See Figure 11.

Figure 11. Global Clock & Clear Distribution Note (1)

#### Notes:

- The global clock and clear distribution signals are shown for EPF6016 and EPF6016A devices. In EPF6010A devices, LABs in rows B and C drive global signals. In EPF6024A devices, LABs in rows C and E drive global signals. The local interconnect from LABs C1 and D1 can drive two global control signals on the left side.

- (2)

- Global signals drive into every LAB as clock, asynchronous clear, preset, and data signals. (3)

- The local interconnect from LABs C22 and D22 can drive two global control signals on the right side.

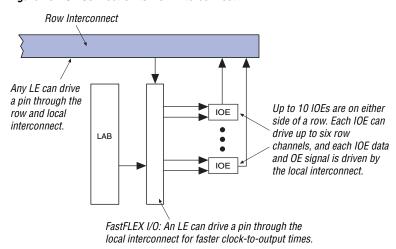

Each IOE drives a row or column interconnect when used as an input or bidirectional pin. A row IOE can drive up to six row lines; a column IOE can drive up to two column lines. The input path from the I/O pad to the FastTrack Interconnect has a programmable delay element that can be used to guarantee a zero hold time. Depending on the placement of the IOE relative to what it is driving, the designer may choose to turn on the programmable delay to ensure a zero hold time. Figure 13 shows how an IOE connects to a row interconnect, and Figure 14 shows how an IOE connects to a column interconnect.

Figure 13. IOE Connection to Row Interconnect

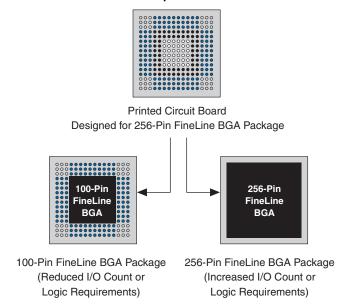

Figure 15. SameFrame Pin-Out Example

Table 6 lists the 3.3-V FLEX 6000 devices with the Same Frame pin-out feature.

| Table 6. 3.3-V FLEX 6000 Devices with SameFrame Pin-Outs |   |   |  |  |  |

|----------------------------------------------------------|---|---|--|--|--|

| Device 100-Pin FineLine BGA 256-Pin FineLine BGA         |   |   |  |  |  |

| EPF6016A                                                 | V | v |  |  |  |

| EPF6024A                                                 |   | V |  |  |  |

# Output Configuration

This section discusses slew-rate control, the MultiVolt I/O interface, power sequencing, and hot-socketing for FLEX 6000 devices.

#### **Slew-Rate Control**

The output buffer in each IOE has an adjustable output slew-rate that can be configured for low-noise or high-speed performance. A slower slew-rate reduces system noise and adds a maximum delay of 6.8 ns. The fast slew-rate should be used for speed-critical outputs in systems that are adequately protected against noise. Designers can specify the slew-rate on a pin-by-pin basis during design entry or assign a default slew rate to all pins on a device-wide basis. The slew-rate setting affects only the falling edge of the output.

| Table 1          | Table 15. FLEX 6000 3.3-V Device Absolute Maximum Ratings Note (1) |                              |      |      |      |

|------------------|--------------------------------------------------------------------|------------------------------|------|------|------|

| Symbol           | Parameter                                                          | Conditions                   | Min  | Max  | Unit |

| V <sub>CC</sub>  | Supply voltage                                                     | With respect to ground (2)   | -0.5 | 4.6  | V    |

| V <sub>I</sub>   | DC input voltage                                                   |                              | -2.0 | 5.75 | ٧    |

| I <sub>OUT</sub> | DC output current, per pin                                         |                              | -25  | 25   | mA   |

| T <sub>STG</sub> | Storage temperature                                                | No bias                      | -65  | 150  | ° C  |

| T <sub>AMB</sub> | Ambient temperature                                                | Under bias                   | -65  | 135  | ° C  |

| T <sub>J</sub>   | Junction temperature                                               | PQFP, PLCC, and BGA packages |      | 135  | ° C  |

| Table 1            | 6. FLEX 6000 3.3-V Device Rec                       | ommended Operating Condition | ons         |                   |      |

|--------------------|-----------------------------------------------------|------------------------------|-------------|-------------------|------|

| Symbol             | Parameter                                           | Conditions                   | Min         | Max               | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)                     | 3.00 (3.00) | 3.60 (3.60)       | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 3.3-V operation  | (3), (4)                     | 3.00 (3.00) | 3.60 (3.60)       | V    |

|                    | Supply voltage for output buffers, 2.5-V operation  | (3), (4)                     | 2.30 (2.30) | 2.70 (2.70)       | V    |

| VI                 | Input voltage                                       |                              | -0.5        | 5.75              | ٧    |

| Vo                 | Output voltage                                      |                              | 0           | V <sub>CCIO</sub> | V    |

| $T_J$              | Operating temperature                               | For commercial use           | 0           | 85                | ° C  |

|                    |                                                     | For industrial use           | -40         | 100               | ° C  |

| t <sub>R</sub>     | Input rise time                                     |                              |             | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                     |                              |             | 40                | ns   |

| Symbol           | Parameter                                | Conditions                                                   | Min                     | Тур | Max  | Unit |

|------------------|------------------------------------------|--------------------------------------------------------------|-------------------------|-----|------|------|

| V <sub>IH</sub>  | High-level input voltage                 |                                                              | 1.7                     |     | 5.75 | ٧    |

| V <sub>IL</sub>  | Low-level input voltage                  |                                                              | -0.5                    |     | 0.8  | ٧    |

| V <sub>OH</sub>  | 3.3-V high-level TTL output voltage      | $I_{OH} = -8 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7)   | 2.4                     |     |      | V    |

|                  | 3.3-V high-level CMOS output voltage     | $I_{OH} = -0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7) | V <sub>CCIO</sub> - 0.2 |     |      | V    |

|                  | 2.5-V high-level output voltage          | $I_{OH} = -100 \mu A DC, V_{CCIO} = 2.30 V (7)$              | 2.1                     |     |      | ٧    |

|                  |                                          | I <sub>OH</sub> = -1 mA DC, V <sub>CCIO</sub> = 2.30 V (7)   | 2.0                     |     |      | ٧    |

|                  |                                          | $I_{OH} = -2 \text{ mA DC}, V_{CCIO} = 2.30 \text{ V} (7)$   | 1.7                     |     |      | ٧    |

| V <sub>OL</sub>  | 3.3-V low-level TTL output voltage       | $I_{OL} = 8 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V } (8)$   |                         |     | 0.45 | V    |

|                  | 3.3-V low-level CMOS output voltage      | $I_{OL} = 0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V } (8)$ |                         |     | 0.2  | V    |

|                  | 2.5-V low-level output voltage           | I <sub>OL</sub> = 100 μA DC, V <sub>CCIO</sub> = 2.30 V (8)  |                         |     | 0.2  | ٧    |

|                  |                                          | I <sub>OL</sub> = 1 mA DC, V <sub>CCIO</sub> = 2.30 V (8)    |                         |     | 0.4  | ٧    |

|                  |                                          | I <sub>OL</sub> = 2 mA DC, V <sub>CCIO</sub> = 2.30 V (8)    |                         |     | 0.7  | ٧    |

| I <sub>I</sub>   | Input pin leakage current                | V <sub>I</sub> = 5.3 V to ground (8)                         | -10                     |     | 10   | μΑ   |

| I <sub>OZ</sub>  | Tri-stated I/O pin leakage current       | $V_O = 5.3 \text{ V to ground } (8)$                         | -10                     |     | 10   | μΑ   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby) | V <sub>I</sub> = ground, no load                             |                         | 0.5 | 5    | mA   |

| Table 1            | 8. FLEX 6000 3.3-V Device Capa        | citance Note (9)                    | lote (9) |     |      |

|--------------------|---------------------------------------|-------------------------------------|----------|-----|------|

| Symbol             | Parameter                             | Conditions                          | Min      | Max | Unit |

| C <sub>IN</sub>    | Input capacitance for I/O pin         | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |          | 8   | pF   |

| C <sub>INCLK</sub> | Input capacitance for dedicated input | $V_{IN} = 0 V$ , $f = 1.0 MHz$      |          | 12  | pF   |

| C <sub>OUT</sub>   | Output capacitance                    | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |          | 8   | pF   |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) The minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum V<sub>CC</sub> rise time is 100 ms. V<sub>CC</sub> must rise monotonically.

(5) Typical values are for T<sub>A</sub> = 25° C and V<sub>CC</sub> = 3.3 V.

(6) These values are specified under Table 16 on page 33.

(7) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current.

- (8) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (9) Capacitance is sample-tested only.

| Symbol                | Parameter                                                                                 | Conditions     |

|-----------------------|-------------------------------------------------------------------------------------------|----------------|

| t <sub>OD1</sub>      | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = V <sub>CCINT</sub> | C1 = 35 pF (2) |

| t <sub>OD2</sub>      | Output buffer and pad delay, slow slew rate = off, V <sub>CCIO</sub> = low voltage        | C1 = 35 pF (3) |

| t <sub>OD3</sub>      | Output buffer and pad delay, slow slew rate = on                                          | C1 = 35 pF (4) |

| $t_{XZ}$              | Output buffer disable delay                                                               | C1 = 5 pF      |

| t <sub>ZX1</sub>      | Output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = V <sub>CCINT</sub>  | C1 = 35 pF (2) |

| $t_{ZX2}$             | Output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = low voltage         | C1 = 35 pF (3) |

| t <sub>ZX3</sub>      | IOE output buffer enable delay, slow slew rate = on                                       | C1 = 35 pF (4) |

| t <sub>IOE</sub>      | Output enable control delay                                                               |                |

| t <sub>IN</sub>       | Input pad and buffer to FastTrack Interconnect delay                                      |                |

| t <sub>IN_DELAY</sub> | Input pad and buffer to FastTrack Interconnect delay with additional delay turned on      |                |

| Table 21. Int         | Table 21. Interconnect Timing Microparameters      Note (1)                                                          |            |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Symbol                | Parameter                                                                                                            | Conditions |  |  |  |

| t <sub>LOCAL</sub>    | LAB local interconnect delay                                                                                         |            |  |  |  |

| t <sub>ROW</sub>      | Row interconnect routing delay                                                                                       | (5)        |  |  |  |

| t <sub>COL</sub>      | Column interconnect routing delay                                                                                    | (5)        |  |  |  |

| t <sub>DIN_D</sub>    | Dedicated input to LE data delay                                                                                     | (5)        |  |  |  |

| t <sub>DIN_C</sub>    | Dedicated input to LE control delay                                                                                  |            |  |  |  |

| t <sub>LEGLOBAL</sub> | LE output to LE control via internally-generated global signal delay                                                 | (5)        |  |  |  |

| t <sub>LABCARRY</sub> | Routing delay for the carry-out of an LE driving the carry-in signal of a different LE in a different LAB            |            |  |  |  |

| t <sub>LABCASC</sub>  | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |            |  |  |  |

| Table 22. External Reference Timing Parameters |                                                                                      |            |

|------------------------------------------------|--------------------------------------------------------------------------------------|------------|

| Symbol                                         | Parameter                                                                            | Conditions |

| t <sub>1</sub>                                 | Register-to-register test pattern                                                    | (6)        |

| t <sub>DRR</sub>                               | Register-to-register delay via 4 LEs, 3 row interconnects, and 4 local interconnects | (7)        |

| Table 23. External Timing Parameters |                                                                                 |            |

|--------------------------------------|---------------------------------------------------------------------------------|------------|

| Symbol                               | Parameter                                                                       | Conditions |

| t <sub>INSU</sub>                    | Setup time with global clock at LE register                                     | (8)        |

| t <sub>INH</sub>                     | Hold time with global clock at LE register                                      | (8)        |

| t <sub>оитсо</sub>                   | Clock-to-output delay with global clock with LE register using FastFLEX I/O pin | (8)        |

#### *Notes to tables:*

- Microparameters are timing delays contributed by individual architectural elements and cannot be measured explicitly.

- (2) Operating conditions:

- $\hat{V_{CCIO}} = \widecheck{5}.0~V \pm 5\%$  for commercial use in 5.0-V FLEX 6000 devices.

- $V_{CCIO} = 5.0 \text{ V} \pm 10\%$  for industrial use in 5.0-V FLEX 6000 devices.

- $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial or industrial use in 3.3-V FLEX 6000 devices.

- (3) Operating conditions:

- $\hat{V_{CCIO}} = 3.3 \text{ V} \pm 10\%$  for commercial or industrial use in 5.0-V FLEX 6000 devices.

- $V_{CCIO}$  = 2.5 V ±0.2 V for commercial or industrial use in 3.3-V FLEX 6000 devices.

- (4) Operating conditions:

- $V_{\text{CCIO}} = 2.5 \text{ V}, 3.3 \text{ V}, \text{ or } 5.0 \text{ V}.$

- (5) These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing analysis are required to determine actual worst-case performance.

- (6) This timing parameter shows the delay of a register-to-register test pattern and is used to determine speed grades. There are 12 LEs, including source and destination registers. The row and column interconnects between the registers vary in length.

- 7) This timing parameter is shown for reference and is specified by characterization.

- (8) This timing parameter is specified by characterization.

Tables 24 through 28 show the timing information for EPF6010A and EPF6016A devices.

| Parameter                 |     |     | Speed | Grade |     |     | Unit |

|---------------------------|-----|-----|-------|-------|-----|-----|------|

|                           | -   | 1   | -     | 2     | -   | 3   |      |

|                           | Min | Max | Min   | Max   | Min | Max |      |

| treg_to_reg               |     | 1.2 |       | 1.3   |     | 1.7 | ns   |

| t <sub>CASC_TO_REG</sub>  |     | 0.9 |       | 1.0   |     | 1.2 | ns   |

| t <sub>CARRY_TO_REG</sub> |     | 0.9 |       | 1.0   |     | 1.2 | ns   |

| t <sub>DATA_TO_REG</sub>  |     | 1.1 |       | 1.2   |     | 1.5 | ns   |

| t <sub>CASC_TO_OUT</sub>  |     | 1.3 |       | 1.4   |     | 1.8 | ns   |

| t <sub>CARRY_TO_OUT</sub> |     | 1.6 |       | 1.8   |     | 2.3 | ns   |

| <sup>t</sup> DATA_TO_OUT  |     | 1.7 |       | 2.0   |     | 2.5 | ns   |

| t <sub>REG_TO_OUT</sub>   |     | 0.4 |       | 0.4   |     | 0.5 | ns   |

| t <sub>SU</sub>           | 0.9 |     | 1.0   |       | 1.3 |     | ns   |

| t <sub>H</sub>            | 1.4 |     | 1.7   |       | 2.1 |     | ns   |

| Parameter             |     |     | Speed | Grade |     |     | Unit |

|-----------------------|-----|-----|-------|-------|-----|-----|------|

|                       | -1  |     | -2    |       | -3  |     | 1    |

|                       | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>LOCAL</sub>    |     | 0.7 |       | 0.7   |     | 1.0 | ns   |

| t <sub>ROW</sub>      |     | 2.9 |       | 3.2   |     | 3.2 | ns   |

| t <sub>COL</sub>      |     | 1.2 |       | 1.3   |     | 1.4 | ns   |

| t <sub>DIN_D</sub>    |     | 5.4 |       | 5.7   |     | 6.4 | ns   |

| t <sub>DIN_C</sub>    |     | 4.3 |       | 5.0   |     | 6.1 | ns   |

| t<br>LEGLOBAL         |     | 2.6 |       | 3.0   |     | 3.7 | ns   |

| t <sub>LABCARRY</sub> |     | 0.7 |       | 0.8   |     | 0.9 | ns   |

| t <sub>LABCASC</sub>  |     | 1.3 |       | 1.4   |     | 1.8 | ns   |

| Table 27. External Reference Timing Parameters for EPF6010A & EPF6016A Devices |          |             |       |     |      |     |      |      |

|--------------------------------------------------------------------------------|----------|-------------|-------|-----|------|-----|------|------|

| Parameter                                                                      | Device   | Speed Grade |       |     |      |     |      | Unit |

|                                                                                |          | -           | -1 -2 |     |      | -3  |      |      |

|                                                                                |          | Min         | Max   | Min | Max  | Min | Max  |      |

| t <sub>1</sub>                                                                 | EPF6010A |             | 37.6  |     | 43.6 |     | 53.7 | ns   |

|                                                                                | EPF6016A |             | 38.0  |     | 44.0 |     | 54.1 | ns   |

| Table 28. External Timing Parameters for EPF6010A & EPF6016A Devices |             |     |         |     |         |      |    |  |

|----------------------------------------------------------------------|-------------|-----|---------|-----|---------|------|----|--|

| Parameter                                                            | Speed Grade |     |         |     |         |      |    |  |

|                                                                      | -1          | -1  |         | -2  |         | 3    | ]  |  |

|                                                                      | Min         | Max | Min     | Max | Min     | Max  |    |  |

| t <sub>INSU</sub>                                                    | 2.1 (1)     |     | 2.4 (1) |     | 3.3 (1) |      | ns |  |

| t <sub>INH</sub>                                                     | 0.2 (2)     |     | 0.3 (2) |     | 0.1 (2) |      | ns |  |

| t <sub>оитсо</sub>                                                   | 2.0         | 7.1 | 2.0     | 8.2 | 2.0     | 10.1 | ns |  |

#### Notes:

Setup times are longer when the *Increase Input Delay* option is turned on. The setup time values are shown with the *Increase Input Delay* option turned off.

Hold time is zero when the *Increase Input Delay* option is turned on.

Tables 29 through 33 show the timing information for EPF6016 devices.

| Parameter                   | Speed Grade |     |     |     |    |  |

|-----------------------------|-------------|-----|-----|-----|----|--|

|                             | -2          |     | -;  | 3   | 1  |  |

|                             | Min         | Max | Min | Max |    |  |

| t <sub>REG_TO_REG</sub>     |             | 2.2 |     | 2.8 | ns |  |

| t <sub>CASC_TO_REG</sub>    |             | 0.9 |     | 1.2 | ns |  |

| t <sub>CARRY_TO_REG</sub>   |             | 1.6 |     | 2.1 | ns |  |

| t <sub>DATA_TO_REG</sub>    |             | 2.4 |     | 3.0 | ns |  |

| t <sub>CASC_TO_OUT</sub>    |             | 1.3 |     | 1.7 | ns |  |

| t <sub>CARRY_TO_OUT</sub>   |             | 2.4 |     | 3.0 | ns |  |

| t <sub>DATA_TO_OUT</sub>    |             | 2.7 |     | 3.4 | ns |  |

| t <sub>REG_TO_OUT</sub>     |             | 0.3 |     | 0.5 | ns |  |

| $t_{SU}$                    | 1.1         |     | 1.6 |     | ns |  |

| t <sub>H</sub>              | 1.8         |     | 2.3 |     | ns |  |

| $t_{CO}$                    |             | 0.3 |     | 0.4 | ns |  |

| t <sub>CLR</sub>            |             | 0.5 |     | 0.6 | ns |  |

| $t_C$                       |             | 1.2 |     | 1.5 | ns |  |

| t <sub>LD_CLR</sub>         |             | 1.2 |     | 1.5 | ns |  |

| t <sub>CARRY_TO_CARRY</sub> |             | 0.2 |     | 0.4 | ns |  |

| t <sub>REG_TO_CARRY</sub>   |             | 0.8 |     | 1.1 | ns |  |

| t <sub>DATA_TO_CARRY</sub>  |             | 1.7 |     | 2.2 | ns |  |

| t <sub>CARRY_TO_CASC</sub>  |             | 1.7 |     | 2.2 | ns |  |

| t <sub>CASC_TO_CASC</sub>   |             | 0.9 |     | 1.2 | ns |  |

| t <sub>REG_TO_CASC</sub>    |             | 1.6 |     | 2.0 | ns |  |

| t <sub>DATA_TO_CASC</sub>   |             | 1.7 |     | 2.1 | ns |  |

| t <sub>CH</sub>             | 4.0         |     | 4.0 |     | ns |  |

| $t_{CL}$                    | 4.0         |     | 4.0 |     | ns |  |

| Parameter        | Speed Grade |     |     |     |    |  |

|------------------|-------------|-----|-----|-----|----|--|

|                  | -2          |     | -3  |     | 1  |  |

|                  | Min         | Max | Min | Max |    |  |

| t <sub>OD1</sub> |             | 2.3 |     | 2.8 | ns |  |

| t <sub>OD2</sub> |             | 4.6 |     | 5.1 | ns |  |

| Parameter             |     | Speed | Grade |     | Unit |

|-----------------------|-----|-------|-------|-----|------|

|                       | -2  |       | -     | 3   | 1    |

|                       | Min | Max   | Min   | Max |      |

| OD3                   |     | 4.7   |       | 5.2 | ns   |

| XZ                    |     | 2.3   |       | 2.8 | ns   |

| ZX1                   |     | 2.3   |       | 2.8 | ns   |

| ZX2                   |     | 4.6   |       | 5.1 | ns   |

| ZX3                   |     | 4.7   |       | 5.2 | ns   |

| IOE                   |     | 0.5   |       | 0.6 | ns   |

| <sup>t</sup> in       |     | 3.3   |       | 4.0 | ns   |

| t <sub>IN DELAY</sub> |     | 4.6   |       | 5.6 | ns   |

| Parameter             | Speed Grade |     |     |     |    |  |

|-----------------------|-------------|-----|-----|-----|----|--|

|                       | -2          |     | -   | 3   | -  |  |

|                       | Min         | Max | Min | Max |    |  |

| t <sub>LOCAL</sub>    |             | 0.8 |     | 1.0 | ns |  |

| t <sub>ROW</sub>      |             | 2.9 |     | 3.3 | ns |  |

| t <sub>COL</sub>      |             | 2.3 |     | 2.5 | ns |  |

| t <sub>DIN_D</sub>    |             | 4.9 |     | 6.0 | ns |  |

| t <sub>DIN_C</sub>    |             | 4.8 |     | 6.0 | ns |  |

| t <sub>LEGLOBAL</sub> |             | 3.1 |     | 3.9 | ns |  |

| t <sub>LABCARRY</sub> |             | 0.4 |     | 0.5 | ns |  |

| t <sub>LABCASC</sub>  |             | 0.8 |     | 1.0 | ns |  |

| Table 32. External Referen | nce Timing Parai | meters for EPF60 | 116 Devices |      |    |

|----------------------------|------------------|------------------|-------------|------|----|

| Parameter                  |                  | Unit             |             |      |    |

|                            |                  | -2               |             |      |    |

|                            | Min              | Max              | Min         | Max  |    |

| t <sub>1</sub>             |                  | 53.0             |             | 65.0 | ns |

| t <sub>DRR</sub>           |                  | 16.0             |             | 20.0 | ns |

| Table 33. External Timing Parameters for EPF6016 Devices |     |             |     |     |    |  |  |  |

|----------------------------------------------------------|-----|-------------|-----|-----|----|--|--|--|

| Parameter                                                |     | Speed Grade |     |     |    |  |  |  |

|                                                          |     | -2          |     | -3  |    |  |  |  |

|                                                          | Min | Max         | Min | Max |    |  |  |  |

| t <sub>INSU</sub>                                        | 3.2 |             | 4.1 |     | ns |  |  |  |

| t <sub>INH</sub>                                         | 0.0 |             | 0.0 |     | ns |  |  |  |

| t <sub>оитсо</sub>                                       | 2.0 | 7.9         | 2.0 | 9.9 | ns |  |  |  |

Tables 34 through 38 show the timing information for EPF6024A devices.

| Parameter                   | Speed Grade |     |     |     |     |     |    |  |

|-----------------------------|-------------|-----|-----|-----|-----|-----|----|--|

|                             | -1          |     | -2  |     | -3  |     |    |  |

|                             | Min         | Max | Min | Max | Min | Max |    |  |

| t <sub>REG_TO_REG</sub>     |             | 1.2 |     | 1.3 |     | 1.6 | ns |  |

| t <sub>CASC_TO_REG</sub>    |             | 0.7 |     | 0.8 |     | 1.0 | ns |  |

| t <sub>CARRY_TO_REG</sub>   |             | 1.6 |     | 1.8 |     | 2.2 | ns |  |

| t <sub>DATA_TO_REG</sub>    |             | 1.3 |     | 1.4 |     | 1.7 | ns |  |

| t <sub>CASC_TO_OUT</sub>    |             | 1.2 |     | 1.3 |     | 1.6 | ns |  |

| t <sub>CARRY_TO_OUT</sub>   |             | 2.0 |     | 2.2 |     | 2.6 | ns |  |

| t <sub>DATA_TO_OUT</sub>    |             | 1.8 |     | 2.1 |     | 2.6 | ns |  |

| t <sub>REG_TO_OUT</sub>     |             | 0.3 |     | 0.3 |     | 0.4 | ns |  |

| t <sub>SU</sub>             | 0.9         |     | 1.0 |     | 1.2 |     | ns |  |

| t <sub>H</sub>              | 1.3         |     | 1.4 |     | 1.7 |     | ns |  |

| $t_{CO}$                    |             | 0.2 |     | 0.3 |     | 0.3 | ns |  |

| t <sub>CLR</sub>            |             | 0.3 |     | 0.3 |     | 0.4 | ns |  |

| $t_C$                       |             | 1.9 |     | 2.1 |     | 2.5 | ns |  |

| t <sub>LD_CLR</sub>         |             | 1.9 |     | 2.1 |     | 2.5 | ns |  |

| t <sub>CARRY_TO_CARRY</sub> |             | 0.2 |     | 0.2 |     | 0.3 | ns |  |

| t <sub>REG_TO_CARRY</sub>   |             | 1.4 |     | 1.6 |     | 1.9 | ns |  |

| t <sub>DATA_TO_CARRY</sub>  |             | 1.3 | _   | 1.4 |     | 1.7 | ns |  |

| t <sub>CARRY_TO_CASC</sub>  |             | 1.1 |     | 1.2 |     | 1.4 | ns |  |

| t <sub>CASC_TO_CASC</sub>   |             | 0.7 |     | 0.8 |     | 1.0 | ns |  |

| t <sub>REG_TO_CASC</sub>    |             | 1.4 |     | 1.6 |     | 1.9 | ns |  |

| t <sub>DATA_TO_CASC</sub>   |             | 1.0 |     | 1.1 |     | 1.3 | ns |  |

| t <sub>CH</sub>             | 2.5         |     | 3.0 |     | 3.5 |     | ns |  |

| t <sub>CL</sub>             | 2.5         |     | 3.0 |     | 3.5 |     | ns |  |

### Device Pin-Outs

See the Altera web site (http://www.altera.com) or the *Altera Digital Library* for pin-out information.