Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                               |

| Core Processor                  | MPC8xx                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 80MHz                                                                  |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10Mbps (4), 10/100Mbps (1)                                             |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 3.3V                                                                   |

| Operating Temperature           | -40°C ~ 115°C (TA)                                                     |

| Security Features               | -                                                                      |

| Package / Case                  | 357-BBGA                                                               |

| Supplier Device Package         | 357-PBGA (25x25)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc862tcvr80b |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- The MPC862/857T/857DSL provides enhanced ATM functionality over that of the MPC860SAR.

The MPC862/857T/857DSL adds major new features available in "enhanced SAR" (ESAR) mode, including the following:

- Improved operation, administration and maintenance (OAM) support

- OAM performance monitoring (PM) support

- Multiple APC priority levels available to support a range of traffic pace requirements

- ATM port-to-port switching capability without the need for RAM-based microcode

- Simultaneous MII (10/100Base-T) and UTOPIA (half-duplex) capability

- Optional statistical cell counters per PHY

- UTOPIA level 2 compliant interface with added FIFO buffering to reduce the total cell transmission time. (The earlier UTOPIA level 1 specification is also supported.)

- Multi-PHY support on the MPC857T

- Four PHY support on the MPC857DSL

- Parameter RAM for both SPI and I<sup>2</sup>C can be relocated without RAM-based microcode

- Supports full-duplex UTOPIA both master (ATM side) and slave (PHY side) operation using a "split" bus

- AAL2/VBR functionality is ROM-resident

- Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

- 32 address lines

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank

- Up to 30 wait states programmable per memory bank

- Glueless interface to Page mode/EDO/SDRAM, SRAM, EPROMs, flash EPROMs, and other memory devices.

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbyte–256 Mbyte)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers cascadable to be two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

- Fast Ethernet controller (FEC)

- Simultaneous MII (10/100Base-T) and UTOPIA operation when using the UTOPIA multiplexed bus.

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

#### **Features**

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC) from the PowerPC architecture

- Reset controller

- IEEE 1149.1 test access port (JTAG)

- Interrupts

- Seven external interrupt request (IRQ) lines

- 12 port pins with interrupt capability

- The MPC862P and MPC862T have 23 internal interrupt sources; the MPC857T and MPC857DSL have 20 internal interrupt sources

- Programmable priority between SCCs (MPC862P and MPC862T)

- Programmable highest priority request

- Communications processor module (CPM)

- RISC controller

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- Up to 8-Kbytes of dual-port RAM

- The MPC862P and MPC862T have 16 serial DMA (SDMA) channels; the MPC857T and MPC857DSL have 10 serial DMA (SDMA) channels

- Three parallel I/O registers with open-drain capability

- Four baud rate generators

- Independent (can be connected to any SCC or SMC)

- Allow changes during operation

- Autobaud support option

- The MPC862P and MPC862T have four SCCs (serial communication controller) The MPC857T and MPC857DSL have one SCC, SCC1; the MPC857DSL supports ethernet only

- Serial ATM capability on all SCCs

- Optional UTOPIA port on SCC4

- Ethernet/IEEE 802.3 optional on SCC1–4, supporting full 10-Mbps operation

- HDLC/SDLC

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support PPP (point-to-point protocol)

- AppleTalk

9

Table 2. Maximum Tolerated Ratings (continued)

(GND = 0 V)

| Rating                                           | Symbol              | Value           | Unit | Max Freq<br>(MHz) |

|--------------------------------------------------|---------------------|-----------------|------|-------------------|

| Input voltage <sup>2</sup>                       | V <sub>in</sub>     | GND-0.3 to VDDH | V    | -                 |

| Temperature <sup>3</sup> (standard) <sup>4</sup> | T <sub>A(min)</sub> | 0               | °C   | 100               |

|                                                  | T <sub>j(max)</sub> | 105             | °C   | 100               |

| Temperature <sup>3</sup> (extended)              | T <sub>A(min)</sub> | -40             | °C   | 80                |

|                                                  | T <sub>j(max)</sub> | 115             | °C   | 80                |

| Storage temperature range                        | T <sub>stg</sub>    | -55 to +150     | °C   | -                 |

<sup>&</sup>lt;sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{CC}$ ).

<sup>&</sup>lt;sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 5. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device.

**Caution**: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction applies to power-up and normal operation (that is, if the MPC862/857T/857DSL is unpowered, voltage greater than 2.5 V must not be applied to its inputs).

<sup>&</sup>lt;sup>3</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as junction temperature, T<sub>i</sub>.

<sup>&</sup>lt;sup>4</sup> JTAG is tested only at ambient, not at standard maximum or extended maximum.

# 7.2 Estimation with Junction-to-Case Thermal Resistance

Historically, the thermal resistance has frequently been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta IC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user adjusts the thermal environment to affect the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the air flow around the device, add a heat sink, change the mounting arrangement on the printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device. This thermal model is most useful for ceramic packages with heat sinks where some 90% of the heat flows through the case and the heat sink to the ambient environment. For most packages, a better model is required.

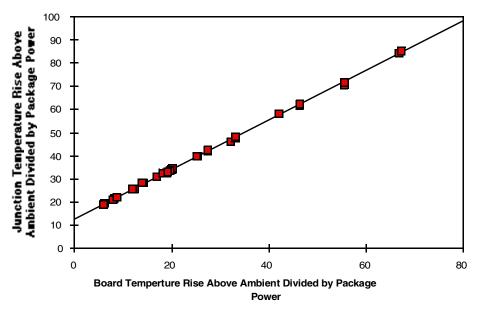

## 7.3 Estimation with Junction-to-Board Thermal Resistance

A simple package thermal model which has demonstrated reasonable accuracy (about 20%) is a two resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The junction-to-case covers the situation where a heat sink is used or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed circuit board. It has been observed that the thermal performance of most plastic packages and especially PBGA packages is strongly dependent on the board temperature; see Figure 3.

Figure 3. Effect of Board Temperature Rise on Thermal Behavior

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

**Table 7. Bus Operation Timings (continued)**

| Num   | Characteristic                                                                                                                                                | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| Mulli |                                                                                                                                                               | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| В8а   | CLKOUT to TSIZ(0:1), $\overline{REG}$ , $\overline{RSV}$ , AT(0:3) $\overline{BDIP}$ , PTR valid (MAX = 0.25 x B1 + 6.3)                                      | 7.60   | 13.80 | 6.30   | 12.50 | 5.00   | 11.30 | 3.80   | 10.00 | ns   |

| B8b   | CLKOUT to BR, BG, VFLS(0:1),<br>VF(0:2), IWP(0:2), FRZ, LWP(0:1),<br>STS Valid <sup>4</sup> (MAX = 0.25 x B1 + 6.3)                                           | 7.60   | 13.80 | 6.30   | 12.50 | 5.00   | 11.30 | 3.80   | 10.00 | ns   |

| В9    | CLKOUT to A(0:31), BADDR(28:30),<br>RD/WR, BURST, D(0:31), DP(0:3),<br>TSIZ(0:1), REG, RSV, AT(0:3), PTR<br>High-Z (MAX = 0.25 x B1 + 6.3)                    | 7.60   | 13.80 | 6.30   | 12.50 | 5.00   | 11.30 | 3.80   | 10.00 | ns   |

| B11   | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion (MAX = 0.25 x B1 + 6.0)                                                                                 | 7.60   | 13.60 | 6.30   | 12.30 | 5.00   | 11.00 | 3.80   | 11.30 | ns   |

| B11a  | CLKOUT to $\overline{\text{TA}}$ , $\overline{\text{BI}}$ assertion (when driven by the memory controller or PCMCIA interface) (MAX = 0.00 x B1 + 9.30 $^5$ ) | 2.50   | 9.30  | 2.50   | 9.30  | 2.50   | 9.30  | 2.50   | 9.80  | ns   |

| B12   | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation (MAX = 0.25 x B1 + 4.8)                                                                                  | 7.60   | 12.30 | 6.30   | 11.00 | 5.00   | 9.80  | 3.80   | 8.50  | ns   |

| B12a  | CLKOUT to TA, BI negation (when driven by the memory controller or PCMCIA interface) (MAX = 0.00 x B1 + 9.00)                                                 | 2.50   | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | ns   |

| B13   | CLKOUT to TS, BB High-Z (MIN = 0.25 x B1)                                                                                                                     | 7.60   | 21.60 | 6.30   | 20.30 | 5.00   | 19.00 | 3.80   | 14.00 | ns   |

| B13a  | CLKOUT to TA, BI High-Z (when driven by the memory controller or PCMCIA interface) (MIN = 0.00 x B1 + 2.5)                                                    | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | ns   |

| B14   | CLKOUT to TEA assertion (MAX = 0.00 x B1 + 9.00)                                                                                                              | 2.50   | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | ns   |

| B15   | CLKOUT to TEA High-Z (MIN = 0.00 x B1 + 2.50)                                                                                                                 | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | ns   |

| B16   | TA, BI valid to CLKOUT (setup time)<br>(MIN = 0.00 x B1 + 6.00)                                                                                               | 6.00   | _     | 6.00   | _     | 6.00   | _     | 6.00   | _     | ns   |

| B16a  | TEA, KR, RETRY, CR valid to CLKOUT (setup time) (MIN = 0.00 x B1 + 4.5)                                                                                       | 4.50   | _     | 4.50   | _     | 4.50   | _     | 4.50   | _     | ns   |

| B16b  | BB, BG, BR, valid to CLKOUT (setup time) <sup>6</sup> (4MIN = 0.00 x B1 + 0.00)                                                                               | 4.00   | _     | 4.00   | _     | 4.00   | _     | 4.00   | _     | ns   |

| B17   | CLKOUT to TA, TEA, BI, BB, BG, BR valid (hold time) (MIN = 0.00 x B1 + 1.00 7)                                                                                | 1.00   | _     | 1.00   | _     | 1.00   | _     | 2.00   | _     | ns   |

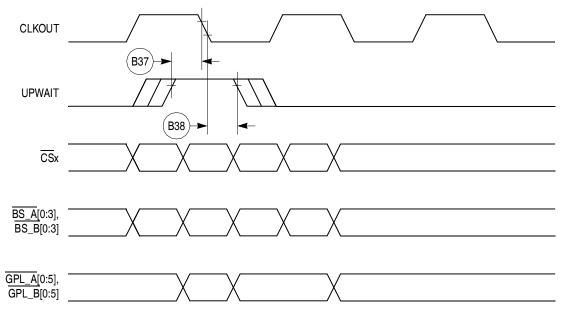

### **Bus Signal Timing**

Figure 19 provides the timing for the asynchronous asserted UPWAIT signal controlled by the UPM.

Figure 19. Asynchronous UPWAIT Asserted Detection in UPM Handled Cycles Timing

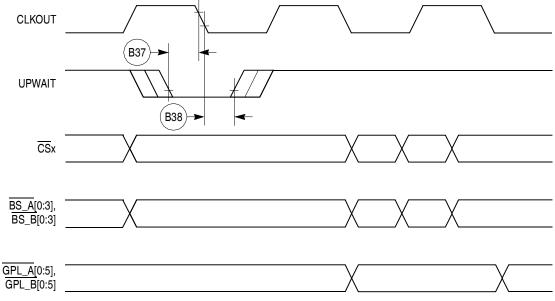

Figure 20 provides the timing for the asynchronous negated UPWAIT signal controlled by the UPM.

Figure 20. Asynchronous UPWAIT Negated Detection in UPM Handled Cycles Timing

### **Bus Signal Timing**

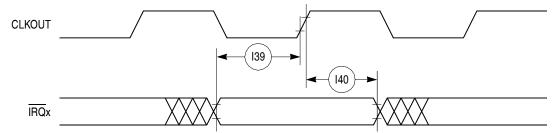

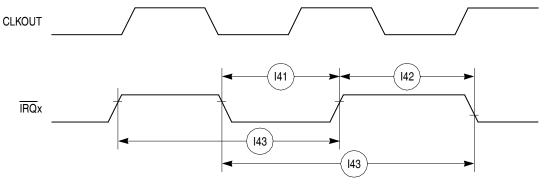

### Table 8 provides interrupt timing for the MPC862/857T/857DSL.

### **Table 8. Interrupt Timing**

| Num   | Characteristic <sup>1</sup>                    | All Freq                | Unit |       |

|-------|------------------------------------------------|-------------------------|------|-------|

| Nulli | Characteristic                                 | Min                     | Max  | Offic |

| 139   | IRQx valid to CLKOUT rising edge (set up time) | 6.00                    |      | ns    |

| 140   | IRQx hold time after CLKOUT                    | 2.00                    |      | ns    |

| 141   | IRQx pulse width low                           | 3.00                    |      | ns    |

| 142   | IRQx pulse width high                          | 3.00                    |      | ns    |

| 143   | IRQx edge-to-edge time                         | 4xT <sub>CLOCKOUT</sub> |      | _     |

The timings I39 and I40 describe the testing conditions under which the IRQ lines are tested when being defined as level sensitive. The IRQ lines are synchronized internally and do not have to be asserted or negated with reference to the CLKOUT.

The timings I41, I42, and I43 are specified to allow the correct function of the  $\overline{\text{IRQ}}$  lines detection circuitry, and has no direct relation with the total system interrupt latency that the MPC862/857T/857DSL is able to support.

Figure 24 provides the interrupt detection timing for the external level-sensitive lines.

Figure 24. Interrupt Detection Timing for External Level Sensitive Lines

Figure 25 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 25. Interrupt Detection Timing for External Edge Sensitive Lines

### **Bus Signal Timing**

Table 10 shows the PCMCIA port timing for the MPC862/857T/857DSL.

**Table 10. PCMCIA Port Timing**

| Num | Characteristic                                                    | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit  |

|-----|-------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|-------|

|     |                                                                   | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Oiiit |

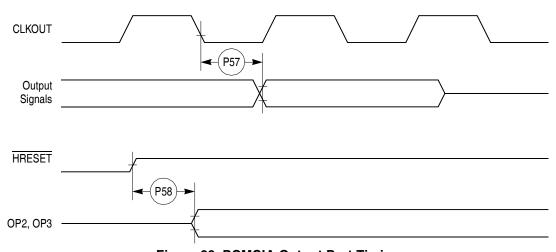

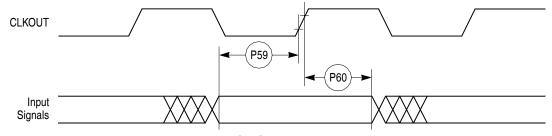

| P57 | CLKOUT to OPx Valid (MAX = 0.00 x B1 + 19.00)                     | _      | 19.00 | _      | 19.00 | _      | 19.00 | _      | 19.00 | ns    |

| P58 | HRESET negated to OPx drive <sup>1</sup> (MIN = 0.75 x B1 + 3.00) | 25.70  | _     | 21.70  | _     | 18.00  | _     | 14.40  | _     | ns    |

| P59 | IP_Xx valid to CLKOUT rising edge<br>(MIN = 0.00 x B1 + 5.00)     | 5.00   | _     | 5.00   | _     | 5.00   | _     | 5.00   | _     | ns    |

| P60 | CLKOUT rising edge to IP_Xx invalid (MIN = 0.00 x B1 + 1.00)      | 1.00   | _     | 1.00   | _     | 1.00   | _     | 1.00   | _     | ns    |

OP2 and OP3 only.

Figure 29 provides the PCMCIA output port timing for the MPC862/857T/857DSL.

Figure 29. PCMCIA Output Port Timing

Figure 30 provides the PCMCIA output port timing for the MPC862/857T/857DSL.

**Figure 30. PCMCIA Input Port Timing**

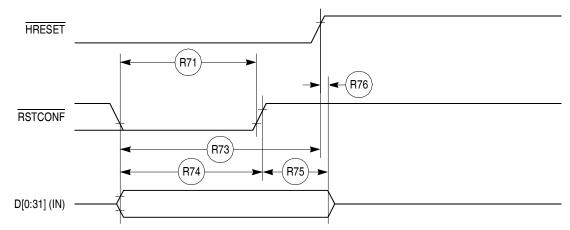

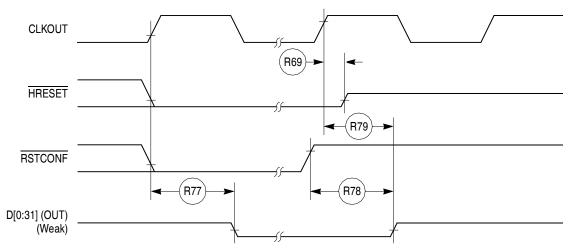

Figure 33 shows the reset timing for the data bus configuration.

Figure 33. Reset Timing—Configuration from Data Bus

Figure 34 provides the reset timing for the data bus weak drive during configuration.

Figure 34. Reset Timing—Data Bus Weak Drive during Configuration

**CPM Electrical Characteristics**

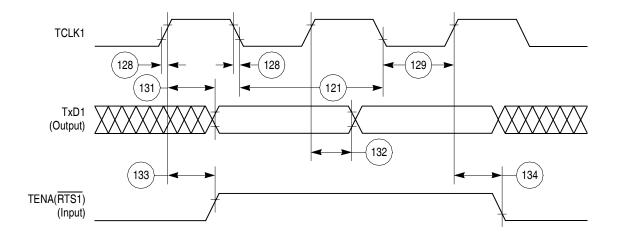

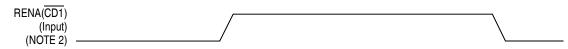

# 11.7 SCC in NMSI Mode Electrical Specifications

Table 20 provides the NMSI external clock timing.

**Table 20. NMSI External Clock Timing**

| Neven | Ohavastavistis                                       | All Freq     | uencies | 11   |

|-------|------------------------------------------------------|--------------|---------|------|

| Num   | Characteristic                                       | Min          | Max     | Unit |

| 100   | RCLK1 and TCLK1 width high <sup>1</sup>              | 1/SYNCCLK    | _       | ns   |

| 101   | RCLK1 and TCLK1 width low                            | 1/SYNCCLK +5 | _       | ns   |

| 102   | RCLK1 and TCLK1 rise/fall time                       | _            | 15.00   | ns   |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00         | 50.00   | ns   |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00         | 50.00   | ns   |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 5.00         | _       | ns   |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 5.00         | _       | ns   |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 5.00         | _       | ns   |

| 108   | CD1 setup Time to RCLK1 rising edge                  | 5.00         | _       | ns   |

<sup>&</sup>lt;sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater than or equal to 2.25/1.

Table 21 provides the NMSI internal clock timing.

**Table 21. NMSI Internal Clock Timing**

| Num   | Characteristic                                       | All Freq | Unit      |       |

|-------|------------------------------------------------------|----------|-----------|-------|

| Nulli | Characteristic                                       | Min      | Max       | Oilit |

| 100   | RCLK1 and TCLK1 frequency <sup>1</sup>               | 0.00     | SYNCCLK/3 | MHz   |

| 102   | RCLK1 and TCLK1 rise/fall time                       | _        | _         | ns    |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00     | 30.00     | ns    |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00     | 30.00     | ns    |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 40.00    | _         | ns    |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 40.00    | _         | ns    |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 0.00     | _         | ns    |

| 108   | CD1 setup time to RCLK1 rising edge                  | 40.00    | _         | ns    |

<sup>&</sup>lt;sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater or equal to 3/1.

<sup>&</sup>lt;sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signal.

Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signals.

### **CPM Electrical Characteristics**

### NOTES:

- 1. Transmit clock invert (TCI) bit in GSMR is set.

- 2. If RENA is deasserted before TENA, or RENA is not asserted at all during transmit, then the CSL bit is set in the buffer descriptor at the end of the frame transmission.

Figure 62. Ethernet Transmit Timing Diagram

Figure 63. CAM Interface Receive Start Timing Diagram

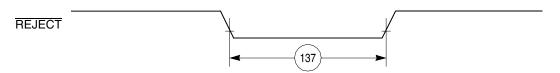

Figure 64. CAM Interface REJECT Timing Diagram

### **CPM Electrical Characteristics**

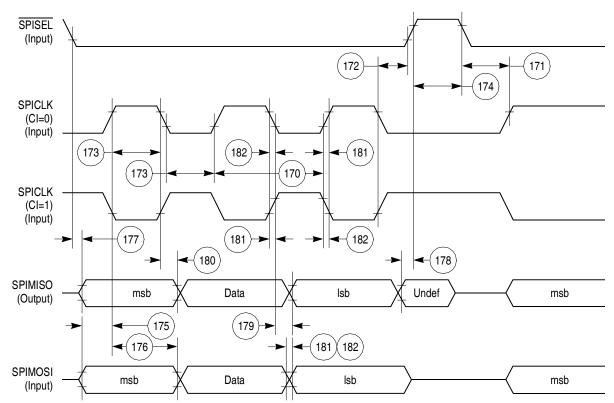

Figure 68. SPI Slave (CP = 0) Timing Diagram

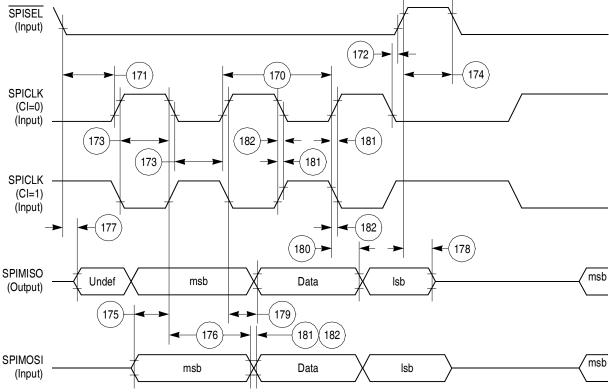

Figure 69. SPI Slave (CP = 1) Timing Diagram

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

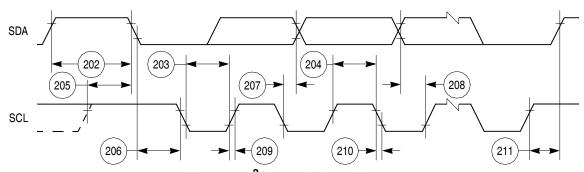

# 11.12 I<sup>2</sup>C AC Electrical Specifications

Table 26 provides the  $I^2C$  (SCL < 100 KHz) timings.

Table 26. I<sup>2</sup>C Timing (SCL < 100 KHz)

| Num | Charratariatia                            | All Fred | 11  |      |

|-----|-------------------------------------------|----------|-----|------|

|     | Characteristic                            | Min      | Max | Unit |

| 200 | SCL clock frequency (slave)               | 0        | 100 | kHz  |

| 200 | SCL clock frequency (master) <sup>1</sup> | 1.5      | 100 | kHz  |

| 202 | Bus free time between transmissions       | 4.7      | _   | μs   |

| 203 | Low period of SCL                         | 4.7      | _   | μs   |

| 204 | High period of SCL                        | 4.0      | _   | μs   |

| 205 | Start condition setup time                | 4.7      | _   | μs   |

| 206 | Start condition hold time                 | 4.0      | _   | μs   |

| 207 | Data hold time                            | 0        | _   | μs   |

| 208 | Data setup time                           | 250      | _   | ns   |

| 209 | SDL/SCL rise time                         | _        | 1   | μs   |

| 210 | SDL/SCL fall time                         | _        | 300 | ns   |

| 211 | Stop condition setup time                 | 4.7      | _   | μs   |

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(BRGCLK/pre\_scaler) must be greater or equal to 4/1.

Table 27 provides the  $I^2C$  (SCL > 100 kHz) timings.

Table 27.  $I^2C$  Timing (SCL > 100 kHz)

| Num | Characteristic                            | Expression  | All Freq        | Unit          |       |

|-----|-------------------------------------------|-------------|-----------------|---------------|-------|

|     | Citalacteristic                           | LAPICSSIOII | Min             | Max           | Oiiii |

| 200 | SCL clock frequency (slave)               | fSCL        | 0               | BRGCLK/48     | Hz    |

| 200 | SCL clock frequency (master) <sup>1</sup> | fSCL        | BRGCLK/16512    | BRGCLK/48     | Hz    |

| 202 | Bus free time between transmissions       | _           | 1/(2.2 * fSCL)  | _             | s     |

| 203 | Low period of SCL                         | _           | 1/(2.2 * fSCL)  | _             | s     |

| 204 | High period of SCL                        | _           | 1/(2.2 * fSCL)  | _             | s     |

| 205 | Start condition setup time                | _           | 1/(2.2 * fSCL)  | _             | s     |

| 206 | Start condition hold time                 | _           | 1/(2.2 * fSCL)  | _             | s     |

| 207 | Data hold time                            | _           | 0               | _             | s     |

| 208 | Data setup time                           | _           | 1/(40 * fSCL)   | _             | s     |

| 209 | SDL/SCL rise time                         | _           | _               | 1/(10 * fSCL) | s     |

| 210 | SDL/SCL fall time                         | _           | _               | 1/(33 * fSCL) | s     |

| 211 | Stop condition setup time                 | _           | 1/2(2.2 * fSCL) | _             | S     |

SCL frequency is given by SCL = BrgClk\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(Brg\_Clk/pre\_scaler) must be greater or equal to 4/1.

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

### **UTOPIA AC Electrical Specifications**

Figure 70 shows the I<sup>2</sup>C bus timing.

Figure 70. I<sup>2</sup>C Bus Timing Diagram

# 12 UTOPIA AC Electrical Specifications

Table 28 shows the AC electrical specifications for the UTOPIA interface.

**Table 28. UTOPIA AC Electrical Specifications**

| Num | Signal Characteristic                                                  | Direction | Min  | Max   | Unit |

|-----|------------------------------------------------------------------------|-----------|------|-------|------|

| U1  | UtpClk rise/fall time (Internal clock option)                          | Output    |      | 4 ns  | ns   |

|     | Duty cycle                                                             |           | 50   | 50    | %    |

|     | Frequency                                                              |           |      | 33    | MHz  |

| U1a | UtpClk rise/fall time (external clock option)                          | Input     |      | 4ns   | ns   |

|     | Duty cycle                                                             |           | 40   | 60    | %    |

|     | Frequency                                                              |           |      | 33    | MHz  |

| U2  | RxEnb and TxEnb active delay                                           | Output    | 2 ns | 16 ns | ns   |

| U3  | UTPB, SOC, Rxclav and Txclav setup time                                | Input     | 4 ns |       | ns   |

| U4  | UTPB, SOC, Rxclav and Txclav hold time                                 | Input     | 1 ns |       | ns   |

| U5  | UTPB, SOC active delay (and PHREQ and PHSEL active delay in MPHY mode) | Output    | 2 ns | 16 ns | ns   |

### **Mechanical Data and Ordering Information**

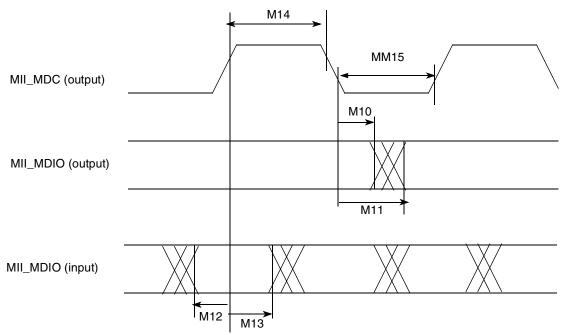

| Num | Characteristic                                                              | Min | Max | Unit           |

|-----|-----------------------------------------------------------------------------|-----|-----|----------------|

| M10 | MII_MDC falling edge to MII_MDIO output invalid (minimum propagation delay) | 0   | _   | ns             |

| M11 | MII_MDC falling edge to MII_MDIO output valid (max prop delay)              | _   | 25  | ns             |

| M12 | MII_MDIO (input) to MII_MDC rising edge setup                               | 10  | _   | ns             |

| M13 | MII_MDIO (input) to MII_MDC rising edge hold                                | 0   | _   | ns             |

| M14 | MII_MDC pulse width high                                                    | 40% | 60% | MII_MDC period |

| M15 | MII_MDC pulse width low                                                     | 40% | 60% | MII_MDC period |

Figure 76 shows the MII serial management channel timing diagram.

Figure 76. MII Serial Management Channel Timing Diagram

# 14 Mechanical Data and Ordering Information

Table 33 provides information on the MPC862/857T/857DSL derivative devices.

Table 33. MPC862/857T/857DSL Derivatives

| Device  | Number<br>of<br>SCCs <sup>1</sup> | Ethernet<br>Support | Multi-Channel<br>HDLC Support | ATM Support | Cache Size  |          |

|---------|-----------------------------------|---------------------|-------------------------------|-------------|-------------|----------|

|         |                                   |                     |                               |             | Instruction | Data     |

| MPC862T | Four                              | 10/100 Mbps         | Yes                           | Yes         | 4 Kbytes    | 4 Kbytes |

| MPC862P | Four                              | 10/100 Mbps         | Yes                           | Yes         | 16 Kbytes   | 8 Kbytes |

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

### **Mechanical Data and Ordering Information**

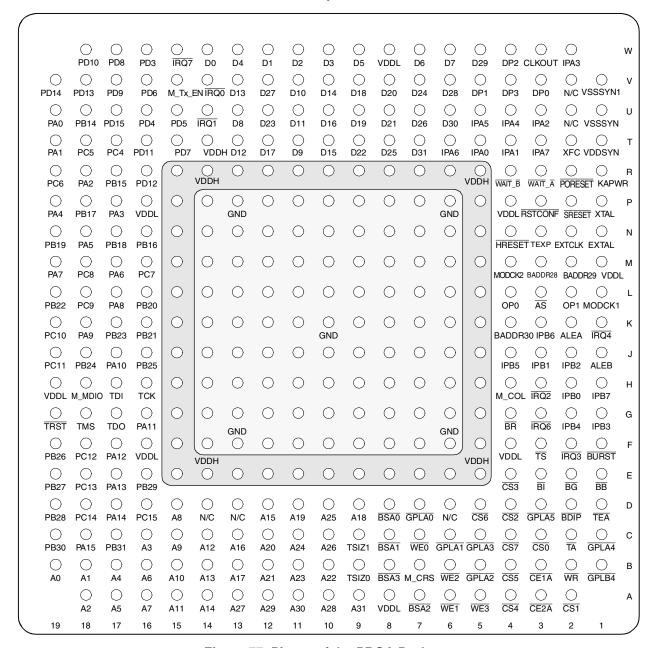

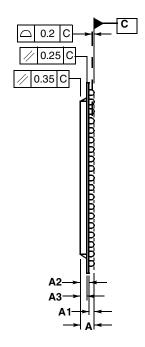

### NOTE: This is the top view of the device.

Figure 77. Pinout of the PBGA Package

Table 35 contains a list of the MPC862 input and output signals and shows multiplexing and pin assignments.

**Table 35. Pin Assignments**

| Name                           | Pin Number                                                                                                                                                   | Туре                            |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| A[0:31]                        | B19, B18, A18, C16, B17, A17, B16, A16, D15, C15, B15, A15, C14, B14, A14, D12, C13, B13, D9, D11, C12, B12, B10, B11, C11, D10, C10, A13, A10, A12, A11, A9 | Bidirectional<br>Three-state    |

| TSIZ0<br>REG                   | B9                                                                                                                                                           | Bidirectional<br>Three-state    |

| TSIZ1                          | C9                                                                                                                                                           | Bidirectional<br>Three-state    |

| RD/WR                          | B2                                                                                                                                                           | Bidirectional<br>Three-state    |

| BURST                          | F1                                                                                                                                                           | Bidirectional<br>Three-state    |

| BDIP<br>GPL_B5                 | D2                                                                                                                                                           | Output                          |

| TS                             | F3                                                                                                                                                           | Bidirectional<br>Active Pull-up |

| TA                             | C2                                                                                                                                                           | Bidirectional<br>Active Pull-up |

| TEA                            | D1                                                                                                                                                           | Open-drain                      |

| BI                             | E3                                                                                                                                                           | Bidirectional<br>Active Pull-up |

| IRQ2<br>RSV                    | НЗ                                                                                                                                                           | Bidirectional<br>Three-state    |

| IRQ4<br>KR<br>RETRY<br>SPKROUT | K1                                                                                                                                                           | Bidirectional<br>Three-state    |

| CR<br>IRQ3                     | F2                                                                                                                                                           | Input                           |

| D[0:31]                        | W14, W12, W11, W10, W13, W9, W7, W6, U13, T11, V11, U11, T13, V13, V10, T10, U10, T12, V9, U9, V8, U8, T9, U12, V7, T8, U7, V12, V6, W5, U6, T7              | Bidirectional<br>Three-state    |

| DP0<br>IRQ3                    | V3                                                                                                                                                           | Bidirectional<br>Three-state    |

| DP1<br>IRQ4                    | V5                                                                                                                                                           | Bidirectional<br>Three-state    |

| DP2<br>IRQ5                    | W4                                                                                                                                                           | Bidirectional<br>Three-state    |

| DP3<br>IRQ6                    | V4                                                                                                                                                           | Bidirectional<br>Three-state    |

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

### **Mechanical Data and Ordering Information**

# Table 35. Pin Assignments (continued)

| Name                                           | Pin Number | Туре                         |

|------------------------------------------------|------------|------------------------------|

| IP_A6<br>UTPB_Split6 <sup>2</sup><br>MII-TXERR | Т6         | Input                        |

| IP_A7<br>UTPB_Split7 <sup>2</sup><br>MII-RXDV  | ТЗ         | Input                        |

| ALE_B<br>DSCK/AT1                              | J1         | Bidirectional<br>Three-state |

| IP_B[0:1]<br>IWP[0:1]<br>VFLS[0:1]             | H2, J3     | Bidirectional                |

| IP_B2<br>IOIS16_B<br>AT2                       | J2         | Bidirectional<br>Three-state |

| IP_B3<br>IWP2<br>VF2                           | G1         | Bidirectional                |

| IP_B4<br>LWP0<br>VF0                           | G2         | Bidirectional                |

| IP_B5<br>LWP1<br>VF1                           | J4         | Bidirectional                |

| IP_B6<br>DSDI<br>AT0                           | К3         | Bidirectional<br>Three-state |

| IP_B7<br>PTR<br>AT3                            | H1         | Bidirectional<br>Three-state |

| OP0<br>MII-TXD0<br>UtpClk_Split <sup>2</sup>   | L4         | Bidirectional                |

| OP1                                            | L2         | Output                       |

| OP2<br>MODCK1<br>STS                           | L1         | Bidirectional                |

| OP3<br>MODCK2<br>DSDO                          | M4         | Bidirectional                |

| BADDR30<br>REG                                 | K4         | Output                       |

| BADDR[28:29]                                   | M3, M2     | Output                       |

| ĀS                                             | L3         | Input                        |

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

### **Mechanical Data and Ordering Information**

Table 35. Pin Assignments (continued)

| Name        | Pin Number                                                                                                                                                                                                                                                                                                                                                                      | Туре          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| TRST        | G19                                                                                                                                                                                                                                                                                                                                                                             | Input         |

| TDO<br>DSDO | G17                                                                                                                                                                                                                                                                                                                                                                             | Output        |

| M_CRS       | B7                                                                                                                                                                                                                                                                                                                                                                              | Input         |

| M_MDIO      | H18                                                                                                                                                                                                                                                                                                                                                                             | Bidirectional |

| M_TXEN      | V15                                                                                                                                                                                                                                                                                                                                                                             | Output        |

| M_COL       | H4                                                                                                                                                                                                                                                                                                                                                                              | Input         |

| KAPWR       | R1                                                                                                                                                                                                                                                                                                                                                                              | Power         |

| GND         | F6, F7, F8, F9, F10, F11, F12, F13, F14, G6, G7, G8, G9, G10, G11, G12, G13, G14, H6, H7, H8, H9, H10, H11, H12, H13, H14, J6, J7, J8, J9, J10, J11, J12, J13, J14, K6, K7, K8, K9, K10, K11, K12, K13, K14, L6, L7, L8, L9, L10, L11, L12, L13, L14, M6, M7, M8, M9, M10, M11, M12, M13, M14, N6, N7, N8, N9, N10, N11, N12, N13, N14, P6, P7, P8, P9, P10, P11, P12, P13, P14 | Power         |

| VDDL        | A8, M1, W8, H19, F4, F16, P4, P16                                                                                                                                                                                                                                                                                                                                               | Power         |

| VDDH        | E5, E6, E7, E8, E9, E10, E11, E12, E13, E14, E15, F5, F15, G5, G15, H5, H15, J5, J15, K5, K15, L5, L15, M5, M15, N5, N15, P5, P15, R5, R6, R7, R8, R9, R10, R11, R12, R13, R14, R15, T14                                                                                                                                                                                        | Power         |

| N/C         | D6, D13, D14, U2, V2                                                                                                                                                                                                                                                                                                                                                            | No-connect    |

Classic SAR mode only

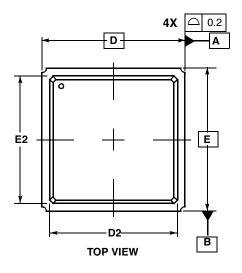

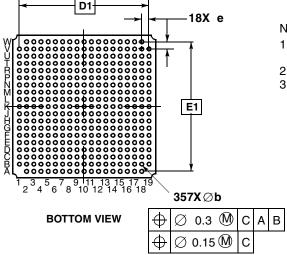

# 14.2 Mechanical Dimensions of the PBGA Package

For more information on the printed circuit board layout of the PBGA package, including thermal via design and suggested pad layout, please refer to *Plastic Ball Grid Array Application Note* (order number: AN1231/D) available from your local Freescale sales office. Figure 78 shows the mechanical dimensions of the PBGA package.

<sup>&</sup>lt;sup>2</sup> ESAR mode only

### SIDE VIEW

### NOTES:

- Dimensions and tolerancing per ASME Y14.5M, 1994.

- 2. Dimensions in millimeters.

- 3. Dimension b is the maximum solder ball diameter measured parallel to datum C.

|           | MILLIMETERS |       |  |

|-----------|-------------|-------|--|

| DIM       | MIN         | MAX   |  |

| Α         |             | 2.05  |  |

| A1        | 0.50        | 0.70  |  |

| <b>A2</b> | 0.95        | 1.35  |  |

| А3        | 0.70        | 0.90  |  |

| b         | 0.60        | 0.90  |  |

| D         | 25.00 BSC   |       |  |

| D1        | 22.86 BSC   |       |  |

| D2        | 22.40       | 22.60 |  |

| е         | 1.27 BSC    |       |  |

| Е         | 25.00 BSC   |       |  |

| E1        | 22.86 BSC   |       |  |

| E2        | 22.40 22.60 |       |  |

Case No. 1103-01

Figure 78. Mechanical Dimensions and Bottom Surface Nomenclature of the PBGA Package