### NXP USA Inc. - KMPC862TZQ100B Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 100MHz                                                                 |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10Mbps (4), 10/100Mbps (1)                                             |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 3.3V                                                                   |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 357-BBGA                                                               |

| Supplier Device Package         | 357-PBGA (25x25)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc862tzq100b |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC) from the PowerPC architecture

- Reset controller

- IEEE 1149.1 test access port (JTAG)

- Interrupts

- Seven external interrupt request (IRQ) lines

- 12 port pins with interrupt capability

- The MPC862P and MPC862T have 23 internal interrupt sources; the MPC857T and MPC857DSL have 20 internal interrupt sources

- Programmable priority between SCCs (MPC862P and MPC862T)

- Programmable highest priority request

- Communications processor module (CPM)

- RISC controller

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- Up to 8-Kbytes of dual-port RAM

- The MPC862P and MPC862T have 16 serial DMA (SDMA) channels; the MPC857T and MPC857DSL have 10 serial DMA (SDMA) channels

- Three parallel I/O registers with open-drain capability

- Four baud rate generators

- Independent (can be connected to any SCC or SMC)

- Allow changes during operation

- Autobaud support option

- The MPC862P and MPC862T have four SCCs (serial communication controller) The MPC857T and MPC857DSL have one SCC, SCC1; the MPC857DSL supports ethernet only

- Serial ATM capability on all SCCs

- Optional UTOPIA port on SCC4

- Ethernet/IEEE 802.3 optional on SCC1–4, supporting full 10-Mbps operation

- HDLC/SDLC

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support PPP (point-to-point protocol)

- AppleTalk

Features

- Sleep—All units disabled except RTC, PIT, time base, and decrementer with PLL active for fast wake up

- Deep sleep—All units disabled including PLL except RTC, PIT, time base, and decrementer.

- Power down mode- All units powered down except PLL, RTC, PIT, time base and

- decrementerDebug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two

operate on data

- Supports conditions:  $= \neq < >$

- Each watchpoint can generate a break point internally

- 3.3 V operation with 5-V TTL compatibility except EXTAL and EXTCLK

- 357-pin plastic ball grid array (PBGA) package

- Operation up to 100MHz

The MPC862/857T/857DSL is comprised of three modules that each use the 32-bit internal bus: the MPC8xx core, the system integration unit (SIU), and the communication processor module (CPM). The MPC862P/862T block diagram is shown in Figure 1. The MPC857T/857DSL block diagram is shown in Figure 2.

### Table 2. Maximum Tolerated Ratings (continued)

(GND = 0 V)

| Rating                                           | Symbol              | Value           | Unit | Max Freq<br>(MHz) |

|--------------------------------------------------|---------------------|-----------------|------|-------------------|

| Input voltage <sup>2</sup>                       | V <sub>in</sub>     | GND-0.3 to VDDH | V    | -                 |

| Temperature <sup>3</sup> (standard) <sup>4</sup> | T <sub>A(min)</sub> | 0               | °C   | 100               |

|                                                  | T <sub>j(max)</sub> | 105             | °C   | 100               |

| Temperature <sup>3</sup> (extended)              | T <sub>A(min)</sub> | -40             | °C   | 80                |

|                                                  | T <sub>j(max)</sub> | 115             | °C   | 80                |

| Storage temperature range                        | T <sub>stg</sub>    | -55 to +150     | °C   | -                 |

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 5. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device. Caution: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction applies to power-up and normal operation (that is, if the MPC862/857T/857DSL is unpowered, voltage greater

than 2.5 V must not be applied to its inputs).

<sup>3</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as

junction temperature, T<sub>j</sub>.

<sup>4</sup> JTAG is tested only at ambient, not at standard maximum or extended maximum.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{CC}$ ).

| Die Revision      | Frequency | Typical <sup>1</sup> | Maximum <sup>2</sup> | Unit |

|-------------------|-----------|----------------------|----------------------|------|

| A.1, B.0          | 66 MHz    | 910                  | 1060                 | mW   |

| (2:1 Mode)        | 80 MHz    | 1.06                 | 1.20                 | W    |

| B.0<br>(2:1 Mode) | 100 MHz   | 1.35                 | 1.54                 | W    |

Table 4. Power Dissipation (P<sub>D</sub>) (continued)

<sup>1</sup> Typical power dissipation is measured at 3.3 V.

<sup>2</sup> Maximum power dissipation is measured at 3.5 V.

### NOTE

Values in Table 4 represent VDDL based power dissipation and do not include I/O power dissipation over VDDH. I/O power dissipation varies widely by application due to buffer current, depending on external circuitry.

## 6 DC Characteristics

Table 5 provides the DC electrical characteristics for the MPC862/857T/857DSL.

| Characteristic                                                                                | Symbol                                     | Min        | Мах     | Unit |

|-----------------------------------------------------------------------------------------------|--------------------------------------------|------------|---------|------|

| Operating voltage                                                                             | VDDH, VDDL,<br>KAPWR,<br>VDDSYN            | 3.135      | 3.465   | V    |

|                                                                                               | KAPWR<br>(power-down<br>mode)              | 2.0        | 3.6     | V    |

|                                                                                               | KAPWR<br>(all other<br>operating<br>modes) | VDDH – 0.4 | VDDH    | V    |

| Input High Voltage (all inputs except EXTAL and EXTCLK)                                       | VIH                                        | 2.0        | 5.5     | V    |

| Input Low Voltage <sup>1</sup>                                                                | VIL                                        | GND        | 0.8     | V    |

| EXTAL, EXTCLK Input High Voltage                                                              | VIHC                                       | 0.7*(VCC)  | VCC+0.3 | V    |

| Input Leakage Current, Vin = 5.5 V (Except TMS, TRST, DSCK and DSDI pins)                     | l <sub>in</sub>                            | —          | 100     | μA   |

| Input Leakage Current, Vin = 3.6 V (Except TMS, TRST, DSCK, and DSDI)                         | l <sub>in</sub>                            | —          | 10      | μA   |

| Input Leakage Current, Vin = 0 V (Except TMS, $\overline{\text{TRST}}$ , DSCK, and DSDI pins) | l <sub>in</sub>                            | —          | 10      | μA   |

| Input Capacitance <sup>2</sup>                                                                | C <sub>in</sub>                            | —          | 20      | pF   |

| Output High Voltage, IOH = -2.0 mA, VDDH = 3.0 V<br>(Except XTAL, XFC, and Open drain pins)   | VOH                                        | 2.4        | _       | V    |

**Table 5. DC Electrical Specifications**

**Bus Signal Timing**

|      | Characteristic                                                                                                                                                                                                                                                                                                                                                                | 33    | MHz | 40 MHz |     | 50 MHz |     | 66 MHz |     |      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|--------|-----|--------|-----|--------|-----|------|

| Num  |                                                                                                                                                                                                                                                                                                                                                                               | Min   | Max | Min    | Max | Min    | Max | Min    | Max | Unit |

| B29d | WE(0:3) negated to D(0:31), DP(0:3)<br>High-Z GPCM write access, TRLX = 1,<br>CSNT = 1, EBDF = 0 (MIN = 1.50 x B1<br>- 2.00)                                                                                                                                                                                                                                                  | 43.50 | _   | 35.50  |     | 28.00  | _   | 20.70  | _   | ns   |

| B29e | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3)<br>High-Z GPCM write access, TRLX = 1,<br>CSNT = 1, ACS = 10, or ACS = 11<br>EBDF = 0 (MIN = 1.50 x B1 - 2.00)                                                                                                                                                                                                             | 43.50 | _   | 35.50  | _   | 28.00  | _   | 20.70  | _   | ns   |

| B29f | $\overline{\text{WE}}(0:3)$ negated to D(0:31), DP(0:3)<br>High Z GPCM write access, TRLX = 0,<br>CSNT = 1, EBDF = 1 (MIN = 0.375 x<br>B1 - 6.30)                                                                                                                                                                                                                             | 5.00  | _   | 3.00   |     | 1.10   | _   | 0.00   | _   | ns   |

| B29g | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3)<br>High-Z GPCM write access, TRLX = 0,<br>CSNT = 1 ACS = 10 or ACS = 11,<br>EBDF = 1 (MIN = 0.375 x B1 - 6.30)                                                                                                                                                                                                             | 5.00  | _   | 3.00   |     | 1.10   | _   | 0.00   | _   | ns   |

| B29h | $\overline{\text{WE}}$ (0:3) negated to D(0:31), DP(0:3)<br>High Z GPCM write access, TRLX = 1,<br>CSNT = 1, EBDF = 1 (MIN = 0.375 x<br>B1 - 3.30)                                                                                                                                                                                                                            | 38.40 | _   | 31.10  | _   | 24.20  | _   | 17.50  | _   | ns   |

| B29i | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3)<br>High-Z GPCM write access, TRLX = 1,<br>CSNT = 1, ACS = 10 or ACS = 11,<br>EBDF = 1 (MIN = 0.375 x B1 - 3.30)                                                                                                                                                                                                            | 38.40 | _   | 31.10  |     | 24.20  | _   | 17.50  | _   | ns   |

| B30  | $\overline{CS}$ , $\overline{WE}$ (0:3) negated to A(0:31),<br>BADDR(28:30) Invalid GPCM write<br>access <sup>11</sup> (MIN = 0.25 x B1 - 2.00)                                                                                                                                                                                                                               | 5.60  | _   | 4.30   | _   | 3.00   | _   | 1.80   | _   | ns   |

| B30a | $\overline{WE}(0:3) \text{ negated to } A(0:31), \\ BADDR(28:30) \text{ Invalid GPCM, write} \\ access, TRLX = 0, CSNT = 1, \overline{CS} \\ negated to A(0:31) \text{ invalid GPCM write} \\ access TRLX = 0, CSNT = 1 ACS = 10, \\ or ACS == 11, EBDF = 0 (MIN = 0.50) \\ x B1 - 2.00)$                                                                                     | 13.20 |     | 10.50  |     | 8.00   |     | 5.60   |     | ns   |

| B30b | $\overline{WE}(0:3) \text{ negated to } A(0:31) \text{ Invalid} \\ \text{GPCM BADDR}(28:30) \text{ invalid GPCM} \\ \text{write access, TRLX = 1, CSNT = 1.} \\ \overline{\text{CS}} \text{ negated to } A(0:31) \text{ Invalid GPCM} \\ \text{write access TRLX = 1, CSNT = 1,} \\ \text{ACS = 10, or ACS == 11 EBDF = 0} \\ (\text{MIN = 1.50 x B1 - 2.00)} \\ \end{array}$ | 43.50 |     | 35.50  | _   | 28.00  |     | 20.70  |     | ns   |

### Table 7. Bus Operation Timings (continued)

**Bus Signal Timing**

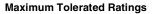

Figure 19 provides the timing for the asynchronous asserted UPWAIT signal controlled by the UPM.

Cycles Timing

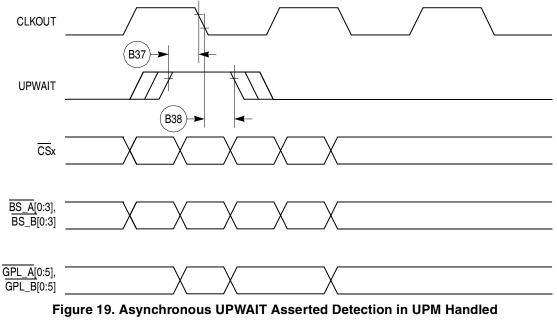

Figure 20 provides the timing for the asynchronous negated UPWAIT signal controlled by the UPM.

#### **IEEE 1149.1 Electrical Specifications**

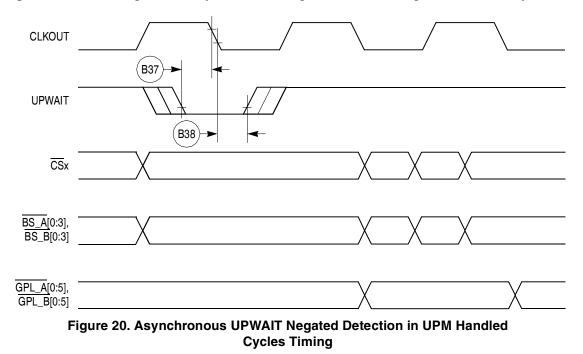

Figure 35 provides the reset timing for the debug port configuration.

Figure 35. Reset Timing—Debug Port Configuration

## 10 IEEE 1149.1 Electrical Specifications

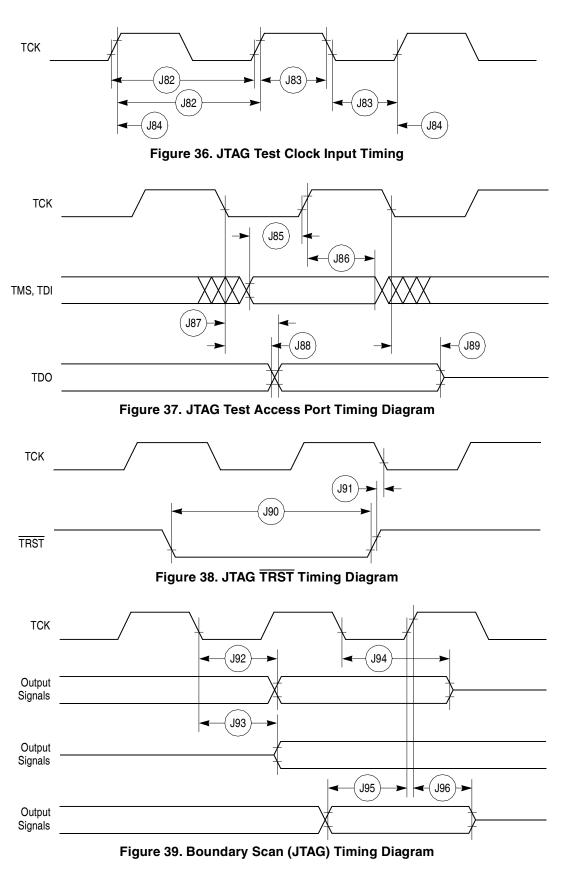

Table 13 provides the JTAG timings for the MPC862/857T/857DSL shown in Figure 36 though Figure 39.

| Num | Characteristic                                         | All Freq | All Frequencies |      |  |  |

|-----|--------------------------------------------------------|----------|-----------------|------|--|--|

| num | Characteristic                                         | Min      | Мах             | Unit |  |  |

| J82 | TCK cycle time                                         | 100.00   | —               | ns   |  |  |

| J83 | TCK clock pulse width measured at 1.5 V                | 40.00    | —               | ns   |  |  |

| J84 | TCK rise and fall times                                | 0.00     | 10.00           | ns   |  |  |

| J85 | TMS, TDI data setup time                               | 5.00     | —               | ns   |  |  |

| J86 | TMS, TDI data hold time                                | 25.00    | —               | ns   |  |  |

| J87 | TCK low to TDO data valid                              | —        | 27.00           | ns   |  |  |

| J88 | TCK low to TDO data invalid                            | 0.00     | —               | ns   |  |  |

| J89 | TCK low to TDO high impedance                          | —        | 20.00           | ns   |  |  |

| J90 | TRST assert time                                       | 100.00   | —               | ns   |  |  |

| J91 | TRST setup time to TCK low                             | 40.00    | —               | ns   |  |  |

| J92 | TCK falling edge to output valid                       | —        | 50.00           | ns   |  |  |

| J93 | TCK falling edge to output valid out of high impedance | —        | 50.00           | ns   |  |  |

| J94 | TCK falling edge to output high impedance              | —        | 50.00           | ns   |  |  |

| J95 | Boundary scan input valid to TCK rising edge           | 50.00    | —               | ns   |  |  |

| J96 | TCK rising edge to boundary scan input invalid         | 50.00    | —               | ns   |  |  |

### Table 13. JTAG Timing

| Num | Characteristic                                                                                           |     | All Frequencies |      |  |

|-----|----------------------------------------------------------------------------------------------------------|-----|-----------------|------|--|

| num | Characteristic                                                                                           | Min | Мах             | Unit |  |

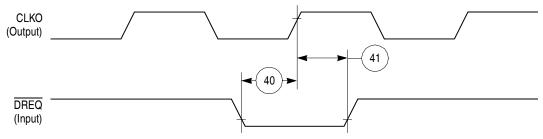

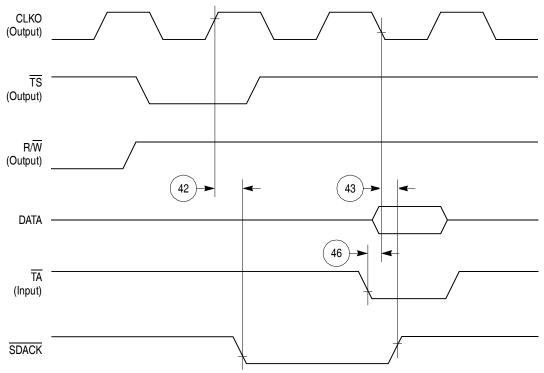

| 43  | SDACK negation delay from clock low                                                                      | _   | 12              | ns   |  |

| 44  | SDACK negation delay from TA low                                                                         | _   | 20              | ns   |  |

| 45  | SDACK negation delay from clock high                                                                     | _   | 15              | ns   |  |

| 46  | $\overline{TA}$ assertion to falling edge of the clock setup time (applies to external $\overline{TA}$ ) | 7   | —               | ns   |  |

### Table 16. IDMA Controller Timing (continued)

Figure 46. IDMA External Requests Timing Diagram

Figure 47. SDACK Timing Diagram—Peripheral Write, Externally-Generated TA

## **11.10 SPI Master AC Electrical Specifications**

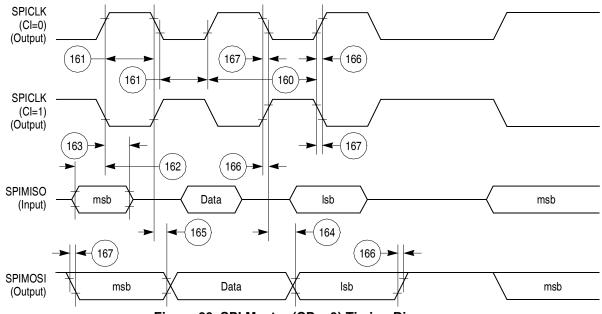

Table 24 provides the SPI master timings as shown in Figure 66 though Figure 67.

### Table 24. SPI Master Timing

| Num | Characteristic                      |    | All Frequencies |                  |  |

|-----|-------------------------------------|----|-----------------|------------------|--|

| Num |                                     |    | Max             | Unit             |  |

| 160 | MASTER cycle time                   | 4  | 1024            | t <sub>cyc</sub> |  |

| 161 | MASTER clock (SCK) high or low time | 2  | 512             | t <sub>cyc</sub> |  |

| 162 | MASTER data setup time (inputs)     | 15 | _               | ns               |  |

| 163 | Master data hold time (inputs)      | 0  | _               | ns               |  |

| 164 | Master data valid (after SCK edge)  | _  | 10              | ns               |  |

| 165 | Master data hold time (outputs)     | 0  | _               | ns               |  |

| 166 | Rise time output                    | _  | 15              | ns               |  |

| 167 | Fall time output                    | _  | 15              | ns               |  |

Figure 66. SPI Master (CP = 0) Timing Diagram

## 11.12 I<sup>2</sup>C AC Electrical Specifications

Table 26 provides the  $I^2C$  (SCL < 100 KHz) timings.

| Table 26. | I <sup>2</sup> C | Timing | (SCL < | 100 KHz) |

|-----------|------------------|--------|--------|----------|

|-----------|------------------|--------|--------|----------|

| Num | Characteristic                            | All Freq | Unit |      |

|-----|-------------------------------------------|----------|------|------|

| Num |                                           | Min      | Мах  | Unit |

| 200 | SCL clock frequency (slave)               | 0        | 100  | kHz  |

| 200 | SCL clock frequency (master) <sup>1</sup> | 1.5      | 100  | kHz  |

| 202 | Bus free time between transmissions       | 4.7      | —    | μs   |

| 203 | Low period of SCL                         | 4.7      | —    | μs   |

| 204 | High period of SCL                        | 4.0      | —    | μs   |

| 205 | Start condition setup time                | 4.7      | —    | μs   |

| 206 | Start condition hold time                 | 4.0      | —    | μs   |

| 207 | Data hold time                            | 0        | —    | μs   |

| 208 | Data setup time                           | 250      | —    | ns   |

| 209 | SDL/SCL rise time                         | —        | 1    | μs   |

| 210 | SDL/SCL fall time                         | —        | 300  | ns   |

| 211 | Stop condition setup time                 | 4.7      | —    | μs   |

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(BRGCLK/pre\_scaler) must be greater or equal to 4/1.

### Table 27 provides the $I^2C$ (SCL > 100 kHz) timings.

Table 27.  $I^2C$  Timing (SCL > 100 kHz)

| Num | Characteristic                            | Expression | All Freq        | Unit          |      |

|-----|-------------------------------------------|------------|-----------------|---------------|------|

| Num | Characteristic                            | Lyression  | Min             | Мах           | Onit |

| 200 | SCL clock frequency (slave)               | fSCL       | 0               | BRGCLK/48     | Hz   |

| 200 | SCL clock frequency (master) <sup>1</sup> | fSCL       | BRGCLK/16512    | BRGCLK/48     | Hz   |

| 202 | Bus free time between transmissions       | —          | 1/(2.2 * fSCL)  | _             | S    |

| 203 | Low period of SCL                         | —          | 1/(2.2 * fSCL)  | _             | S    |

| 204 | High period of SCL                        | —          | 1/(2.2 * fSCL)  | _             | S    |

| 205 | Start condition setup time                | —          | 1/(2.2 * fSCL)  | _             | S    |

| 206 | Start condition hold time                 | —          | 1/(2.2 * fSCL)  | _             | S    |

| 207 | Data hold time                            | —          | 0               | _             | S    |

| 208 | Data setup time                           | —          | 1/(40 * fSCL)   | _             | S    |

| 209 | SDL/SCL rise time                         | —          | —               | 1/(10 * fSCL) | s    |

| 210 | SDL/SCL fall time                         | —          | —               | 1/(33 * fSCL) | S    |

| 211 | Stop condition setup time                 | —          | 1/2(2.2 * fSCL) | _             | S    |

SCL frequency is given by SCL = BrgClk\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(Brg\_Clk/pre\_scaler) must be greater or equal to 4/1.

### MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

1

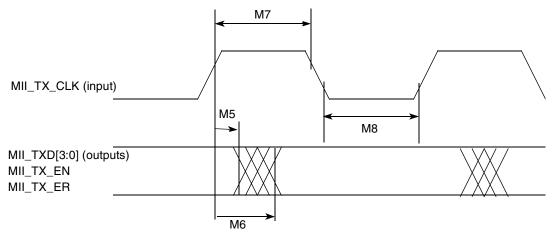

| Num | Characteristic              | Min | Max | Unit              |

|-----|-----------------------------|-----|-----|-------------------|

| M7  | MII_TX_CLK pulse width high | 35% | 65% | MII_TX_CLK period |

| M8  | MII_TX_CLK pulse width low  | 35% | 65% | MII_TX_CLK period |

Table 30. MII Transmit Signal Timing (continued)

Figure 74 shows the MII transmit signal timing diagram.

Figure 74. MII Transmit Signal Timing Diagram

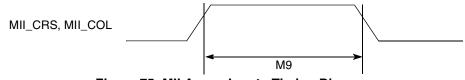

## 13.3 MII Async Inputs Signal Timing (MII\_CRS, MII\_COL)

Table 31 provides information on the MII async inputs signal timing.

Table 31. MII Async Inputs Signal Timing

| Num | Characteristic                       | Min | Мах | Unit              |

|-----|--------------------------------------|-----|-----|-------------------|

| M9  | MII_CRS, MII_COL minimum pulse width | 1.5 | _   | MII_TX_CLK period |

Figure 75 shows the MII asynchronous inputs signal timing diagram.

Figure 75. MII Async Inputs Timing Diagram

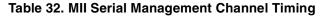

## 13.4 MII Serial Management Channel Timing (MII\_MDIO, MII\_MDC)

Table 32 provides information on the MII serial management channel signal timing. The FEC functions correctly with a maximum MDC frequency in excess of 2.5 MHz. The exact upper bound is under investigation.

| Num | Characteristic                                                              | Min | Max | Unit           |

|-----|-----------------------------------------------------------------------------|-----|-----|----------------|

| M10 | MII_MDC falling edge to MII_MDIO output invalid (minimum propagation delay) | 0   | _   | ns             |

| M11 | MII_MDC falling edge to MII_MDIO output valid (max prop delay)              |     | 25  | ns             |

| M12 | MII_MDIO (input) to MII_MDC rising edge setup                               | 10  | —   | ns             |

| M13 | MII_MDIO (input) to MII_MDC rising edge hold                                | 0   | —   | ns             |

| M14 | MII_MDC pulse width high                                                    | 40% | 60% | MII_MDC period |

| M15 | MII_MDC pulse width low                                                     | 40% | 60% | MII_MDC period |

Figure 76 shows the MII serial management channel timing diagram.

Figure 76. MII Serial Management Channel Timing Diagram

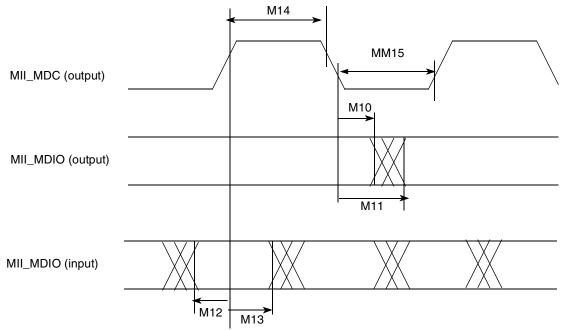

## 14 Mechanical Data and Ordering Information

Table 33 provides information on the MPC862/857T/857DSL derivative devices.

### Table 33. MPC862/857T/857DSL Derivatives

| Device  | Number<br>of      | Ethernet    | Multi-Channel ATM Support |     | Cache Size  |          |

|---------|-------------------|-------------|---------------------------|-----|-------------|----------|

| Device  | SCCs <sup>1</sup> | Support     | HDLC Support              |     | Instruction | Data     |

| MPC862T | Four              | 10/100 Mbps | Yes                       | Yes | 4 Kbytes    | 4 Kbytes |

| MPC862P | Four              | 10/100 Mbps | Yes                       | Yes | 16 Kbytes   | 8 Kbytes |

Figure 77. Pinout of the PBGA Package

| Name                                    | Pin Number | Туре                                    |

|-----------------------------------------|------------|-----------------------------------------|

| PA15<br>RXD1<br>RXD4                    | C18        | Bidirectional                           |

| PA14<br>TXD1<br>TXD4                    | D17        | Bidirectional<br>(Optional: Open-drain) |

| PA13<br>RXD2                            | E17        | Bidirectional                           |

| PA12<br>TXD2                            | F17        | Bidirectional<br>(Optional: Open-drain) |

| PA11<br>L1TXDB<br>RXD3                  | G16        | Bidirectional<br>(Optional: Open-drain) |

| PA10<br>L1RXDB<br>TXD3                  | J17        | Bidirectional<br>(Optional: Open-drain) |

| PA9<br>L1TXDA                           | К18        | Bidirectional<br>(Optional: Open-drain) |

| RXD4                                    |            |                                         |

| PA8<br>L1RXDA<br>TXD4                   | L17        | Bidirectional<br>(Optional: Open-drain) |

| PA7<br>CLK1<br>L1RCLKA<br>BRGO1<br>TIN1 | M19        | Bidirectional                           |

| PA6<br>CLK2<br>TOUT1                    | M17        | Bidirectional                           |

| PA5<br>CLK3<br>L1TCLKA<br>BRGO2<br>TIN2 | N18        | Bidirectional                           |

| PA4<br>CLK4<br>TOUT2                    | P19        | Bidirectional                           |

| PA3<br>CLK5<br>BRGO3<br>TIN3            | P17        | Bidirectional                           |

### Table 35. Pin Assignments (continued)

| Name        | Pin Number                                                                                                                                                                                                                                                                                                                                                                      | Туре          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| TRST        | G19                                                                                                                                                                                                                                                                                                                                                                             | Input         |

| TDO<br>DSDO | G17                                                                                                                                                                                                                                                                                                                                                                             | Output        |

| M_CRS       | B7                                                                                                                                                                                                                                                                                                                                                                              | Input         |

| M_MDIO      | H18                                                                                                                                                                                                                                                                                                                                                                             | Bidirectional |

| M_TXEN      | V15                                                                                                                                                                                                                                                                                                                                                                             | Output        |

| M_COL       | H4                                                                                                                                                                                                                                                                                                                                                                              | Input         |

| KAPWR       | R1                                                                                                                                                                                                                                                                                                                                                                              | Power         |

| GND         | F6, F7, F8, F9, F10, F11, F12, F13, F14, G6, G7, G8, G9, G10, G11, G12, G13, G14, H6, H7, H8, H9, H10, H11, H12, H13, H14, J6, J7, J8, J9, J10, J11, J12, J13, J14, K6, K7, K8, K9, K10, K11, K12, K13, K14, L6, L7, L8, L9, L10, L11, L12, L13, L14, M6, M7, M8, M9, M10, M11, M12, M13, M14, N6, N7, N8, N9, N10, N11, N12, N13, N14, P6, P7, P8, P9, P10, P11, P12, P13, P14 | Power         |

| VDDL        | A8, M1, W8, H19, F4, F16, P4, P16                                                                                                                                                                                                                                                                                                                                               | Power         |

| VDDH        | E5, E6, E7, E8, E9, E10, E11, E12, E13, E14, E15, F5, F15, G5,<br>G15, H5, H15, J5, J15, K5, K15, L5, L15, M5, M15, N5, N15, P5,<br>P15, R5, R6, R7, R8, R9, R10, R11, R12, R13, R14, R15, T14                                                                                                                                                                                  | Power         |

| N/C         | D6, D13, D14, U2, V2                                                                                                                                                                                                                                                                                                                                                            | No-connect    |

### Table 35. Pin Assignments (continued)

<sup>1</sup> Classic SAR mode only

<sup>2</sup> ESAR mode only

## 14.2 Mechanical Dimensions of the PBGA Package

For more information on the printed circuit board layout of the PBGA package, including thermal via design and suggested pad layout, please refer to *Plastic Ball Grid Array Application Note* (order number: AN1231/D) available from your local Freescale sales office. Figure 78 shows the mechanical dimensions of the PBGA package.

**Document Revision History**

# **15 Document Revision History**

Table 36 lists significant changes between revisions of this document.

| Rev. No. | Date    | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 2001    | Initial revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0.1      | 9/2001  | Change extended temperature from 95 to 105                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0.2      | 11/2001 | Revised for new template, changed Table 7 B23 max value @ 66 MHz from 2 ns to 8 ns.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0.3      | 4/2002  | <ul> <li>Timing modified and equations added, for Rev. A and B devices.</li> <li>Modified power numbers and temperature ranges. Added ESAR UTOPIA timing.</li> </ul>                                                                                                                                                                                                                                                                                                                   |

| 1.0      | 9/2002  | <ul> <li>Specification changed to include the MPC857T and MPC857DSL.</li> <li>Changed maximum operating frequency from 80 MHz to 100 MHz.</li> <li>Removed MPC862DP, DT, and SR derivatives and part numbers.</li> <li>Corrected power dissipation numbers.</li> <li>Changed UTOPIA maximum frequency from 50 MHz to 33 MHz.</li> <li>Changed part number ordering information to Rev. B devices only.</li> <li>To maximum ratings for temperature, added frequency ranges.</li> </ul> |

| 1.1      | 5/2003  | Changed SPI Master Timing Specs. 162 and 164                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.2      | 8/2003  | <ul> <li>Changed B28a through B28d and B29b to show that TRLX can be 0 or 1.</li> <li>Non-technical reformatting</li> </ul>                                                                                                                                                                                                                                                                                                                                                            |

| 2.0      | 11/2004 | <ul> <li>Added a table footnote to Table 5 DC Electrical Specifications about meeting the VIL Max of the I2C Standard.</li> <li>Updated document template.</li> </ul>                                                                                                                                                                                                                                                                                                                  |

| 3.0      | 2/2006  | Changed Tj from 95C to 105C in table 34                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### Table 36. Document Revision History