#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XFI

| Product Status                  | Active                                                    |

|---------------------------------|-----------------------------------------------------------|

| Core Processor                  | MPC8xx                                                    |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                            |

| Speed                           | 66MHz                                                     |

| Co-Processors/DSP               | Communications; CPM                                       |

| RAM Controllers                 | DRAM                                                      |

| Graphics Acceleration           | No                                                        |

| Display & Interface Controllers | -                                                         |

| Ethernet                        | 10Mbps (1), 10/100Mbps (1)                                |

| SATA                            | -                                                         |

| USB                             | -                                                         |

| Voltage - I/O                   | 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                          |

| Security Features               | -                                                         |

| Package / Case                  | 357-BBGA                                                  |

| Supplier Device Package         | 357-PBGA (25x25)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc857tvr66b |

|                                 |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

The MPC862/857T/857DSL is a derivative of Freescale's MPC860 PowerQUICC<sup>™</sup> family of devices. It is a versatile single-chip integrated microprocessor and peripheral combination that can be used in a variety of controller applications and communications and networking systems. The MPC862/857T/857DSL provides enhanced ATM functionality over that of other ATM enabled members.

MPC862/857T/857DSL provides enhanced ATM functionality over that of other ATM-enabled members of the MPC860 family.

Table 1 shows the functionality supported by the members of the MPC862/857T/857DSL family.

|           | Ca                   | Ethe       | rnet    |        |                |                |

|-----------|----------------------|------------|---------|--------|----------------|----------------|

| Part      | Instruction<br>Cache | Data Cache | 10T     | 10/100 | SCC            | SMC            |

| MPC862P   | 16 Kbyte             | 8 Kbyte    | Up to 4 | 1      | 4              | 2              |

| MPC862T   | 4 Kbyte              | 4 Kbyte    | Up to 4 | 1      | 4              | 2              |

| MPC857T   | 4 Kbyte              | 4 Kbyte    | 1       | 1      | 1              | 2              |

| MPC857DSL | 4 Kbyte              | 4 Kbyte    | 1       | 1      | 1 <sup>1</sup> | 1 <sup>2</sup> |

Table 1. MPC862 Family Functionality

<sup>1</sup> On the MPC857DSL, the SCC (SCC1) is for ethernet only. Also, the MPC857DSL does not support the Time Slot Assigner (TSA).

<sup>2</sup> On the MPC857DSL, the SMC (SMC1) is for UART only.

# 2 Features

The following list summarizes the key MPC862/857T/857DSL features:

- Embedded single-issue, 32-bit MPC8xx core (implementing the PowerPC architecture) with thirty-two 32-bit general-purpose registers (GPRs)

- The core performs branch prediction with conditional prefetch, without conditional execution

- 4- or 8-Kbyte data cache and 4- or 16-Kbyte instruction cache (see Table 1).

- 16-Kbyte instruction cache (MPC862P) is four-way, set-associative with 256 sets; 4-Kbyte instruction cache (MPC862T, MPC857T, and MPC857DSL) is two-way, set-associative with 128 sets.

- 8-Kbyte data cache (MPC862P) is two-way, set-associative with 256 sets; 4-Kbyte data cache (MPC862T, MPC857T, and MPC857DSL) is two-way, set-associative with 128 sets.

- Cache coherency for both instruction and data caches is maintained on 128-bit (4-word) cache blocks.

- Caches are physically addressed, implement a least recently used (LRU) replacement algorithm, and are lockable on a cache block basis.

- MMUs with 32-entry TLB, fully associative instruction and data TLBs

- MMUs support multiple page sizes of 4, 16, and 512 Kbytes, and 8 Mbytes; 16 virtual address spaces and 16 protection groups

- Advanced on-chip-emulation debug mode

## Table 2. Maximum Tolerated Ratings (continued)

(GND = 0 V)

| Rating                                           | Symbol              | Value           | Unit | Max Freq<br>(MHz) |

|--------------------------------------------------|---------------------|-----------------|------|-------------------|

| Input voltage <sup>2</sup>                       | V <sub>in</sub>     | GND-0.3 to VDDH | V    | -                 |

| Temperature <sup>3</sup> (standard) <sup>4</sup> | T <sub>A(min)</sub> | 0               | °C   | 100               |

|                                                  | T <sub>j(max)</sub> | 105             | °C   | 100               |

| Temperature <sup>3</sup> (extended)              | T <sub>A(min)</sub> | -40             | °C   | 80                |

|                                                  | T <sub>j(max)</sub> | 115             | °C   | 80                |

| Storage temperature range                        | T <sub>stg</sub>    | -55 to +150     | °C   | -                 |

<sup>1</sup> The power supply of the device must start its ramp from 0.0 V.

<sup>2</sup> Functional operating conditions are provided with the DC electrical specifications in Table 5. Absolute maximum ratings are stress ratings only; functional operation at the maxima is not guaranteed. Stress beyond those listed may affect device reliability or cause permanent damage to the device. Caution: All inputs that tolerate 5 V cannot be more than 2.5 V greater than the supply voltage. This restriction applies to power-up and normal operation (that is, if the MPC862/857T/857DSL is unpowered, voltage greater

than 2.5 V must not be applied to its inputs).

<sup>3</sup> Minimum temperatures are guaranteed as ambient temperature, T<sub>A</sub>. Maximum temperatures are guaranteed as

junction temperature, T<sub>j</sub>.

<sup>4</sup> JTAG is tested only at ambient, not at standard maximum or extended maximum.

This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{CC}$ ).

| Die Revision      | Frequency | Typical <sup>1</sup> | Maximum <sup>2</sup> | Unit |

|-------------------|-----------|----------------------|----------------------|------|

| A.1, B.0          | 66 MHz    | 910                  | 1060                 | mW   |

| (2:1 Mode)        | 80 MHz    | 1.06                 | 1.20                 | W    |

| B.0<br>(2:1 Mode) | 100 MHz   | 1.35                 | 1.54                 | W    |

Table 4. Power Dissipation (P<sub>D</sub>) (continued)

<sup>1</sup> Typical power dissipation is measured at 3.3 V.

<sup>2</sup> Maximum power dissipation is measured at 3.5 V.

## NOTE

Values in Table 4 represent VDDL based power dissipation and do not include I/O power dissipation over VDDH. I/O power dissipation varies widely by application due to buffer current, depending on external circuitry.

# 6 DC Characteristics

Table 5 provides the DC electrical characteristics for the MPC862/857T/857DSL.

| Characteristic                                                                                | Symbol                                     | Min        | Мах     | Unit |

|-----------------------------------------------------------------------------------------------|--------------------------------------------|------------|---------|------|

| Operating voltage                                                                             | VDDH, VDDL,<br>KAPWR,<br>VDDSYN            | 3.135      | 3.465   | V    |

|                                                                                               | KAPWR<br>(power-down<br>mode)              | 2.0        | 3.6     | V    |

|                                                                                               | KAPWR<br>(all other<br>operating<br>modes) | VDDH – 0.4 | VDDH    | V    |

| Input High Voltage (all inputs except EXTAL and EXTCLK)                                       | VIH                                        | 2.0        | 5.5     | V    |

| Input Low Voltage <sup>1</sup>                                                                | VIL                                        | GND        | 0.8     | V    |

| EXTAL, EXTCLK Input High Voltage                                                              | VIHC                                       | 0.7*(VCC)  | VCC+0.3 | V    |

| Input Leakage Current, Vin = 5.5 V (Except TMS, TRST, DSCK and DSDI pins)                     | l <sub>in</sub>                            | —          | 100     | μA   |

| Input Leakage Current, Vin = 3.6 V (Except TMS, TRST, DSCK, and DSDI)                         | l <sub>in</sub>                            | —          | 10      | μA   |

| Input Leakage Current, Vin = 0 V (Except TMS, $\overline{\text{TRST}}$ , DSCK, and DSDI pins) | l <sub>in</sub>                            | —          | 10      | μA   |

| Input Capacitance <sup>2</sup>                                                                | C <sub>in</sub>                            | —          | 20      | pF   |

| Output High Voltage, IOH = -2.0 mA, VDDH = 3.0 V<br>(Except XTAL, XFC, and Open drain pins)   | VOH                                        | 2.4        | _       | V    |

**Table 5. DC Electrical Specifications**

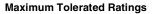

Thermal Calculation and Measurement

| Characteristic                                                                                                                                                                                                       | Symbol | Min | Мах | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|------|

| Output Low Voltage<br>IOL = 2.0 mA (CLKOUT)<br>IOL = $3.2 \text{ mA}^3$<br>IOL = $5.3 \text{ mA}^4$<br>IOL = $7.0 \text{ mA} (TXD1/PA14, TXD2/PA12)$<br>IOL = $8.9 \text{ mA} (TS, TA, TEA, BI, BB, HRESET, SRESET)$ | VOL    | _   | 0.5 | V    |

## Table 5. DC Electrical Specifications (continued)

<sup>1</sup>  $V_{IL}(max)$  for the I<sup>2</sup>C interface is 0.8 V rather than the 1.5 V as specified in the I<sup>2</sup>C standard.

<sup>2</sup> Input capacitance is periodically sampled.

<sup>3</sup> A(0:31), TSIZ0/REG, TSIZ1, D(0:31), DP(0:3)/IRQ(3:6), RD/WR, BURST, RSV/IRQ2, IP\_B(0:1)/IWP(0:1)/VFLS(0:1), IP\_B2/IOIS16\_B/AT2, IP\_B3/IWP2/VF2, IP\_B4/LWP0/VF0, IP\_B5/LWP1/VF1, IP\_B6/DSDI/AT0, IP\_B7/PTR/AT3, RXD1 /PA15, RXD2/PA13, L1TXDB/PA11, L1RXDB/PA10, L1TXDA/PA9, L1RXDA/PA8, TIN1/L1RCLKA/BRGO1/CLK1/PA7, BRGCLK1/TOUT1/CLK2/PA6, TIN2/L1TCLKA/BRGO2/CLK3/PA5, TOUT2/CLK4/PA4, TIN3/BRGO3/CLK5/PA3, BRGCLK2/L1RCLKB/TOUT3/CLK6/PA2, TIN4/BRGO4/CLK7/PA1, L1TCLKB/TOUT4/CLK8/PA0, REJCT1/SPISEL/PB31, SPICLK/PB30, SPIMOSI/PB29, BRGO4/SPIMISO/PB28, BRGO1/I2CSDA/PB27, BRGO2/I2CSCL/PB26, SMTXD1/PB25, SMRXD1/PB29, BRGO4/SPIMISO/PB28, SMSYN2/SDACK2/PB22, SMTXD2/L1CLKOB/PB21, SMRXD2/L1CLKOA/PB20, L1ST1/RTS1/PB19, L1ST2/RTS2/PB18, L1ST3/L1RQB/PB17, L1ST4/L1RQA/PB16, BRGO3/PB15, RSTRT1/PB14, L1ST1/RTS1/DREQ0/PC15, L1ST2/RTS2/DREQ1/PC14, L1ST3/L1RQB/PC13, L1ST4/L1RQA/PC12, CTS1/PC11, TGATE1/CD1/PC10, CTS2/PC9, TGATE2/CD2/PC8, CTS3/SDACK2/L1SYNCB/PC7, CD3/L1RSYNCB/PC6, CTS4/SDACK1/L1TSYNCA/PC5, CD4/L1RSYNCA/PC4, PD15/L1TSYNCA, PD14/L1RSYNCA, PD13/L1TSYNCB, PD12/L1RSYNCB, PD11/RXD3, PD10/TXD3, PD9/RXD4, PD8/TXD4, PD5/REJECT2, PD6/RTS4, PD7/RTS3, PD4/REJECT3, PD3, MII\_MDC, MII\_TX\_ER, MII\_EN, MII\_MDIO, MII\_TXD[0:3].

<sup>4</sup> BDIP/GPL\_B(5), BR, BG, FRZ/IRQ6, CS(0:5), CS(6)/CE(1)\_B, CS(7)/CE(2)\_B, WE0/BS\_B0/IORD, WE1/BS\_B1/IOWR, WE2/BS\_B2/PCOE, WE3/BS\_B3/PCWE, BS\_A(0:3), GPL\_A0/GPL\_B0, OE/GPL\_A1/GPL\_B1, GPL\_A(2:3)/GPL\_B(2:3)/CS(2:3), UPWAITA/GPL\_A4, UPWAITB/GPL\_B4, GPL\_A5, ALE\_A, CE1\_A, CE2\_A, ALE\_B/DSCK/AT1, OP(0:1), OP2/MODCK1/STS, OP3/MODCK2/DSDO, BADDR(28:30).

# 7 Thermal Calculation and Measurement

For the following discussions,  $P_D = (VDD \times IDD) + PI/O$ , where PI/O is the power dissipation of the I/O drivers.

# 7.1 Estimation with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, in °C can be obtained from the equation:

$T_J = T_A + (R_{\theta JA} \times P_D)$

where:

$T_A$  = ambient temperature (°C)

$R_{\theta IA}$  = package junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in package

The junction-to-ambient thermal resistance is an industry standard value which provides a quick and easy estimation of thermal performance. However, the answer is only an estimate; test cases have demonstrated that errors of a factor of two (in the quantity  $T_J$ - $T_A$ ) are possible.

**Thermal Calculation and Measurement**

## 7.2 Estimation with Junction-to-Case Thermal Resistance

Historically, the thermal resistance has frequently been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta IC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user adjusts the thermal environment to affect the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the air flow around the device, add a heat sink, change the mounting arrangement on the printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device. This thermal model is most useful for ceramic packages with heat sinks where some 90% of the heat flows through the case and the heat sink to the ambient environment. For most packages, a better model is required.

## 7.3 Estimation with Junction-to-Board Thermal Resistance

A simple package thermal model which has demonstrated reasonable accuracy (about 20%) is a two resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The junction-to-case covers the situation where a heat sink is used or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed circuit board. It has been observed that the thermal performance of most plastic packages and especially PBGA packages is strongly dependent on the board temperature; see Figure 3.

Figure 3. Effect of Board Temperature Rise on Thermal Behavior

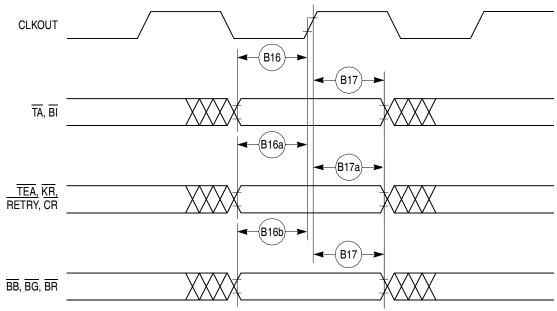

Figure 8 provides the timing for the synchronous input signals.

Figure 8. Synchronous Input Signals Timing

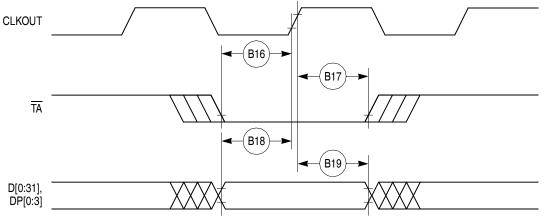

Figure 9 provides normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 9. Input Data Timing in Normal Case

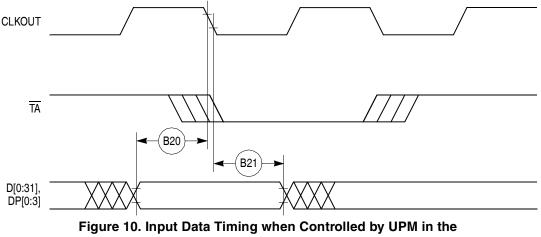

Figure 10 provides the timing for the input data controlled by the UPM for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

Memory Controller and DLT3 = 1

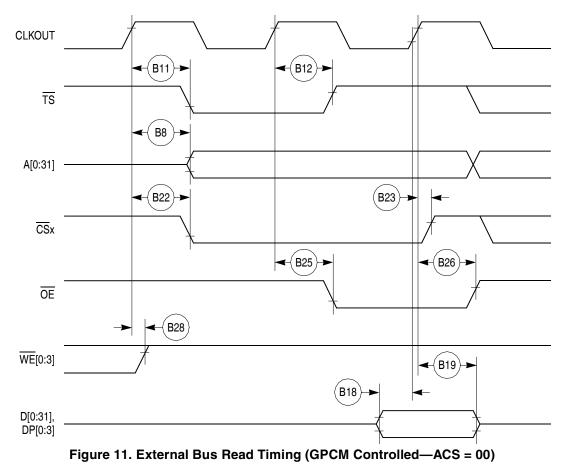

Figure 11 through Figure 14 provide the timing for the external bus read controlled by various GPCM factors.

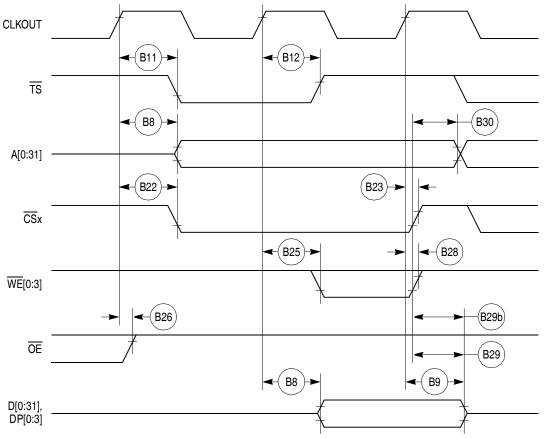

Figure 15 through Figure 17 provide the timing for the external bus write controlled by various GPCM factors.

Figure 15. External Bus Write Timing (GPCM Controlled—TRLX = 0,1 CSNT = 0)

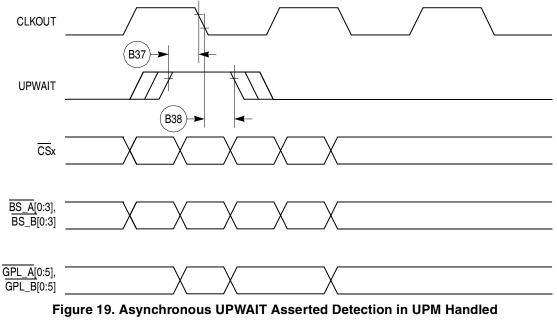

Figure 19 provides the timing for the asynchronous asserted UPWAIT signal controlled by the UPM.

Cycles Timing

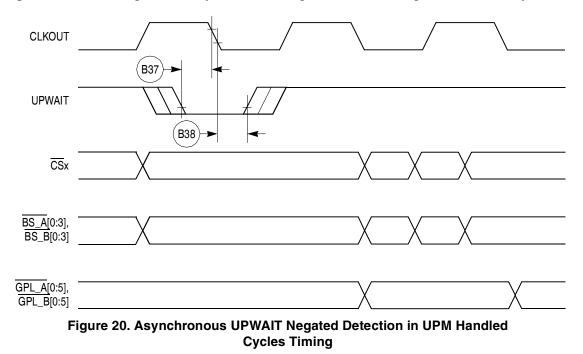

Figure 20 provides the timing for the asynchronous negated UPWAIT signal controlled by the UPM.

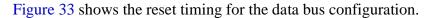

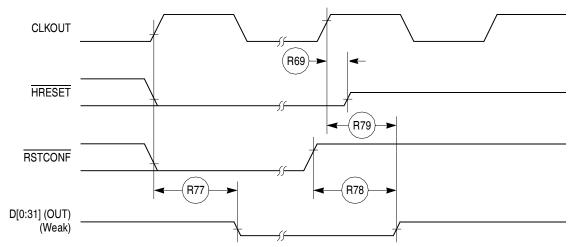

## Table 12 shows the reset timing for the MPC862/857T/857DSL.

Table 12. Reset Timing

| Num | Characteristic                                                                                                                                   | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| NUM |                                                                                                                                                  |        | Max   | Min    | Мах   | Min    | Max   | Min    | Max   | Unit |

| R69 | CLKOUT to $\overline{\text{HRESET}}$ high impedance<br>(MAX = 0.00 x B1 + 20.00)                                                                 | _      | 20.00 | _      | 20.00 | _      | 20.00 | _      | 20.00 | ns   |

| R70 | CLKOUT to $\overline{\text{SRESET}}$ high impedance<br>(MAX = 0.00 x B1 + 20.00)                                                                 |        | 20.00 | —      | 20.00 | _      | 20.00 | —      | 20.00 | ns   |

| R71 | $\overline{\text{RSTCONF}} \text{ pulse width} $ (MIN = 17.00 x B1)                                                                              | 515.20 |       | 425.00 | _     | 340.00 | —     | 257.60 |       | ns   |

| R72 | —                                                                                                                                                |        |       | —      |       | —      | —     | —      | —     | —    |

| R73 | Configuration data to HRESET rising<br>edge set up time<br>(MIN = 15.00 x B1 + 50.00)                                                            | 504.50 | _     | 425.00 | —     | 350.00 | —     | 277.30 | _     | ns   |

| R74 | Configuration data to RSTCONF rising<br>edge set up time<br>(MIN = 0.00 x B1 + 350.00)                                                           | 350.00 | _     | 350.00 | —     | 350.00 | —     | 350.00 | _     | ns   |

| R75 | Configuration data hold time after<br>RSTCONF negation<br>(MIN = 0.00 x B1 + 0.00)                                                               | 0.00   | _     | 0.00   | _     | 0.00   | —     | 0.00   | _     | ns   |

| R76 | Configuration data hold time after<br>HRESET negation<br>(MIN = 0.00 x B1 + 0.00)                                                                | 0.00   | _     | 0.00   | _     | 0.00   | _     | 0.00   | _     | ns   |

| R77 | HRESET and RSTCONF asserted to data out drive (MAX = 0.00 x B1 + 25.00)                                                                          |        | 25.00 | —      | 25.00 | _      | 25.00 | —      | 25.00 | ns   |

| R78 | RSTCONF negated to data out high<br>impedance. (MAX = 0.00 x B1 + 25.00)                                                                         | _      | 25.00 | —      | 25.00 | _      | 25.00 | _      | 25.00 | ns   |

| R79 | CLKOUT of last rising edge before chip<br>three-states $\overrightarrow{\text{HRESET}}$ to data out high<br>impedance. (MAX = 0.00 x B1 + 25.00) | _      | 25.00 | _      | 25.00 | _      | 25.00 | —      | 25.00 | ns   |

| R80 | DSDI, DSCK set up (MIN = 3.00 x B1)                                                                                                              | 90.90  | _     | 75.00  |       | 60.00  | _     | 45.50  | —     | ns   |

| R81 | DSDI, DSCK hold time<br>(MIN = 0.00 x B1 + 0.00)                                                                                                 | 0.00   | _     | 0.00   |       | 0.00   | _     | 0.00   | —     | ns   |

| R82 | SRESET negated to CLKOUT rising<br>edge for DSDI and DSCK sample<br>(MIN = 8.00 x B1)                                                            | 242.40 | _     | 200.00 | —     | 160.00 | —     | 121.20 | —     | ns   |

Figure 33. Reset Timing—Configuration from Data Bus

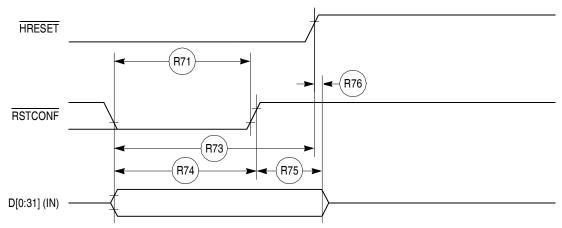

Figure 34 provides the reset timing for the data bus weak drive during configuration.

Figure 34. Reset Timing—Data Bus Weak Drive during Configuration

**CPM Electrical Characteristics**

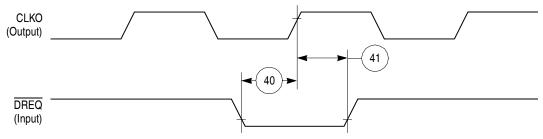

# **11 CPM Electrical Characteristics**

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC862/857T/857DSL.

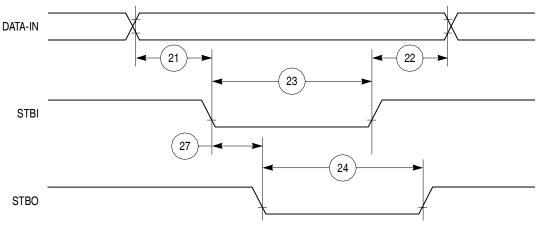

# 11.1 PIP/PIO AC Electrical Specifications

Table 14 provides the PIP/PIO AC timings as shown in Figure 40 though Figure 44.

# Table 14. PIP/PIO Timing

| Num | Characteristic                                                       | All Freq              | uencies | Unit |

|-----|----------------------------------------------------------------------|-----------------------|---------|------|

| Num | Cliaracteristic                                                      | Min                   | Мах     |      |

| 21  | Data-in setup time to STBI low                                       | 0                     | _       | ns   |

| 22  | Data-in hold time to STBI high                                       | 2.5 - t3 <sup>1</sup> | _       | clk  |

| 23  | STBI pulse width                                                     | 1.5                   | _       | clk  |

| 24  | STBO pulse width                                                     | 1 clk – 5 ns          | _       | ns   |

| 25  | Data-out setup time to STBO low                                      | 2                     | _       | clk  |

| 26  | Data-out hold time from STBO high                                    | 5                     | _       | clk  |

| 27  | STBI low to STBO low (Rx interlock)                                  | —                     | 2       | clk  |

| 28  | STBI low to STBO high (Tx interlock)                                 | 2                     | _       | clk  |

| 29  | Data-in setup time to clock high                                     | 15                    | _       | ns   |

| 30  | Data-in hold time from clock high                                    | 7.5                   | _       | ns   |

| 31  | Clock low to data-out valid (CPU writes data, control, or direction) | —                     | 25      | ns   |

<sup>1</sup> t3 = Specification 23

Figure 40. PIP Rx (Interlock Mode) Timing Diagram

#### **CPM Electrical Characteristics**

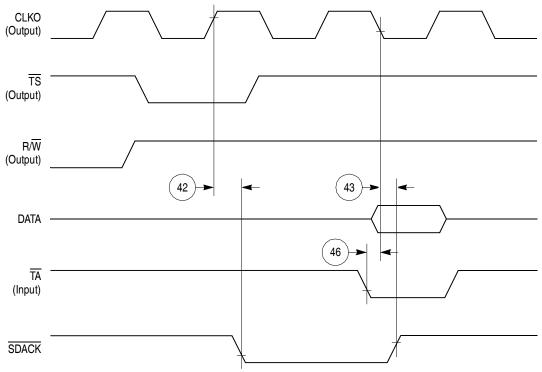

| Num | Characteristic                                                                                           |     | All Frequencies |      |  |

|-----|----------------------------------------------------------------------------------------------------------|-----|-----------------|------|--|

|     | Characteristic                                                                                           | Min | Мах             | Unit |  |

| 43  | SDACK negation delay from clock low                                                                      | _   | 12              | ns   |  |

| 44  | SDACK negation delay from TA low                                                                         | _   | 20              | ns   |  |

| 45  | SDACK negation delay from clock high                                                                     | _   | 15              | ns   |  |

| 46  | $\overline{TA}$ assertion to falling edge of the clock setup time (applies to external $\overline{TA}$ ) | 7   | —               | ns   |  |

## Table 16. IDMA Controller Timing (continued)

Figure 46. IDMA External Requests Timing Diagram

Figure 47. SDACK Timing Diagram—Peripheral Write, Externally-Generated TA

**CPM Electrical Characteristics**

# 11.12 I<sup>2</sup>C AC Electrical Specifications

Table 26 provides the  $I^2C$  (SCL < 100 KHz) timings.

| Table 26. | I <sup>2</sup> C | Timing | (SCL < | 100 KHz) |

|-----------|------------------|--------|--------|----------|

|-----------|------------------|--------|--------|----------|

| Num | Characteristic                            | All Frequencies |     | Unit |

|-----|-------------------------------------------|-----------------|-----|------|

| Num | Characteristic                            |                 | Мах | Unit |

| 200 | SCL clock frequency (slave)               | 0               | 100 | kHz  |

| 200 | SCL clock frequency (master) <sup>1</sup> | 1.5             | 100 | kHz  |

| 202 | Bus free time between transmissions       | 4.7             | —   | μs   |

| 203 | Low period of SCL                         | 4.7             | —   | μs   |

| 204 | High period of SCL                        | 4.0             | —   | μs   |

| 205 | Start condition setup time                | 4.7             | —   | μs   |

| 206 | Start condition hold time                 | 4.0             | —   | μs   |

| 207 | Data hold time                            | 0               | —   | μs   |

| 208 | Data setup time                           | 250             | —   | ns   |

| 209 | SDL/SCL rise time                         | —               | 1   | μs   |

| 210 | SDL/SCL fall time                         | —               | 300 | ns   |

| 211 | Stop condition setup time                 | 4.7             | —   | μs   |

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(BRGCLK/pre\_scaler) must be greater or equal to 4/1.

## Table 27 provides the $I^2C$ (SCL > 100 kHz) timings.

Table 27.  $I^2C$  Timing (SCL > 100 kHz)

| Num | Characteristic                            | Expression | All Freq        | Unit          |      |

|-----|-------------------------------------------|------------|-----------------|---------------|------|

| Num | Characteristic                            | Lyression  | Min             | Мах           | Onit |

| 200 | SCL clock frequency (slave)               | fSCL       | 0               | BRGCLK/48     | Hz   |

| 200 | SCL clock frequency (master) <sup>1</sup> | fSCL       | BRGCLK/16512    | BRGCLK/48     | Hz   |

| 202 | Bus free time between transmissions       | —          | 1/(2.2 * fSCL)  | _             | S    |

| 203 | Low period of SCL                         | —          | 1/(2.2 * fSCL)  | _             | S    |

| 204 | High period of SCL                        | —          | 1/(2.2 * fSCL)  | _             | S    |

| 205 | Start condition setup time                | —          | 1/(2.2 * fSCL)  | _             | S    |

| 206 | Start condition hold time                 | —          | 1/(2.2 * fSCL)  | _             | S    |

| 207 | Data hold time                            | —          | 0               | _             | S    |

| 208 | Data setup time                           | —          | 1/(40 * fSCL)   | _             | S    |

| 209 | SDL/SCL rise time                         | —          | —               | 1/(10 * fSCL) | S    |

| 210 | SDL/SCL fall time                         | —          | —               | 1/(33 * fSCL) | S    |

| 211 | Stop condition setup time                 | —          | 1/2(2.2 * fSCL) | _             | S    |

SCL frequency is given by SCL = BrgClk\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(Brg\_Clk/pre\_scaler) must be greater or equal to 4/1.

### MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

1

| Name                                           | Pin Number | Туре                         |

|------------------------------------------------|------------|------------------------------|

| IP_A6<br>UTPB_Split6 <sup>2</sup><br>MII-TXERR | Тб         | Input                        |

| IP_A7<br>UTPB_Split7 <sup>2</sup><br>MII-RXDV  | ТЗ         | Input                        |

| ALE_B<br>DSCK/AT1                              | J1         | Bidirectional<br>Three-state |

| IP_B[0:1]<br>IWP[0:1]<br>VFLS[0:1]             | H2, J3     | Bidirectional                |

| IP_B2<br>IOIS16_B<br>AT2                       | J2         | Bidirectional<br>Three-state |

| IP_B3<br>IWP2<br>VF2                           | G1         | Bidirectional                |

| IP_B4<br>LWP0<br>VF0                           | G2         | Bidirectional                |

| IP_B5<br>LWP1<br>VF1                           | J4         | Bidirectional                |

| IP_B6<br>DSDI<br>AT0                           | КЗ         | Bidirectional<br>Three-state |

| IP_B7<br>PTR<br>AT3                            | H1         | Bidirectional<br>Three-state |

| OP0<br>MII-TXD0<br>UtpClk_Split <sup>2</sup>   | L4         | Bidirectional                |

| OP1                                            | L2         | Output                       |

| OP2<br>MODCK1<br>STS                           | L1         | Bidirectional                |

| OP3<br>MODCK2<br>DSDO                          | M4         | Bidirectional                |

| BADDR30<br>REG                                 | K4         | Output                       |

| BADDR[28:29]                                   | M3, M2     | Output                       |

| ĀS                                             | L3         | Input                        |

## Table 35. Pin Assignments (continued)

| Name                                    | Pin Number | Туре                                    |

|-----------------------------------------|------------|-----------------------------------------|

| PA15<br>RXD1<br>RXD4                    | C18        | Bidirectional                           |

| PA14<br>TXD1<br>TXD4                    | D17        | Bidirectional<br>(Optional: Open-drain) |

| PA13<br>RXD2                            | E17        | Bidirectional                           |

| PA12<br>TXD2                            | F17        | Bidirectional<br>(Optional: Open-drain) |

| PA11<br>L1TXDB<br>RXD3                  | G16        | Bidirectional<br>(Optional: Open-drain) |

| PA10<br>L1RXDB<br>TXD3                  | J17        | Bidirectional<br>(Optional: Open-drain) |

| PA9<br>L1TXDA                           | К18        | Bidirectional<br>(Optional: Open-drain) |

| RXD4                                    |            |                                         |

| PA8<br>L1RXDA<br>TXD4                   | L17        | Bidirectional<br>(Optional: Open-drain) |

| PA7<br>CLK1<br>L1RCLKA<br>BRGO1<br>TIN1 | M19        | Bidirectional                           |

| PA6<br>CLK2<br>TOUT1                    | M17        | Bidirectional                           |

| PA5<br>CLK3<br>L1TCLKA<br>BRGO2<br>TIN2 | N18        | Bidirectional                           |

| PA4<br>CLK4<br>TOUT2                    | P19        | Bidirectional                           |

| PA3<br>CLK5<br>BRGO3<br>TIN3            | P17        | Bidirectional                           |

## Table 35. Pin Assignments (continued)

| Table 35. Pin Assignments | (continued) |

|---------------------------|-------------|

|---------------------------|-------------|

| Name                                 | Pin Number | Туре          |

|--------------------------------------|------------|---------------|

| PD12<br>L1RSYNCB<br>MII-MDC<br>UTPB3 | R16        | Bidirectional |

| PD11<br>RXD3<br>MII-TXERR<br>RXENB   | T16        | Bidirectional |

| PD10<br>TXD3<br>MII-RXD0<br>TXENB    | W18        | Bidirectional |

| PD9<br>RXD4<br>MII-TXD0<br>UTPCLK    | V17        | Bidirectional |

| PD8<br>TXD4<br>MII-MDC<br>MII-RXCLK  | W17        | Bidirectional |

| PD7<br>RTS3<br>MII-RXERR<br>UTPB4    | T15        | Bidirectional |

| PD6<br>RTS4<br>MII-RXDV<br>UTPB5     | V16        | Bidirectional |

| PD5<br>REJECT2<br>MII-TXD3<br>UTPB6  | U15        | Bidirectional |

| PD4<br>REJECT3<br>MII-TXD2<br>UTPB7  | U16        | Bidirectional |

| PD3<br>REJECT4<br>MII-TXD1<br>SOC    | W16        | Bidirectional |

| TMS                                  | G18        | Input         |

| TDI<br>DSDI                          | H17        | Input         |

| TCK<br>DSCK                          | H16        | Input         |

| Name        | Pin Number                                                                                                                                                                                                                                                                                                                                                                      | Туре          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| TRST        | G19                                                                                                                                                                                                                                                                                                                                                                             | Input         |

| TDO<br>DSDO | G17                                                                                                                                                                                                                                                                                                                                                                             | Output        |

| M_CRS       | B7                                                                                                                                                                                                                                                                                                                                                                              | Input         |

| M_MDIO      | H18                                                                                                                                                                                                                                                                                                                                                                             | Bidirectional |

| M_TXEN      | V15                                                                                                                                                                                                                                                                                                                                                                             | Output        |

| M_COL       | H4                                                                                                                                                                                                                                                                                                                                                                              | Input         |

| KAPWR       | R1                                                                                                                                                                                                                                                                                                                                                                              | Power         |

| GND         | F6, F7, F8, F9, F10, F11, F12, F13, F14, G6, G7, G8, G9, G10, G11, G12, G13, G14, H6, H7, H8, H9, H10, H11, H12, H13, H14, J6, J7, J8, J9, J10, J11, J12, J13, J14, K6, K7, K8, K9, K10, K11, K12, K13, K14, L6, L7, L8, L9, L10, L11, L12, L13, L14, M6, M7, M8, M9, M10, M11, M12, M13, M14, N6, N7, N8, N9, N10, N11, N12, N13, N14, P6, P7, P8, P9, P10, P11, P12, P13, P14 | Power         |

| VDDL        | A8, M1, W8, H19, F4, F16, P4, P16                                                                                                                                                                                                                                                                                                                                               | Power         |

| VDDH        | E5, E6, E7, E8, E9, E10, E11, E12, E13, E14, E15, F5, F15, G5,<br>G15, H5, H15, J5, J15, K5, K15, L5, L15, M5, M15, N5, N15, P5,<br>P15, R5, R6, R7, R8, R9, R10, R11, R12, R13, R14, R15, T14                                                                                                                                                                                  | Power         |

| N/C         | D6, D13, D14, U2, V2                                                                                                                                                                                                                                                                                                                                                            | No-connect    |

## Table 35. Pin Assignments (continued)

<sup>1</sup> Classic SAR mode only

<sup>2</sup> ESAR mode only

# 14.2 Mechanical Dimensions of the PBGA Package

For more information on the printed circuit board layout of the PBGA package, including thermal via design and suggested pad layout, please refer to *Plastic Ball Grid Array Application Note* (order number: AN1231/D) available from your local Freescale sales office. Figure 78 shows the mechanical dimensions of the PBGA package.