#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 80MHz                                                                 |

| Co-Processors/DSP               | Communications; CPM                                                   |

| RAM Controllers                 | DRAM                                                                  |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10Mbps (4), 10/100Mbps (1)                                            |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 3.3V                                                                  |

| Operating Temperature           | -40°C ~ 115°C (TA)                                                    |

| Security Features               | -                                                                     |

| Package / Case                  | 357-BBGA                                                              |

| Supplier Device Package         | 357-PBGA (25x25)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc862pcvr80b |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

- Sleep—All units disabled except RTC, PIT, time base, and decrementer with PLL active for fast wake up

- Deep sleep—All units disabled including PLL except RTC, PIT, time base, and decrementer.

- Power down mode- All units powered down except PLL, RTC, PIT, time base and

- decrementerDebug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two

operate on data

- Supports conditions:  $= \neq < >$

- Each watchpoint can generate a break point internally

- 3.3 V operation with 5-V TTL compatibility except EXTAL and EXTCLK

- 357-pin plastic ball grid array (PBGA) package

- Operation up to 100MHz

The MPC862/857T/857DSL is comprised of three modules that each use the 32-bit internal bus: the MPC8xx core, the system integration unit (SIU), and the communication processor module (CPM). The MPC862P/862T block diagram is shown in Figure 1. The MPC857T/857DSL block diagram is shown in Figure 2.

#### **Thermal Calculation and Measurement**

If the board temperature is known, an estimate of the junction temperature in the environment can be made using the following equation:

$$T_{J} = T_{B} + (R_{\theta JB} \times P_{D})$$

where:

$R_{\theta JB}$  = junction-to-board thermal resistance (°C/W)

$T_{B}$  = board temperature (°C)

$P_D$  = power dissipation in package

If the board temperature is known and the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. For this method to work, the board and board mounting must be similar to the test board used to determine the junction-to-board thermal resistance, namely a 2s2p (board with a power and a ground plane) and vias attaching the thermal balls to the ground plane.

# 7.4 Estimation Using Simulation

When the board temperature is not known, a thermal simulation of the application is needed. The simple two resistor model can be used with the thermal simulation of the application [2], or a more accurate and complex model of the package can be used in the thermal simulation.

# 7.5 Experimental Determination

To determine the junction temperature of the device in the application after prototypes are available, the thermal characterization parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$T_J = T_T + (\Psi_{JT} \times P_D)$

where:

$\Psi_{\text{IT}}$  = thermal characterization parameter

$T_T$  = thermocouple temperature on top of package

$P_D$  = power dissipation in package

The thermal characterization parameter is measured per JESD51-2 specification published by JEDEC using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

**Bus Signal Timing**

| Num  | Oh ava stavistis                                                                                                                                  | 33    | MHz   | 40    | MHz   | 50   | MHz   | 66   | MHz   | 11   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|------|-------|------|-------|------|

| Num  | Characteristic                                                                                                                                    | Min   | Max   | Min   | Max   | Min  | Max   | Min  | Мах   | Unit |

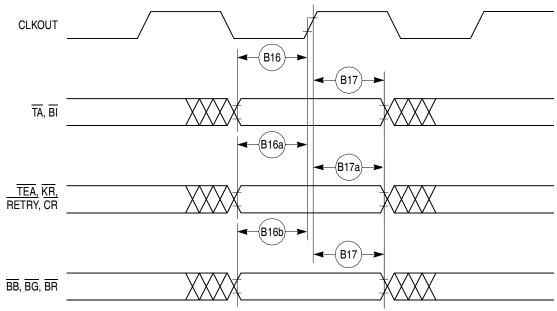

| B17a | CLKOUT to KR, RETRY, CR valid<br>(hold time) (MIN = 0.00 x B1 + 2.00)                                                                             | 2.00  | _     | 2.00  | —     | 2.00 | —     | 2.00 | —     | ns   |

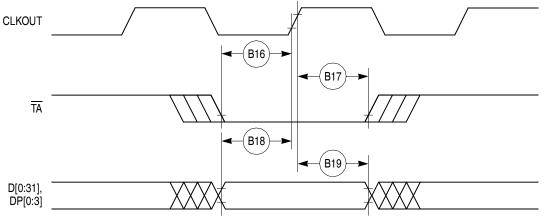

| B18  | D(0:31), DP(0:3) valid to CLKOUT<br>rising edge (setup time) <sup>8</sup> (MIN = 0.00<br>x B1 + 6.00)                                             | 6.00  | —     | 6.00  | —     | 6.00 | _     | 6.00 | —     | ns   |

| B19  | CLKOUT rising edge to D(0:31),<br>DP(0:3) valid (hold time) <sup>8</sup> (MIN = 0.00<br>x B1 + 1.00 <sup>9</sup> )                                | 1.00  | —     | 1.00  | —     | 1.00 | _     | 2.00 | —     | ns   |

| B20  | D(0:31), DP(0:3) valid to CLKOUT<br>falling edge (setup time) $^{10}$ (MIN = 0.00<br>x B1 + 4.00)                                                 | 4.00  | _     | 4.00  | _     | 4.00 | _     | 4.00 | _     | ns   |

| B21  | CLKOUT falling edge to D(0:31),<br>DP(0:3) valid (hold Time) <sup>10</sup> (MIN =<br>0.00 x B1 + 2.00)                                            | 2.00  | —     | 2.00  | —     | 2.00 | _     | 2.00 | —     | ns   |

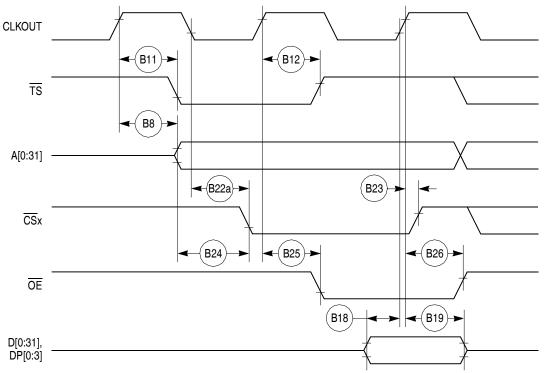

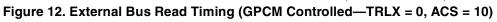

| B22  | CLKOUT rising edge to $\overline{CS}$ asserted<br>GPCM ACS = 00 (MAX = 0.25 x B1 + 6.3)                                                           | 7.60  | 13.80 | 6.30  | 12.50 | 5.00 | 11.30 | 3.80 | 10.00 | ns   |

| B22a | CLKOUT falling edge to CS asserted<br>GPCM ACS = 10, TRLX = 0 (MAX =<br>0.00 x B1 + 8.00)                                                         | —     | 8.00  |       | 8.00  | —    | 8.00  |      | 8.00  | ns   |

| B22b | CLKOUT falling edge to <del>CS</del> asserted<br>GPCM ACS = 11, TRLX = 0, EBDF =<br>0 (MAX = 0.25 x B1 + 6.3)                                     | 7.60  | 13.80 | 6.30  | 12.50 | 5.00 | 11.30 | 3.80 | 10.00 | ns   |

| B22c | CLKOUT falling edge to <del>CS</del> asserted<br>GPCM ACS = 11, TRLX = 0, EBDF =<br>1 (MAX = 0.375 x B1 + 6.6)                                    | 10.90 | 18.00 | 10.90 | 18.00 | 7.00 | 14.30 | 5.20 | 12.30 | ns   |

| B23  | CLKOUT rising edge to $\overline{CS}$ negated<br>GPCM read access, GPCM write<br>access ACS = 00, TRLX = 0 & CSNT =<br>0 (MAX = 0.00 x B1 + 8.00) | 2.00  | 8.00  | 2.00  | 8.00  | 2.00 | 8.00  | 2.00 | 8.00  | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 10, TRLX = 0<br>(MIN = 0.25 x B1 - 2.00)                                       | 5.60  | —     | 4.30  | —     | 3.00 | —     | 1.80 | —     | ns   |

| B24a | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 11 TRLX = 0<br>(MIN = 0.50 x B1 - 2.00)                                        | 13.20 | _     | 10.50 | _     | 8.00 | _     | 5.60 | _     | ns   |

| B25  | CLKOUT rising edge to $\overline{OE}$ , $\overline{WE}(0:3)$<br>asserted (MAX = 0.00 x B1 + 9.00)                                                 | —     | 9.00  |       | 9.00  |      | 9.00  |      | 9.00  | ns   |

| B26  | CLKOUT rising edge to $\overline{OE}$ negated<br>(MAX = 0.00 x B1 + 9.00)                                                                         | 2.00  | 9.00  | 2.00  | 9.00  | 2.00 | 9.00  | 2.00 | 9.00  | ns   |

# Table 7. Bus Operation Timings (continued)

|      | Oh one of a single                                                                                                                                                                                                                                                                        | 33    | MHz   | 40    | MHz   | 50 I  | MHz   | 66 I  | MHz   |      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Num  | Characteristic                                                                                                                                                                                                                                                                            | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| B30c | $\overline{WE}(0:3) \text{ negated to } A(0:31),$<br>BADDR(28:30) invalid GPCM write<br>access, TRLX = 0, CSNT = 1.<br>$\overline{CS} \text{ negated to } A(0:31) \text{ invalid GPCM}$<br>write access, TRLX = 0, CSNT = 1<br>ACS = 10, ACS == 11, EBDF = 1<br>(MIN = 0.375 x B1 - 3.00) | 8.40  |       | 6.40  |       | 4.50  |       | 2.70  |       | ns   |

| B30d | $\overline{WE}$ (0:3) negated to A(0:31),<br>BADDR(28:30) invalid GPCM write<br>access TRLX = 1, CSNT =1,<br>$\overline{CS}$ negated to A(0:31) invalid GPCM<br>write access TRLX = 1, CSNT = 1,<br>ACS = 10 or 11, EBDF = 1                                                              | 38.67 | _     | 31.38 |       | 24.50 | _     | 17.83 | _     | ns   |

| B31  | CLKOUT falling edge to $\overline{CS}$ valid - as<br>requested by control bit CST4 in the<br>corresponding word in the UPM<br>(MAX = 0.00 X B1 + 6.00)                                                                                                                                    | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | ns   |

| B31a | CLKOUT falling edge to $\overline{CS}$ valid - as<br>requested by control bit CST1 in the<br>corresponding word in the UPM<br>(MAX = 0.25 x B1 + 6.80)                                                                                                                                    | 7.60  | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80  | 10.50 | ns   |

| B31b | CLKOUT rising edge to $\overline{CS}$ valid - as<br>requested by control bit CST2 in the<br>corresponding word in the UPM<br>(MAX = 0.00 x B1 + 8.00)                                                                                                                                     | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | ns   |

| B31c | CLKOUT rising edge to $\overline{CS}$ valid- as<br>requested by control bit CST3 in the<br>corresponding word in the UPM<br>(MAX = 0.25 x B1 + 6.30)                                                                                                                                      | 7.60  | 13.80 | 6.30  | 12.50 | 5.00  | 11.30 | 3.80  | 10.00 | ns   |

| B31d | CLKOUT falling edge to $\overline{CS}$ valid, as<br>requested by control bit CST1 in the<br>corresponding word in the UPM<br>EBDF = 1 (MAX = 0.375 x B1 + 6.6)                                                                                                                            | 9.40  | 18.00 | 7.60  | 16.00 | 13.30 | 14.10 | 11.30 | 12.30 | ns   |

| B32  | CLKOUT falling edge to $\overline{\text{BS}}$ valid- as<br>requested by control bit BST4 in the<br>corresponding word in the UPM<br>(MAX = 0.00 x B1 + 6.00)                                                                                                                              | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | ns   |

| B32a | CLKOUT falling edge to $\overline{\text{BS}}$ valid - as<br>requested by control bit BST1 in the<br>corresponding word in the UPM,<br>EBDF = 0 (MAX = 0.25 x B1 + 6.80)                                                                                                                   | 7.60  | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80  | 10.50 | ns   |

| B32b | CLKOUT rising edge to $\overline{BS}$ valid - as<br>requested by control bit BST2 in the<br>corresponding word in the UPM<br>(MAX = 0.00 x B1 + 8.00)                                                                                                                                     | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50  | 8.00  | ns   |

# Table 7. Bus Operation Timings (continued)

**Bus Signal Timing**

Figure 8 provides the timing for the synchronous input signals.

Figure 8. Synchronous Input Signals Timing

Figure 9 provides normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 9. Input Data Timing in Normal Case

**Bus Signal Timing**

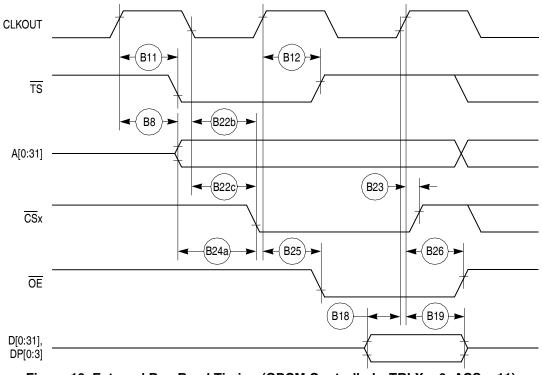

Figure 13. External Bus Read Timing (GPCM Controlled—TRLX = 0, ACS = 11)

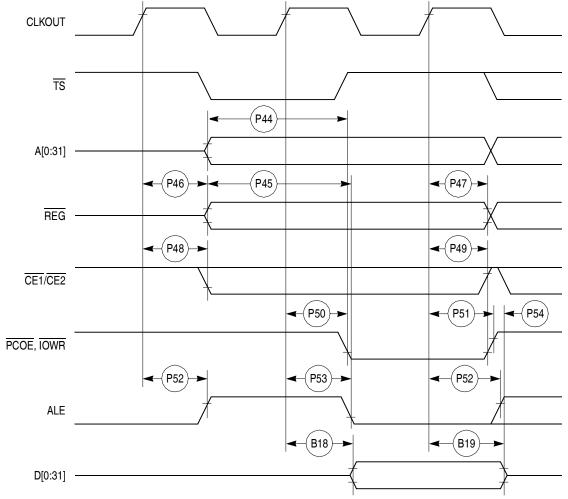

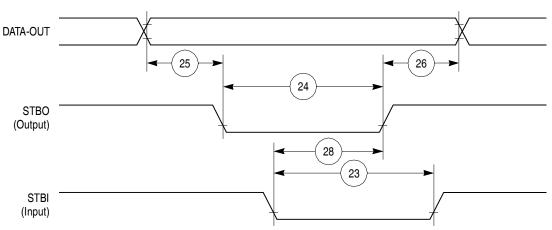

Figure 27 provides the PCMCIA access cycle timing for the external bus write.

Figure 27. PCMCIA Access Cycles Timing External Bus Write

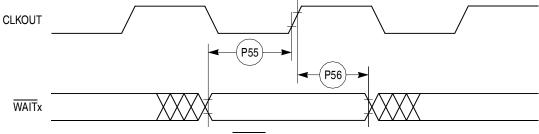

Figure 28 provides the PCMCIA WAIT signals detection timing.

Figure 28. PCMCIA WAIT Signals Detection Timing

Bus Signal Timing

# Table 10 shows the PCMCIA port timing for the MPC862/857T/857DSL.

| Table | 10. | <b>PCMCIA</b> | Port | Timina |

|-------|-----|---------------|------|--------|

| 10010 |     | 1 0 11 0 17   |      |        |

| Num | Num Characteristic                                              |       | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |      |

|-----|-----------------------------------------------------------------|-------|--------|-------|--------|-------|--------|-------|--------|------|

| Num | Characteristic                                                  | Min   | Max    | Min   | Max    | Min   | Мах    | Min   | Max    | Unit |

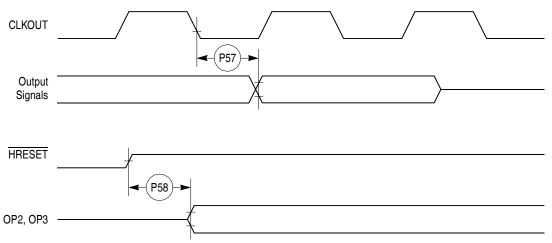

| P57 | CLKOUT to OPx Valid (MAX = 0.00 x<br>B1 + 19.00)                | _     | 19.00  | _     | 19.00  | _     | 19.00  | _     | 19.00  | ns   |

| P58 | HRESET negated to OPx drive $^{1}$ (MIN = 0.75 x B1 + 3.00)     | 25.70 | _      | 21.70 | —      | 18.00 | _      | 14.40 | _      | ns   |

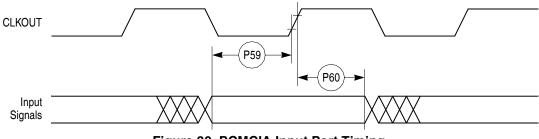

| P59 | IP_Xx valid to CLKOUT rising edge<br>(MIN = 0.00 x B1 + 5.00)   | 5.00  | _      | 5.00  | _      | 5.00  | _      | 5.00  | _      | ns   |

| P60 | CLKOUT rising edge to IP_Xx invalid<br>(MIN = 0.00 x B1 + 1.00) | 1.00  | _      | 1.00  | _      | 1.00  | _      | 1.00  | _      | ns   |

<sup>1</sup> OP2 and OP3 only.

# Figure 29 provides the PCMCIA output port timing for the MPC862/857T/857DSL.

## Figure 29. PCMCIA Output Port Timing

Figure 30 provides the PCMCIA output port timing for the MPC862/857T/857DSL.

Figure 30. PCMCIA Input Port Timing

Table 11 shows the debug port timing for the MPC862/857T/857DSL.

| Num   | Characteristic              | All Freq                     | uencies | Unit |

|-------|-----------------------------|------------------------------|---------|------|

| Nulli | Characteristic              | Min                          | Мах     | Unit |

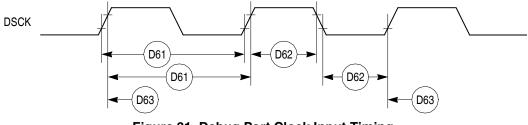

| D61   | DSCK cycle time             | 3 x T <sub>CLOCKOUT</sub>    |         | -    |

| D62   | DSCK clock pulse width      | 1.25 x T <sub>CLOCKOUT</sub> |         | -    |

| D63   | DSCK rise and fall times    | 0.00                         | 3.00    | ns   |

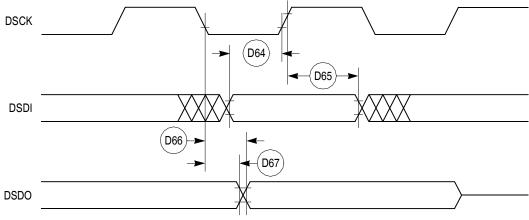

| D64   | DSDI input data setup time  | 8.00                         |         | ns   |

| D65   | DSDI data hold time         | 5.00                         |         | ns   |

| D66   | DSCK low to DSDO data valid | 0.00                         | 15.00   | ns   |

| D67   | DSCK low to DSDO invalid    | 0.00                         | 2.00    | ns   |

#### Table 11. Debug Port Timing

Figure 31 provides the input timing for the debug port clock.

Figure 31. Debug Port Clock Input Timing

Figure 32 provides the timing for the debug port.

Figure 32. Debug Port Timings

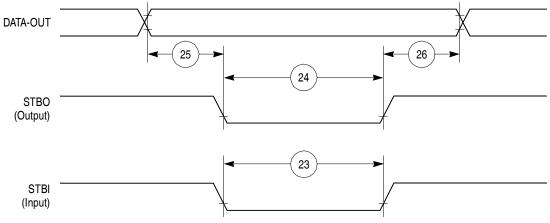

Figure 42. PIP Rx (Pulse Mode) Timing Diagram

Figure 43. PIP TX (Pulse Mode) Timing Diagram

| Num | Characteristic                                                      | All Freq | Unit  |            |

|-----|---------------------------------------------------------------------|----------|-------|------------|

| Num | Characteristic                                                      | Min      | Max   |            |

| 83a | L1RCLK, L1TCLK width high $(DSC = 1)^3$                             | P + 10   | _     | ns         |

| 84  | L1CLK edge to L1CLKO valid (DSC = 1)                                | _        | 30.00 | ns         |

| 85  | L1RQ valid before falling edge of L1TSYNC <sup>4</sup>              | 1.00     | _     | L1TCL<br>K |

| 86  | L1GR setup time <sup>2</sup>                                        | 42.00    | _     | ns         |

| 87  | L1GR hold time                                                      | 42.00    | _     | ns         |

| 88  | L1CLK edge to L1SYNC valid (FSD = 00) CNT = 0000, BYT = 0, DSC = 0) | _        | 0.00  | ns         |

#### Table 19. SI Timing (continued)

<sup>1</sup> The ratio SyncCLK/L1RCLK must be greater than 2.5/1.

<sup>2</sup> These specs are valid for IDL mode only.

<sup>3</sup> Where P = 1/CLKOUT. Thus for a 25-MHz CLKO1 rate, P = 40 ns.

<sup>4</sup> These strobes and TxD on the first bit of the frame become valid after L1CLK edge or L1SYNC, whichever is later.

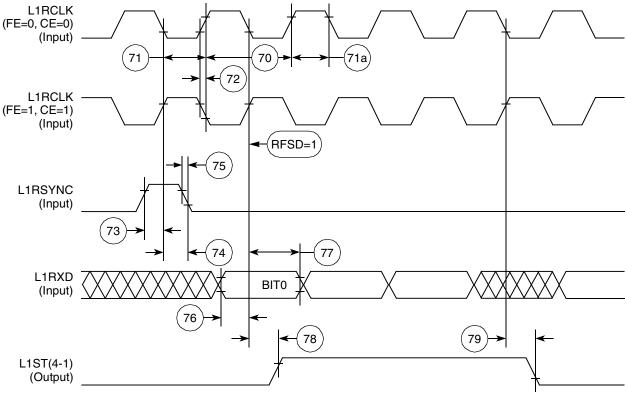

Figure 52. SI Receive Timing Diagram with Normal Clocking (DSC = 0)

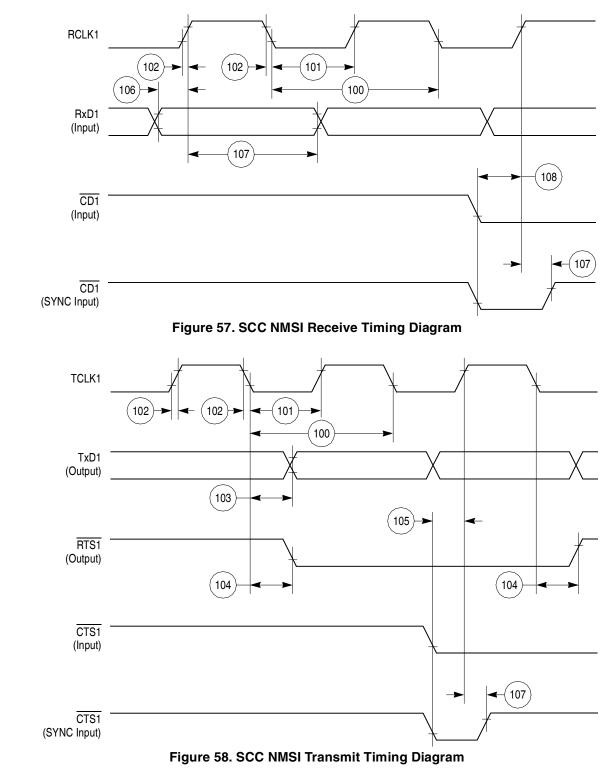

# 11.7 SCC in NMSI Mode Electrical Specifications

Table 20 provides the NMSI external clock timing.

### Table 20. NMSI External Clock Timing

| Num   | Characteristic                                       | All Freq     | uencies | Unit |

|-------|------------------------------------------------------|--------------|---------|------|

| Nulli | Characteristic                                       | Min          | Мах     | onn  |

| 100   | RCLK1 and TCLK1 width high <sup>1</sup>              | 1/SYNCCLK    | _       | ns   |

| 101   | RCLK1 and TCLK1 width low                            | 1/SYNCCLK +5 | _       | ns   |

| 102   | RCLK1 and TCLK1 rise/fall time                       | —            | 15.00   | ns   |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00         | 50.00   | ns   |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00         | 50.00   | ns   |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 5.00         | _       | ns   |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 5.00         | _       | ns   |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 5.00         | _       | ns   |

| 108   | CD1 setup Time to RCLK1 rising edge                  | 5.00         | _       | ns   |

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater than or equal to 2.25/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signal.

Table 21 provides the NMSI internal clock timing.

Table 21. NMSI Internal Clock Timing

| Num   | Characteristic                                       | All Freq | Unit      |      |

|-------|------------------------------------------------------|----------|-----------|------|

| Nulli |                                                      | Min      | Мах       | Omit |

| 100   | RCLK1 and TCLK1 frequency <sup>1</sup>               | 0.00     | SYNCCLK/3 | MHz  |

| 102   | RCLK1 and TCLK1 rise/fall time                       | —        | —         | ns   |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00     | 30.00     | ns   |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00     | 30.00     | ns   |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 40.00    | —         | ns   |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 40.00    | —         | ns   |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 0.00     | —         | ns   |

| 108   | CD1 setup time to RCLK1 rising edge                  | 40.00    | —         | ns   |

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signals.

**CPM Electrical Characteristics**

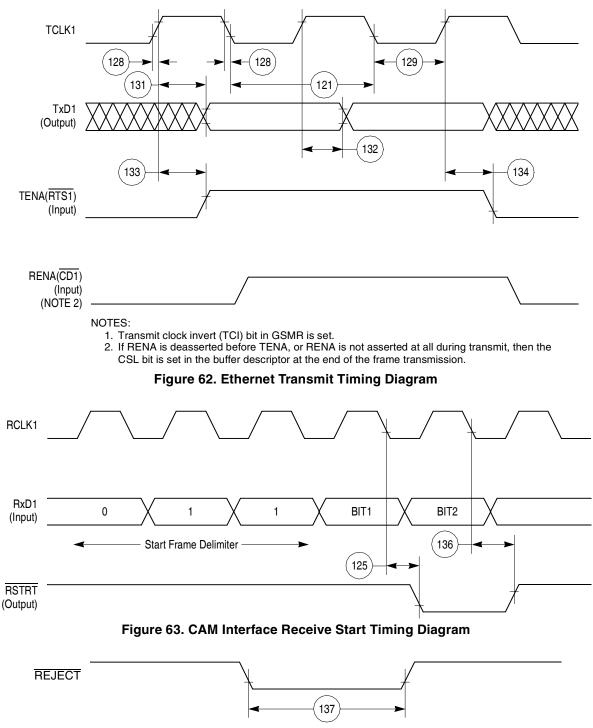

Figure 57 through Figure 59 show the NMSI timings.

Figure 64. CAM Interface REJECT Timing Diagram

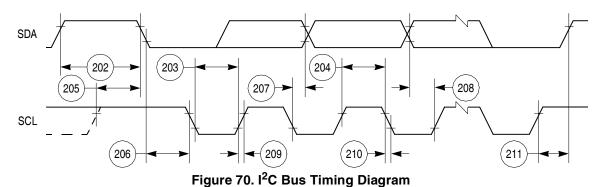

#### **UTOPIA AC Electrical Specifications**

Figure 70 shows the  $I^2C$  bus timing.

# **12 UTOPIA AC Electrical Specifications**

Table 28 shows the AC electrical specifications for the UTOPIA interface.

| Num | Signal Characteristic                                                  | Direction | Min  | Max   | Unit |

|-----|------------------------------------------------------------------------|-----------|------|-------|------|

| U1  | UtpClk rise/fall time (Internal clock option)                          | Output    |      | 4 ns  | ns   |

|     | Duty cycle                                                             |           | 50   | 50    | %    |

|     | Frequency                                                              |           |      | 33    | MHz  |

| U1a | UtpClk rise/fall time (external clock option)                          | Input     |      | 4ns   | ns   |

|     | Duty cycle                                                             |           | 40   | 60    | %    |

|     | Frequency                                                              |           |      | 33    | MHz  |

| U2  | RxEnb and TxEnb active delay                                           | Output    | 2 ns | 16 ns | ns   |

| U3  | UTPB, SOC, Rxclav and Txclav setup time                                | Input     | 4 ns |       | ns   |

| U4  | UTPB, SOC, Rxclav and Txclav hold time                                 | Input     | 1 ns |       | ns   |

| U5  | UTPB, SOC active delay (and PHREQ and PHSEL active delay in MPHY mode) | Output    | 2 ns | 16 ns | ns   |

#### Table 28. UTOPIA AC Electrical Specifications

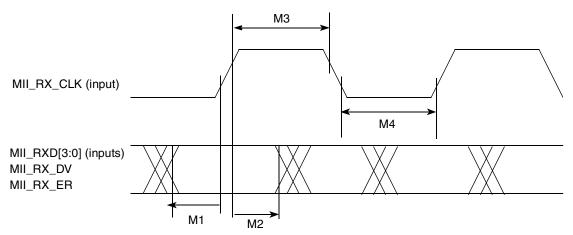

# 13.1 MII Receive Signal Timing (MII\_RXD[3:0], MII\_RX\_DV, MII\_RX\_ER, MII\_RX\_CLK)

The receiver functions correctly up to a MII\_RX\_CLK maximum frequency of 25MHz +1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_RX\_CLK frequency - 1%.

Table 29 provides information on the MII receive signal timing.

| Num | n Characteristic                                       |     | Мах | Unit              |

|-----|--------------------------------------------------------|-----|-----|-------------------|

| M1  | MII_RXD[3:0], MII_RX_DV, MII_RX_ER to MII_RX_CLK setup | 5   | _   | ns                |

| M2  | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold  | 5   | _   | ns                |

| М3  | MII_RX_CLK pulse width high                            | 35% | 65% | MII_RX_CLK period |

| M4  | MII_RX_CLK pulse width low                             | 35% | 65% | MII_RX_CLK period |

## Table 29. MII Receive Signal Timing

Figure 73 shows MII receive signal timing.

Figure 73. MII Receive Signal Timing Diagram

# 13.2 MII Transmit Signal Timing (MII\_TXD[3:0], MII\_TX\_EN, MII\_TX\_ER, MII\_TX\_CLK)

The transmitter functions correctly up to a MII\_TX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_TX\_CLK frequency - 1%.

Table 30 provides information on the MII transmit signal timing.

Table 30. MII Transmit Signal Timing

| Num | Characteristic                                           | Min | Мах | Unit |

|-----|----------------------------------------------------------|-----|-----|------|

| M5  | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER invalid | 5   | _   | ns   |

| M6  | MII_TX_CLK to MII_TXD[3:0], MII_TX_EN, MII_TX_ER valid   | _   | 25  |      |

| Device    | Number<br>of      | Ethernet    | Multi-Channel | ATM Support       | Cache Size  |          |

|-----------|-------------------|-------------|---------------|-------------------|-------------|----------|

| Device    | SCCs <sup>1</sup> | Support     | HDLC Support  |                   | Instruction | Data     |

| MPC857T   | One (SCC1)        | 10/100 Mbps | Yes           | Yes               | 4 Kbytes    | 4 Kbytes |

| MPC857DSL | One (SCC1)        | 10/100 Mbps | No            | Up to 4 addresses | 4 Kbytes    | 4 Kbytes |

Table 33. MPC862/857T/857DSL Derivatives (continued)

<sup>1</sup> Serial communications controller (SCC)

Table 34 identifies the packages and operating frequencies orderable for the MPC862/857T/857DSL derivative devices.

Temperature (Tj) Frequency (MHz) Package Type **Order Number** Plastic ball grid array 0°C to 105°C 50 XPC862PZP50B (ZP suffix) XPC862TZP50B XPC857TZP50B XPC857DSLZP50B 66 XPC862PZP66B XPC862TZP66B XPC857TZP66B XPC857DSLZP66B 80 XPC862PZP80B XPC862TZP80B XPC857TZP80B 100 XPC862PZP100B XPC862TZP100B XPC857TZP100B Plastic ball grid array -40°C to 115°C 66 <sup>1</sup> XPC862PCZP66B (CZP suffix) XPC857TCZP66B

Table 34. MPC862/857T/857DSL Package/Frequency Orderable

Additional extended temperature devices can be made available at 50MHz, 66MHz, and 80MHz

# 14.1 Pin Assignments

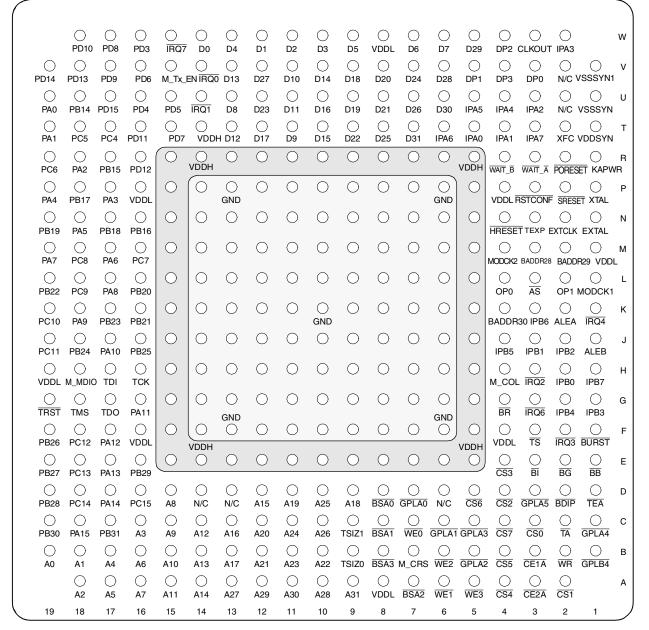

Figure 77 shows the top view pinout of the PBGA package. For additional information, see the *MPC862 PowerQUICC Family User s Manual*.

Figure 77. Pinout of the PBGA Package

| Name                                                      | Pin Number | Туре                      |  |  |  |  |  |

|-----------------------------------------------------------|------------|---------------------------|--|--|--|--|--|

| GPL_A5                                                    | D3         | Output                    |  |  |  |  |  |

| PORESET                                                   | R2         | Input                     |  |  |  |  |  |

| RSTCONF                                                   | P3         | Input                     |  |  |  |  |  |

| HRESET                                                    | N4         | Open-drain                |  |  |  |  |  |

| SRESET                                                    | P2         | Open-drain                |  |  |  |  |  |

| XTAL                                                      | P1         | Analog Output             |  |  |  |  |  |

| EXTAL                                                     | N1         | Analog Input (3.3 V only) |  |  |  |  |  |

| XFC                                                       | T2         | Analog Input              |  |  |  |  |  |

| CLKOUT                                                    | W3         | Output                    |  |  |  |  |  |

| EXTCLK                                                    | N2         | Input (3.3 V only)        |  |  |  |  |  |

| TEXP                                                      | N3         | Output                    |  |  |  |  |  |

| ALE_A<br>MII-TXD1                                         | К2         | Output                    |  |  |  |  |  |

| CE1_A<br>MII-TXD2                                         | B3         | Output                    |  |  |  |  |  |

| CE2_A<br>MII-TXD3                                         | АЗ         | Output                    |  |  |  |  |  |

| WAIT_A<br>SOC_Split <sup>2</sup>                          | R3         | Input                     |  |  |  |  |  |

| WAIT_B                                                    | R4         | Input                     |  |  |  |  |  |

| IP_A0<br>UTPB_Split0 <sup>2</sup><br>MII-RXD3             | Т5         | Input                     |  |  |  |  |  |

| IP_A1<br>UTPB_Split1 <sup>2</sup><br>MII-RXD2             | Τ4         | Input                     |  |  |  |  |  |

| IP_A2<br>IOIS16_A<br>UTPB_Split2 <sup>2</sup><br>MII-RXD1 | U3         | Input                     |  |  |  |  |  |

| IP_A3<br>UTPB_Split3 <sup>2</sup><br>MII-RXD0             | W2         | Input                     |  |  |  |  |  |

| IP_A4<br>UTPB_Split4 <sup>2</sup><br>MII-RXCLK            | U4         | Input                     |  |  |  |  |  |

| IP_A5<br>UTPB_Split5 <sup>2</sup><br>MII-RXERR            | U5         | Input                     |  |  |  |  |  |

# Table 35. Pin Assignments (continued)

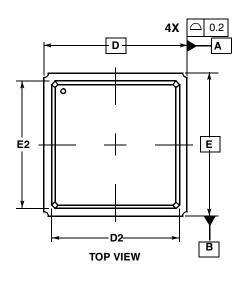

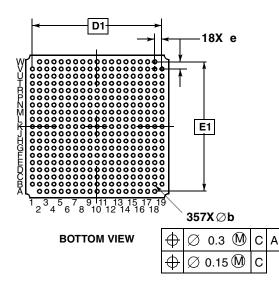

Mechanical Data and Ordering Information

#### SIDE VIEW

#### NOTES:

- 1. Dimensions and tolerancing per ASME Y14.5M, 1994.

- 2. Dimensions in millimeters.

- 3. Dimension b is the maximum solder ball diameter measured parallel to datum C.

|     | MILLIMETERS |       |  |

|-----|-------------|-------|--|

| DIM | MIN         | MAX   |  |

| Α   |             | 2.05  |  |

| A1  | 0.50        | 0.70  |  |

| A2  | 0.95        | 1.35  |  |

| A3  | 0.70        | 0.90  |  |

| b   | 0.60        | 0.90  |  |

| D   | 25.00 BSC   |       |  |

| D1  | 22.86 BSC   |       |  |

| D2  | 22.40       | 22.60 |  |

| е   | 1.27 BSC    |       |  |

| Е   | 25.00 BSC   |       |  |

| E1  | 22.86 BSC   |       |  |

| E2  | 22.40       | 22.60 |  |

Case No. 1103-01

В