#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Product Status                  | Active                                                     |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                     |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 80MHz                                                      |

| Co-Processors/DSP               | Communications; CPM                                        |

| RAM Controllers                 | DRAM                                                       |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | 10Mbps (4), 10/100Mbps (1)                                 |

| SATA                            | -                                                          |

| USB                             | -                                                          |

| Voltage - I/O                   | 3.3V                                                       |

| Operating Temperature           | -40°C ~ 115°C (TA)                                         |

| Security Features               | -                                                          |

| Package / Case                  | 357-BBGA                                                   |

| Supplier Device Package         | 357-PBGA (25x25)                                           |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc862tcvr80b |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

- System integration unit (SIU)

- Bus monitor

- Software watchdog

- Periodic interrupt timer (PIT)

- Low-power stop mode

- Clock synthesizer

- Decrementer, time base, and real-time clock (RTC) from the PowerPC architecture

- Reset controller

- IEEE 1149.1 test access port (JTAG)

- Interrupts

- Seven external interrupt request (IRQ) lines

- 12 port pins with interrupt capability

- The MPC862P and MPC862T have 23 internal interrupt sources; the MPC857T and MPC857DSL have 20 internal interrupt sources

- Programmable priority between SCCs (MPC862P and MPC862T)

- Programmable highest priority request

- Communications processor module (CPM)

- RISC controller

- Communication-specific commands (for example, GRACEFUL STOP TRANSMIT, ENTER HUNT MODE, and RESTART TRANSMIT)

- Supports continuous mode transmission and reception on all serial channels

- Up to 8-Kbytes of dual-port RAM

- The MPC862P and MPC862T have 16 serial DMA (SDMA) channels; the MPC857T and MPC857DSL have 10 serial DMA (SDMA) channels

- Three parallel I/O registers with open-drain capability

- Four baud rate generators

- Independent (can be connected to any SCC or SMC)

- Allow changes during operation

- Autobaud support option

- The MPC862P and MPC862T have four SCCs (serial communication controller) The MPC857T and MPC857DSL have one SCC, SCC1; the MPC857DSL supports ethernet only

- Serial ATM capability on all SCCs

- Optional UTOPIA port on SCC4

- Ethernet/IEEE 802.3 optional on SCC1–4, supporting full 10-Mbps operation

- HDLC/SDLC

- HDLC bus (implements an HDLC-based local area network (LAN))

- Asynchronous HDLC to support PPP (point-to-point protocol)

- AppleTalk

#### Features

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART

- Serial infrared (IrDA)

- Binary synchronous communication (BISYNC)

- Totally transparent (bit streams)

- Totally transparent (frame based with optional cyclic redundancy check (CRC))

- Two SMCs (serial management channels) (The MPC857DSL has one SMC, SMC1 for UART)

- UART

- Transparent

- General circuit interface (GCI) controller

- Can be connected to the time-division multiplexed (TDM) channels

- One serial peripheral interface (SPI)

- Supports master and slave modes

- Supports multiple-master operation on the same bus

- One inter-integrated circuit (I<sup>2</sup>C) port

- Supports master and slave modes

- Multiple-master environment support

- Time-slot assigner (TSA) (The MPC857DSL does not have the TSA)

- Allows SCCs and SMCs to run in multiplexed and/or non-multiplexed operation

- Supports T1, CEPT, PCM highway, ISDN basic rate, ISDN primary rate, user defined

- 1- or 8-bit resolution

- Allows independent transmit and receive routing, frame synchronization, clocking

- Allows dynamic changes

- On the MPC862P and MPC862T, can be internally connected to six serial channels (four SCCs and two SMCs); on the MPC857T, can be connected to three serial channels (one SCC and two SMCs)

- Parallel interface port (PIP)

- Centronics interface support

- Supports fast connection between compatible ports on MPC862/857T/857DSL or MC68360

- PCMCIA interface

- Master (socket) interface, release 2.1 compliant

- Supports one or two PCMCIA sockets dependent upon whether ESAR functionality is enabled

- 8 memory or I/O windows supported

- Low power support

- Full on—All units fully powered

- Doze—Core functional units disabled except time base decrementer, PLL, memory controller, RTC, and CPM in low-power standby

**Bus Signal Timing**

| Num  | Characteristic                                                                                                                                    | 33    | MHz   | 40 MHz |       | 50   | MHz   | 66   | MHz   | 11   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|--------|-------|------|-------|------|-------|------|

| Num  | Characteristic                                                                                                                                    | Min   | Max   | Min    | Max   | Min  | Max   | Min  | Мах   | Unit |

| B17a | a CLKOUT to $\overline{KR}$ , $\overline{RETRY}$ , $\overline{CR}$ valid<br>(hold time) (MIN = 0.00 x B1 + 2.00)                                  |       | _     | 2.00   | —     | 2.00 | —     | 2.00 | —     | ns   |

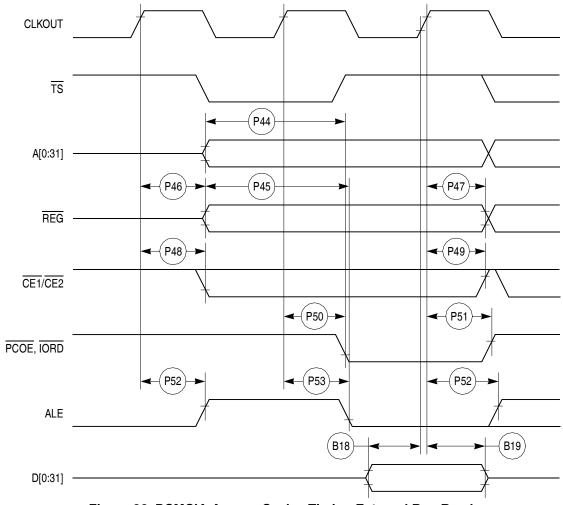

| B18  | D(0:31), DP(0:3) valid to CLKOUT<br>rising edge (setup time) <sup>8</sup> (MIN = 0.00<br>x B1 + 6.00)                                             | 6.00  | _     | 6.00   | —     | 6.00 | _     | 6.00 | —     | ns   |

| B19  | CLKOUT rising edge to D(0:31),<br>DP(0:3) valid (hold time) <sup>8</sup> (MIN = 0.00<br>x B1 + 1.00 <sup>9</sup> )                                | 1.00  | _     | 1.00   | —     | 1.00 | _     | 2.00 | —     | ns   |

| B20  | D(0:31), DP(0:3) valid to CLKOUT<br>falling edge (setup time) $^{10}$ (MIN = 0.00<br>x B1 + 4.00)                                                 | 4.00  | _     | 4.00   | _     | 4.00 | _     | 4.00 | _     | ns   |

| B21  | CLKOUT falling edge to D(0:31),<br>DP(0:3) valid (hold Time) <sup>10</sup> (MIN =<br>0.00 x B1 + 2.00)                                            | 2.00  | _     | 2.00   | —     | 2.00 | _     | 2.00 | —     | ns   |

| B22  | CLKOUT rising edge to $\overline{CS}$ asserted<br>GPCM ACS = 00 (MAX = 0.25 x B1 + 6.3)                                                           |       | 13.80 | 6.30   | 12.50 | 5.00 | 11.30 | 3.80 | 10.00 | ns   |

| B22a | CLKOUT falling edge to CS asserted<br>GPCM ACS = 10, TRLX = 0 (MAX =<br>0.00 x B1 + 8.00)                                                         | —     | 8.00  |        | 8.00  | —    | 8.00  |      | 8.00  | ns   |

| B22b | CLKOUT falling edge to <del>CS</del> asserted<br>GPCM ACS = 11, TRLX = 0, EBDF =<br>0 (MAX = 0.25 x B1 + 6.3)                                     | 7.60  | 13.80 | 6.30   | 12.50 | 5.00 | 11.30 | 3.80 | 10.00 | ns   |

| B22c | CLKOUT falling edge to <del>CS</del> asserted<br>GPCM ACS = 11, TRLX = 0, EBDF =<br>1 (MAX = 0.375 x B1 + 6.6)                                    | 10.90 | 18.00 | 10.90  | 18.00 | 7.00 | 14.30 | 5.20 | 12.30 | ns   |

| B23  | CLKOUT rising edge to $\overline{CS}$ negated<br>GPCM read access, GPCM write<br>access ACS = 00, TRLX = 0 & CSNT =<br>0 (MAX = 0.00 x B1 + 8.00) | 2.00  | 8.00  | 2.00   | 8.00  | 2.00 | 8.00  | 2.00 | 8.00  | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 10, TRLX = 0<br>(MIN = 0.25 x B1 - 2.00)                                       | 5.60  | —     | 4.30   | —     | 3.00 | —     | 1.80 | —     | ns   |

| B24a | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 11 TRLX = 0<br>(MIN = 0.50 x B1 - 2.00)                                        | 13.20 | _     | 10.50  | _     | 8.00 | _     | 5.60 | _     | ns   |

| B25  | CLKOUT rising edge to $\overline{OE}$ , $\overline{WE}(0:3)$<br>asserted (MAX = 0.00 x B1 + 9.00)                                                 | —     | 9.00  |        | 9.00  |      | 9.00  |      | 9.00  | ns   |

| B26  | CLKOUT rising edge to $\overline{OE}$ negated<br>(MAX = 0.00 x B1 + 9.00)                                                                         | 2.00  | 9.00  | 2.00   | 9.00  | 2.00 | 9.00  | 2.00 | 9.00  | ns   |

## Table 7. Bus Operation Timings (continued)

**Bus Signal Timing**

| N    | Characteristic                                                                                                                                                          | 33    | MHz   | 40 I  | MHz   | 50 I  | MHz   | 66 MHz |       | 11   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                                                          | Min   | Max   | Min   | Max   | Min   | Max   | Min    | Max   | Unit |

| B32c | 2c CLKOUT rising edge to $\overline{BS}$ valid - as<br>requested by control bit BST3 in the<br>corresponding word in the UPM<br>(MAX = 0.25 x B1 + 6.80)                |       | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80   | 10.50 | ns   |

| B32d | CLKOUT falling edge to $\overline{\text{BS}}$ valid- as<br>requested by control bit BST1 in the<br>corresponding word in the UPM,<br>EBDF = 1 (MAX = 0.375 x B1 + 6.60) |       | 18.00 | 7.60  | 16.00 | 13.30 | 14.10 | 11.30  | 12.30 | ns   |

| B33  | CLKOUT falling edge to $\overline{\text{GPL}}$ valid - as<br>requested by control bit GxT4 in the<br>corresponding word in the UPM<br>(MAX = 0.00 x B1 + 6.00)          |       | 6.00  | 1.50  | 6.00  | 1.50  | 6.00  | 1.50   | 6.00  | ns   |

| B33a | CLKOUT rising edge to $\overline{\text{GPL}}$ Valid - as<br>requested by control bit GxT3 in the<br>corresponding word in the UPM<br>(MAX = 0.25 x B1 + 6.80)           |       | 14.30 | 6.30  | 13.00 | 5.00  | 11.80 | 3.80   | 10.50 | ns   |

| B34  | A(0:31), BADDR(28:30), and D(0:31)<br>to $\overline{CS}$ valid - as requested by control bit<br>CST4 in the corresponding word in the<br>UPM (MIN = 0.25 x B1 - 2.00)   | 5.60  | _     | 4.30  | _     | 3.00  | _     | 1.80   | _     | ns   |

| B34a | A(0:31), BADDR(28:30), and D(0:31)<br>to $\overline{CS}$ valid - as requested by control bit<br>CST1 in the corresponding word in the<br>UPM (MIN = 0.50 x B1 - 2.00)   | 13.20 | _     | 10.50 | _     | 8.00  | _     | 5.60   | _     | ns   |

| B34b | A(0:31), BADDR(28:30), and D(0:31)<br>to $\overline{CS}$ valid - as requested by CST2 in<br>the corresponding word in UPM<br>(MIN = 0.75 x B1 - 2.00)                   | 20.70 | _     | 16.70 | _     | 13.00 | _     | 9.40   | _     | ns   |

| B35  | A(0:31), BADDR(28:30) to $\overline{CS}$ valid -<br>as requested by control bit BST4 in the<br>corresponding word in the UPM<br>(MIN = 0.25 x B1 - 2.00)                | 5.60  | _     | 4.30  | _     | 3.00  | _     | 1.80   | _     | ns   |

| B35a | A(0:31), BADDR(28:30), and D(0:31)<br>to $\overline{BS}$ valid - As Requested by BST1 in<br>the corresponding word in the UPM<br>(MIN = 0.50 x B1 - 2.00)               | 13.20 | _     | 10.50 | _     | 8.00  | _     | 5.60   | _     | ns   |

| B35b | A(0:31), BADDR(28:30), and D(0:31)<br>to BS valid - as requested by control bit<br>BST2 in the corresponding word in the<br>UPM (MIN = $0.75 \times B1 - 2.00$ )        | 20.70 | _     | 16.70 | _     | 13.00 | _     | 9.40   | _     | ns   |

| B36  | A(0:31), BADDR(28:30), and D(0:31)<br>to $\overline{GPL}$ valid as requested by control<br>bit GxT4 in the corresponding word in<br>the UPM (MIN = 0.25 x B1 - 2.00)    | 5.60  | _     | 4.30  | _     | 3.00  | _     | 1.80   | _     | ns   |

## Table 7. Bus Operation Timings (continued)

**Bus Signal Timing**

Figure 26 provides the PCMCIA access cycle timing for the external bus read.

Figure 26. PCMCIA Access Cycles Timing External Bus Read

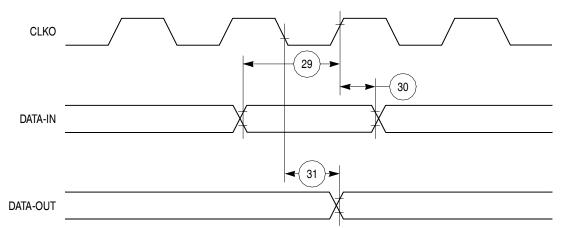

Figure 44. Parallel I/O Data-In/Data-Out Timing Diagram

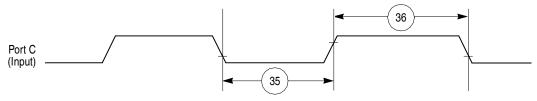

## **11.2 Port C Interrupt AC Electrical Specifications**

Table 15 provides the timings for port C interrupts.

### Table 15. Port C Interrupt Timing

| Num | Characteristic                                         | 33.34 | Unit |      |

|-----|--------------------------------------------------------|-------|------|------|

|     | Characteristic                                         | Min   | Max  | Onit |

| 35  | Port C interrupt pulse width low (edge-triggered mode) | 55    | _    | ns   |

| 36  | Port C interrupt minimum time between active edges     | 55    | _    | ns   |

Figure 45 shows the port C interrupt detection timing.

Figure 45. Port C Interrupt Detection Timing

## **11.3 IDMA Controller AC Electrical Specifications**

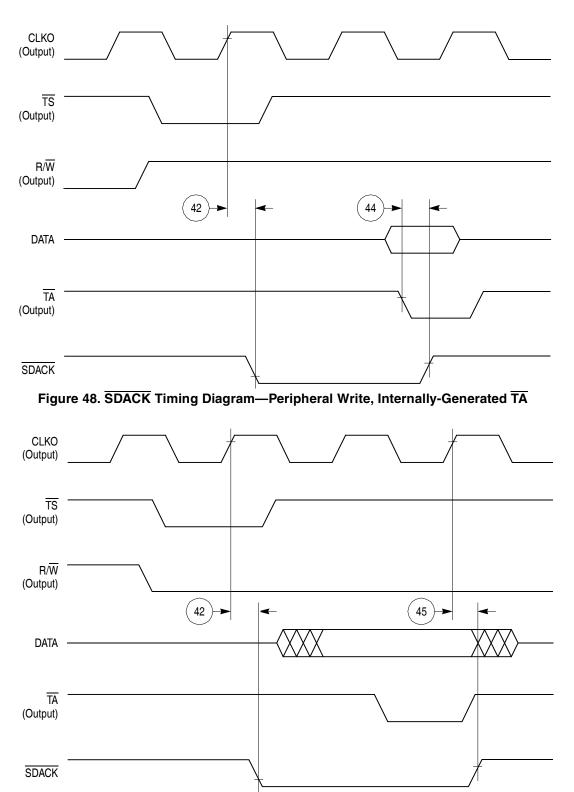

Table 16 provides the IDMA controller timings as shown in Figure 46 though Figure 49.

### Table 16. IDMA Controller Timing

| Num | Characteristic                        | All Freq | Unit |      |

|-----|---------------------------------------|----------|------|------|

|     |                                       |          | Max  | onne |

| 40  | DREQ setup time to clock high         | 7        | _    | ns   |

| 41  | DREQ hold time from clock high        | 3        | _    | ns   |

| 42  | SDACK assertion delay from clock high | _        | 12   | ns   |

Figure 49. SDACK Timing Diagram—Peripheral Read, Internally-Generated TA

| Num | Characteristic                                                      | All Freq | Unit  |            |

|-----|---------------------------------------------------------------------|----------|-------|------------|

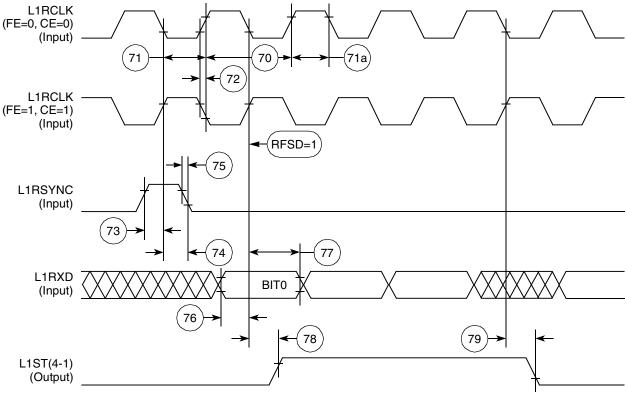

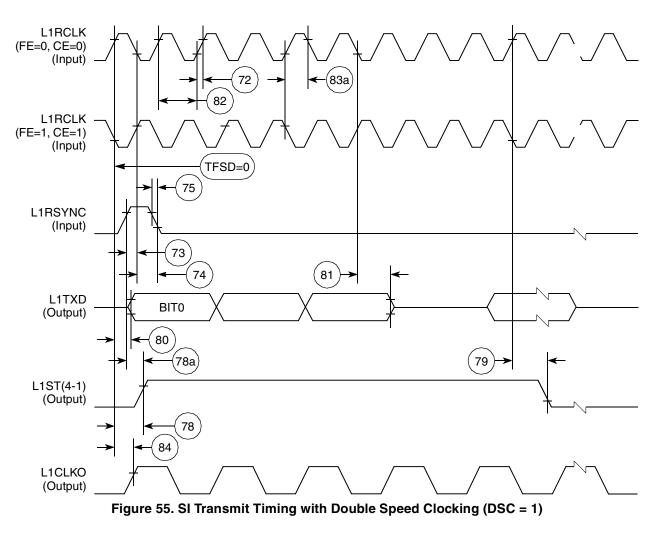

|     | Characteristic                                                      | Min      | Max   |            |

| 83a | L1RCLK, L1TCLK width high $(DSC = 1)^3$                             | P + 10   | _     | ns         |

| 84  | L1CLK edge to L1CLKO valid (DSC = 1)                                | _        | 30.00 | ns         |

| 85  | L1RQ valid before falling edge of L1TSYNC <sup>4</sup>              | 1.00     | _     | L1TCL<br>K |

| 86  | L1GR setup time <sup>2</sup>                                        | 42.00    | _     | ns         |

| 87  | L1GR hold time                                                      | 42.00    | _     | ns         |

| 88  | L1CLK edge to L1SYNC valid (FSD = 00) CNT = 0000, BYT = 0, DSC = 0) | _        | 0.00  | ns         |

#### Table 19. SI Timing (continued)

<sup>1</sup> The ratio SyncCLK/L1RCLK must be greater than 2.5/1.

<sup>2</sup> These specs are valid for IDL mode only.

<sup>3</sup> Where P = 1/CLKOUT. Thus for a 25-MHz CLKO1 rate, P = 40 ns.

<sup>4</sup> These strobes and TxD on the first bit of the frame become valid after L1CLK edge or L1SYNC, whichever is later.

Figure 52. SI Receive Timing Diagram with Normal Clocking (DSC = 0)

## 11.7 SCC in NMSI Mode Electrical Specifications

Table 20 provides the NMSI external clock timing.

### Table 20. NMSI External Clock Timing

| Num   | Characteristic                                       | All Freq     | uencies | Unit |

|-------|------------------------------------------------------|--------------|---------|------|

| Nulli | Characteristic                                       | Min          | Мах     | onn  |

| 100   | RCLK1 and TCLK1 width high <sup>1</sup>              | 1/SYNCCLK    | _       | ns   |

| 101   | RCLK1 and TCLK1 width low                            | 1/SYNCCLK +5 | _       | ns   |

| 102   | RCLK1 and TCLK1 rise/fall time                       | —            | 15.00   | ns   |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00         | 50.00   | ns   |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00         | 50.00   | ns   |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 5.00         | _       | ns   |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 5.00         | _       | ns   |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 5.00         | _       | ns   |

| 108   | CD1 setup Time to RCLK1 rising edge                  | 5.00         | _       | ns   |

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater than or equal to 2.25/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signal.

Table 21 provides the NMSI internal clock timing.

Table 21. NMSI Internal Clock Timing

| Num   | Characteristic                                       | All Freq | Unit      |      |

|-------|------------------------------------------------------|----------|-----------|------|

| Nulli |                                                      | Min      | Мах       | Omit |

| 100   | RCLK1 and TCLK1 frequency <sup>1</sup>               | 0.00     | SYNCCLK/3 | MHz  |

| 102   | RCLK1 and TCLK1 rise/fall time                       | —        | —         | ns   |

| 103   | TXD1 active delay (from TCLK1 falling edge)          | 0.00     | 30.00     | ns   |

| 104   | RTS1 active/inactive delay (from TCLK1 falling edge) | 0.00     | 30.00     | ns   |

| 105   | CTS1 setup time to TCLK1 rising edge                 | 40.00    | —         | ns   |

| 106   | RXD1 setup time to RCLK1 rising edge                 | 40.00    | —         | ns   |

| 107   | RXD1 hold time from RCLK1 rising edge <sup>2</sup>   | 0.00     | —         | ns   |

| 108   | CD1 setup time to RCLK1 rising edge                  | 40.00    | —         | ns   |

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signals.

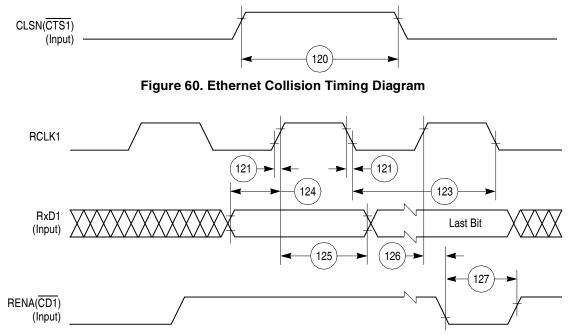

| Num | Characteristic                                 |     | All Frequencies |      |  |

|-----|------------------------------------------------|-----|-----------------|------|--|

| num | Characteristic                                 | Min | Мах             | Unit |  |

| 134 | TENA inactive delay (from TCLK1 rising edge)   | 10  | 50              | ns   |  |

| 135 | RSTRT active delay (from TCLK1 falling edge)   | 10  | 50              | ns   |  |

| 136 | RSTRT inactive delay (from TCLK1 falling edge) | 10  | 50              | ns   |  |

| 137 | REJECT width low                               | 1   | —               | CLK  |  |

| 138 | CLKO1 low to SDACK asserted <sup>2</sup>       | —   | 20              | ns   |  |

| 139 | CLKO1 low to SDACK negated <sup>2</sup>        |     | 20              | ns   |  |

#### Table 22. Ethernet Timing (continued)

<sup>1</sup> The ratios SyncCLK/RCLK1 and SyncCLK/TCLK1 must be greater or equal to 2/1.

<sup>2</sup> SDACK is asserted whenever the SDMA writes the incoming frame DA into memory.

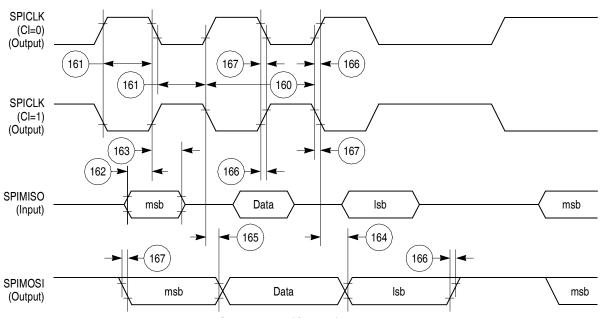

Figure 67. SPI Master (CP = 1) Timing Diagram

## **11.11 SPI Slave AC Electrical Specifications**

Table 25 provides the SPI slave timings as shown in Figure 68 though Figure 69.

### Table 25. SPI Slave Timing

| Num   | Characteristic                                              | All Freq | uencies | Unit             |

|-------|-------------------------------------------------------------|----------|---------|------------------|

| Nulli | Characteristic                                              | Min      | Мах     |                  |

| 170   | Slave cycle time                                            | 2        |         | t <sub>cyc</sub> |

| 171   | Slave enable lead time                                      |          | —       | ns               |

| 172   | Slave enable lag time                                       | 15       | —       | ns               |

| 173   | Slave clock (SPICLK) high or low time                       | 1        | —       | t <sub>cyc</sub> |

| 174   | Slave sequential transfer delay (does not require deselect) | 1        | —       | t <sub>cyc</sub> |

| 175   | Slave data setup time (inputs)                              | 20       | —       | ns               |

| 176   | Slave data hold time (inputs)                               | 20       | —       | ns               |

| 177   | Slave access time                                           | —        | 50      | ns               |

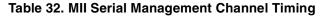

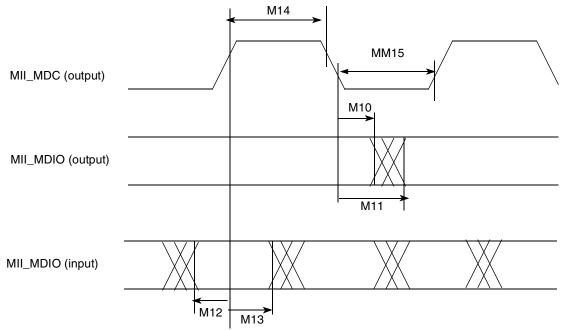

| Num | Characteristic                                                              | Min | Max | Unit           |

|-----|-----------------------------------------------------------------------------|-----|-----|----------------|

| M10 | MII_MDC falling edge to MII_MDIO output invalid (minimum propagation delay) | 0   | _   | ns             |

| M11 | MII_MDC falling edge to MII_MDIO output valid (max prop delay)              | _   | 25  | ns             |

| M12 | MII_MDIO (input) to MII_MDC rising edge setup                               | 10  | —   | ns             |

| M13 | MII_MDIO (input) to MII_MDC rising edge hold                                | 0   | —   | ns             |

| M14 | MII_MDC pulse width high                                                    | 40% | 60% | MII_MDC period |

| M15 | MII_MDC pulse width low                                                     | 40% | 60% | MII_MDC period |

Figure 76 shows the MII serial management channel timing diagram.

Figure 76. MII Serial Management Channel Timing Diagram

# 14 Mechanical Data and Ordering Information

Table 33 provides information on the MPC862/857T/857DSL derivative devices.

### Table 33. MPC862/857T/857DSL Derivatives

| Device  | Number<br>of      | Ethernet    | Multi-Channel | ATM Support | Cache       | e Size   |

|---------|-------------------|-------------|---------------|-------------|-------------|----------|

|         | SCCs <sup>1</sup> | Support     | HDLC Support  |             | Instruction | Data     |

| MPC862T | Four              | 10/100 Mbps | Yes           | Yes         | 4 Kbytes    | 4 Kbytes |

| MPC862P | Four              | 10/100 Mbps | Yes           | Yes         | 16 Kbytes   | 8 Kbytes |

| Device    | Number<br>of      | Ethernet    | Multi-Channel | ATM Support       | Cache Size  |          |

|-----------|-------------------|-------------|---------------|-------------------|-------------|----------|

| Device    | SCCs <sup>1</sup> | Support     | HDLC Support  |                   | Instruction | Data     |

| MPC857T   | One (SCC1)        | 10/100 Mbps | Yes           | Yes               | 4 Kbytes    | 4 Kbytes |

| MPC857DSL | One (SCC1)        | 10/100 Mbps | No            | Up to 4 addresses | 4 Kbytes    | 4 Kbytes |

Table 33. MPC862/857T/857DSL Derivatives (continued)

<sup>1</sup> Serial communications controller (SCC)

Table 34 identifies the packages and operating frequencies orderable for the MPC862/857T/857DSL derivative devices.

Temperature (Tj) Frequency (MHz) Package Type **Order Number** Plastic ball grid array 0°C to 105°C 50 XPC862PZP50B (ZP suffix) XPC862TZP50B XPC857TZP50B XPC857DSLZP50B 66 XPC862PZP66B XPC862TZP66B XPC857TZP66B XPC857DSLZP66B 80 XPC862PZP80B XPC862TZP80B XPC857TZP80B 100 XPC862PZP100B XPC862TZP100B XPC857TZP100B Plastic ball grid array -40°C to 115°C 66 <sup>1</sup> XPC862PCZP66B (CZP suffix) XPC857TCZP66B

Table 34. MPC862/857T/857DSL Package/Frequency Orderable

Additional extended temperature devices can be made available at 50MHz, 66MHz, and 80MHz

## 14.1 Pin Assignments

Figure 77 shows the top view pinout of the PBGA package. For additional information, see the *MPC862 PowerQUICC Family User s Manual*.

| Name                                | Pin Number             | Туре                            |

|-------------------------------------|------------------------|---------------------------------|

| BR                                  | G4                     | Bidirectional                   |

| BG                                  | E2                     | Bidirectional                   |

| BB                                  | E1                     | Bidirectional<br>Active Pull-up |

| FRZ<br>IRQ6                         | G3                     | Bidirectional                   |

| IRQ0                                | V14                    | Input                           |

| IRQ1                                | U14                    | Input                           |

| M_TX_CLK<br>IRQ7                    | W15                    | Input                           |

| <u>CS</u> [0:5]                     | C3, A2, D4, E4, A4, B4 | Output                          |

| CS6<br>CE1_B                        | D5                     | Output                          |

| CS7<br>CE2_B                        | C4                     | Output                          |

| WE0<br>BS_B0<br>IORD                | C7                     | Output                          |

| WE1<br>BS_B1<br>IOWR                | A6                     | Output                          |

| WE2<br>BS_B2<br>PCOE                | B6                     | Output                          |

| WE3<br>BS_B3<br>PCWE                | A5                     | Output                          |

| BS_A[0:3]                           | D8, C8, A7, B8         | Output                          |

| GPL_A0<br>GPL_B0                    | D7                     | Output                          |

| OE<br>GPL_A1<br>GPL_B1              | C6                     | Output                          |

| GPL_A[2:3]<br>GPL_B[2:3]<br>CS[2–3] | B5, C5                 | Output                          |

| UPWAITA<br>GPL_A4                   | C1                     | Bidirectional                   |

| UPWAITB<br>GPL_B4                   | B1                     | Bidirectional                   |

| Name                                    | Pin Number | Туре                                    |

|-----------------------------------------|------------|-----------------------------------------|

| PA15<br>RXD1<br>RXD4                    | C18        | Bidirectional                           |

| PA14<br>TXD1<br>TXD4                    | D17        | Bidirectional<br>(Optional: Open-drain) |

| PA13<br>RXD2                            | E17        | Bidirectional                           |

| PA12<br>TXD2                            | F17        | Bidirectional<br>(Optional: Open-drain) |

| PA11<br>L1TXDB<br>RXD3                  | G16        | Bidirectional<br>(Optional: Open-drain) |

| PA10<br>L1RXDB<br>TXD3                  | J17        | Bidirectional<br>(Optional: Open-drain) |

| PA9<br>L1TXDA                           | К18        | Bidirectional<br>(Optional: Open-drain) |

| RXD4                                    |            |                                         |

| PA8<br>L1RXDA<br>TXD4                   | L17        | Bidirectional<br>(Optional: Open-drain) |

| PA7<br>CLK1<br>L1RCLKA<br>BRGO1<br>TIN1 | M19        | Bidirectional                           |

| PA6<br>CLK2<br>TOUT1                    | M17        | Bidirectional                           |

| PA5<br>CLK3<br>L1TCLKA<br>BRGO2<br>TIN2 | N18        | Bidirectional                           |

| PA4<br>CLK4<br>TOUT2                    | P19        | Bidirectional                           |

| PA3<br>CLK5<br>BRGO3<br>TIN3            | P17        | Bidirectional                           |

| Name                                  | Pin Number | Туре          |

|---------------------------------------|------------|---------------|

| PC13<br>L1RQb<br>L1ST3<br>RTS3        | E18        | Bidirectional |

| PC12<br>L1RQa<br>L1ST4<br>RTS4        | F18        | Bidirectional |

| PC11<br>CTS1                          | J19        | Bidirectional |

| PC10<br>CD1<br>TGATE1                 | K19        | Bidirectional |

| PC9<br>CTS2                           | L18        | Bidirectional |

| PC8<br>CD2<br>TGATE2                  | M18        | Bidirectional |

| PC7<br>CTS3<br>L1TSYNCB<br>SDACK2     | M16        | Bidirectional |

| PC6<br>CD3<br>L1RSYNCB                | R19        | Bidirectional |

| PC5<br>CTS4<br>L1TSYNCA<br>SDACK1     | T18        | Bidirectional |

| PC4<br>CD4<br>L1RSYNCA                | T17        | Bidirectional |

| PD15<br>L1TSYNCA<br>MII-RXD3<br>UTPB0 | U17        | Bidirectional |

| PD14<br>L1RSYNCA<br>MII-RXD2<br>UTPB1 | V19        | Bidirectional |

| PD13<br>L1TSYNCB<br>MII-RXD1<br>UTPB2 | V18        | Bidirectional |

| Table 35. Pin Assignments | (continued) |

|---------------------------|-------------|

|---------------------------|-------------|

| Name                                 | Pin Number | Туре          |

|--------------------------------------|------------|---------------|

| PD12<br>L1RSYNCB<br>MII-MDC<br>UTPB3 | R16        | Bidirectional |

| PD11<br>RXD3<br>MII-TXERR<br>RXENB   | T16        | Bidirectional |

| PD10<br>TXD3<br>MII-RXD0<br>TXENB    | W18        | Bidirectional |

| PD9<br>RXD4<br>MII-TXD0<br>UTPCLK    | V17        | Bidirectional |

| PD8<br>TXD4<br>MII-MDC<br>MII-RXCLK  | W17        | Bidirectional |

| PD7<br>RTS3<br>MII-RXERR<br>UTPB4    | T15        | Bidirectional |

| PD6<br>RTS4<br>MII-RXDV<br>UTPB5     | V16        | Bidirectional |

| PD5<br>REJECT2<br>MII-TXD3<br>UTPB6  | U15        | Bidirectional |

| PD4<br>REJECT3<br>MII-TXD2<br>UTPB7  | U16        | Bidirectional |

| PD3<br>REJECT4<br>MII-TXD1<br>SOC    | W16        | Bidirectional |

| TMS                                  | G18        | Input         |

| TDI<br>DSDI                          | H17        | Input         |

| TCK<br>DSCK                          | H16        | Input         |

| Name        | Pin Number                                                                                                                                                                                                                                                                                                                                                                      | Туре          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| TRST        | G19                                                                                                                                                                                                                                                                                                                                                                             | Input         |

| TDO<br>DSDO | G17                                                                                                                                                                                                                                                                                                                                                                             | Output        |

| M_CRS       | B7                                                                                                                                                                                                                                                                                                                                                                              | Input         |

| M_MDIO      | H18                                                                                                                                                                                                                                                                                                                                                                             | Bidirectional |

| M_TXEN      | V15                                                                                                                                                                                                                                                                                                                                                                             | Output        |

| M_COL       | H4                                                                                                                                                                                                                                                                                                                                                                              | Input         |

| KAPWR       | R1                                                                                                                                                                                                                                                                                                                                                                              | Power         |

| GND         | F6, F7, F8, F9, F10, F11, F12, F13, F14, G6, G7, G8, G9, G10, G11, G12, G13, G14, H6, H7, H8, H9, H10, H11, H12, H13, H14, J6, J7, J8, J9, J10, J11, J12, J13, J14, K6, K7, K8, K9, K10, K11, K12, K13, K14, L6, L7, L8, L9, L10, L11, L12, L13, L14, M6, M7, M8, M9, M10, M11, M12, M13, M14, N6, N7, N8, N9, N10, N11, N12, N13, N14, P6, P7, P8, P9, P10, P11, P12, P13, P14 | Power         |

| VDDL        | A8, M1, W8, H19, F4, F16, P4, P16                                                                                                                                                                                                                                                                                                                                               | Power         |

| VDDH        | E5, E6, E7, E8, E9, E10, E11, E12, E13, E14, E15, F5, F15, G5,<br>G15, H5, H15, J5, J15, K5, K15, L5, L15, M5, M15, N5, N15, P5,<br>P15, R5, R6, R7, R8, R9, R10, R11, R12, R13, R14, R15, T14                                                                                                                                                                                  | Power         |

| N/C         | D6, D13, D14, U2, V2                                                                                                                                                                                                                                                                                                                                                            | No-connect    |

<sup>1</sup> Classic SAR mode only

<sup>2</sup> ESAR mode only

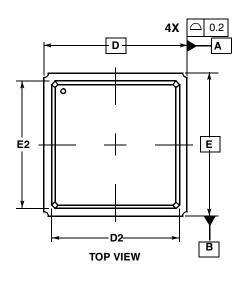

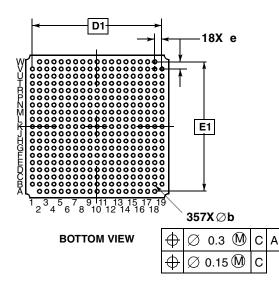

## 14.2 Mechanical Dimensions of the PBGA Package

For more information on the printed circuit board layout of the PBGA package, including thermal via design and suggested pad layout, please refer to *Plastic Ball Grid Array Application Note* (order number: AN1231/D) available from your local Freescale sales office. Figure 78 shows the mechanical dimensions of the PBGA package.

Mechanical Data and Ordering Information

#### SIDE VIEW

#### NOTES:

- 1. Dimensions and tolerancing per ASME Y14.5M, 1994.

- 2. Dimensions in millimeters.

- 3. Dimension b is the maximum solder ball diameter measured parallel to datum C.

|     | MILLIMETERS |       |

|-----|-------------|-------|

| DIM | MIN         | MAX   |

| Α   |             | 2.05  |

| A1  | 0.50        | 0.70  |

| A2  | 0.95        | 1.35  |

| A3  | 0.70        | 0.90  |

| b   | 0.60        | 0.90  |

| D   | 25.00 BSC   |       |

| D1  | 22.86 BSC   |       |

| D2  | 22.40       | 22.60 |

| е   | 1.27 BSC    |       |

| Е   | 25.00 BSC   |       |

| E1  | 22.86 BSC   |       |

| E2  | 22.40       | 22.60 |

Case No. 1103-01

В