Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                       |

|---------------------------------|-----------------------------------------------------------------------|

| Product Status                  | Obsolete                                                              |

| Core Processor                  | MPC8xx                                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 50MHz                                                                 |

| Co-Processors/DSP               | Communications; CPM                                                   |

| RAM Controllers                 | DRAM                                                                  |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10Mbps (4), 10/100Mbps (1)                                            |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 3.3V                                                                  |

| Operating Temperature           | -40°C ~ 115°C (TA)                                                    |

| Security Features               | -                                                                     |

| Package / Case                  | 357-BBGA                                                              |

| Supplier Device Package         | 357-PBGA (25x25)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc862tczq50b |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Overview

The MPC862/857T/857DSL is a derivative of Freescale's MPC860 PowerQUICC<sup>™</sup> family of devices. It is a versatile single-chip integrated microprocessor and peripheral combination that can be used in a variety of controller applications and communications and networking systems. The MPC862/857T/857DSL provides enhanced ATM functionality over that of other ATM-enabled members of the MPC860 family.

Table 1 shows the functionality supported by the members of the MPC862/857T/857DSL family.

Cache **Ethernet Part** SCC SMC Instruction **Data Cache** 10/100 10T Cache MPC862P 16 Kbyte 8 Kbyte Up to 4 1 2 MPC862T 4 Kbyte 4 Kbyte Up to 4 2 MPC857T 4 Kbyte 4 Kbyte 1 1 1 2 1<sup>2</sup> 11 MPC857DSL 4 Kbyte 1 4 Kbyte

**Table 1. MPC862 Family Functionality**

## 2 Features

The following list summarizes the key MPC862/857T/857DSL features:

- Embedded single-issue, 32-bit MPC8xx core (implementing the PowerPC architecture) with thirty-two 32-bit general-purpose registers (GPRs)

- The core performs branch prediction with conditional prefetch, without conditional execution

- 4- or 8-Kbyte data cache and 4- or 16-Kbyte instruction cache (see Table 1).

- 16-Kbyte instruction cache (MPC862P) is four-way, set-associative with 256 sets; 4-Kbyte instruction cache (MPC862T, MPC857T, and MPC857DSL) is two-way, set-associative with 128 sets.

- 8-Kbyte data cache (MPC862P) is two-way, set-associative with 256 sets; 4-Kbyte data cache (MPC862T, MPC857T, and MPC857DSL) is two-way, set-associative with 128 sets.

- Cache coherency for both instruction and data caches is maintained on 128-bit (4-word) cache blocks.

- Caches are physically addressed, implement a least recently used (LRU) replacement algorithm, and are lockable on a cache block basis.

- MMUs with 32-entry TLB, fully associative instruction and data TLBs

- MMUs support multiple page sizes of 4, 16, and 512 Kbytes, and 8 Mbytes; 16 virtual address spaces and 16 protection groups

- Advanced on-chip-emulation debug mode

On the MPC857DSL, the SCC (SCC1) is for ethernet only. Also, the MPC857DSL does not support the Time Slot Assigner (TSA).

<sup>&</sup>lt;sup>2</sup> On the MPC857DSL, the SMC (SMC1) is for UART only.

- The MPC862/857T/857DSL provides enhanced ATM functionality over that of the MPC860SAR.

The MPC862/857T/857DSL adds major new features available in "enhanced SAR" (ESAR) mode, including the following:

- Improved operation, administration and maintenance (OAM) support

- OAM performance monitoring (PM) support

- Multiple APC priority levels available to support a range of traffic pace requirements

- ATM port-to-port switching capability without the need for RAM-based microcode

- Simultaneous MII (10/100Base-T) and UTOPIA (half-duplex) capability

- Optional statistical cell counters per PHY

- UTOPIA level 2 compliant interface with added FIFO buffering to reduce the total cell transmission time. (The earlier UTOPIA level 1 specification is also supported.)

- Multi-PHY support on the MPC857T

- Four PHY support on the MPC857DSL

- Parameter RAM for both SPI and I<sup>2</sup>C can be relocated without RAM-based microcode

- Supports full-duplex UTOPIA both master (ATM side) and slave (PHY side) operation using a "split" bus

- AAL2/VBR functionality is ROM-resident

- Up to 32-bit data bus (dynamic bus sizing for 8, 16, and 32 bits)

- 32 address lines

- Memory controller (eight banks)

- Contains complete dynamic RAM (DRAM) controller

- Each bank can be a chip select or  $\overline{RAS}$  to support a DRAM bank

- Up to 30 wait states programmable per memory bank

- Glueless interface to Page mode/EDO/SDRAM, SRAM, EPROMs, flash EPROMs, and other memory devices.

- DRAM controller programmable to support most size and speed memory interfaces

- Four  $\overline{CAS}$  lines, four  $\overline{WE}$  lines, one  $\overline{OE}$  line

- Boot chip-select available at reset (options for 8-, 16-, or 32-bit memory)

- Variable block sizes (32 Kbyte–256 Mbyte)

- Selectable write protection

- On-chip bus arbitration logic

- General-purpose timers

- Four 16-bit timers cascadable to be two 32-bit timers

- Gate mode can enable/disable counting

- Interrupt can be masked on reference match and event capture

- Fast Ethernet controller (FEC)

- Simultaneous MII (10/100Base-T) and UTOPIA operation when using the UTOPIA multiplexed bus.

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

| Table 4.  | Power  | Dissi | nation | (P <sub>D</sub> ) | (continued)    |

|-----------|--------|-------|--------|-------------------|----------------|

| I abic T. | I OWCI | Dissi | pation | (1 D              | (COIILIII aca) |

| Die Revision      | Frequency | Typical <sup>1</sup> | Maximum <sup>2</sup> | Unit |

|-------------------|-----------|----------------------|----------------------|------|

| A.1, B.0          | 66 MHz    | 910                  | 1060                 | mW   |

| (2:1 Mode)        | 80 MHz    | 1.06                 | 1.20                 | W    |

| B.0<br>(2:1 Mode) | 100 MHz   | 1.35                 | 1.54                 | W    |

Typical power dissipation is measured at 3.3 V.

#### NOTE

Values in Table 4 represent VDDL based power dissipation and do not include I/O power dissipation over VDDH. I/O power dissipation varies widely by application due to buffer current, depending on external circuitry.

# 6 DC Characteristics

Table 5 provides the DC electrical characteristics for the MPC862/857T/857DSL.

**Table 5. DC Electrical Specifications**

| Characteristic                                                                           | Symbol                                     | Min        | Max     | Unit |

|------------------------------------------------------------------------------------------|--------------------------------------------|------------|---------|------|

| Operating voltage                                                                        | VDDH, VDDL,<br>KAPWR,<br>VDDSYN            | 3.135      | 3.465   | V    |

|                                                                                          | KAPWR<br>(power-down<br>mode)              | 2.0        | 3.6     | V    |

|                                                                                          | KAPWR<br>(all other<br>operating<br>modes) | VDDH – 0.4 | VDDH    | V    |

| Input High Voltage (all inputs except EXTAL and EXTCLK)                                  | VIH                                        | 2.0        | 5.5     | V    |

| Input Low Voltage <sup>1</sup>                                                           | VIL                                        | GND        | 0.8     | V    |

| EXTAL, EXTCLK Input High Voltage                                                         | VIHC                                       | 0.7*(VCC)  | VCC+0.3 | V    |

| Input Leakage Current, Vin = 5.5 V (Except TMS, TRST, DSCK and DSDI pins)                | I <sub>in</sub>                            | _          | 100     | μA   |

| Input Leakage Current, Vin = 3.6 V (Except TMS, TRST, DSCK, and DSDI)                    | I <sub>In</sub>                            | _          | 10      | μA   |

| Input Leakage Current, Vin = 0 V (Except TMS, TRST, DSCK, and DSDI pins)                 | I <sub>In</sub>                            | _          | 10      | μΑ   |

| Input Capacitance <sup>2</sup>                                                           | C <sub>in</sub>                            | _          | 20      | pF   |

| Output High Voltage, IOH = -2.0 mA, VDDH = 3.0 V (Except XTAL, XFC, and Open drain pins) | VOH                                        | 2.4        | _       | V    |

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

<sup>&</sup>lt;sup>2</sup> Maximum power dissipation is measured at 3.5 V.

### 7.2 Estimation with Junction-to-Case Thermal Resistance

Historically, the thermal resistance has frequently been expressed as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$$

where:

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$R_{\theta IC}$  = junction-to-case thermal resistance (°C/W)

$R_{\theta CA}$  = case-to-ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user adjusts the thermal environment to affect the case-to-ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the air flow around the device, add a heat sink, change the mounting arrangement on the printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device. This thermal model is most useful for ceramic packages with heat sinks where some 90% of the heat flows through the case and the heat sink to the ambient environment. For most packages, a better model is required.

#### 7.3 Estimation with Junction-to-Board Thermal Resistance

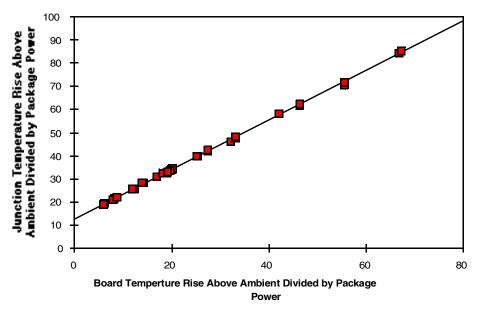

A simple package thermal model which has demonstrated reasonable accuracy (about 20%) is a two resistor model consisting of a junction-to-board and a junction-to-case thermal resistance. The junction-to-case covers the situation where a heat sink is used or where a substantial amount of heat is dissipated from the top of the package. The junction-to-board thermal resistance describes the thermal performance when most of the heat is conducted to the printed circuit board. It has been observed that the thermal performance of most plastic packages and especially PBGA packages is strongly dependent on the board temperature; see Figure 3.

Figure 3. Effect of Board Temperature Rise on Thermal Behavior

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

### 7.6 References

Semiconductor Equipment and Materials International (415) 964-5111

805 East Middlefield Rd. Mountain View, CA 94043

MIL-SPEC and EIA/JESD (JEDEC) Specifications

(Available from Global Engineering Documents)

800-854-7179 or

303-397-7956

JEDEC Specifications http://www.jedec.org

1. C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47-54.

2. B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212-220.

# **8 Layout Practices**

Each  $V_{CC}$  pin on the MPC862/857T/857DSL should be provided with a low-impedance path to the board's supply. Each GND pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The  $V_{CC}$  power supply should be bypassed to ground using at least four 0.1  $\mu$ F by-pass capacitors located as close as possible to the four sides of the package. The capacitor leads and associated printed circuit traces connecting to chip  $V_{CC}$  and GND should be kept to less than half an inch per capacitor lead. A four-layer board is recommended, employing two inner layers as  $V_{CC}$  and GND planes.

All output pins on the MPC862/857T/857DSL have fast rise and fall times. Printed circuit (PC) trace interconnection length should be minimized in order to minimize undershoot and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data busses. Maximum PC trace lengths of six inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PC traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the  $V_{\rm CC}$  and GND circuits. Pull up all unused inputs or signals that will be inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins.

# 9 Bus Signal Timing

The maximum bus speed supported by the MPC862/857T/857DSL is 66 MHz. Higher-speed parts must be operated in half-speed bus mode (for example, an MPC862/857T/857DSL used at 80MHz must be configured for a 40 MHz bus). Table 6 shows the period ranges for standard part frequencies.

100 MHz 50 MHz 66 MHz 80 MHz Freq Min Max Min Max Min Max Min Max 20.00 30.30 25.00 20.00 Period 30.30 15.15 30.30 30.30

**Table 6. Period Range for Standard Part Frequencies**

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

**Table 7. Bus Operation Timings (continued)**

| Num  | Characteristic                                                                                                                                                | 33 MHz |       | 40   | 40 MHz |      | 50 MHz |      | 66 MHz |      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|------|--------|------|--------|------|--------|------|

| Num  | Characteristic                                                                                                                                                | Min    | Max   | Min  | Max    | Min  | Max    | Min  | Max    | Unit |

| В8а  | CLKOUT to TSIZ(0:1), $\overline{REG}$ , $\overline{RSV}$ , AT(0:3) $\overline{BDIP}$ , PTR valid (MAX = 0.25 x B1 + 6.3)                                      | 7.60   | 13.80 | 6.30 | 12.50  | 5.00 | 11.30  | 3.80 | 10.00  | ns   |

| B8b  | CLKOUT to BR, BG, VFLS(0:1),<br>VF(0:2), IWP(0:2), FRZ, LWP(0:1),<br>STS Valid <sup>4</sup> (MAX = 0.25 x B1 + 6.3)                                           | 7.60   | 13.80 | 6.30 | 12.50  | 5.00 | 11.30  | 3.80 | 10.00  | ns   |

| В9   | CLKOUT to A(0:31), BADDR(28:30),<br>RD/WR, BURST, D(0:31), DP(0:3),<br>TSIZ(0:1), REG, RSV, AT(0:3), PTR<br>High-Z (MAX = 0.25 x B1 + 6.3)                    | 7.60   | 13.80 | 6.30 | 12.50  | 5.00 | 11.30  | 3.80 | 10.00  | ns   |

| B11  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ assertion (MAX = 0.25 x B1 + 6.0)                                                                                 | 7.60   | 13.60 | 6.30 | 12.30  | 5.00 | 11.00  | 3.80 | 11.30  | ns   |

| B11a | CLKOUT to $\overline{\text{TA}}$ , $\overline{\text{BI}}$ assertion (when driven by the memory controller or PCMCIA interface) (MAX = 0.00 x B1 + 9.30 $^5$ ) | 2.50   | 9.30  | 2.50 | 9.30   | 2.50 | 9.30   | 2.50 | 9.80   | ns   |

| B12  | CLKOUT to $\overline{TS}$ , $\overline{BB}$ negation (MAX = 0.25 x B1 + 4.8)                                                                                  | 7.60   | 12.30 | 6.30 | 11.00  | 5.00 | 9.80   | 3.80 | 8.50   | ns   |

| B12a | CLKOUT to TA, BI negation (when driven by the memory controller or PCMCIA interface) (MAX = 0.00 x B1 + 9.00)                                                 | 2.50   | 9.00  | 2.50 | 9.00   | 2.50 | 9.00   | 2.50 | 9.00   | ns   |

| B13  | CLKOUT to TS, BB High-Z (MIN = 0.25 x B1)                                                                                                                     | 7.60   | 21.60 | 6.30 | 20.30  | 5.00 | 19.00  | 3.80 | 14.00  | ns   |

| B13a | CLKOUT to TA, BI High-Z (when driven by the memory controller or PCMCIA interface) (MIN = 0.00 x B1 + 2.5)                                                    | 2.50   | 15.00 | 2.50 | 15.00  | 2.50 | 15.00  | 2.50 | 15.00  | ns   |

| B14  | CLKOUT to TEA assertion (MAX = 0.00 x B1 + 9.00)                                                                                                              | 2.50   | 9.00  | 2.50 | 9.00   | 2.50 | 9.00   | 2.50 | 9.00   | ns   |

| B15  | CLKOUT to TEA High-Z (MIN = 0.00 x B1 + 2.50)                                                                                                                 | 2.50   | 15.00 | 2.50 | 15.00  | 2.50 | 15.00  | 2.50 | 15.00  | ns   |

| B16  | TA, BI valid to CLKOUT (setup time)<br>(MIN = 0.00 x B1 + 6.00)                                                                                               | 6.00   | _     | 6.00 | _      | 6.00 | _      | 6.00 | _      | ns   |

| B16a | TEA, KR, RETRY, CR valid to CLKOUT (setup time) (MIN = 0.00 x B1 + 4.5)                                                                                       | 4.50   | _     | 4.50 | _      | 4.50 | _      | 4.50 | _      | ns   |

| B16b | BB, BG, BR, valid to CLKOUT (setup time) <sup>6</sup> (4MIN = 0.00 x B1 + 0.00)                                                                               | 4.00   | _     | 4.00 | _      | 4.00 | _      | 4.00 | _      | ns   |

| B17  | CLKOUT to TA, TEA, BI, BB, BG, BR valid (hold time) (MIN = 0.00 x B1 + 1.00 7)                                                                                | 1.00   | _     | 1.00 | _      | 1.00 | _      | 2.00 | _      | ns   |

#### **Bus Signal Timing**

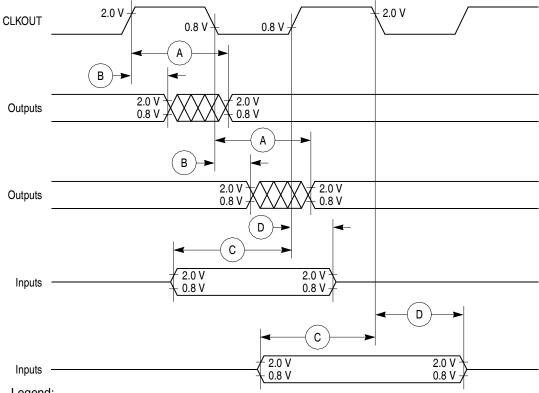

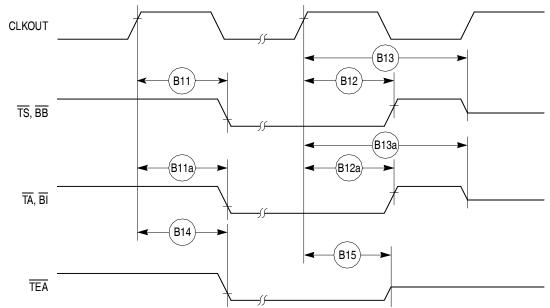

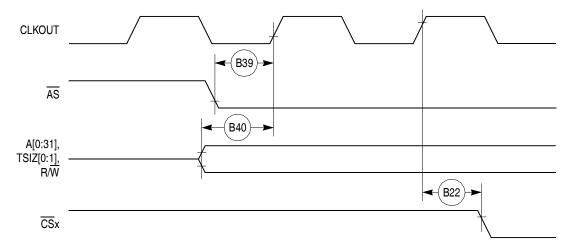

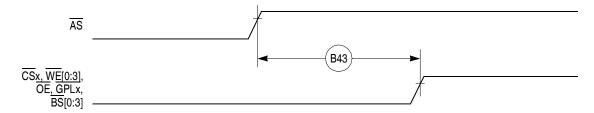

Figure 4 is the control timing diagram.

#### Legend:

- Α Maximum output delay specification.

- В Minimum output hold time.

- Minimum input setup time specification. С

- Minimum input hold time specification.

**Figure 4. Control Timing**

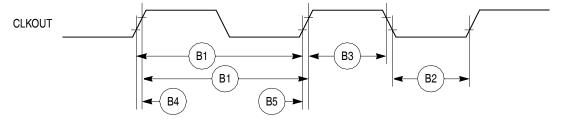

Figure 5 provides the timing for the external clock.

Figure 5. External Clock Timing

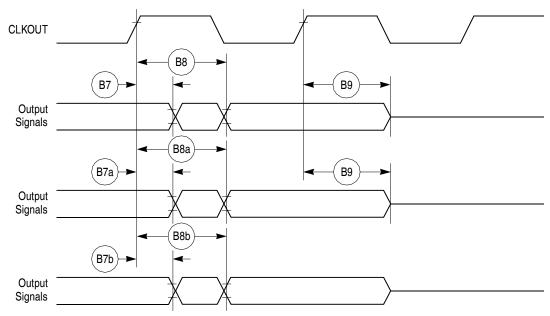

Figure 6 provides the timing for the synchronous output signals.

Figure 6. Synchronous Output Signals Timing

Figure 7 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 7. Synchronous Active Pull-Up Resistor and Open-Drain Outputs Signals Timing

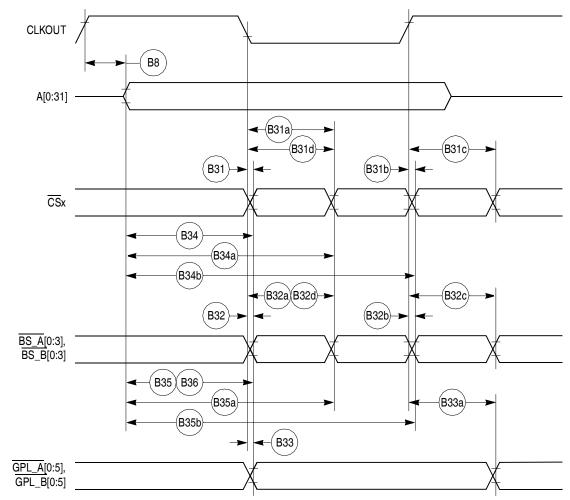

Figure 18 provides the timing for the external bus controlled by the UPM.

Figure 18. External Bus Timing (UPM Controlled Signals)

#### **Bus Signal Timing**

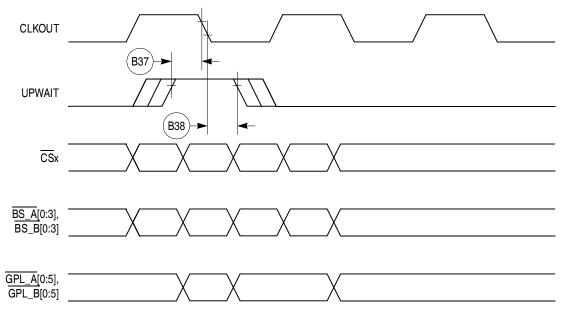

Figure 19 provides the timing for the asynchronous asserted UPWAIT signal controlled by the UPM.

Figure 19. Asynchronous UPWAIT Asserted Detection in UPM Handled Cycles Timing

Figure 20 provides the timing for the asynchronous negated UPWAIT signal controlled by the UPM.

Figure 20. Asynchronous UPWAIT Negated Detection in UPM Handled Cycles Timing

35

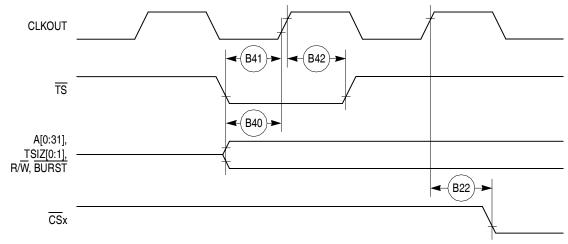

Figure 21 provides the timing for the synchronous external master access controlled by the GPCM.

Figure 21. Synchronous External Master Access Timing (GPCM Handled ACS = 00)

Figure 22 provides the timing for the asynchronous external master memory access controlled by the GPCM.

Figure 22. Asynchronous External Master Memory Access Timing (GPCM Controlled—ACS = 00)

Figure 23 provides the timing for the asynchronous external master control signals negation.

Figure 23. Asynchronous External Master—Control Signals Negation Timing

**CPM Electrical Characteristics**

# 11 CPM Electrical Characteristics

This section provides the AC and DC electrical specifications for the communications processor module (CPM) of the MPC862/857T/857DSL.

## 11.1 PIP/PIO AC Electrical Specifications

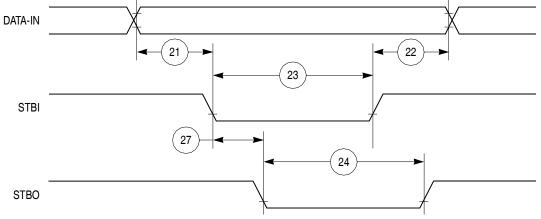

Table 14 provides the PIP/PIO AC timings as shown in Figure 40 though Figure 44.

Table 14. PIP/PIO Timing

| Num   | Characteristic                                                       | All Freq              | uencies | Unit |

|-------|----------------------------------------------------------------------|-----------------------|---------|------|

| Nulli | Characteristic                                                       | Min                   | Max     |      |

| 21    | Data-in setup time to STBI low                                       | 0                     | _       | ns   |

| 22    | Data-in hold time to STBI high                                       | 2.5 – t3 <sup>1</sup> | _       | clk  |

| 23    | STBI pulse width                                                     | 1.5                   | _       | clk  |

| 24    | STBO pulse width                                                     | 1 clk – 5 ns          | _       | ns   |

| 25    | Data-out setup time to STBO low                                      | 2                     | _       | clk  |

| 26    | Data-out hold time from STBO high                                    | 5                     | _       | clk  |

| 27    | STBI low to STBO low (Rx interlock)                                  | _                     | 2       | clk  |

| 28    | STBI low to STBO high (Tx interlock)                                 | 2                     | _       | clk  |

| 29    | Data-in setup time to clock high                                     | 15                    | _       | ns   |

| 30    | Data-in hold time from clock high                                    | 7.5                   | _       | ns   |

| 31    | Clock low to data-out valid (CPU writes data, control, or direction) | _                     | 25      | ns   |

<sup>1</sup> t3 = Specification 23

Figure 40. PIP Rx (Interlock Mode) Timing Diagram

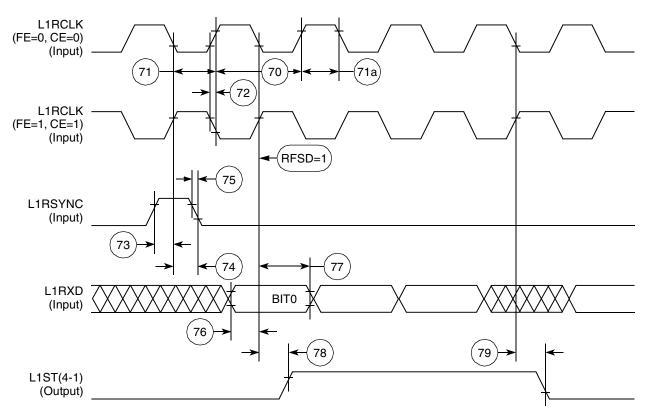

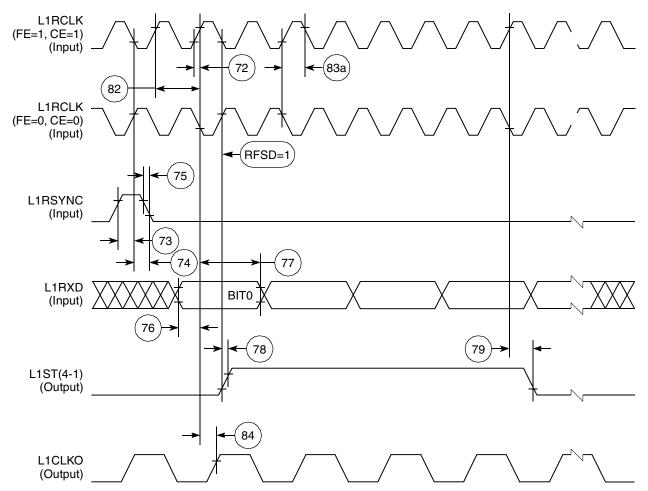

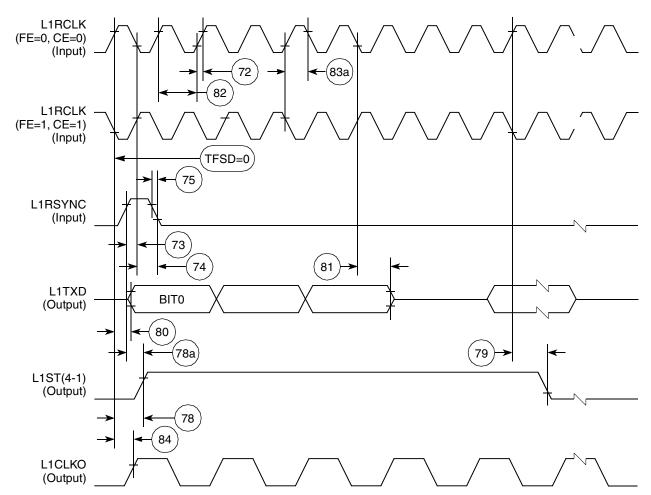

| Num | Characteristic                                                      | All Freq | Unit  |            |

|-----|---------------------------------------------------------------------|----------|-------|------------|

| Num | Characteristic                                                      | Min      | Max   | Onit       |

| 83a | L1RCLK, L1TCLK width high (DSC = 1) <sup>3</sup>                    | P + 10   | _     | ns         |

| 84  | L1CLK edge to L1CLKO valid (DSC = 1)                                | _        | 30.00 | ns         |

| 85  | L1RQ valid before falling edge of L1TSYNC <sup>4</sup>              | 1.00     | _     | L1TCL<br>K |

| 86  | L1GR setup time <sup>2</sup>                                        | 42.00    | _     | ns         |

| 87  | L1GR hold time                                                      | 42.00    | _     | ns         |

| 88  | L1CLK edge to L1SYNC valid (FSD = 00) CNT = 0000, BYT = 0, DSC = 0) | _        | 0.00  | ns         |

The ratio SyncCLK/L1RCLK must be greater than 2.5/1.

<sup>&</sup>lt;sup>4</sup> These strobes and TxD on the first bit of the frame become valid after L1CLK edge or L1SYNC, whichever is later.

Figure 52. SI Receive Timing Diagram with Normal Clocking (DSC = 0)

<sup>&</sup>lt;sup>2</sup> These specs are valid for IDL mode only.

$<sup>^{3}</sup>$  Where P = 1/CLKOUT. Thus for a 25-MHz CLKO1 rate, P = 40 ns.

#### **CPM Electrical Characteristics**

Figure 53. SI Receive Timing with Double-Speed Clocking (DSC = 1)

#### **CPM Electrical Characteristics**

Figure 55. SI Transmit Timing with Double Speed Clocking (DSC = 1)

# 11.12 I<sup>2</sup>C AC Electrical Specifications

Table 26 provides the  $I^2C$  (SCL < 100 KHz) timings.

Table 26. I<sup>2</sup>C Timing (SCL < 100 KHz)

| Nivers | Chavastavistis                            | All Fred |     |      |

|--------|-------------------------------------------|----------|-----|------|

| Num    | Characteristic                            |          | Max | Unit |

| 200    | SCL clock frequency (slave)               | 0        | 100 | kHz  |

| 200    | SCL clock frequency (master) <sup>1</sup> | 1.5      | 100 | kHz  |

| 202    | Bus free time between transmissions       | 4.7      | _   | μs   |

| 203    | Low period of SCL                         | 4.7      | _   | μs   |

| 204    | High period of SCL                        | 4.0      | _   | μs   |

| 205    | Start condition setup time                | 4.7      | _   | μs   |

| 206    | Start condition hold time                 | 4.0      | _   | μs   |

| 207    | Data hold time                            | 0        | _   | μs   |

| 208    | Data setup time                           | 250      | _   | ns   |

| 209    | SDL/SCL rise time                         | _        | 1   | μs   |

| 210    | SDL/SCL fall time                         | _        | 300 | ns   |

| 211    | Stop condition setup time                 | 4.7      | _   | μs   |

SCL frequency is given by SCL = BRGCLK\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(BRGCLK/pre\_scaler) must be greater or equal to 4/1.

Table 27 provides the  $I^2C$  (SCL > 100 kHz) timings.

Table 27.  $I^2C$  Timing (SCL > 100 kHz)

| Num | Characteristic                            | Expression  | All Freq        | Unit          |       |

|-----|-------------------------------------------|-------------|-----------------|---------------|-------|

| Num | Citalacteristic                           | LAPICSSIOII | Min             | Max           | Oiiii |

| 200 | SCL clock frequency (slave)               | fSCL        | 0               | BRGCLK/48     | Hz    |

| 200 | SCL clock frequency (master) <sup>1</sup> | fSCL        | BRGCLK/16512    | BRGCLK/48     | Hz    |

| 202 | Bus free time between transmissions       | _           | 1/(2.2 * fSCL)  | _             | s     |

| 203 | Low period of SCL                         | _           | 1/(2.2 * fSCL)  | _             | s     |

| 204 | High period of SCL                        | _           | 1/(2.2 * fSCL)  | _             | s     |

| 205 | Start condition setup time                | _           | 1/(2.2 * fSCL)  | _             | s     |

| 206 | Start condition hold time                 | _           | 1/(2.2 * fSCL)  | _             | s     |

| 207 | Data hold time                            | _           | 0               | _             | s     |

| 208 | Data setup time                           | _           | 1/(40 * fSCL)   | _             | s     |

| 209 | SDL/SCL rise time                         | _           | _               | 1/(10 * fSCL) | s     |

| 210 | SDL/SCL fall time                         | _           | _               | 1/(33 * fSCL) | s     |

| 211 | Stop condition setup time                 | _           | 1/2(2.2 * fSCL) | _             | S     |

SCL frequency is given by SCL = BrgClk\_frequency / ((BRG register + 3) \* pre\_scaler \* 2). The ratio SyncClk/(Brg\_Clk/pre\_scaler) must be greater or equal to 4/1.

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

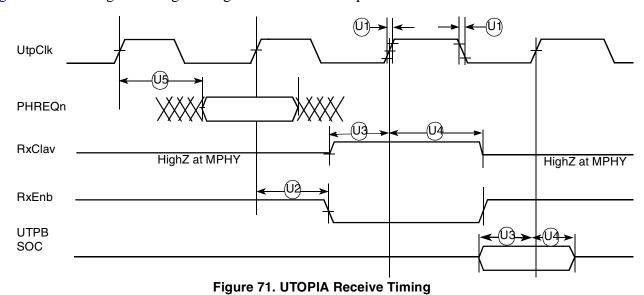

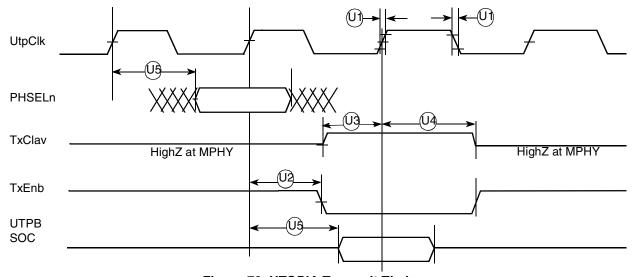

Figure 71 shows signal timings during UTOPIA receive operations.

Figure 72 shows signal timings during UTOPIA transmit operations.

Figure 72. UTOPIA Transmit Timing

# 13 FEC Electrical Characteristics

This section provides the AC electrical specifications for the Fast Ethernet controller (FEC). Note that the timing specifications for the MII signals are independent of system clock frequency (part speed designation). Furthermore, MII signals use TTL signal levels compatible with devices operating at either 5.0 or 3.3 V.

**FEC Electrical Characteristics**

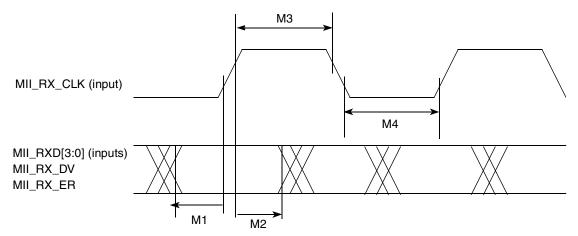

# 13.1 MII Receive Signal Timing (MII\_RXD[3:0], MII\_RX\_DV, MII\_RX\_ER, MII\_RX\_CLK)

The receiver functions correctly up to a MII\_RX\_CLK maximum frequency of 25MHz +1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_RX\_CLK frequency - 1%.

Table 29 provides information on the MII receive signal timing.

| Num | Characteristic                                         | Min | Max | Unit              |

|-----|--------------------------------------------------------|-----|-----|-------------------|

| M1  | MII_RXD[3:0], MII_RX_DV, MII_RX_ER to MII_RX_CLK setup | 5   | _   | ns                |

| M2  | MII_RX_CLK to MII_RXD[3:0], MII_RX_DV, MII_RX_ER hold  | 5   | _   | ns                |

| М3  | MII_RX_CLK pulse width high                            | 35% | 65% | MII_RX_CLK period |

| M4  | MII_RX_CLK pulse width low                             | 35% | 65% | MII_RX_CLK period |

**Table 29. MII Receive Signal Timing**

Figure 73 shows MII receive signal timing.

Figure 73. MII Receive Signal Timing Diagram

# 13.2 MII Transmit Signal Timing (MII\_TXD[3:0], MII\_TX\_EN, MII\_TX\_ER, MII\_TX\_CLK)

The transmitter functions correctly up to a MII\_TX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed the MII\_TX\_CLK frequency - 1%.

Table 30 provides information on the MII transmit signal timing.

Num

Characteristic

Min

Max

Unit

M5

MII\_TX\_CLK to MII\_TXD[3:0], MII\_TX\_EN, MII\_TX\_ER invalid

5

—

ns

M6

MII\_TX\_CLK to MII\_TXD[3:0], MII\_TX\_EN, MII\_TX\_ER valid

—

25

Table 30. MII Transmit Signal Timing

MPC862/857T/857DSL PowerQUICC™ Family Hardware Specifications, Rev. 3

## Table 35. Pin Assignments (continued)

| Name                                    | Pin Number | Туре                                    |

|-----------------------------------------|------------|-----------------------------------------|

| PA15<br>RXD1<br>RXD4                    | C18        | Bidirectional                           |

| PA14<br>TXD1<br>TXD4                    | D17        | Bidirectional<br>(Optional: Open-drain) |

| PA13<br>RXD2                            | E17        | Bidirectional                           |

| PA12<br>TXD2                            | F17        | Bidirectional<br>(Optional: Open-drain) |

| PA11<br>L1TXDB<br>RXD3                  | G16        | Bidirectional<br>(Optional: Open-drain) |

| PA10<br>L1RXDB<br>TXD3                  | J17        | Bidirectional<br>(Optional: Open-drain) |

| PA9<br>L1TXDA                           | K18        | Bidirectional<br>(Optional: Open-drain) |

| RXD4                                    |            |                                         |

| PA8<br>L1RXDA<br>TXD4                   | L17        | Bidirectional<br>(Optional: Open-drain) |

| PA7<br>CLK1<br>L1RCLKA<br>BRGO1<br>TIN1 | M19        | Bidirectional                           |

| PA6<br>CLK2<br>TOUT1                    | M17        | Bidirectional                           |

| PA5<br>CLK3<br>L1TCLKA<br>BRGO2<br>TIN2 | N18        | Bidirectional                           |

| PA4<br>CLK4<br>TOUT2                    | P19        | Bidirectional                           |

| PA3<br>CLK5<br>BRGO3<br>TIN3            | P17        | Bidirectional                           |

## Table 35. Pin Assignments (continued)

| Name                                 | Pin Number | Туре          |

|--------------------------------------|------------|---------------|

| PD12<br>L1RSYNCB<br>MII-MDC<br>UTPB3 | R16        | Bidirectional |

| PD11<br>RXD3<br>MII-TXERR<br>RXENB   | T16        | Bidirectional |

| PD10<br>TXD3<br>MII-RXD0<br>TXENB    | W18        | Bidirectional |

| PD9<br>RXD4<br>MII-TXD0<br>UTPCLK    | V17        | Bidirectional |

| PD8<br>TXD4<br>MII-MDC<br>MII-RXCLK  | W17        | Bidirectional |

| PD7<br>RTS3<br>MII-RXERR<br>UTPB4    | T15        | Bidirectional |

| PD6<br>RTS4<br>MII-RXDV<br>UTPB5     | V16        | Bidirectional |

| PD5<br>REJECT2<br>MII-TXD3<br>UTPB6  | U15        | Bidirectional |

| PD4<br>REJECT3<br>MII-TXD2<br>UTPB7  | U16        | Bidirectional |

| PD3<br>REJECT4<br>MII-TXD1<br>SOC    | W16        | Bidirectional |

| TMS                                  | G18        | Input         |

| TDI<br>DSDI                          | H17        | Input         |

| TCK<br>DSCK                          | H16        | Input         |