Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                 |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 15x12b; D/A 3x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 49-UFBGA, WLCSP                                                         |

| Supplier Device Package    | 49-WLCSP (2.89x3.74)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f334c8y6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1 Introduction

This datasheet provides the ordering information and the mechanical device characteristics of the STM32F334x4/6/8 microcontrollers.

This document should be read in conjunction with the STM32F303xx reference manual RM0364 available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M4 core with FPU, refer to:

- ARM<sup>®</sup> Cortex<sup>®</sup>-M4 Processor Technical Reference Manual available from the www.arm.com website.

- STM32F3xxx and STM32F4xxx Cortex<sup>®</sup>-M4 programming manual (PM0214) available from the <u>www.st.com</u> website.

### **3** Functional overview

# 3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU with embedded Flash and SRAM

The ARM Cortex-M4 processor with FPU is the latest generation of ARM processors for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM 32-bit Cortex-M4 RISC processor with FPU features exceptional code-efficiency, delivering the high performance expected from an ARM core, with memory sizes usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allows efficient signal processing and complex algorithm execution.

Its single precision FPU speeds up software development by using metalanguage development tools, while avoiding saturation.

With its embedded ARM core, the STM32F334x4/6/8 family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the STM32F334x4/6/8 family devices.

#### 3.2 Memories

#### 3.2.1 Embedded Flash memory

All STM32F334x4/6/8 devices feature up to 64 Kbytes of embedded Flash memory available for storing programs and data. The Flash memory access time is adjusted to the CPU clock frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above).

#### 3.2.2 Embedded SRAM

The STM32F334x4/6/8 devices feature up to 12 Kbytes of embedded SRAM with hardware parity check. The memory can be accessed in read/write at CPU clock speed with 0 wait states, allowing the CPU to achieve 90 Dhrystone Mips at 72 MHz when running code from CCM (core coupled memory) RAM.

The SRAM is organized as follows:

- 4 Kbytes of SRAM on instruction and data bus with parity check (core coupled memory or CCM) and used to execute critical routines or to access data

- 12 Kbytes of SRAM with parity check mapped on the data bus.

input channels. The precise voltage of VREFINT is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

#### 3.10.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC1\_IN17. As the V<sub>BAT</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the V<sub>BAT</sub> pin is internally connected to a bridge divider by 2. As a consequence, the converted digital value is half the V<sub>BAT</sub> voltage.

#### 3.10.4 OPAMP2 reference voltage (VOPAMP2)

OPAMP2 reference voltage can be measured using ADC2 internal channel 17.

#### 3.11 Digital-to-analog converter (DAC)

One 12-bit buffered DAC channel (DAC1\_OUT1) and two 12-bit unbuffered DAC channels (DAC1\_OUT2 and DAC2\_OUT1) can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital interface supports the following features:

- Three DAC output channels

- 8-bit or 12-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation (only on DAC1)

- Triangular-wave generation (only on DAC1)

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

#### 3.12 Operational amplifier (OPAMP)

The STM32F334x4/6/8 embeds an operational amplifier (OPAMP2) with external or internal follower routing and PGA capability (or even amplifier and filter capability with external components). When an operational amplifier is selected, an external ADC channel is used to enable output measurement.

The operational amplifier features:

- 8 MHz GBP

- 0.5 mA output capability

- Rail-to-rail input/output

- In PGA mode, the gain can be programmed to 2, 4, 8 or 16.

### 3.19 Development support

#### 3.19.1 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

| Pi         | n Numb     | er         |                                    |          |               | Pin functions                                                                                                |                      |  |

|------------|------------|------------|------------------------------------|----------|---------------|--------------------------------------------------------------------------------------------------------------|----------------------|--|

| LQFP<br>32 | LQFP<br>48 | LQFP<br>64 | Pin name (function<br>after reset) | Pin type | I/O structure | Alternate<br>functions                                                                                       | Additional functions |  |

| 28         | 41         | 57         | PB5                                | I/O      | FT            | TIM16_BKIN,<br>TIM3_CH2,<br>I2C1_SMBA,<br>SPI1_MOSI,<br>USART2_CK,<br>TIM17_CH1,<br>HRTIM1_EEV6,<br>EVENTOUT | -                    |  |

| 29         | 42         | 58         | PB6                                | I/O      | FTf           | TIM16_CH1N,<br>TSC_G5_IO3,<br>I2C1_SCL,<br>USART1_TX,<br>HRTIM1_SCIN,<br>HRTIM1_EEV4,<br>EVENTOUT            | -                    |  |

| 30         | 43         | 59         | PB7                                | I/O      | FTf           | TIM17_CH1N,<br>TSC_G5_IO4,<br>I2C1_SDA,<br>USART1_RX,<br>TIM3_CH4,<br>HRTIM1_EEV3,<br>EVENTOUT               | -                    |  |

| 31         | 44         | 60         | BOOT0                              | I        | В             | -                                                                                                            | -                    |  |

| -          | 45         | 61         | PB8                                | I/O      | FTf           | TIM16_CH1,<br>TSC_SYNC, I2C1_SCL,<br>USART3_RX, CAN_RX,<br>TIM1_BKIN,<br>HRTIM1_EEV8,<br>EVENTOUT            | -                    |  |

| -          | 46         | 62         | PB9                                | I/O      | FTf           | TIM17_CH1, I2C1_SDA,<br>IR_OUT, USART3_TX,<br>COMP2_OUT, CAN_TX,<br>HRTIM1_EEV5,<br>EVENTOUT                 | -                    |  |

| 32         | 47         | 63         | VSS                                | S        | -             | -                                                                                                            | -                    |  |

| 1          | 48         | 64         | VDD                                | S        | -             | -                                                                                                            | -                    |  |

| Table 13. STM32F334x4/ | 6/8 pin definitions | (continued) |

|------------------------|---------------------|-------------|

|                        |                     | (001101000) |

1.

PC13, PC14 and PC15 are supplied through the power switch. Since the switch sinks only a limited amount of current (3 mA), the use of GPIO PC13 to PC15 in output mode is limited: - The speed should not exceed 2 MHz with a maximum load of 30 pF - These GPIOs must not be used as current sources (e.g. to drive an LED). After the first backup domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the Backup registers which is not reset by the main reset. For details on how to manage these GPIOs, refer to the Battery backup domain and BKP register description sections in the reference manual.

2. Fast ADC channel.

3. These GPIOs offer a reduced touch sensing sensitivity. It is thus recommended to use them as sampling capacitor I/O.

| Calibration value name  | Description                                                              | Memory address            |

|-------------------------|--------------------------------------------------------------------------|---------------------------|

| V <sub>REFINT_CAL</sub> | Raw data acquired at<br>temperature of 30 °C<br>V <sub>DDA</sub> = 3.3 V | 0x1FFF F7BA - 0x1FFF F7BB |

#### Table 24. Internal reference voltage calibration values

#### 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 11: Scheme of the current-consumption measurement.*

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

Note: The total current consumption is the sum of IDD and IDDA.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states from 48 to 72 MHz)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled  $f_{PCLK2} = f_{HCLK}$  and  $f_{PCLK1} = f_{HCLK/2}$

- When f<sub>HCLK</sub> > 8 MHz, the PLL is ON and the PLL input is equal to HSI/2 (4 MHz) or HSE (8 MHz) in bypass mode.

The parameters given in *Table 25* to *Table 29* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 19*.

|                  |                                   |                     |                                                             |                         | Тур. @   | €V <sub>DD</sub> ( | V <sub>DD</sub> = | V <sub>DDA</sub> ) | )        |                           | Max. <sup>(1)</sup>      |                                |      |  |

|------------------|-----------------------------------|---------------------|-------------------------------------------------------------|-------------------------|----------|--------------------|-------------------|--------------------|----------|---------------------------|--------------------------|--------------------------------|------|--|

| Symbol           | Parameter                         |                     | Conditions                                                  | 2.0<br>V                | 2.4<br>V | 2.7<br>V           | 3.0<br>V          | 3.3<br>V           | 3.6<br>V | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 ℃ | T <sub>A</sub> =<br>105 °<br>C | Unit |  |

|                  | Supply<br>current in<br>Stop mode | supervisor ON       | Regulator in run/low-<br>power mode, all<br>oscillators OFF | 1.67                    | 1.79     | 1.91               | 2.04              | 2.19               | 2.35     | 2.5                       | 5.9                      | 6.2                            |      |  |

|                  | Supply                            |                     | LSI ON and IWDG ON                                          | 2.06                    | 2.24     | 2.41               | 2.60              | 2.80               | 3.04     | -                         | -                        | -                              |      |  |

|                  | ••••••••••                        | V <sub>DDA</sub> sı | LSI OFF and IWDG<br>OFF                                     | 1.54                    | 1.68     | 1.78               | 1.92              | 2.06               | 2.22     | 2.6                       | 3.0                      | 3.8                            |      |  |

| I <sub>DDA</sub> | Supply<br>current in<br>Stop mode | supervisor OFF      | Regulator in run/low-<br>power mode, all<br>oscillators OFF | 0.97                    | 0.99     | 1.03               | 1.07              | 1.14               | 1.22     | -                         | -                        | -                              | μA   |  |

|                  | Supply                            |                     | LSI ON and IWDG ON                                          | 1.36                    | 1.44     | 1.52               | 1.62              | 1.76               | 1.91     | -                         | -                        | -                              |      |  |

|                  | current in<br>Standby<br>mode     |                     | V <sub>DDA</sub> su                                         | LSI OFF and IWDG<br>OFF | 0.86     | 0.88               | 0.91              | 0.95               | 1.03     | 1.09                      | -                        | -                              | -    |  |

Table 28. Typical and maximum  $V_{DDA}$  consumption in Stop and Standby modes

1. Data based on characterization results, not tested in production.

|          | Para              |                                                                                           | Typ.@V <sub>BAT</sub> |      |      |      |      |      |      |      | @V <sub>E</sub>          |                              |                           |      |

|----------|-------------------|-------------------------------------------------------------------------------------------|-----------------------|------|------|------|------|------|------|------|--------------------------|------------------------------|---------------------------|------|

| Symbol   | meter             | Conditions <sup>(1)</sup>                                                                 | 1.65<br>V             | 1.8V | 2V   | 2.4V | 2.7V | 3V   | 3.3V | 3.6V | T <sub>A</sub> =<br>25°C | T <sub>A</sub> =<br>85°<br>C | T <sub>A</sub> =<br>105°C | Unit |

|          | Backup<br>domain  | LSE & RTC<br>ON; "Xtal<br>mode" lower<br>driving<br>capability;<br>LSEDRV[1:0]<br>= '00'  | 0.42                  | 0.44 | 0.47 | 0.54 | 0.60 | 0.66 | 0.74 | 0.82 | _                        | -                            | -                         |      |

| IDD_VBAT | supply<br>current | LSE & RTC<br>ON; "Xtal<br>mode" higher<br>driving<br>capability;<br>LSEDRV[1:0]<br>= '11' | 0.71                  | 0.74 | 0.77 | 0.85 | 0.91 | 0.98 | 1.06 | 1.16 | -                        | -                            | -                         | μA   |

#### Table 29. Typical and maximum current consumption from $V_{\text{BAT}}$ supply

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a CL of 6 pF for typical values.

2. Data based on characterization results, not tested in production.

|                                     |                                            |                                       |                   | Ту                     | /p.                                                                                                                                                                         |      |  |  |

|-------------------------------------|--------------------------------------------|---------------------------------------|-------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| Symbol                              | Parameter                                  | Conditions                            | <sup>f</sup> HCLK | Peripherals<br>enabled | Peripherals<br>disabled           6.3           5.7           4.40           3.13           2.49           1.85           0.99           0.88           0.80           0.76 | Unit |  |  |

|                                     |                                            |                                       | 72 MHz 51.8       |                        |                                                                                                                                                                             |      |  |  |

|                                     |                                            |                                       | 64 MHz            | 46.4                   | 5.7                                                                                                                                                                         |      |  |  |

|                                     |                                            |                                       | 48 MHz            | 35.0                   | 4.40                                                                                                                                                                        |      |  |  |

|                                     |                                            |                                       | 32 MHz            | 23.7                   | 3.13                                                                                                                                                                        |      |  |  |

|                                     |                                            |                                       | 24 MHz            | 18.0                   | 2.49                                                                                                                                                                        |      |  |  |

|                                     | Supply current in                          |                                       | 16 MHz            | 12.2                   | 1.85                                                                                                                                                                        | ^    |  |  |

| I <sub>DD</sub>                     | Sleep mode from<br>V <sub>DD</sub> supply  |                                       | 8 MHz             | 6.2                    | 0.99                                                                                                                                                                        | - mA |  |  |

|                                     |                                            |                                       | 4 MHz             | 3.68                   | 0.88                                                                                                                                                                        |      |  |  |

|                                     |                                            | Running from HSE crystal clock 8 MHz, | 2 MHz             | 2.26                   | 0.80                                                                                                                                                                        | μΑ   |  |  |

|                                     |                                            |                                       | 1 MHz             | 1.55                   | 0.76                                                                                                                                                                        |      |  |  |

|                                     |                                            |                                       | 500 kHz           | 1.20                   | 0.74                                                                                                                                                                        |      |  |  |

|                                     |                                            |                                       | 125 kHz           | 0.89                   | 0.72                                                                                                                                                                        |      |  |  |

|                                     |                                            | code executing from<br>Flash or RAM   | 72 MHz            | 239.0                  | 236.7                                                                                                                                                                       |      |  |  |

|                                     |                                            | FIASTI OF RAIM                        | 64 MHz            | 209.4                  | 207.8                                                                                                                                                                       |      |  |  |

|                                     |                                            |                                       | 48 MHz            | 154.0                  | 152.9                                                                                                                                                                       |      |  |  |

|                                     |                                            |                                       | 32 MHz            | 103.7                  | 103.2                                                                                                                                                                       |      |  |  |

|                                     |                                            |                                       | 24 MHz            | 80.1                   | 79.8                                                                                                                                                                        |      |  |  |

| ı (1)(2)                            | Supply current in                          |                                       | 16 MHz            | 56.7                   | 56.6                                                                                                                                                                        |      |  |  |

| I <sub>DDA</sub> <sup>(1) (2)</sup> | Sleep mode from<br>V <sub>DDA</sub> supply |                                       | 8 MHz             | 1.14                   | 1.14                                                                                                                                                                        |      |  |  |

|                                     |                                            |                                       | 4 MHz             | 1.14                   | 1.14                                                                                                                                                                        |      |  |  |

|                                     |                                            |                                       | 2 MHz             | 1.14                   | 1.14                                                                                                                                                                        |      |  |  |

|                                     |                                            |                                       | 1 MHz             | 1.14                   | 1.14                                                                                                                                                                        |      |  |  |

|                                     |                                            |                                       | 500 kHz           | 1.14                   | 1.14                                                                                                                                                                        |      |  |  |

|                                     |                                            |                                       | 125 kHz           | 1.14                   | 1.14                                                                                                                                                                        | 1    |  |  |

| Table 31. Typical current | consumption in Sleep | mode, code running | from Flash or RAM |

|---------------------------|----------------------|--------------------|-------------------|

|                           |                      |                    |                   |

1.  $V_{DDA}$  supervisor is OFF.

2. When peripherals are enabled, the power consumption of the analog part of peripherals such as ADC, DAC, Comparators, OpAmp etc. is not included. Refer to the tables of characteristics in the subsequent sections.

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 50: I/O static characteristics*.

DocID025409 Rev 5

#### 6.3.10 Memory characteristics

#### Flash memory

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

| -                  |                         | -                               |      |      |                     |      |

|--------------------|-------------------------|---------------------------------|------|------|---------------------|------|

| Symbol             | Parameter               | Conditions                      | Min. | Тур. | Max. <sup>(1)</sup> | Unit |

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = -40 to +105 °C | 40   | 53.5 | 60                  | μs   |

| t <sub>ERASE</sub> | Page (2 KB) erase time  | $T_A = -40$ to +105 °C          | 20   | -    | 40                  | ms   |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +105 °C          | 20   | -    | 40                  | ms   |

| I <sub>DD</sub>    | Supply current          | Write mode                      | -    | -    | 10                  | mA   |

|                    |                         | Erase mode                      | -    | -    | 12                  | mA   |

| Table 43. Flash memory | characteristics |

|------------------------|-----------------|

|------------------------|-----------------|

1. Guaranteed by design, not tested in production.

| 0h.el            | Demonster Openditions |                                                                                   | Value               | 11 14   |  |

|------------------|-----------------------|-----------------------------------------------------------------------------------|---------------------|---------|--|

| Symbol           | Parameter             | Conditions                                                                        | Min. <sup>(1)</sup> | Unit    |  |

| N <sub>END</sub> | Endurance             | TA = -40 to +85 °C (6 suffix versions)<br>TA = -40 to +105 °C (7 suffix versions) | 10                  | kcycles |  |

|                  | Data retention        | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                 | 30                  |         |  |

| t <sub>RET</sub> |                       | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                | 10                  | Years   |  |

|                  |                       | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                               | 20                  |         |  |

1. Data based on characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

#### 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 45*. They are based on the EMS levels and classes defined in application note AN1709.

DocID025409 Rev 5

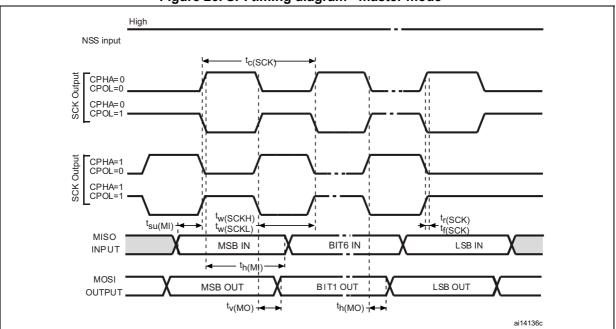

Figure 26. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at  $0.5V_{DD}$  and with external C<sub>L</sub> = 30 pF.

#### CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

#### 6.3.19 ADC characteristics

Unless otherwise specified, the parameters given in *Table 64* to *Table 67* are guaranteed by design, with conditions summarized in *Table 19*.

| Symbol           | Parameter                     | Conditions                     | Min.                                               | Тур.   | Max.   | Unit |

|------------------|-------------------------------|--------------------------------|----------------------------------------------------|--------|--------|------|

| V <sub>DDA</sub> | Analog supply voltage for ADC | -                              | 2                                                  | -      | 3.6    | V    |

|                  |                               | Single ended mode, 5<br>MSPS,  | -                                                  | 1011.3 | 1172.0 |      |

|                  |                               | Single ended mode, 1<br>MSPS   | -                                                  | 214.7  | 322.3  |      |

|                  | ADC current consumption       | Single ended mode, 200<br>KSPS | e ended mode, 200 - 54.7<br>ential mode,5 - 1061.5 | 81.1   |        |      |

| I <sub>DDA</sub> | (Figure 27)                   | Differential mode,5<br>MSPS,   |                                                    | 1243.6 | μA     |      |

|                  |                               | Differential mode, 1<br>MSPS   | -                                                  | 246.6  | 337.6  |      |

|                  |                               | Differential mode, 200<br>KSPS | -                                                  | 56.4   | 83.0   |      |

Table 64. ADC characteristics

#### **Electrical characteristics**

| Symbol       | Parameter                          | Conditions           |                     |                     | Min<br>(3) | Тур     | Max<br>(3) | Unit  |

|--------------|------------------------------------|----------------------|---------------------|---------------------|------------|---------|------------|-------|

| Total        |                                    | 0                    | Fast channel 5.1 Ms | -                   | ±4         | ±4.5    |            |       |

|              |                                    |                      | Single ended        | Slow channel 4.8 Ms | -          | ±5.5 ±6 | ±6         |       |

| ET           | unadjusted<br>error                |                      |                     | Fast channel 5.1 Ms | -          | ±3.5    | ±4         |       |

|              |                                    |                      | Differential        | Slow channel 4.8 Ms | -          | ±3.5    | ±4         |       |

|              |                                    |                      | Single ended        | Fast channel 5.1 Ms | -          | ±2      | ±2         |       |

| FO           | Offect error                       |                      | Single ended        | Slow channel 4.8 Ms | -          | ±1.5    | ±2         |       |

| EO           | Offset error                       | fset error           | Differential        | Fast channel 5.1 Ms | -          | ±1.5    | ±2         |       |

|              |                                    |                      | Differential        | Slow channel 4.8 Ms | -          | ±1.5    | ±2         |       |

|              |                                    |                      | Single and d        | Fast channel 5.1 Ms | -          | ±3      | ±4         |       |

| EG Gain erro | Coin orror                         | or                   | Single ended -      | Slow channel 4.8 Ms | -          | ±5      | ±5.5       |       |

|              | Gain enor                          |                      | Differential        | Fast channel 5.1 Ms | -          | ±3      | ±3         | - LSB |

|              |                                    |                      |                     | Slow channel 4.8 Ms | -          | ±3      | ±3.5       |       |

|              |                                    | inearity Vop = 3.3 V | Fast channel 5.1 Ms | -                   | ±1         | ±1      |            |       |

|              | Differential<br>linearity<br>error |                      | Single ended        | Slow channel 4.8 Ms | -          | ±1      | ±1         |       |

| ED           |                                    |                      | Differential        | Fast channel 5.1 Ms | -          | ±1      | ±1         |       |

|              |                                    |                      | Differential        | Slow channel 4.8 Ms | -          | ±1      | ±1         |       |

|              |                                    |                      | Single ended        | Fast channel 5.1 Ms | -          | ±1.5    | ±2         |       |

| -            | Integral                           | Single ended         | Slow channel 4.8 Ms | -                   | ±2         | ±3      | 1          |       |

| EL           | linearity<br>error                 |                      | Differential        | Fast channel 5.1 Ms | -          | ±1.5    | ±1.5       |       |

|              |                                    | Differentia          | Dillerential        | Slow channel 4.8 Ms | -          | ±1.5    | ±2         |       |

|              |                                    |                      | Cingle and d        | Fast channel 5.1 Ms | 10.8       | 10.8    | -          |       |

| ENOB         | Effective                          | number of            | Single ended        | Slow channel 4.8 Ms | 10.8       | 10.8    | -          | L.:4  |

| (4)          | number of<br>bits                  |                      | Differential        | Fast channel 5.1 Ms | 11.2 11.3  | -       | bit        |       |

|              |                                    |                      | Dillerential        | Slow channel 4.8 Ms | 11.2       | 11.3    | -          |       |

|              | Circulto                           |                      | Single ended        | Fast channel 5.1 Ms | 66         | 67      | -          |       |

| SINAD        | Signal-to-<br>noise and            |                      |                     | Slow channel 4.8 Ms | 66         | 67      | -          | dB    |

| (4)          | distortion                         |                      | Differential        | Fast channel 5.1 Ms | 69         | 70      | -          | uБ    |

|              | ratio                              |                      |                     | Slow channel 4.8 Ms | 69         | 70      | -          |       |

### Table 66. ADC accuracy - limited test conditions<sup>(1)(2)</sup>

| Symbol             | Parameter                                      | Conditions                        |              |                                                |                     | Max<br>(4) | Unit |    |

|--------------------|------------------------------------------------|-----------------------------------|--------------|------------------------------------------------|---------------------|------------|------|----|

| EL                 |                                                |                                   | Single ended | Fast channel 5.1 Ms                            | -                   | ±3         |      |    |

|                    | Integral<br>linearity                          |                                   |              | Slow channel 4.8 Ms                            | -                   | ±3.5       |      |    |

|                    | error                                          |                                   | Differential | Fast channel 5.1 Ms                            | -                   | ±2         |      |    |

|                    |                                                |                                   | Differential | Slow channel 4.8 Ms                            | -                   | ±2.5       |      |    |

|                    |                                                |                                   | Single ended | Fast channel 5.1 Ms                            | 10.4                | -          | bits |    |

| ENOB               | Effective<br>number of                         | r of Sampling freq. $\leq 5$ Msps | Single ended | Slow channel 4.8 Ms                            | 10.4                | -          |      |    |

| (5)                | bits                                           |                                   | Differential | Fast channel 5.1 Ms                            | 10.8                | -          |      |    |

|                    |                                                |                                   | Differential | Slow channel 4.8 Ms                            | 10.8                | -          |      |    |

|                    | Signal-to-<br>noise and<br>distortion<br>ratio | ind                               | Single ended | ded Fast channel 5.1 Ms<br>Slow channel 4.8 Ms | 64                  | -          | dB   |    |

| SINAD              |                                                |                                   | Single ended |                                                | 63                  | -          |      |    |

| (5)                |                                                |                                   | Differential | Fast channel 5.1 Ms                            | 67                  | -          |      |    |

|                    |                                                |                                   |              | Slow channel 4.8 Ms                            | 67                  | -          |      |    |

|                    | Signal-to-                                     | ) Signal-to-                      |              | Single ended                                   | Fast channel 5.1 Ms | 64         | -    | dB |

| SNR <sup>(5)</sup> |                                                |                                   |              | Single ended                                   | Slow channel 4.8 Ms | 64         | -    |    |

| SINK               | noise ratio                                    |                                   | Differential | Fast channel 5.1 Ms                            | 67                  | -          |      |    |

|                    |                                                |                                   | Differential | Slow channel 4.8 Ms                            | 67                  | -          |      |    |

| THD <sup>(5)</sup> | Total                                          | armonic                           | Single ended | Fast channel 5.1 Ms                            | -                   | -75        |      |    |

|                    |                                                |                                   |              | Slow channel 4.8 Ms                            | -                   | -75        |      |    |

| יישחו              | distortion                                     |                                   | Differential | Fast channel 5.1 Ms                            | -                   | -79        |      |    |

|                    |                                                |                                   |              | Slow channel 4.8 Ms                            | -                   | -78        |      |    |

#### Table 67. ADC accuracy $^{(1)(2)(3)}$ (continued)

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.14 does not affect the ADC accuracy.

- 3. Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

- 4. Data based on characterization results, not tested in production.

- 5. Value measured with a -0.5 dB full scale 50 kHz sine wave input signal.

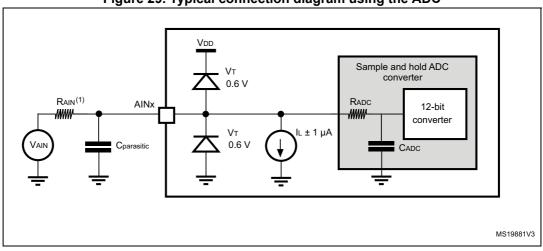

Figure 29. Typical connection diagram using the ADC

1. Refer to *Table 64* for the values of R<sub>AIN</sub>.

C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 10: Power-supply scheme*. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

#### 6.3.20 DAC electrical specifications

| Symbol                           | Parameter                                                  | Conditions                                                                                                            | Min. | Тур. | Max.                    | Unit |

|----------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|-------------------------|------|

| V <sub>DDA</sub>                 | Analog supply voltage -                                    |                                                                                                                       | 2.4  | -    | 3.6                     | V    |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load DAC output buffer ON (to V <sub>SSA</sub> ) |                                                                                                                       | 5    | -    | -                       | kΩ   |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load                                             | DAC output buffer ON (to $V_{DDA}$ )                                                                                  | 25   | -    | -                       | kΩ   |

| R <sub>O</sub> <sup>(1)</sup>    | Output impedance                                           | DAC output buffer OFF                                                                                                 | -    | -    | 15                      | kΩ   |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                            | DAC output buffer ON                                                                                                  | -    | -    | 50                      | pF   |

| V <sub>DAC,OUT</sub> (           | Voltage on DAC_OUT                                         | Corresponds to 12-bit input code (0x0E0) to (0xF1C) at $V_{DDA}$ = 3.6 V and (0x155) and (0xEAB) at $V_{DDA}$ = 2.4 V | 0.2  | -    | V <sub>DDA</sub> – 0.2  | v    |

|                                  |                                                            |                                                                                                                       | -    | 0.5  | -                       | mV   |

|                                  |                                                            | DAC output buffer OFF -                                                                                               |      | -    | V <sub>DDA</sub> – 1LSB | V    |

| I <sub>DDA</sub> <sup>(3)</sup>  | DAC DC current consumption in quiescent                    | With no load, middle code (0x800)<br>on the input                                                                     |      | -    | 380                     | μA   |

|                                  | mode <sup>(2)</sup>                                        | With no load, worst code (0xF1C) on the input.                                                                        | -    | -    | 480                     | μA   |

#### Table 69. DAC characteristics

### 7 Package information

### 7.1 Package mechanical data

To meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

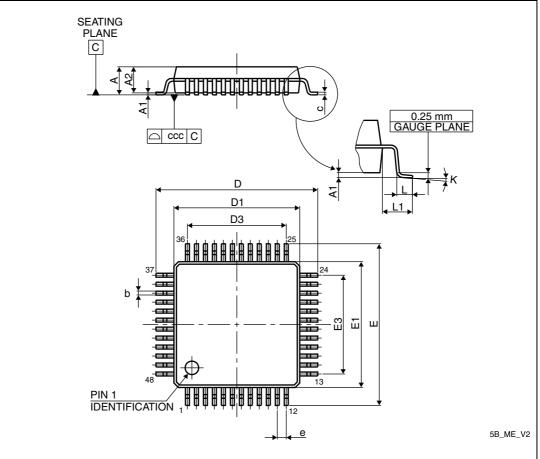

### 7.3 LQFP48 package information

LQFP48 is a 48-pin, 7 x 7mm low-profile quad flat package.

Figure 36. LQFP48 package outline

1. Drawing is not to scale.

Table 76. LQFP48 package mechanical data

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

|        | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| А      | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543                | 0.3622 |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756                | 0.2835 |

| D3     | -     | 5.500       | -     | -      | 0.2165                | -      |

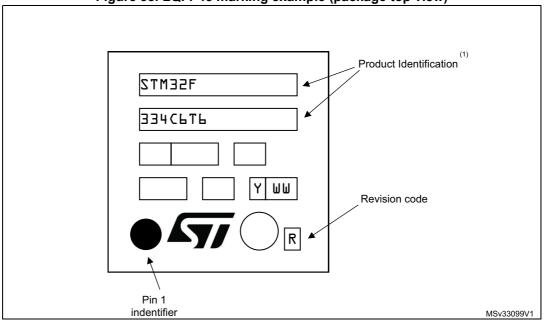

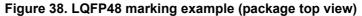

#### **Device marking for LQFP48**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### **Device marking for LQFP64**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### 7.5 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub> max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$P_{I/O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                      | Value  | Unit |

|-----------------|--------------------------------------------------------------------------------|--------|------|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch      | 45°C/W | °C/W |

| Θ <sub>JA</sub> | <b>Thermal resistance junction-ambient</b><br>LQFP48 - 7 × 7 mm / 0.5 mm pitch | 55°C/W | °C/W |

| $\Theta_{JA}$   | <b>Thermal resistance junction-ambient</b><br>LQFP32 - 7 × 7 mm / 0.8 mm pitch | 60°C/W | °C/W |

#### 7.5.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

#### 7.5.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Table 79: Ordering information scheme*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F334x4/6/8 at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

## 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19-Jun-2014 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 09-Dec-2014 | 2        | Updated:<br>Table 54: TIMx characteristics<br>Table 14: STM32F303x6/8 pin definitions<br>Table 59: ADC characteristics<br>Table 34: Peripheral current consumption<br>Table 40: HSI oscillator characteristics<br>Table 17: HSI oscillator accuracy characterization results for<br>soldered parts<br>Table 2: STM32F334x4/6/8 family device features and<br>peripheral counts                                                                                                                                      |

| 2-Feb-2015  | 3        | Updated:<br>Figure 1: STM32F334x4/6/8 block diagram<br>Table 38: HSE oscillator characteristics<br>Table 43: Flash memory characteristics<br>Added Figure 13: High-speed external clock source AC timing<br>diagram                                                                                                                                                                                                                                                                                                 |

| 09-Jun-2015 | 4        | Udpated :<br>Title<br>Section 3.14.1: 217 ps high-resolution timer (HRTIM1)<br>Section 6.1.6: Power-supply scheme<br>Table 19: General operating conditions                                                                                                                                                                                                                                                                                                                                                         |

| 27-Sep-2016 | 5        | Updated:<br>Section Table 69.: DAC characteristics, Section Table 64.:<br>ADC characteristics, Table 53: NRST pin characteristics,<br>Figure 2: Clock tree, Table 13: STM32F334x4/6/8 pin<br>definitions, Table 71: Operational amplifier characteristics,<br>Figure 20: Five volt tolerant (FT and FTf) I/O input<br>characteristics - CMOS port, Table 23: Embedded internal<br>reference voltage, Table 39: LSE oscillator characteristics<br>(fLSE = 32.768 kHz)<br>Added:<br>Table 35: Wakeup time using USART |

#### Table 80. Document revision history

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID025409 Rev 5