Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 1MB (341.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj1024ga606-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC24FJ1024GA610/GB610 FAMILY PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. Their pinout diagrams appear on the following pages.

|                  | Mem                | ory             | Pi    | ns  | A                  | nalo       | g    |                 |            |           | Dig              | ital |                          |           |     |      |         |

|------------------|--------------------|-----------------|-------|-----|--------------------|------------|------|-----------------|------------|-----------|------------------|------|--------------------------|-----------|-----|------|---------|

| Device           | Program<br>(bytes) | Data<br>(bytes) | Total | 0/1 | 10/12-Bit A/D (ch) | Comparator | CTMU | 16/32-Bit Timer | IC/OC/PWIM | MCCP/SCCP | I <sup>2</sup> C | IdS  | UART w/IrDA <sup>®</sup> | EPMP/EPSP | СГС | RTCC | USB OTG |

| PIC24FJ128GA606  | 128K               | 32K             | 64    | 53  | 16                 | 3          | Y    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Ν       |

| PIC24FJ256GA606  | 256K               | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Ν       |

| PIC24FJ512GA606  | 512K               | 32K             | 64    | 53  | 16                 | 3          | Y    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Ν       |

| PIC24FJ1024GA606 | 1024K              | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Y    | Ν       |

| PIC24FJ128GA610  | 128K               | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Υ    | Ν       |

| PIC24FJ256GA610  | 256K               | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Υ    | Ν       |

| PIC24FJ512GA610  | 512K               | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Ν       |

| PIC24FJ1024GA610 | 1024K              | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Ν       |

| PIC24FJ128GB606  | 128K               | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Υ       |

| PIC24FJ256GB606  | 256K               | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Υ       |

| PIC24FJ512GB606  | 512K               | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Υ       |

| PIC24FJ1024GB606 | 1024K              | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Υ       |

| PIC24FJ128GB610  | 128K               | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Y       |

| PIC24FJ256GB610  | 256K               | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Υ       |

| PIC24FJ512GB610  | 512K               | 32K             | 100   | 85  | 24                 | 3          | Y    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Y       |

| PIC24FJ1024GB610 | 1024K              | 32K             | 100   | 85  | 24                 | 3          | Y    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Y    | Y       |

## TABLE 1: PIC24FJ1024GA610/GB610 GENERAL PURPOSE FAMILIES

## TABLE 6: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJXXXGA610 BGA) (CONTINUED)

| Pin | Full Pin Name                               | Pin | Full Pin Name                         |

|-----|---------------------------------------------|-----|---------------------------------------|

| J1  | AN3/C2INA/RB3                               | K7  | AN14/RP14/CTED5/CTPLS/PMA1/PMALH/RB14 |

| J2  | AN2/CTCMP/C2INB/RP13/CTED13/RB2             | K8  | VDD                                   |

| J3  | PGED2/AN7/ <b>RP7</b> /U6TX/RB7             | K9  | RP5/RD15                              |

| J4  | AVDD                                        | K10 | RP16/RF3                              |

| J5  | AN11/REFI/PMA12/RB11                        | K11 | RP30/RF2                              |

| J6  | TCK/RA1                                     | L1  | PGEC2/AN6/ <b>RP6</b> /RB6            |

| J7  | AN12/U6RX/CTED2/PMA11/RB12                  | L2  | CVREF-/VREF-/PMA7/RA9                 |

| J8  | N/C                                         | L3  | AVss                                  |

| J9  | N/C                                         | L4  | AN9/TMPR/RP9/T1CK/RB9                 |

| J10 | RP15/RF8                                    | L5  | CVREF/AN10/PMA13/RB10                 |

| J11 | SDA1/RG3                                    | L6  | RP31/RF13                             |

| K1  | PGEC1/ALTCVREF-/ALTVREF-/AN1/RP1/CTED12/RB1 | L7  | AN13/CTED1/PMA10/RB13                 |

| K2  | PGED1/ALTCVREF+/ALTVREF+/AN0/RP0/RB0        | L8  | AN15/RP29/CTED6/PMA0/PMALL/RB15       |

| K3  | CVREF+/VREF+/PMA6/RA10                      | L9  | RPI43/RD14                            |

| K4  | AN8/ <b>RP8</b> /PWRGT/RB8                  | L10 | RP10/PMA9/RF4                         |

| K5  | N/C                                         | L11 | RP17/PMA8/RF5                         |

| K6  | RPI32/CTED7/PMA18/RF12                      |     |                                       |

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select (PPS) functions.

**Note:** Pinouts are subject to change.

| File Name     | Address           | All Resets | File Name        | Address          | All Resets     |  |

|---------------|-------------------|------------|------------------|------------------|----------------|--|

| SINGLE OUTPUT | CAPTURE/COMPARE/P | WM         | SINGLE OUTPUT CA | APTURE/COMPARE/F | WM (CONTINUED) |  |

| CCP4CON1L     | 0300              | 0000       | CCP6STATH        | 0356             | 0000           |  |

| CCP4CON1H     | 0302              | 0000       | CCP6TMRL         | 0358             | 0000           |  |

| CCP4CON2L     | 0304              | 0000       | CCP6TMRH         | 035A             | 0000           |  |

| CCP4CON2H     | 0306              | 0100       | CCP6PRL          | 035C             | FFFF           |  |

| CCP4CON3L     | 0308              | 0000       | CCP6PRH          | 035E             | FFFF           |  |

| CCP4CON3H     | 030A              | 0000       | CCP6RAL          | 0360             | 0000           |  |

| CCP4STATL     | 030C              | 00x0       | CCP6RAH          | 0362             | 0000           |  |

| CCP4STATH     | 030E              | 0000       | CCP6RBL          | 0364             | 0000           |  |

| CCP4TMRL      | 0310              | 0000       | CCP6RBH          | 0366             | 0000           |  |

| CCP4TMRH      | 0312              | 0000       | CCP6BUFL         | 0368             | 0000           |  |

| CCP4PRL       | 0314              | FFFF       | CCP6BUFH         | 036A             | 0000           |  |

| CCP4PRH       | 0316              | FFFF       | CCP7CON1L        | 036C             | 0000           |  |

| CCP4RAL       | 0318              | 0000       | CCP7CON1H        | 036E             | 0000           |  |

| CCP4RAH       | 031A              | 0000       | CCP7CON2L        | 0370             | 0000           |  |

| CCP4RBL       | 031C              | 0000       | CCP7CON2H        | 0372             | 0100           |  |

| CCP4RBH       | 031E              | 0000       | CCP7CON3L        | 0374             | 0000           |  |

| CCP4BUFL      | 0320              | 0000       | CCP7CON3H        | 0376             | 0000           |  |

| CCP4BUFH      | 0322              | 0000       | CCP7STATL        | 0378             | 00x0           |  |

| CCP5CON1L     | 0324              | 0000       | CCP7STATH        | 037A             | 0000           |  |

| CCP5CON1H     | 0326              | 0000       | CCP7TMRL         | 037C             | 0000           |  |

| CCP5CON2L     | 0328              | 0000       | CCP7TMRH         | 037E             | 0000           |  |

| CCP5CON2H     | 032A              | 0100       | CCP7PRL          | 0380             | FFFF           |  |

| CCP5CON3L     | 032C              | 0000       | CCP7PRH          | 0382             | FFFF           |  |

| CCP5CON3H     | 032E              | 0000       | CCP7RAL          | 0384             | 0000           |  |

| CCP5STATL     | 0330              | 00x0       | CCP7RAH          | 0386             | 0000           |  |

| CCP5STATH     | 0332              | 0000       | CCP7RBL          | 0388             | 0000           |  |

| CCP5TMRL      | 0334              | 0000       | CCP7RBH          | 038A             | 0000           |  |

| CCP5TMRH      | 0336              | 0000       | CCP7BUFL         | 038C             | 0000           |  |

| CCP5PRL       | 0338              | FFFF       | CCP7BUFH         | 038E             | 0000           |  |

| CCP5PRH       | 033A              | FFFF       | UART             | 0002             |                |  |

| CCP5RAL       | 033C              | 0000       | U1MODE           | 0398             | 0000           |  |

| CCP5RAH       | 033E              | 0000       | U1STA            | 039A             | 0110           |  |

| CCP5RBL       | 0340              | 0000       | U1TXREG          | 039C             | x0xx           |  |

| CCP5RBH       | 0342              | 0000       | U1RXREG          | 039E             | 0000           |  |

| CCP5BUFL      | 0344              | 0000       | U1BRG            | 03A0             | 0000           |  |

| CCP5BUFH      | 0346              | 0000       | U1ADMD           | 03A2             | 0000           |  |

| CCP6CON1L     | 0348              | 0000       | U2MODE           | 03AE             | 0000           |  |

| CCP6CON1H     | 034A              | 0000       | U2STA 03B0       |                  | 0110           |  |

| CCP6CON2L     | 034C              | 0000       | U2TXREG 03B2     |                  | xxxx           |  |

| CCP6CON2H     | 034E              | 0100       | U2RXREG 03B4     |                  | 0000           |  |

| CCP6CON3L     | 0350              | 0000       | U2BRG 03B6       |                  | 0000           |  |

| CCP6CON3H     | 0352              | 0000       | U2ADMD           | 03B8             | 0000           |  |

| CCP6STATL     | 0354              | 00x0       | U3MODE           | 03C4             | 0000           |  |

#### TABLE 4-7: SFR MAP: 0300h BLOCK

Legend: — = unimplemented, read as '0'; x = undefined. Reset values are shown in hexadecimal.

| REGISTER            |                                                                                                               |                                                                                                               |                                                                                                    |                                |                  |                             |                  |

|---------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------|------------------|-----------------------------|------------------|

| R/W-0               | R/W-0                                                                                                         | R/W-1                                                                                                         | R/W-1                                                                                              | R/W-0                          | R/W-0            | R/W-0                       | R/W-0            |

| ROI                 | DOZE2                                                                                                         | DOZE1                                                                                                         | DOZE0                                                                                              | DOZEN <sup>(1)</sup>           | RCDIV2           | RCDIV1                      | RCDIV0           |

| bit 15              |                                                                                                               |                                                                                                               |                                                                                                    |                                |                  |                             | bit 8            |

| R/W-0               | R/W-0                                                                                                         | R/W-0                                                                                                         | U-0                                                                                                | U-0                            | U-0              | U-0                         | U-0              |

| CPDIV1              | CPDIV0                                                                                                        | PLLEN                                                                                                         | 0-0                                                                                                | 0-0                            | 0-0              |                             |                  |

| bit 7               | CFDIVU                                                                                                        | FLLEIN                                                                                                        | _                                                                                                  | —                              |                  | —                           | <br>bit 0        |

|                     |                                                                                                               |                                                                                                               |                                                                                                    |                                |                  |                             |                  |

| Legend:             |                                                                                                               |                                                                                                               |                                                                                                    |                                |                  |                             |                  |

| R = Readab          | le bit                                                                                                        | W = Writable                                                                                                  | bit                                                                                                | U = Unimplem                   | nented bit, read | d as '0'                    |                  |

| -n = Value a        | t POR                                                                                                         | '1' = Bit is set                                                                                              |                                                                                                    | '0' = Bit is clea              | ared             | x = Bit is unkr             | nown             |

| bit 15<br>bit 14-12 | 1 = Interrupts<br>0 = Interrupts                                                                              | have no effect                                                                                                |                                                                                                    |                                | pheral clock ra  | itio to 1:1                 |                  |

|                     | 111 = 1:128<br>110 = 1:64<br>101 = 1:32<br>100 = 1:16<br>011 = 1:8 (de<br>010 = 1:4<br>001 = 1:2<br>000 = 1:1 | fault)                                                                                                        |                                                                                                    |                                |                  |                             |                  |

| bit 11              | 1 = DOZE<2                                                                                                    |                                                                                                               | the CPU perip<br>tio is set to 1:1                                                                 | oheral clock ration            | D                |                             |                  |

| bit 10-8            | •                                                                                                             | -                                                                                                             |                                                                                                    | lock Source Se                 | lect hits        |                             |                  |

|                     | 000 = Fast R<br>001 = Fast R<br>010 = Primar<br>011 = Primar<br>100 = Second<br>101 = Low-Pe<br>110 = Digital | C Oscillator (F<br>C Oscillator (F<br>y Oscillator (X<br>y Oscillator (X<br>dary Oscillator<br>ower RC Oscill | RC)<br>RC) with PLL n<br>r, HS, EC)<br>r, HS, EC) with<br>(SOSC)<br>ator (LPRC)<br>scillator (DCO) | nodule (FRCPL<br>PLL module (X | L)               | , ECPLL)                    |                  |

| bit 7-6             | 11 = 4 MHz (<br>10 = 8 MHz (<br>01 = 16 MHz<br>00 = 32 MHz                                                    | divide-by-8) <sup>(2)</sup><br>divide-by-4) <sup>(2)</sup><br>(divide-by-2)<br>(divide-by-1)                  | ŭ                                                                                                  | stscaler select                | from 96 MHz F    | PLL, 32 MHz clo             | ock branch)      |

| bit 5               | 1 = PLL is alw<br>0 = PLL is on                                                                               | ly active when                                                                                                | a PLL Oscillato                                                                                    | or mode is seled               | cted (OSCCON     | <b>J&lt;14:12&gt; =</b> 011 | L <b>or</b> 001) |

| bit 4-0             | Unimplemen                                                                                                    | ted: Read as '                                                                                                | 0'                                                                                                 |                                |                  |                             |                  |

|                     | his bit is automa<br>his setting is not                                                                       | -                                                                                                             |                                                                                                    |                                | n interrupt occu | Irs.                        |                  |

## REGISTER 9-2: CLKDIV: CLOCK DIVIDER REGISTER

## 9.8 Secondary Oscillator

## 9.8.1 BASIC SOSC OPERATION

PIC24FJ1024GA610/GB610 family devices do not have to set the SOSCEN bit to use the Secondary Oscillator. Any module requiring the SOSC (such as RTCC or Timer1) will automatically turn on the SOSC when the clock signal is needed. The SOSC, however, has a long start-up time (as long as 1 second). To avoid delays for peripheral start-up, the SOSC can be manually started using the SOSCEN bit.

To use the Secondary Oscillator, the SOSCSEL bit (FOSC<3>) must be set to '1'. Programming the SOSCSEL bit to '0' configures the SOSC pins for Digital mode, enabling digital I/O functionality on the pins.

## 9.8.2 CRYSTAL SELECTION

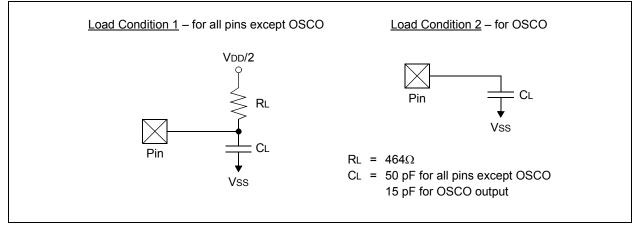

The 32.768 kHz crystal used for the SOSC must have the following specifications in order to properly start up and run at the correct frequency when in High-Power mode:

- 12.5 pF loading capacitance

- 1.0 pF shunt capacitance

- A typical ESR of 35K; 50K maximum

In addition, the two external crystal loading capacitors should be in the range of 18-22 pF, which will be based on the PC board layout. The capacitors should be COG, 5% tolerance and rated 25V or greater.

The accuracy and duty cycle of the SOSC can be measured on the REFO pin, and is recommended to be in the range of 40-60% and accurate to  $\pm 0.65$  Hz.

## 9.8.3 LOW-POWER SOSC OPERATION

The Secondary Oscillator can operate in two distinct levels of power consumption based on device configuration. In Low-Power mode, the oscillator operates in a low drive strength, low-power state. By default, the oscillator uses a higher drive strength, and therefore, requires more power. Low-Power mode is selected by Configuration bit, SOSCHP (FDEVOPT1<3>). The lower drive strength of this mode makes the SOSC more sensitive to noise and requires a longer start-up time. This mode can be used with lower load capacitance crystals (6 pF-9 pF) having higher ESR ratings (50K-80K) to reduce Sleep current in the RTCC. When Low-Power mode is used, care must be taken in the design and layout of the SOSC circuit to ensure that the oscillator starts up and oscillates properly. PC board layout issues, stray capacitance and other factors will need to be carefully controlled in order for the crystal to operate.

## 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:256, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

## 10.4 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMD Control registers.

Both bits have similar functions in enabling or disabling their associated module. Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect and read values will be invalid. Many peripheral modules have a corresponding PMD bit.

In contrast, disabling a module by clearing its XXXEN bit disables its functionality, but leaves its registers available to be read and written to. This reduces power consumption, but not by as much as setting the PMD bit does. Most peripheral modules have an enable bit; exceptions include input capture, output compare and RTCC.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature allows further reduction of power consumption during Idle mode, enhancing power savings for extremely critical power applications. NOTES:

# PIC24FJ1024GA610/GB610 FAMILY

| U-0          | U-0          | U-0                                                                                                                             | R/W-0                                | R/W-0                               | U-0             | U-0             | R/W-0    |  |  |  |  |  |  |  |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------|-----------------|-----------------|----------|--|--|--|--|--|--|--|

| _            | _            | _                                                                                                                               | FRMERREN                             | BUSYEN                              | _               | _               | SPITUREN |  |  |  |  |  |  |  |

| bit 15       |              |                                                                                                                                 |                                      |                                     |                 |                 | bit 8    |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

| R/W-0        | R/W-0        | R/W-0                                                                                                                           | U-0                                  | R/W-0                               | U-0             | R/W-0           | R/W-0    |  |  |  |  |  |  |  |

| SRMTEN       | SPIROVEN     | SPIRBEN                                                                                                                         | —                                    | SPITBEN                             | —               | SPITBFEN        | SPIRBFEN |  |  |  |  |  |  |  |

| bit 7        |              |                                                                                                                                 |                                      |                                     |                 |                 | bit 0    |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

| Legend:      |              |                                                                                                                                 |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

| R = Readab   | ole bit      | W = Writable b                                                                                                                  | it                                   | U = Unimpleme                       | ented bit, read | as '0'          |          |  |  |  |  |  |  |  |

| -n = Value a | at POR       | '1' = Bit is set                                                                                                                |                                      | '0' = Bit is clear                  | red             | x = Bit is unkr | nown     |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

| bit 15-13    | Unimplemer   | nted: Read as '                                                                                                                 | )'                                   |                                     |                 |                 |          |  |  |  |  |  |  |  |

| bit 12       |              |                                                                                                                                 | pt Events via FF                     |                                     |                 |                 |          |  |  |  |  |  |  |  |

|              |              | <ul> <li>= Frame error generates an interrupt event</li> <li>&gt; = Frame error does not generate an interrupt event</li> </ul> |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

| bit 11       |              | ) = Frame error does not generate an interrupt event<br>BUSYEN: Enable Interrupt Events via SPIBUSY bit                         |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

|              |              | = SPIBUSY generates an interrupt event                                                                                          |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

|              |              | . = SPIBUSY generates an interrupt event<br>= SPIBUSY does not generate an interrupt event                                      |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

| bit 10-9     | Unimplemer   | Jnimplemented: Read as '0'                                                                                                      |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

| bit 8        | SPITUREN:    | Enable Interrup                                                                                                                 | t Events via SPI                     | TUR bit                             |                 |                 |          |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 | ) generates an i                     |                                     |                 |                 |          |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 | -                                    | n interrupt event                   |                 |                 |          |  |  |  |  |  |  |  |

| bit 7        |              |                                                                                                                                 | Events via SRM                       |                                     |                 |                 |          |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 |                                      | interrupt events interrupt events   |                 |                 |          |  |  |  |  |  |  |  |

| bit 6        | -            |                                                                                                                                 | t Events via SPI                     | -                                   |                 |                 |          |  |  |  |  |  |  |  |

|              |              | •                                                                                                                               | enerates an inte                     |                                     |                 |                 |          |  |  |  |  |  |  |  |

|              | 0 = SPIx Red | ceive Overflow of                                                                                                               | loes not genera                      | te an interrupt ev                  | vent            |                 |          |  |  |  |  |  |  |  |

| bit 5        |              |                                                                                                                                 | Events via SPIR                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 | enerates an inte                     |                                     |                 |                 |          |  |  |  |  |  |  |  |

| bit 4        |              | nted: Read as '                                                                                                                 |                                      | e an interrupt ev                   | ent             |                 |          |  |  |  |  |  |  |  |

|              | -            |                                                                                                                                 |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

| bit 3        |              | •                                                                                                                               | Events via SPITI                     | n interrupt event                   | ŀ               |                 |          |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 |                                      | nerate an interru                   |                 |                 |          |  |  |  |  |  |  |  |

| bit 2        | Unimplemer   | nted: Read as '                                                                                                                 | )'                                   |                                     | -               |                 |          |  |  |  |  |  |  |  |

| bit 1        | SPITBFEN:    | Enable Interrupt                                                                                                                | Events via SPI                       | TBF bit                             |                 |                 |          |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 | l generates an i<br>l does not gener | nterrupt event<br>rate an interrupt | event           |                 |          |  |  |  |  |  |  |  |

| bit 0        |              |                                                                                                                                 | t Events via SPI                     | -                                   | 0.0m            |                 |          |  |  |  |  |  |  |  |

| 2100         |              | •                                                                                                                               | generates an ir                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 |                                      | ate an interrupt e                  | event           |                 |          |  |  |  |  |  |  |  |

|              |              |                                                                                                                                 |                                      |                                     |                 |                 |          |  |  |  |  |  |  |  |

## REGISTER 17-9: SPIXIMSKL: SPIX INTERRUPT MASK REGISTER LOW

#### 20.5.2 COMPLETE A CONTROL TRANSACTION TO A CONNECTED DEVICE

- 1. Follow the procedure described in Section 20.5.1 "Enable Host Mode and Discover a Connected Device" to discover a device.

- Set up the Endpoint Control register for bidirectional control transfers by writing 0Dh to U1EP0 (this sets the EPCONDIS, EPTXEN and EPHSHK bits).

- 3. Place a copy of the device framework setup command in a memory buffer. See Chapter 9 of the *"USB 2.0 Specification"* for information on the device framework command set.

- Initialize the Buffer Descriptor (BD) for the current (even or odd) TX EP0 to transfer the eight bytes of command data for a device framework command (i.e., GET DEVICE DESCRIPTOR):

- a) Set the BD Data Buffer Address (BD0ADR) to the starting address of the 8-byte memory buffer containing the command.

- b) Write 8008h to BD0STAT (this sets the UOWN bit and sets a byte count of 8).

- Set the USB device address of the target device in the address register (U1ADDR<6:0>). After a USB bus Reset, the device USB address will be zero. After enumeration, it will be set to another value between 1 and 127.

- 6. Write D0h to U1TOK; this is a SETUP token to Endpoint 0, the target device's default control pipe. This initiates a SETUP token on the bus, followed by a data packet. The device handshake is returned in the PID field of BD0STAT after the packets are complete. When the USB module updates BD0STAT, a Token Complete Interrupt Flag is asserted (the TRNIF flag is set). This completes the setup phase of the setup transaction, as referenced in Chapter 9 of the "USB 2.0 Specification".

- 7. To initiate the data phase of the setup transaction (i.e., get the data for the GET DEVICE DESCRIPTOR command), set up a buffer in memory to store the received data.

- 8. Initialize the current (even or odd) RX or TX (RX for IN, TX for OUT) EP0 BD to transfer the data.

- a) Write C040h to BD0STAT. This sets the UOWN, configures the Data Toggle bit (DTS) to DATA1 and sets the byte count to the length of the data buffer (64 or 40h in this case).

- b) Set BD0ADR to the starting address of the data buffer.

- 9. Write the Token register with the appropriate IN or OUT token to Endpoint 0, the target device's default control pipe (e.g., write 90h to U1TOK for an IN token for a GET DEVICE DESCRIPTOR command). This initiates an IN token on the bus, followed by a data packet from the device to the host. When the data packet completes, the BD0STAT is written and a Token Complete Interrupt Flag is asserted (the TRNIF flag is set). For control transfers with a single packet data phase, this completes the data phase of the setup transaction, as referenced in Chapter 9 of the "USB 2.0 Specification". If more data needs to be transferred, return to Step 8.

- 10. To initiate the status phase of the setup transaction, set up a buffer in memory to receive or send the zero length status phase data packet.

- 11. Initialize the current (even or odd) TX EP0 BD to transfer the status data:

- a) Set the BDT buffer address field to the start address of the data buffer.

- b) Write 8000h to BD0STAT (set UOWN bit, configure DTS to DATA0 and set byte count to 0).

- 12. Write the Token register with the appropriate IN or OUT token to Endpoint 0, the target device's default control pipe (e.g., write 01h to U1TOK for an OUT token for a GET DEVICE DESCRIPTOR command). This initiates an OUT token on the bus, followed by a zero length data packet from the host to the device. When the data packet completes, the BD is updated with the hand-shake from the device and a Token Complete Interrupt Flag is asserted (the TRNIF flag is set). This completes the status phase of the setup transaction, as described in Chapter 9 of the "USB 2.0 Specification".

**Note:** Only one control transaction can be performed per frame.

## REGISTER 20-16: U1IR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0           | U-0         | U-0                                        | U-0              | U-0               | U-0                 | U-0                | U-0                |

|---------------|-------------|--------------------------------------------|------------------|-------------------|---------------------|--------------------|--------------------|

| _             | —           |                                            | —                |                   |                     |                    | —                  |

| bit 15        |             |                                            |                  |                   |                     |                    | bit 8              |

|               |             |                                            |                  |                   |                     |                    |                    |

| R/K-0, HS     | U-0         | R/K-0, HS                                  | R/K-0, HS        | R/K-0, HS         | R/K-0, HS           | R/K-0, HS          | R/K-0, HS          |

| STALLIF       |             | RESUMEIF                                   | IDLEIF           | TRNIF             | SOFIF               | UERRIF             | URSTIF             |

| bit 7         |             |                                            |                  |                   |                     |                    | bit 0              |

|               |             |                                            |                  |                   |                     |                    |                    |

| Legend:       |             | U = Unimplem                               | ented bit, read  | d as '0'          |                     |                    |                    |

| R = Readabl   |             | K = Write '1' to                           | o Clear bit      | HS = Hardwa       | re Settable bit     |                    |                    |

| -n = Value at | POR         | '1' = Bit is set                           |                  | '0' = Bit is clea | ared                | x = Bit is unkr    | nown               |

|               |             |                                            |                  |                   |                     |                    |                    |

| bit 15-8      | Unimplem    | ented: Read as '0                          | )'               |                   |                     |                    |                    |

| bit 7         | STALLIF: S  | STALL Handshake                            | e Interrupt bit  |                   |                     |                    |                    |

|               |             | LL handshake wa                            | s sent by the p  | peripheral durin  | g the handshal      | ke phase of the    | transaction in     |

|               |             | e mode<br>LL handshake has                 | s not been sen   | ht.               |                     |                    |                    |

| bit 6         |             | ented: Read as '0                          |                  | it.               |                     |                    |                    |

| bit 5         | -           | -: Resume Interru                          |                  |                   |                     |                    |                    |

| Sit 0         |             | ate is observed on                         |                  | oin for 2.5 us (d | lifferential '1' fo | r low speed, dit   | fferential '0' for |

|               | full spe    |                                            |                  |                   |                     |                    |                    |

|               | 0 = No K-s  | state is observed                          |                  |                   |                     |                    |                    |

| bit 4         | IDLEIF: Idl | e Detect Interrupt                         | bit              |                   |                     |                    |                    |

|               |             | ndition is detected<br>e condition is dete | •                | e state of 3 ms   | or more)            |                    |                    |

| bit 3         |             | e condition is dete                        |                  | unt hit           |                     |                    |                    |

| DIL 3         |             | ssing of the curren                        | -                | -                 | LI1STAT regist      | er for endpoint    | information        |

|               |             | ssing of the curren                        |                  |                   |                     |                    |                    |

|               |             | TAT (clearing this                         |                  |                   |                     | -                  |                    |

| bit 2         |             | rt-of-Frame Toker                          | •                |                   |                     |                    |                    |

|               |             | -of-Frame token is                         | s received by t  | he peripheral c   | or the Start-of-F   | rame threshold     | l is reached by    |

|               | the hos     | st<br>ırt-of-Frame token                   | is received or   | threshold read    | bed                 |                    |                    |

| bit 1         |             | ISB Error Conditio                         |                  |                   | neu                 |                    |                    |

| bit 1         |             | masked error cond                          |                  |                   | states enabled      | in the U1EIE r     | egister can set    |

|               | this bit    |                                            |                  | field, only error |                     |                    | egiotor our cor    |

|               | 0 = No unr  | masked error cond                          | dition has occu  | ırred             |                     |                    |                    |

| bit 0         | URSTIF: U   | SB Reset Interrup                          | ot bit           |                   |                     |                    |                    |

|               |             | JSB Reset has oc                           | curred for at le | east 2.5 μs; Re   | set state must      | be cleared before  | ore this bit can   |

|               |             | sserted<br>B Reset has occu                | urred: individua | al hite can only  | be cleared by       | writing a '1' to t | the hit position   |

|               |             | t of a word write of                       |                  | -                 | -                   | -                  |                    |

|               |             | to write to a single                       |                  |                   |                     |                    |                    |

|               | cleared     | d                                          |                  |                   |                     |                    |                    |

|               |             |                                            |                  |                   |                     |                    |                    |

|               |             | can only be cleare                         |                  |                   |                     |                    |                    |

|               | -           | Using Boolean in                           |                  |                   |                     |                    | uon wiii Cause     |

NOTES:

## REGISTER 21-8: PMSTAT: EPMP STATUS REGISTER (SLAVE MODE ONLY)

| R-0, HSC        | R/W-0, HS                                                                             | U-0                                                      | U-0                           | R-0, HSC                            | R-0, HSC            | R-0, HSC            | R-0, HSC            |

|-----------------|---------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|-------------------------------------|---------------------|---------------------|---------------------|

| IBF             | IBOV                                                                                  | —                                                        | —                             | IB3F <sup>(1)</sup>                 | IB2F <sup>(1)</sup> | IB1F <sup>(1)</sup> | IB0F <sup>(1)</sup> |

| bit 15          |                                                                                       |                                                          |                               |                                     |                     | •                   | bit 8               |

| <b>D</b> ( 1100 |                                                                                       |                                                          |                               | <u> </u>                            |                     | <b>D</b> ( 1100     |                     |

| R-1, HSC        | R/W-0, HS                                                                             | U-0                                                      | U-0                           | R-1, HSC                            | R-1, HSC            | R-1, HSC            | R-1, HSC            |

| OBE             | OBUF                                                                                  | —                                                        | _                             | OB3E                                | OB2E                | OB1E                | OB0E                |

| bit 7           |                                                                                       |                                                          |                               |                                     |                     |                     | bit                 |

| Legend:         |                                                                                       | HS = Hardware                                            | e Settable bit                | HSC = Hardw                         | are Settable/C      | learable bit        |                     |

| R = Readable    | e bit                                                                                 | W = Writable b                                           | oit                           | U = Unimplem                        | nented bit, read    | l as '0'            |                     |

| -n = Value at   | POR                                                                                   | '1' = Bit is set                                         |                               | '0' = Bit is clea                   | ared                | x = Bit is unkr     | nown                |

| bit 14          | <ul> <li>0 = Some or</li> <li><b>IBOV:</b> Input B</li> <li>1 = A write at</li> </ul> | Buffer Overflow Stempt to a full li                      | le Input Buffer<br>Status bit | registers are er<br>ccurred (must b |                     | oftware)            |                     |

|                 | 0 = No overfl                                                                         |                                                          |                               |                                     |                     |                     |                     |

| bit 13-12       | •                                                                                     | ted: Read as '0                                          |                               |                                     |                     |                     |                     |

| bit 11-8        | 1 = Input buff                                                                        | put Buffer x Sta<br>fer contains unr<br>fer does not cor | ead data (read                | ling the buffer w                   | ill clear this bit  | )                   |                     |

| bit 7           | 1 = All readal                                                                        | Buffer Empty Sible Output Buffer all of the readal       | er registers are              | empty<br>fer registers are          | full                |                     |                     |

| bit 6           | OBUF: Output                                                                          | ıt Buffer Underfl                                        | ow Status bit                 |                                     |                     |                     |                     |

|                 | 1 = A read or<br>0 = No under                                                         |                                                          | empty Output                  | Buffer register                     | (must be cleare     | ed in software)     |                     |

| bit 5-4         | Unimplemen                                                                            | ted: Read as '0                                          | ,                             |                                     |                     |                     |                     |

| h:+ 0 0         | -                                                                                     | Output Buffer >                                          |                               | ' bit                               |                     |                     |                     |

| bit 3-0         |                                                                                       | •                                                        |                               |                                     | clear this bit)     |                     |                     |

**Note 1:** Even though an individual bit represents the byte in the buffer, the bits corresponding to the word (Byte 0 and 1, or Byte 2 and 3) get cleared, even on byte reading.

NOTES:

## 22.3 Registers

22.3.1 RTCC CONTROL REGISTERS

### REGISTER 22-1: RTCCON1L: RTCC CONTROL REGISTER 1 (LOW)

| R/W-0         | U-0                                                                                                       | U-0                                                         | U-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|--|--|--|

| RTCEN         | —                                                                                                         | —                                                           | —               | WRLOCK            | PWCEN            | PWCPOL          | PWCPOE |  |  |  |  |  |  |  |  |

| bit 15        |                                                                                                           |                                                             |                 |                   |                  |                 | bit 8  |  |  |  |  |  |  |  |  |

|               |                                                                                                           |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                     | R/W-0                                                       | R/W-0           | U-0               | U-0              | U-0             | R/W-0  |  |  |  |  |  |  |  |  |

| RTCOE         | OUTSEL2                                                                                                   | OUTSEL1                                                     | OUTSEL0         | —                 | —                | _               | TSAEN  |  |  |  |  |  |  |  |  |

| bit 7         |                                                                                                           |                                                             |                 |                   |                  |                 | bit 0  |  |  |  |  |  |  |  |  |

|               |                                                                                                           |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| Legend:       |                                                                                                           |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                     | W = Writable                                                | bit             | U = Unimplen      | nented bit, read | 1 as '0'        |        |  |  |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                       | '1' = Bit is set                                            |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |  |  |  |  |  |  |  |  |

|               |                                                                                                           |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| bit 15        | RTCEN: RTC                                                                                                | C Enable bit                                                |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               | 1 = RTCC is e                                                                                             | enabled and co                                              | unts from sele  | cted clock sour   | ce               |                 |        |  |  |  |  |  |  |  |  |

|               | 0 = RTCC is r                                                                                             |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| bit 14-12     | Unimplement                                                                                               | Unimplemented: Read as '0' WRLOCK: RTCC Register Write Lock |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| bit 11        |                                                                                                           | WRLOCK: RTCC Register Write Lock                            |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               | •                                                                                                         | 1 = RTCC registers are locked                               |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               | <ul> <li>0 = RTCC registers may be written to by user</li> <li>PWCEN: Power Control Enable bit</li> </ul> |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| bit 10        |                                                                                                           |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               |                                                                                                           | ontrol is enableo<br>ontrol is disable                      |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| bit 9         |                                                                                                           | ower Control Po                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| bit o         |                                                                                                           | ntrol output is a                                           | -               |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               |                                                                                                           | ntrol output is a                                           |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| bit 8         | PWCPOE: Po                                                                                                | ower Control O                                              | utput Enable bi | it                |                  |                 |        |  |  |  |  |  |  |  |  |

|               | 1 = Power cor                                                                                             | ntrol output pin                                            | is enabled      |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               | 0 = Power cor                                                                                             | ntrol output pin                                            | is disabled     |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| bit 7         |                                                                                                           | C Output Enab                                               | ole bit         |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               |                                                                                                           | put is enabled                                              |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               |                                                                                                           | put is disabled                                             |                 | 4:                |                  |                 |        |  |  |  |  |  |  |  |  |

| bit 6-4       | 111 = Unused                                                                                              | >: RTCC Outp                                                | ut Signal Selec | ction dits        |                  |                 |        |  |  |  |  |  |  |  |  |

|               | 111 = Unused<br>110 = Unused                                                                              |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               | 101 = Unused                                                                                              |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               | 100 <b>= Timest</b> a                                                                                     |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               | 011 = Power                                                                                               |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               | 010 = RTCC i<br>001 = Second                                                                              |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               | 000 = Alarm e                                                                                             |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| bit 3-1       | Unimplement                                                                                               | ted: Read as 'd                                             | )'              |                   |                  |                 |        |  |  |  |  |  |  |  |  |

| bit 0         | TSAEN: Time                                                                                               | stamp A Enabl                                               | e bit           |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               | 1 = Timestam                                                                                              | p event will occ                                            | our when a low  | pulse is detect   | ted on the TMF   | R pin           |        |  |  |  |  |  |  |  |  |

|               | 0 = Timestam                                                                                              | p is disabled                                               |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

|               |                                                                                                           |                                                             |                 |                   |                  |                 |        |  |  |  |  |  |  |  |  |

# PIC24FJ1024GA610/GB610 FAMILY

## **REGISTER 30-11: FDEVOPT1 CONFIGURATION REGISTER**

| Legend: |     | PO = Progran |         |                                 |         |         |           |

|---------|-----|--------------|---------|---------------------------------|---------|---------|-----------|

| bit 7   |     | _            | ALTVREF | SUSCHPUT                        | TMPRPIN | ALTCMPI | <br>bit 0 |

| U-1     | U-1 | U-1          | R/PO-1  | R/PO-1<br>SOSCHP <sup>(1)</sup> | R/PO-1  | R/PO-1  | U-1       |

| bit 15  |     |              |         |                                 |         |         | bit 8     |

|         |     | —            |         | —                               |         | —       | —         |

| U-1     | U-1 | U-1          | U-1     | U-1                             | U-1     | U-1     | U-1       |

| bit 23  |     |              |         |                                 |         |         | bit 16    |

| —       | —   | —            | —       | —                               | —       | —       | —         |

| U-1     | U-1 | U-1          | U-1     | U-1                             | U-1     | U-1     | U-1       |

| bit 4 | ALTVREF: Alternate Voltage Reference Location Enable bit (100-pin and 121-pin devices only)<br>1 = VREF+ and CVREF+ on RA10, VREF- and CVREF- on RA9<br>0 = VREF+ and CVREF+ on RB0, VREF- and CVREF- on RB1 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | <b>SOSCHP:</b> SOSC High-Power Enable bit (valid only when SOSCSEL = 1) <sup>(1)</sup>                                                                                                                       |

|       | 1 = SOSC High-Power mode is enabled<br>0 = SOSC Low-Power mode is enabled                                                                                                                                    |

| bit 2 | <b>TMPRPIN:</b> Tamper Pin Enable bit<br>1 = TMPR pin function is disabled                                                                                                                                   |

|       | 0 = TMPR pin function is enabled                                                                                                                                                                             |

| bit 1 | ALTCMPI: Alternate Comparator Input Enable bit                                                                                                                                                               |

|       | 1 = C1INC, C2INC and C3INC are on their standard pin locations                                                                                                                                               |