Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | PIC                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 32MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 1MB (341.5K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | •                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj1024ga606t-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |                                     | Pin Number/Grid Locator          |                                  |                                  |                         |                         |     |                 |                       |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|-----------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer | Description           |

| RD0             | 46                                  | 46                               | 72                               | 72                               | D9                      | D9                      | I/O | DIG/ST          | PORTD Digital I/Os    |

| RD1             | 49                                  | 49                               | 76                               | 76                               | A11                     | A11                     | I/O | DIG/ST          |                       |

| RD2             | 50                                  | 50                               | 77                               | 77                               | A10                     | A10                     | I/O | DIG/ST          |                       |

| RD3             | 51                                  | 51                               | 78                               | 78                               | B9                      | B9                      | I/O | DIG/ST          |                       |

| RD4             | 52                                  | 52                               | 81                               | 81                               | C8                      | C8                      | I/O | DIG/ST          |                       |

| RD5             | 53                                  | 53                               | 82                               | 82                               | B8                      | B8                      | I/O | DIG/ST          |                       |

| RD6             | 54                                  | 54                               | 83                               | 83                               | D7                      | D7                      | I/O | DIG/ST          |                       |

| RD7             | 55                                  | 55                               | 84                               | 84                               | C7                      | C7                      | I/O | DIG/ST          |                       |

| RD8             | 42                                  | 42                               | 68                               | 68                               | E9                      | E9                      | I/O | DIG/ST          |                       |

| RD9             | 43                                  | 43                               | 69                               | 69                               | E10                     | E10                     | I/O | DIG/ST          |                       |

| RD10            | 44                                  | 44                               | 70                               | 70                               | D11                     | D11                     | I/O | DIG/ST          |                       |

| RD11            | 45                                  | 45                               | 71                               | 71                               | C11                     | C11                     | I/O | DIG/ST          |                       |

| RD12            | —                                   | _                                | 79                               | 79                               | A9                      | A9                      | I/O | DIG/ST          |                       |

| RD13            | —                                   | _                                | 80                               | 80                               | D8                      | D8                      | I/O | DIG/ST          |                       |

| RD14            | —                                   | —                                | 47                               | 47                               | L9                      | L9                      | I/O | DIG/ST          |                       |

| RD15            | _                                   | _                                | 48                               | 48                               | K9                      | K9                      | I/O | DIG/ST          |                       |

| RE0             | 60                                  | 60                               | 93                               | 93                               | A4                      | A4                      | I/O | DIG/ST          | PORTE Digital I/Os    |

| RE1             | 61                                  | 61                               | 94                               | 94                               | B4                      | B4                      | I/O | DIG/ST          |                       |

| RE2             | 62                                  | 62                               | 98                               | 98                               | B3                      | B3                      | I/O | DIG/ST          |                       |

| RE3             | 63                                  | 63                               | 99                               | 99                               | A2                      | A2                      | I/O | DIG/ST          |                       |

| RE4             | 64                                  | 64                               | 100                              | 100                              | A1                      | A1                      | I/O | DIG/ST          |                       |

| RE5             | 1                                   | 1                                | 3                                | 3                                | D3                      | D3                      | I/O | DIG/ST          |                       |

| RE6             | 2                                   | 2                                | 4                                | 4                                | C1                      | C1                      | I/O | DIG/ST          |                       |

| RE7             | 3                                   | 3                                | 5                                | 5                                | D2                      | D2                      | I/O | DIG/ST          |                       |

| RE8             | _                                   | _                                | 18                               | 18                               | G1                      | G1                      | I/O | DIG/ST          |                       |

| RE9             | _                                   | —                                | 19                               | 19                               | G2                      | G2                      | I/O | DIG/ST          |                       |

| REFI            | 24                                  | 24                               | 35                               | 35                               | J5                      | J5                      | Ι   | ST              | Reference Clock Input |

### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

## 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 16V-50V capacitor is recommended. The capacitor should be a low-ESR device with a self-resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

## 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including microcontrollers to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

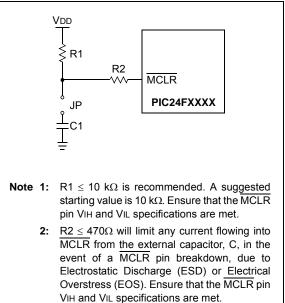

## 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

## FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

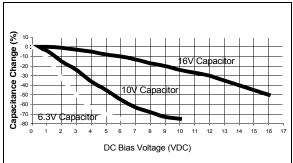

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R) or -20%/ +80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at a minimum of 16V for the 1.8V core voltage. Suggested capacitors are shown in Table 2-1.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" pins (i.e., PGECx/PGEDx), programmed into the device, match the physical connections for the ICSP to the Microchip debugger/ emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 31.0 "Development Support"**.

## 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

## 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and singlecycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

#### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE BIT AND MULTI-BIT SHIFT OPERATION

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic Shift Right Source register by one or more bits. |

| SL          | Shift Left Source register by one or more bits.             |

| LSR         | Logical Shift Right Source register by one or more bits.    |

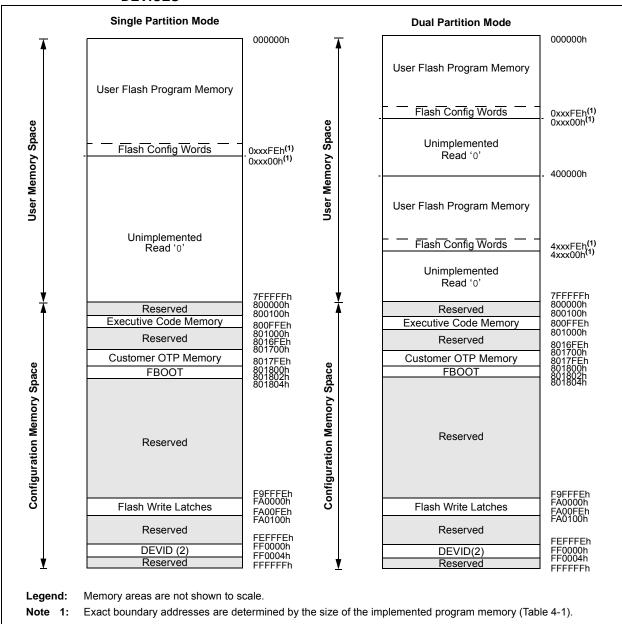

## FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FJ1024GA610/GB610 FAMILY DEVICES

## TABLE 4-1: PROGRAM MEMORY SIZES AND BOUNDARIES<sup>(1)</sup>

|                  | Program Memory   | y Upper Boundary ( |                    |                                |                                |

|------------------|------------------|--------------------|--------------------|--------------------------------|--------------------------------|

| Device           | Single Partition | Dual Part          | ition Mode         | Write<br>Blocks <sup>(2)</sup> | Erase<br>Blocks <sup>(2)</sup> |

|                  | Mode             | Active Partition   | Inactive Partition |                                |                                |

| PIC24FJ1024GX6XX | 0ABFFEh (352K)   | 055FFEh (176K)     | 455FFEh (176K)     | 2752                           | 344                            |

| PIC24FJ512GX6XX  | 055FFEh (176K)   | 02AFFEh (88k)      | 42AFFEh (88k)      | 1376                           | 172                            |

| PIC24FJ256GX6XX  | 02AFFEh (88K)    | 0157FEh (44k)      | 4157FEh (44k)      | 688                            | 86                             |

| PIC24FJ128GX6XX  | 015FFEh (44K)    | 00AFFEh (22k)      | 40AFFEh (22k)      | 352                            | 44                             |

Note 1: Includes Flash Configuration Words.

2: 1 Write Block = 128 Instruction Words; 1 Erase Block = 1024 Instruction Words.

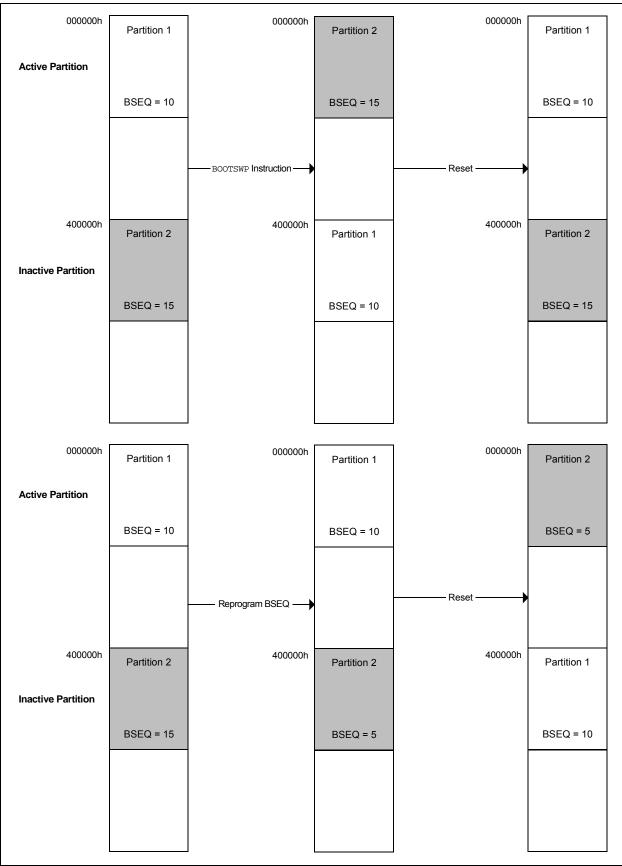

#### FIGURE 4-2: RELATIONSHIP BETWEEN PARTITIONS 1/2 AND ACTIVE/INACTIVE PARTITIONS

| File Name     | Address           | All Resets | File Name        | Address          | All Resets     |

|---------------|-------------------|------------|------------------|------------------|----------------|

| SINGLE OUTPUT | CAPTURE/COMPARE/P | WM         | SINGLE OUTPUT CA | APTURE/COMPARE/F | WM (CONTINUED) |

| CCP4CON1L     | 0300              | 0000       | CCP6STATH        | 0356             | 0000           |

| CCP4CON1H     | 0302              | 0000       | CCP6TMRL         | 0358             | 0000           |

| CCP4CON2L     | 0304              | 0000       | CCP6TMRH         | 035A             | 0000           |

| CCP4CON2H     | 0306              | 0100       | CCP6PRL          | 035C             | FFFF           |

| CCP4CON3L     | 0308              | 0000       | CCP6PRH          | 035E             | FFFF           |

| CCP4CON3H     | 030A              | 0000       | CCP6RAL          | 0360             | 0000           |

| CCP4STATL     | 030C              | 00x0       | CCP6RAH          | 0362             | 0000           |

| CCP4STATH     | 030E              | 0000       | CCP6RBL          | 0364             | 0000           |

| CCP4TMRL      | 0310              | 0000       | CCP6RBH          | 0366             | 0000           |

| CCP4TMRH      | 0312              | 0000       | CCP6BUFL         | 0368             | 0000           |

| CCP4PRL       | 0314              | FFFF       | CCP6BUFH         | 036A             | 0000           |

| CCP4PRH       | 0316              | FFFF       | CCP7CON1L        | 036C             | 0000           |

| CCP4RAL       | 0318              | 0000       | CCP7CON1H        | 036E             | 0000           |

| CCP4RAH       | 031A              | 0000       | CCP7CON2L        | 0370             | 0000           |

| CCP4RBL       | 031C              | 0000       | CCP7CON2H        | 0372             | 0100           |

| CCP4RBH       | 031E              | 0000       | CCP7CON3L        | 0374             | 0000           |

| CCP4BUFL      | 0320              | 0000       | CCP7CON3H        | 0376             | 0000           |

| CCP4BUFH      | 0322              | 0000       | CCP7STATL        | 0378             | 00x0           |

| CCP5CON1L     | 0324              | 0000       | CCP7STATH        | 037A             | 0000           |

| CCP5CON1H     | 0326              | 0000       | CCP7TMRL         | 037C             | 0000           |

| CCP5CON2L     | 0328              | 0000       | CCP7TMRH         | 037E             | 0000           |

| CCP5CON2H     | 032A              | 0100       | CCP7PRL          | 0380             | FFFF           |

| CCP5CON3L     | 032C              | 0000       | CCP7PRH          | 0382             | FFFF           |

| CCP5CON3H     | 032E              | 0000       | CCP7RAL          | 0384             | 0000           |

| CCP5STATL     | 0330              | 00x0       | CCP7RAH          | 0386             | 0000           |

| CCP5STATH     | 0332              | 0000       | CCP7RBL          | 0388             | 0000           |

| CCP5TMRL      | 0334              | 0000       | CCP7RBH          | 038A             | 0000           |

| CCP5TMRH      | 0336              | 0000       | CCP7BUFL         | 038C             | 0000           |

| CCP5PRL       | 0338              | FFFF       | CCP7BUFH         | 038E             | 0000           |

| CCP5PRH       | 033A              | FFFF       | UART             | 0002             |                |

| CCP5RAL       | 033C              | 0000       | U1MODE           | 0398             | 0000           |

| CCP5RAH       | 033E              | 0000       | U1STA            | 039A             | 0110           |

| CCP5RBL       | 0340              | 0000       | U1TXREG          | 039C             | x0xx           |

| CCP5RBH       | 0342              | 0000       | U1RXREG          | 039E             | 0000           |

| CCP5BUFL      | 0344              | 0000       | U1BRG            | 03A0             | 0000           |

| CCP5BUFH      | 0346              | 0000       | U1ADMD           | 03A2             | 0000           |

| CCP6CON1L     | 0348              | 0000       | U2MODE           | 03AE             | 0000           |

| CCP6CON1H     | 034A              | 0000       | U2STA            | 03B0             | 0110           |

| CCP6CON2L     | 034C              | 0000       | U2TXREG          | 03B2             | xxxx           |

| CCP6CON2H     | 034E              | 0100       | U2RXREG          | 03B2             | 0000           |

| CCP6CON3L     | 0350              | 0000       | U2BRG            | 03B6             | 0000           |

| CCP6CON3H     | 0352              | 0000       | U2ADMD           | 03B8             | 0000           |

| CCP6STATL     | 0354              | 00x0       | U3MODE           | 03C4             | 0000           |

#### TABLE 4-7: SFR MAP: 0300h BLOCK

Legend: — = unimplemented, read as '0'; x = undefined. Reset values are shown in hexadecimal.

| R/S-0, HC <sup>(</sup>   | <sup>(1)</sup> R/W-0 <sup>(1)</sup> | R-0, HSC <sup>(1)</sup>                                                    | r-0          | R-0, HSC <sup>(1,3)</sup>                  | R-0 <sup>(1)</sup>    | U-0                   | U-0                   |  |  |  |  |

|--------------------------|-------------------------------------|----------------------------------------------------------------------------|--------------|--------------------------------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

| WR                       | WREN                                | WRERR                                                                      |              | SFTSWP                                     | P2ACTIV               | _                     |                       |  |  |  |  |

| bit 15                   |                                     | <u> </u>                                                                   |              |                                            |                       | _                     | bit                   |  |  |  |  |

|                          |                                     |                                                                            |              |                                            |                       |                       |                       |  |  |  |  |

| U-0                      | U-0                                 | U-0                                                                        | U-0          | R/W-0 <sup>(1)</sup>                       | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  |  |  |  |  |

|                          | —                                   | —                                                                          |              | NVMOP3 <sup>(2)</sup>                      | NVMOP2 <sup>(2)</sup> | NVMOP1 <sup>(2)</sup> | NVMOP0 <sup>(2)</sup> |  |  |  |  |

| bit 7                    |                                     |                                                                            |              |                                            |                       |                       | bit                   |  |  |  |  |

|                          |                                     |                                                                            |              |                                            |                       |                       |                       |  |  |  |  |

| Legend:                  |                                     | S = Settable b                                                             | bit          | HC = Hardware                              | Clearable bit         | r = Reserved I        | oit                   |  |  |  |  |

| R = Reada                | able bit                            | W = Writable                                                               | bit          | '0' = Bit is cleare                        | ed                    | x = Bit is unkn       | own                   |  |  |  |  |

| -n = Value               | at POR                              | '1' = Bit is set                                                           |              | U = Unimpleme                              | nted bit, read as     | s '0'                 |                       |  |  |  |  |

| HSC = Hai                | rdware Settable                     | /Clearable bit                                                             |              |                                            |                       |                       |                       |  |  |  |  |

|                          |                                     |                                                                            |              |                                            |                       |                       |                       |  |  |  |  |

| oit 15                   | WR: Write C                         | Control bit <sup>(1,4)</sup>                                               |              |                                            |                       |                       |                       |  |  |  |  |

|                          |                                     |                                                                            |              | m or erase operat                          |                       | on is self-timed      | and the bit           |  |  |  |  |

|                          |                                     |                                                                            |              | eration is complete<br>mplete and inactive |                       |                       |                       |  |  |  |  |

| oit 14                   |                                     | e Enable bit <sup>(1)</sup>                                                |              |                                            | •                     |                       |                       |  |  |  |  |

| <i>л</i> (1 <del>4</del> |                                     | s Flash program                                                            | /erase ope   | erations                                   |                       |                       |                       |  |  |  |  |

|                          |                                     | Flash program/                                                             |              |                                            |                       |                       |                       |  |  |  |  |

| oit 13                   | WRERR: W                            | rite Sequence E                                                            | Error Flag b | pit <sup>(1)</sup>                         |                       |                       |                       |  |  |  |  |

|                          |                                     |                                                                            |              | sequence attem                             | pt, or terminat       | ion has occurr        | ed (bit is se         |  |  |  |  |

|                          |                                     | tically on any se                                                          |              |                                            |                       |                       |                       |  |  |  |  |

| -: 10                    | -                                   | -                                                                          | operation c  | completed normally                         | ,                     |                       |                       |  |  |  |  |

| oit 12                   |                                     | Maintain as '0'                                                            |              |                                            |                       |                       |                       |  |  |  |  |

| oit 11                   |                                     | SFTSWP: Soft Swap Status bit <sup>(1,3)</sup><br>In Single Partition Mode: |              |                                            |                       |                       |                       |  |  |  |  |

|                          | Read as '0'.                        |                                                                            |              |                                            |                       |                       |                       |  |  |  |  |

|                          | In Dual Part                        |                                                                            |              |                                            |                       |                       |                       |  |  |  |  |

|                          |                                     |                                                                            |              | swapped using the                          |                       | ruction               |                       |  |  |  |  |

|                          |                                     | - ·                                                                        |              | sing the BOOTSWP                           | instruction           |                       |                       |  |  |  |  |

| oit 10                   | -                                   | ual Partition Ac                                                           | tive Status  | bit <sup>(1)</sup>                         |                       |                       |                       |  |  |  |  |

|                          | In Single Pa<br>Read as '0'.        | rtition Mode:                                                              |              |                                            |                       |                       |                       |  |  |  |  |

|                          | In Dual Part                        |                                                                            |              |                                            |                       |                       |                       |  |  |  |  |

|                          |                                     | 2 is mapped in                                                             | to the activ | /e region                                  |                       |                       |                       |  |  |  |  |

|                          |                                     | 1 is mapped in                                                             |              |                                            |                       |                       |                       |  |  |  |  |

| oit 9-4                  | Unimpleme                           | nted: Read as                                                              | '0'          |                                            |                       |                       |                       |  |  |  |  |

|                          | These bits can                      | only be reset or                                                           | n a Power-   | on Reset.                                  |                       |                       |                       |  |  |  |  |

| Note 1:                  |                                     | -                                                                          |              |                                            |                       |                       |                       |  |  |  |  |

|                          | All other combi                     | 114110115 01 11 11                                                         | UPS3.02 a    | are unimplemented                          |                       |                       |                       |  |  |  |  |

| 2:                       |                                     |                                                                            |              | are unimplemented any Reset.               | •                     |                       |                       |  |  |  |  |

| 2:<br>3:                 | This bit may be                     | cleared by soft                                                            | ware or by   | •                                          |                       | h memory progr        | am or erase           |  |  |  |  |

| Reset Type      | Clock Source | SYSRST Delay           | System Clock<br>Delay | Notes         |

|-----------------|--------------|------------------------|-----------------------|---------------|

| POR             | EC           | TPOR + TSTARTUP + TRST |                       | 1, 2, 3       |

|                 | ECPLL        | TPOR + TSTARTUP + TRST | Тьоск                 | 1, 2, 3, 5    |

|                 | XT, HS, SOSC | TPOR + TSTARTUP + TRST | Тоѕт                  | 1, 2, 3, 4    |

|                 | XTPLL, HSPLL | TPOR + TSTARTUP + TRST | TOST + TLOCK          | 1, 2, 3, 4, 5 |

|                 | FRC, OSCFDIV | TPOR + TSTARTUP + TRST | TFRC                  | 1, 2, 3, 6, 7 |

|                 | FRCPLL       | TPOR + TSTARTUP + TRST | TFRC + TLOCK          | 1, 2, 3, 5, 6 |

|                 | LPRC         | TPOR + TSTARTUP + TRST | TLPRC                 | 1, 2, 3, 6    |

|                 | DCO          | TPOR + TSTARTUP + TRST | TDCO                  | 1, 2, 3, 8    |

| BOR             | EC           | TSTARTUP + TRST        | —                     | 2, 3          |

|                 | ECPLL        | TSTARTUP + TRST        | TLOCK                 | 2, 3, 5       |

|                 | XT, HS, SOSC | TSTARTUP + TRST        | Тоѕт                  | 2, 3, 4       |

|                 | XTPLL, HSPLL | TSTARTUP + TRST        | Tost + Tlock          | 2, 3, 4, 5    |

|                 | FRC, OSCFDIV | TSTARTUP + TRST        | TFRC                  | 2, 3, 6, 7    |

|                 | FRCPLL       | TSTARTUP + TRST        | TFRC + TLOCK          | 2, 3, 5, 6    |

|                 | LPRC         | TSTARTUP + TRST        | TLPRC                 | 2, 3, 6       |

|                 | DCO          | TPOR + TSTARTUP + TRST | TDCO                  | 1, 2, 3, 8    |

| MCLR            | Any Clock    | Trst                   | _                     | 3             |

| WDT             | Any Clock    | Trst                   | —                     | 3             |

| Software        | Any clock    | Trst                   | —                     | 3             |

| Illegal Opcode  | Any Clock    | Trst                   | —                     | 3             |

| Uninitialized W | Any Clock    | Trst                   | —                     | 3             |

| Trap Conflict   | Any Clock    | TRST                   | _                     | 3             |

**Note 1:** TPOR = Power-on Reset Delay (10  $\mu$ s nominal).

- 2: TSTARTUP = TVREG.

- **3:** TRST = Internal State Reset Time (2 μs nominal).

- **4:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- 5: TLOCK = PLL Lock Time.

- 6: TFRC and TLPRC = RC Oscillator Start-up Times.

- 7: If Two-Speed Start-up is enabled, regardless of the Primary Oscillator selected, the device starts with FRC so the system clock delay is just TFRC, and in such cases, FRC start-up time is valid; it switches to the Primary Oscillator after its respective clock delay.

- 8: TDCO = DCO Start-up and Stabilization Times.

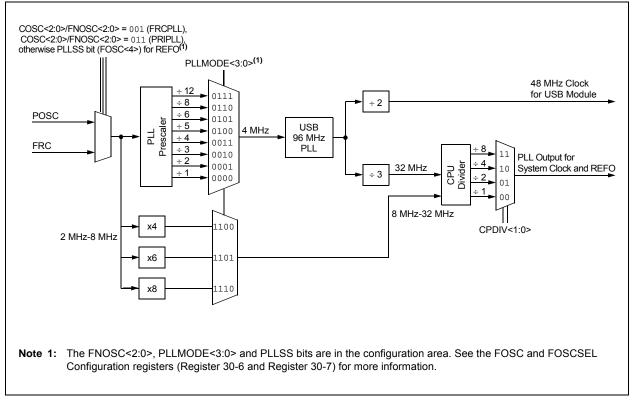

### FIGURE 9-2: PLL BLOCK

NOTES:

## 14.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own 16-bit timer. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (ICx) provides the Least Significant 16 bits of the 32-bit register pairs and the even numbered module (ICy) provides the Most Significant 16 bits. Wrap-arounds of the ICx registers cause an increment of their corresponding ICy registers.

Cascaded operation is configured in hardware by setting the IC32 bits (ICxCON2<8>) for both modules.

## 14.2 Capture Operations

The input capture module can be configured to capture timer values and generate interrupts on rising edges on ICx or all transitions on ICx. Captures can be configured to occur on all rising edges or just some (every 4<sup>th</sup> or 16<sup>th</sup>). Interrupts can be independently configured to generate on each event or a subset of events.

To set up the module for capture operations:

- 1. Configure the ICx input for one of the available Peripheral Pin Select pins.

- 2. If Synchronous mode is to be used, disable the Sync source before proceeding.

- 3. Make sure that any previous data has been removed from the FIFO by reading ICxBUF until the ICBNE bit (ICxCON1<3>) is cleared.

- 4. Set the SYNCSELx bits (ICxCON2<4:0>) to the desired Sync/Trigger source.

- 5. Set the ICTSELx bits (ICxCON1<12:10>) for the desired clock source.

- 6. Set the ICIx bits (ICxCON1<6:5>) to the desired interrupt frequency.

- 7. Select Synchronous or Trigger mode operation:

- a) Check that the SYNCSELx bits are not set to '00000'.

- b) For Synchronous mode, clear the ICTRIG bit (ICxCON2<7>).

- c) For Trigger mode, set ICTRIG and clear the TRIGSTAT bit (ICxCON2<6>).

- 8. Set the ICMx bits (ICxCON1<2:0>) to the desired operational mode.

- 9. Enable the selected Sync/Trigger source.

For 32-bit cascaded operations, the setup procedure is slightly different:

- 1. Set the IC32 bits for both modules (ICyCON2<8> and ICxCON2<8>), enabling the even numbered module first. This ensures the modules will start functioning in unison.

- 2. Set the ICTSELx and SYNCSELx bits for both modules to select the same Sync/Trigger and time base source. Set the even module first, then the odd module. Both modules must use the same ICTSELx and SYNCSELx bits settings.

- Clear the ICTRIG bit of the even module (ICyCON2<7>). This forces the module to run in Synchronous mode with the odd module, regardless of its Trigger setting.

- 4. Use the odd module's ICIx bits (ICxCON1<6:5>) to set the desired interrupt frequency.

- Use the ICTRIG bit of the odd module (ICxCON2<7>) to configure Trigger or Synchronous mode operation.

- **Note:** For Synchronous mode operation, enable the Sync source as the last step. Both input capture modules are held in Reset until the Sync source is enabled.

- Use the ICMx bits of the odd module (ICxCON1<2:0>) to set the desired Capture mode.

The module is ready to capture events when the time base and the Sync/Trigger source are enabled. When the ICBNE bit (ICxCON1<3>) becomes set, at least one capture value is available in the FIFO. Read input capture values from the FIFO until the ICBNE clears to '0'.

For 32-bit operation, read both the ICxBUF and ICyBUF for the full 32-bit timer value (ICxBUF for the Isw, ICyBUF for the msw). At least one capture value is available in the FIFO buffer when the odd module's ICBNE bit (ICxCON1<3>) becomes set. Continue to read the buffer registers until ICBNE is cleared (performed automatically by hardware).

#### REGISTER 17-1: SPIx CONTROL REGISTER 1 LOW (CONTINUED)

| bit 8 | CKE: SPIx Clock Edge Select bit <sup>(1)</sup>                                                                                                                                                                             |       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|       | <ul> <li>1 = Transmit happens on transition from active clock state to Idle clock state</li> <li>0 = Transmit happens on transition from Idle clock state to active clock state</li> </ul>                                 |       |

| bit 7 | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(2)</sup>                                                                                                                                                           |       |

|       | 1 = $\overline{SSx}$ pin is used by the macro in Slave mode; $\overline{SSx}$ pin is used as the slave select 0 = $\overline{SSx}$ pin is not used by the macro ( $\overline{SSx}$ pin will be controlled by the port I/O) | input |

| bit 6 | CKP: SPIx Clock Polarity Select bit                                                                                                                                                                                        |       |

|       | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                   |       |

| bit 5 | MSTEN: Master Mode Enable bit                                                                                                                                                                                              |       |

|       | 1 = Master mode<br>0 = Slave mode                                                                                                                                                                                          |       |

| bit 4 | DISSDI: Disable SDIx Input Port bit                                                                                                                                                                                        |       |

|       | <ul> <li>1 = SDIx pin is not used by the module; pin is controlled by the port function</li> <li>0 = SDIx pin is controlled by the module</li> </ul>                                                                       |       |

| bit 3 | DISSCK: Disable SCKx Output Port bit                                                                                                                                                                                       |       |

|       | <ul> <li>1 = SCKx pin is not used by the module; pin is controlled by the port function</li> <li>0 = SCKx pin is controlled by the module</li> </ul>                                                                       |       |

| bit 2 | MCLKEN: Master Clock Enable bit <sup>(3)</sup>                                                                                                                                                                             |       |

|       | <ul> <li>1 = REFO output is used by the BRG</li> <li>0 = Peripheral clock is used by the BRG</li> </ul>                                                                                                                    |       |

| bit 1 | SPIFE: Frame Sync Pulse Edge Select bit                                                                                                                                                                                    |       |

|       | <ul> <li>1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock</li> <li>0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock</li> </ul>                                         |       |

| bit 0 | ENHBUF: Enhanced Buffer Mode Enable bit                                                                                                                                                                                    |       |

|       | 1 = Enhanced Buffer mode is enabled<br>0 = Enhanced Buffer mode is disabled                                                                                                                                                |       |

|       |                                                                                                                                                                                                                            |       |

| Note  | When AUDEN = 1, this module functions as if $CKE = 0$ , regardless of its actual value.                                                                                                                                    |       |

- 2: When FRMEN = 1, SSEN is not used.

- **3:** MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows the FRMSYPW bit.

#### REGISTER 20-4: U10TGCON: USB ON-THE-GO CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   | —   | —   | _   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0   | R/W-0   | R/W-0                   | R/W-0                   | r-0 | R/W-0                | r-0 | R/W-0                  |

|---------|---------|-------------------------|-------------------------|-----|----------------------|-----|------------------------|

| DPPULUP | DMPULUP | DPPULDWN <sup>(1)</sup> | DMPULDWN <sup>(1)</sup> | _   | OTGEN <sup>(1)</sup> | —   | VBUSDIS <sup>(1)</sup> |

| bit 7   |         |                         |                         |     |                      |     | bit 0                  |

| Legend:           | r = Reserved bit |                                         |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                                                                                 |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | DPPULUP: D+ Pull-up Enable bit                                                                                                                                                                                                                             |

|          | <ul> <li>1 = D+ data line pull-up resistor is enabled</li> <li>0 = D+ data line pull-up resistor is disabled</li> </ul>                                                                                                                                    |

| bit 6    | DMPULUP: D- Pull-up Enable bit                                                                                                                                                                                                                             |

|          | <ul> <li>1 = D- data line pull-up resistor is enabled</li> <li>0 = D- data line pull-up resistor is disabled</li> </ul>                                                                                                                                    |

| bit 5    | DPPULDWN: D+ Pull-Down Enable bit <sup>(1)</sup>                                                                                                                                                                                                           |

|          | <ul> <li>1 = D+ data line pull-down resistor is enabled</li> <li>0 = D+ data line pull-down resistor is disabled</li> </ul>                                                                                                                                |

| bit 4    | DMPULDWN: D- Pull-Down Enable bit <sup>(1)</sup>                                                                                                                                                                                                           |

|          | <ul> <li>1 = D- data line pull-down resistor is enabled</li> <li>0 = D- data line pull-down resistor is disabled</li> </ul>                                                                                                                                |

| bit 3    | Reserved: Maintain as '0'                                                                                                                                                                                                                                  |

| bit 2    | OTGEN: OTG Features Enable bit <sup>(1)</sup>                                                                                                                                                                                                              |

|          | <ul> <li>1 = USB OTG is enabled; all D+/D- pull-up and pull-down bits are enabled</li> <li>0 = USB OTG is disabled; D+/D- pull-up and pull-down bits are controlled in hardware by the settings of the HOSTEN and USBEN (U1CON&lt;3,0&gt;) bits</li> </ul> |

| bit 1    | Reserved: Maintain as '0'                                                                                                                                                                                                                                  |

| bit 0    | VBUSDIS: VBUS Discharge Enable bit <sup>(1)</sup>                                                                                                                                                                                                          |

|          | <ul> <li>1 = VBUS line is discharged through a resistor</li> <li>0 = VBUS line is not discharged</li> </ul>                                                                                                                                                |

Note 1: These bits are only used in Host mode; do not use in Device mode.

## REGISTER 20-13: U1CNFG2: USB CONFIGURATION REGISTER 2

| U-0                                | U-0           | U-0             | U-0               | U-0          | U-0              | U-0    | U-0   |

|------------------------------------|---------------|-----------------|-------------------|--------------|------------------|--------|-------|

| _                                  | —             | —               | —                 | —            | —                | —      | —     |

| bit 15                             |               |                 |                   |              |                  |        | bit 8 |

|                                    |               |                 |                   |              |                  |        |       |

| U-0                                | U-0           | U-0             | R/W-0             | R/W-0        | U-0              | U-0    | U-0   |

| —                                  | —             | —               | PUVBUS            | EXTI2CEN     | —                | —      | —     |

| bit 7                              | ·             |                 | -                 |              |                  |        | bit 0 |

|                                    |               |                 |                   |              |                  |        |       |

| Legend:                            |               |                 |                   |              |                  |        |       |

| R = Readab                         | le bit        | W = Writable    | bit               | U = Unimplem | nented bit, read | as '0' |       |

| -n = Value at POR '1' = Bit is set |               | t               | '0' = Bit is clea | ared         | x = Bit is unkn  | own    |       |

|                                    |               |                 |                   |              |                  |        |       |

| bit 15-5                           | Unimplemen    | ted: Read as    | '0'               |              |                  |        |       |

| bit 4                              | PUVBUS: VB    | us Pull-Up En   | able bit          |              |                  |        |       |

|                                    | 1 = Pull-up o | n Veus nin is d | habled            |              |                  |        |       |

- 1 = Pull-up on VBUS pin is enabled 0 = Pull-up on VBUS pin is disabled

- bit 3 **EXTI2CEN:** I<sup>2</sup>C Interface for External Module Control Enable bit

- 1 = External module(s) is controlled via the  $I^2C$  interface

- 0 = External module(s) is controlled via the dedicated pins

- bit 2-0 Unimplemented: Read as '0'

#### 20.7.2 USB INTERRUPT REGISTERS

#### REGISTER 20-14: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|

| IDIF      | T1MSECIF  | LSTATEIF  | ACTVIF    | SESVDIF   | SESENDIF  | —   | VBUSVDIF  |

| bit 7     |           |           |           |           |           |     | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | K = Write '1' to Clear bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                    |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | IDIF: ID State Change Indicator bit                                                                                                           |

|          | 1 = Change in ID state is detected                                                                                                            |

|          | 0 = No ID state change is detected                                                                                                            |

| bit 6    | T1MSECIF: 1 Millisecond Timer bit                                                                                                             |

|          | 1 = The 1 millisecond timer has expired                                                                                                       |

|          | 0 = The 1 millisecond timer has not expired                                                                                                   |

| bit 5    | LSTATEIF: Line State Stable Indicator bit                                                                                                     |

|          | <ul> <li>1 = USB line state (as defined by the SE0 and JSTATE bits) has been stable for 1 ms, but different from<br/>the last time</li> </ul> |

|          | 0 = USB line state has not been stable for 1 ms                                                                                               |

| bit 4    | ACTVIF: Bus Activity Indicator bit                                                                                                            |

|          | 1 = Activity on the D+/D- lines or VBUS is detected                                                                                           |

|          | 0 = No activity on the D+/D- lines or VBUS is detected                                                                                        |

| bit 3    | SESVDIF: Session Valid Change Indicator bit                                                                                                   |

|          | 1 = VBUS has crossed VA_SESS_END (as defined in the <i>"USB 2.0 Specification"</i> ) <sup>(1)</sup><br>0 = VBUS has not crossed VA_SESS_END   |

| bit 2    | SESENDIF: B-Device VBUS Change Indicator bit                                                                                                  |

|          | 1 = VBUS change on B-device is detected; VBUS has crossed VB_SESS_END (as defined in the "USB 2.0<br>Specification") <sup>(1)</sup>           |

|          | 0 = VBUS has not crossed VB_SESS_END                                                                                                          |

| bit 1    | Unimplemented: Read as '0'                                                                                                                    |

| bit 0    | VBUSVDIF: A-Device VBUS Change Indicator bit                                                                                                  |

|          | 1 = VBUS change on A-device is detected; VBUS has crossed VA_VBUS_VLD (as defined in the "USB 2.0<br>Specification") <sup>(1)</sup>           |

|          | 0 = No VBUS change on A-device is detected                                                                                                    |

| Note 1:  | VBUS threshold crossings may either be rising or falling.                                                                                     |

| 1        |                                                                                                                                               |

**Note:** Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits, at the moment of the write, to become cleared.

| Pin Name<br>(Alternate Function) | Туре | Description                                                            |

|----------------------------------|------|------------------------------------------------------------------------|

| PMA<22:16>                       | 0    | Address Bus bits<22:16>                                                |

| PMA15                            | 0    | Address Bus bit 15                                                     |

|                                  | I/O  | Data Bus bit 15 (16-bit port with Multiplexed Addressing)              |

| (PMCS2)                          | 0    | Chip Select 2 (alternate location)                                     |

| PMA14                            | 0    | Address Bus bit 14                                                     |

|                                  | I/O  | Data Bus bit 14 (16-bit port with Multiplexed Addressing)              |

| (PMCS1)                          | 0    | Chip Select 1 (alternate location)                                     |

| PMA<13:8>                        | 0    | Address Bus bits<13:8>                                                 |

|                                  | I/O  | Data Bus bits<13:8> (16-bit port with Multiplexed Addressing)          |

| PMA<7:3>                         | 0    | Address Bus bits<7:3>                                                  |

| PMA2                             | 0    | Address Bus bit 2                                                      |

| (PMALU)                          | 0    | Address Latch Upper Strobe for Multiplexed Address                     |

| PMA1                             | I/O  | Address Bus bit 1                                                      |

| (PMALH)                          | 0    | Address Latch High Strobe for Multiplexed Address                      |

| PMA0                             | I/O  | Address Bus bit 0                                                      |

| (PMALL)                          | 0    | Address Latch Low Strobe for Multiplexed Address                       |

| PMD<15:8>                        | I/O  | Data Bus bits<15:8> (Demultiplexed Addressing)                         |

| PMD<7:4>                         | I/O  | Data Bus bits<7:4>                                                     |

|                                  | 0    | Address Bus bits<7:4> (4-bit port with 1-Phase Multiplexed Addressing) |

| PMD<3:0>                         | I/O  | Data Bus bits<3:0>                                                     |

| PMCS1 <sup>(1)</sup>             | 0    | Chip Select 1                                                          |

| PMCS2 <sup>(1)</sup>             | 0    | Chip Select 2                                                          |

| PMWR                             | I/O  | Write Strobe <sup>(2)</sup>                                            |

| (PMENB)                          | I/O  | Enable Signal <sup>(2)</sup>                                           |

| PMRD                             | I/O  | Read Strobe <sup>(2)</sup>                                             |

| (PMRD/PMWR)                      | I/O  | Read/Write Signal <sup>(2)</sup>                                       |

| PMBE1                            | 0    | Byte Indicator                                                         |

| PMBE0                            | 0    | Nibble or Byte Indicator                                               |

| PMACK1                           | I    | Acknowledgment Signal 1                                                |

| PMACK2                           | I    | Acknowledgment Signal 2                                                |

#### TABLE 21-2: ENHANCED PARALLEL MASTER PORT PIN DESCRIPTIONS

**Note 1:** These pins are implemented in 100-pin and 121-pin devices only.

2: Signal function depends on the setting of the MODE<1:0> and SM bits (PMCON1<9:8> and PMCSxCF<8>).

| R/W-0               | R/W-0                                                                                                                                                                                               | R/W-0            | R/W-0    | R/W-0             | R/W-0           | R/W-0          | R/W-0    |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|-------------------|-----------------|----------------|----------|

| PWCSAMP7            | PWCSAMP6                                                                                                                                                                                            | PWCSAMP5         | PWCSAMP4 | PWCSAMP3          | PWCSAMP2        | PWCSAMP1       | PWCSAMP0 |

| bit 15              |                                                                                                                                                                                                     |                  |          | •                 |                 |                | bit 8    |

|                     |                                                                                                                                                                                                     |                  |          |                   |                 |                |          |

| R/W-0               | R/W-0                                                                                                                                                                                               | R/W-0            | R/W-0    | R/W-0             | R/W-0           | R/W-0          | R/W-0    |

| PWCSTAB7            | PWCSTAB6                                                                                                                                                                                            | PWCSTAB5         | PWCSTAB4 | PWCSTAB3          | PWCSTAB2        | PWCSTAB1       | PWCSTAB0 |

| bit 7               |                                                                                                                                                                                                     |                  |          |                   |                 |                | bit 0    |

|                     |                                                                                                                                                                                                     |                  |          |                   |                 |                |          |

| Legend:             |                                                                                                                                                                                                     |                  |          |                   |                 |                |          |

| R = Readable        | bit                                                                                                                                                                                                 | W = Writable b   | bit      | U = Unimplem      | ented bit, read | as '0'         |          |

| -n = Value at P     | OR                                                                                                                                                                                                  | '1' = Bit is set |          | '0' = Bit is clea | red             | x = Bit is unk | nown     |

| bit 15-8<br>bit 7-0 | <pre>PWCSAMP&lt;7:0&gt;: Power Control Sample Window Timer bits<br/>11111111 = Sample window is always enabled, even when PWCEN = 0<br/>11111110 = Sample window is 254 TPWCCLK clock periods</pre> |                  |          |                   |                 |                |          |

#### REGISTER 22-5: RTCCON3L: RTCC CONTROL REGISTER 3 (LOW)

Note 1: The sample window always starts when the stability window timer expires, except when its initial value is 00h.

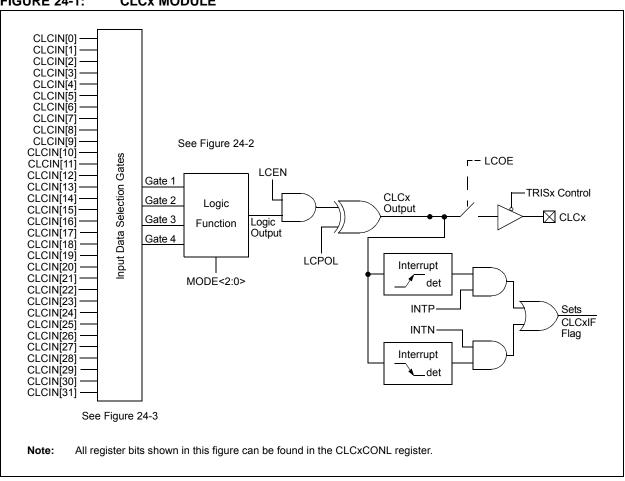

## 24.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins. This provides greater flexibility and potential in embedded designs, since the CLC module can operate outside the limitations of software execution and supports a vast amount of output designs.

There are four input gates to the selected logic function. These four input gates select from a pool of up to 32 signals that are selected using four data source selection multiplexers. Figure 24-1 shows an overview of the module. Figure 24-3 shows the details of the data source multiplexers and logic input gate connections.

#### FIGURE 24-1: **CLCx MODULE**

## REGISTER 25-1: AD1CON1: A/D CONTROL REGISTER 1 (CONTINUED)

| bit 1 | SAMP: A/D Sample Enable bit                     |

|-------|-------------------------------------------------|

|       | 1 = A/D Sample-and-Hold amplifiers are sampling |

|       | 0 = A/D Sample-and-Hold amplifiers are holding  |

| bit 0 | DONE: A/D Conversion Status bit                 |

|       | 1 = A/D conversion cycle has completed          |

- 0 = A/D conversion cycle has not started or is in progress

- Note 1: This bit is only available when Extended DMA and buffer features are available (DMAEN = 1).