Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 1MB (341.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 121-TFBGA                                                                       |

| Supplier Device Package    | 121-TFBGA (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj1024ga610-i-bg |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin | Full Pin Name                    | Pin | Full Pin Name                                                 |

|-----|----------------------------------|-----|---------------------------------------------------------------|

| A1  | HLVDIN/CTED8/PMD4/RE4            |     | AN16/RPI41/OCM3C/PMCS2/RC4                                    |

| A2  | CTED9/PMD3/RE3                   | E2  | RPI40/OCM2D/RC3                                               |

| A3  | OCM2F/CTED10/RG13                | E3  | AN17/C1IND/RP21/ICM1/OCM1A/PMA5/RG6                           |

| A4  | PMD0/RE0                         | E4  | RPI39/OCM2C/RC2                                               |

| A5  | PMD8/RG0                         | E5  | N/C                                                           |

| A6  | PMD10/RF1                        | E6  | PMD9/RG1                                                      |

| A7  | N/C                              | E7  | N/C                                                           |

| A8  | N/C                              | E8  | RPI35/PMBE1/RA15                                              |

| A9  | RPI42/OCM3E/PMD12/RD12           | E9  | CLC4OUT/RP2/U6RTS/U6BCLK/ICM5/RD8                             |

| A10 | RP23/PMACK1/RD2                  | E10 | RP4/PMACK2/RD9                                                |

| A11 | RP24/U5TX/ICM4/RD1               | E11 | RPI36/PMA22/RA14                                              |

| B1  | N/C                              | F1  | MCLR                                                          |

| B2  | OCM1C/CTED3/RG15                 | F2  | AN19/C2IND/RP19/ICM2/OCM2A/PMA3/RG8                           |

| B3  | PMD2/RE2                         | F3  | AN20/C1INC/C2INC/C3INC/ <b>RP27</b> /OCM2B/PMA2/PMALU/<br>RG9 |

| B4  | PMD1/RE1                         | F4  | AN18/C1INC/RP26/OCM1B/PMA4/RG7                                |

| B5  | AN22/OCM1F/PMA17/RA7             | F5  | Vss                                                           |

| B6  | U5CTS/OC6/PMD11/RF0              | F6  | N/C                                                           |

| B7  | VCAP                             | F7  | N/C                                                           |

| B8  | RP20/PMRD/PMWR/RD5               | F8  | VDD                                                           |

| B9  | RP22/ICM7/PMBE0/RD3              | F9  | OSCI/CLKI/RC12                                                |

| B10 | Vss                              | F10 | Vss                                                           |

| B11 | SOSCO/C3INC/RPI37/PWRLCLK/RC14   | F11 | OSCO/CLKO/RC15                                                |

| C1  | SCL3/IC5/PMD6/RE6                | G1  | RPI33/PMCS1/RE8                                               |

| C2  | VDD                              | G2  | AN21/RPI34/PMA19/RE9                                          |

| C3  | OCM2E/RG12                       | G3  | TMS/OCM3D/RA0                                                 |

| C4  | CTED11/PMA16/RG14                | G4  | N/C                                                           |

| C5  | AN23/OCM1E/RA6                   | G5  | VDD                                                           |

| C6  | N/C                              | G6  | Vss                                                           |

| C7  | C3INA/U5RTS/U5BCLK/OC5/PMD15/RD7 | G7  | Vss                                                           |

| C8  | RP25/PMWR/PMENB/RD4              | G8  | N/C                                                           |

| C9  | N/C                              | G9  | TDO/RA5                                                       |

| C10 | SOSCI/C3IND/RC13                 | G10 | SDA2/PMA20/RA3                                                |

| C11 | RP12/PMA14/PMCS1/RD11            | G11 | TDI/PMA21/RA4                                                 |

| D1  | RPI38/OCM1D/RC1                  | H1  | PGEC3/AN5/C1INA/RP18/ICM3/OCM3A/RB5                           |

| D2  | SDA3/IC6/PMD7/RE7                | H2  | PGED3/AN4/C1INB/RP28/OCM3B/RB4                                |

| D3  | IC4/CTED4/PMD5/RE5               | H3  | N/C                                                           |

| D4  | N/C                              | H4  | N/C                                                           |

| D5  | N/C                              | H5  | N/C                                                           |

| D6  | N/C                              | H6  | VDD                                                           |

| D7  | C3INB/U5RX/OC4/PMD14/RD6         | H7  | N/C                                                           |

| D8  | OCM3F/PMD13/RD13                 | H8  | RF7                                                           |

| D9  | CLC3OUT/RP11/U6CTS/ICM6/RD0      | H9  | INT0/RF6                                                      |

| D10 | N/C                              | H10 | SCL1/RG2                                                      |

| D11 | RP3/PMA15/PMCS2/RD10             | H11 | PMPCS1/SCL2/RA2                                               |

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select (PPS) functions.

Note: Pinouts are subject to change.

| File Name          | Address                         | All Resets | File Name              | Address         | All Resets |  |

|--------------------|---------------------------------|------------|------------------------|-----------------|------------|--|

| INPUT CAPTURE      |                                 |            |                        |                 |            |  |

| IC1CON1            | 0200                            | 0000       | OC4R                   | 0254            | xxxx       |  |

| IC1CON2            | 0202                            | 000D       | OC4TMR                 | 0256            | xxxx       |  |

| IC1BUF             | 0204                            | 0000       | OC5CON1                | 0258            | 0000       |  |

| IC1TMR             | 0206                            | 0000       | OC5CON2                | 025A            | 000C       |  |

| IC2CON1            | 0208                            | 0000       | OC5RS                  | 025C            | xxxx       |  |

| IC2CON2            | 020A                            | 000D       | OC5R                   | 025E            | xxxx       |  |

| IC2BUF             | 020C                            | 0000       | OC5TMR                 | 0260            | xxxx       |  |

| IC2TMR             | 020E                            | 0000       | OC6CON1                | 0262            | 0000       |  |

| IC3CON1            | 0210                            | 0000       | OC6CON2                | 0264            | 000C       |  |

| IC3CON2            | 0212                            | 000D       | OC6RS                  | 0266            | xxxx       |  |

| IC3BUF             | 0214                            | 0000       | OC6R                   | 0268            | xxxx       |  |

| IC3TMR             | 0216                            | 0000       | OC6TMR                 | 026A            | xxxx       |  |

| IC4CON1            | 0218                            | 0000       |                        | CAPTURE/COMPARE | 1          |  |

| IC4CON2            | 021A                            | 000D       | CCP1CON1L              | 026C            | 0000       |  |

| IC4BUF             | 021C                            | 0000       | CCP1CON1H              | 026E            | 0000       |  |

| IC4TMR             | 021E                            | 0000       | CCP1CON2L              | 0270            | 0000       |  |

| IC5CON1            | 0220                            | 0000       | CCP1CON2H              | 0272            | 0100       |  |

| IC5CON2            | 0222                            | 000D       | CCP1CON3L              | 0274            | 0000       |  |

| IC5BUF             | 0224                            | 0000       | CCP1CON3H              | 0276            | 0000       |  |

| IC5TMR             | 0226                            | 0000       | CCP1STATL              | 0278            | 00x0       |  |

| IC6CON1            | 0228                            | 0000       | CCP1STATH              | 0276            | 0000       |  |

| IC6CON2            | 022A                            | 000D       | CCP1TMRL               | 027C            | 0000       |  |

| IC6BUF             | 022C                            | 0000       | CCP1TMRH               | 0276<br>027E    | 0000       |  |

| IC6TMR             | 022E                            | 0000       | CCP1PRL                | 0280            | FFFF       |  |

|                    | 1                               | 0000       | CCP1PRH                | 0282            | FFFF       |  |

| OC1CON1            | 0230                            | 0000       | CCP1RAL                | 0284            | 0000       |  |

| OC1CON2            | 0232                            | 0000       | CCP1RAH                | 0286            | 0000       |  |

| OC1RS              | 0234                            | xxxx       | CCP1RBL                | 0288            | 0000       |  |

| OC1R               | 0236                            |            | CCP1RBH                | 0288            | 0000       |  |

| OC1TMR             | 0238                            | xxxx       | CCP1BUFL               | 028C            | 0000       |  |

| OC2CON1            | 0230<br>023A                    | 0000       | CCP1BUFH               | 028E            | 0000       |  |

| OC2CON2            | 023A                            |            | CCP2CON1L              | 0290            |            |  |

| OC2RS              | 023C                            | 000C       | CCP2CON1H              | 0290            | 0000       |  |

| OC2R3              | 023E                            |            | CCP2CON1H<br>CCP2CON2L | 0292            | 0000       |  |

| OC2TMR             | 0240                            |            | CCP2CON2L<br>CCP2CON2H | 0294            | 0100       |  |

| OC3CON1            | 0242                            | 0000       | CCP2CON2H<br>CCP2CON3L | 0298            | 0100       |  |

| OC3CON1<br>OC3CON2 | 0244                            | 0000       | CCP2CON3L<br>CCP2CON3H | 0298<br>029A    | 0000       |  |

| OC3RS              | 1 1                             |            | CCP2CONSH              | 029A            |            |  |

|                    | 0248                            |            | CCP2STATE              |                 | 00x0       |  |

| OC3R               | 024A                            |            |                        | 029E            | 0000       |  |

| OC3TMR             | 024C                            |            | CCP2TMRL               | 02A0            |            |  |

| OC4CON1            | 024E                            | 0000       | CCP2TMRH               | 02A2            | 0000       |  |

| OC4CON2            | 0250                            | 000C       | CCP2PRL                | 02A4            | FFFF       |  |

| OC4RS              | 0252<br>mplemented, read as '0' | XXXX       | CCP2PRH                | 02A6            | FFFF       |  |

TABLE 4-6:SFR MAP: 0200h BLOCK

Legend: — = unimplemented, read as '0'; x = undefined. Reset values are shown in hexadecimal.

| File Name        | Address | All Resets | File Name       | Address | All Resets |

|------------------|---------|------------|-----------------|---------|------------|

| UART (CONTINUED) |         |            | UART (CONTINUED | )       |            |

| U3STA            | 03C6    | 0110       | U5BRG           | 03E4    | 0000       |

| U3TXREG          | 03C8    | xxxx       | U5ADMD          | 03E6    | 0000       |

| U3RXREG          | 03CA    | 0000       | U6MODE          | 03E8    | 0000       |

| U3BRG            | 03CC    | 0000       | U6STA           | 03EA    | 0110       |

| U3ADMD           | 03CE    | 0000       | U6TXREG         | 03EC    | xxxx       |

| U4MODE           | 03D0    | 0000       | U6RXREG         | 03EE    | 0000       |

| U4STA            | 03D2    | 0110       | U6BRG           | 03F0    | 0000       |

| U4TXREG          | 03D4    | xxxx       | U6ADMD          | 03F2    | 0000       |

| U4RXREG          | 03D6    | 0000       | SPI             | •       | ·          |

| U4BRG            | 03D8    | 0000       | SPI1CON1        | 03F4    | 0x00       |

| U4ADMD           | 03DA    | 0000       | SPI1CON2        | 03F6    | 0000       |

| U5MODE           | 03DC    | 0000       | SPI1CON3        | 03F8    | 0000       |

| U5STA            | 03DE    | 0110       | SPI1STATL       | 03FC    | 0028       |

| U5TXREG          | 03E0    | xxxx       | SPI1STATH       | 03FE    | 0000       |

| U5RXREG          | 03E2    | 0000       |                 |         |            |

# TABLE 4-7: SFR MAP: 0300h BLOCK (CONTINUED)

**Legend:** — = unimplemented, read as '0'; x = undefined. Reset values are shown in hexadecimal.

| File Name            | Address | All Resets | File Name       | Address | All Resets |

|----------------------|---------|------------|-----------------|---------|------------|

| I/O                  |         |            | PORTD (CONTINUE | D)      |            |

| PADCON               | 065E    | 0000       | ANSD            | 06A6    | FFFF       |

| IOCSTAT              | 0660    | 0000       | IOCPD           | 06A8    | 0000       |

| PORTA <sup>(1)</sup> | 1 1     |            | IOCND           | 06AA    | 0000       |

| TRISA                | 0662    | FFFF       | IOCFD           | 06AC    | 0000       |

| PORTA                | 0664    | 0000       | IOCPUD          | 06AE    | 0000       |

| LATA                 | 0666    | 0000       | IOCPDD          | 06B0    | 0000       |

| ODCA                 | 0668    | 0000       | PORTE           |         | 4          |

| ANSA                 | 066A    | FFFF       | TRISE           | 06B2    | FFFF       |

| IOCPA                | 066C    | 0000       | PORTE           | 06B4    | 0000       |

| IOCNA                | 066E    | 0000       | LATE            | 06B6    | 0000       |

| IOCFA                | 0670    | 0000       | ODCE            | 06B8    | 0000       |

| IOCPUA               | 0672    | 0000       | ANSE            | 06BA    | FFFF       |

| IOCPDA               | 0674    | 0000       | IOCPE           | 06BC    | 0000       |

| PORTB                | · ·     |            | IOCNE           | 06BE    | 0000       |

| TRISB                | 0676    | FFFF       | IOCFE           | 06C0    | 0000       |

| PORTB                | 0678    | 0000       | IOCPUE          | 06C2    | 0000       |

| LATB                 | 067A    | 0000       | IOCPDE          | 06C4    | 0000       |

| ODCB                 | 067C    | 0000       | PORTF           |         | 1          |

| ANSB                 | 067E    | FFFF       | TRISF           | 06C6    | FFFF       |

| IOCPB                | 0680    | 0000       | PORTF           | 06C8    | 0000       |

| IOCNB                | 0682    | 0000       | LATF            | 06CA    | 0000       |

| IOCFB                | 0684    | 0000       | ODCF            | 06CC    | 0000       |

| IOCPUB               | 0686    | 0000       | IOCPF           | 06D0    | 0000       |

| IOCPDB               | 0688    | 0000       | IOCNF           | 06D2    | 0000       |

| PORTC                |         |            | IOCFF           | 06D4    | 0000       |

| TRISC                | 068A    | FFFF       | IOCPUF          | 06D6    | 0000       |

| PORTC                | 068C    | 0000       | IOCPDF          | 06D8    | 0000       |

| LATC                 | 068E    | 0000       | PORTG           |         |            |

| ODCC                 | 0690    | 0000       | TRISG           | 06DA    | FFFF       |

| ANSC                 | 0692    | FFFF       | PORTG           | 06DC    | 0000       |

| IOCPC                | 0694    | 0000       | LATG            | 06DE    | 0000       |

| IOCNC                | 0696    | 0000       | ODCG            | 06E0    | 0000       |

| IOCFC                | 0698    | 0000       | ANSG            | 06E2    | FFFF       |

| IOCPUC               | 069A    | 0000       | IOCPG           | 06E4    | 0000       |

| IOCPDC               | 069C    | 0000       | IOCNG           | 06E6    | 0000       |

| PORTD                | I       |            | IOCFG           | 06E8    | 0000       |

| TRISD                | 069E    | FFFF       | IOCPUG          | 06EA    | 0000       |

| PORTD                | 06A0    | 0000       | IOCPDG          | 06EC    | 0000       |

| LATD                 | 06A2    | 0000       |                 |         |            |

| ODCD                 | 06A4    | 0000       |                 |         |            |

# TABLE 4-10:SFR MAP: 0600h BLOCK

$\label{eq:legend: Legend: Legend: Legend: Legend: Legend: Constant of the set of the s$

Note 1: PORTA and all associated bits are unimplemented in 64-pin devices and read as '0'.

| Oscillator Mode                                   | Oscillator Source | FNOSC<2:0> | Notes   |

|---------------------------------------------------|-------------------|------------|---------|

| Oscillator with Frequency Division (OSCFDIV)      | Internal/External | 111        | 1, 2, 3 |

| Digitally Controlled Oscillator (DCO)             | Internal          | 110        | 3       |

| Low-Power RC Oscillator (LPRC)                    | Internal          | 101        | 3       |

| Secondary (Timer1) Oscillator (SOSC)              | Secondary         | 100        | 3       |

| Primary Oscillator (XT, HS or EC) with PLL Module | Primary           | 011        | 4       |

| Primary Oscillator (XT, HS or EC)                 | Primary           | 010        | 4       |

| Fast RC Oscillator with PLL Module (FRCPLL)       | Internal          | 001        | 3       |

| Fast RC Oscillator (FRC)                          | Internal          | 000        | 3       |

# TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** The input oscillator to the OSCFDIV Clock mode is determined by the RCDIV<2:0> (CLKDIV<10:8) bits. At POR, the default value selects the FRC module.

- **2:** This is the default oscillator mode for an unprogrammed (erased) device.

- 3: OSCO pin function is determined by the OSCIOFCN Configuration bit.

- 4: The POSCMD<1:0> Configuration bits select the oscillator driver mode (XT, HS or EC).

# 9.3 Control Registers

The operation of the oscillator is controlled by five Special Function Registers:

- OSCCON

- CLKDIV

- OSCTUN

- OSCDIV

- OSCFDIV

In addition, two registers are used to control the DCO:

- DCOCON

- DCOTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources. OSCCON is protected by a write lock to prevent inadvertent clock switches. See **Section 9.4 "Clock Switching Operation**" for more information. The CLKDIV register (Register 9-2) controls the features associated with Doze mode, as well as the postscalers for the OSCFDIV Clock mode and the PLL module.

The OSCTUN register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 1.5\%$ . It also controls the FRC self-tuning features described in **Section 9.5 "FRC Active Clock Tuning"**.

The OSCDIV and OSCFDIV registers provide control for the system Oscillator Frequency Divider.

# 9.3.1 DCO OVERVIEW

The DCO (Digitally Controlled Oscillator) is a lowpower alternative to the FRC. It can generate a wider selection of operating frequencies and can be trimmed to correct process variations if an exact frequency is required. However, the DCO is not designed for use with USB applications and cannot meet USB timing restrictions.

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 3 **CF:** Clock Fail Detect bit 1 = FSCM has detected a clock failure 0 = No clock failure has been detected

- bit 2 **POSCEN:** Primary Oscillator Sleep Enable bit

- 1 = Primary Oscillator continues to operate during Sleep mode

- 0 = Primary Oscillator is disabled during Sleep mode

- bit 1 SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit

- 1 = Enables Secondary Oscillator

- 0 = Disables Secondary Oscillator

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Initiates an oscillator switch to a clock source specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: Reset values for these bits are determined by the FNOSCx Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1', once the IOLOCK bit is set, it cannot be cleared.

- 3: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

| U-0          | U-0                                                             | U-0              | U-0   | U-0                                | U-0  | R/W-1                | U-0   |

|--------------|-----------------------------------------------------------------|------------------|-------|------------------------------------|------|----------------------|-------|

|              | —                                                               | —                | _     | —                                  | —    | ANSE9 <sup>(1)</sup> | _     |

| bit 15       |                                                                 |                  |       | -<br>-                             |      |                      | bit 8 |

|              |                                                                 |                  |       |                                    |      |                      |       |

| U-0          | U-0                                                             | U-0              | R/W-1 | U-0                                | U-0  | U-0                  | U-0   |

| —            | —                                                               | —                | ANSE4 | —                                  | —    | —                    | —     |

| bit 7        |                                                                 |                  |       |                                    |      |                      | bit 0 |

|              |                                                                 |                  |       |                                    |      |                      |       |

| Legend:      |                                                                 |                  |       |                                    |      |                      |       |

| R = Readab   | le bit                                                          | W = Writable bit |       | U = Unimplemented bit, read as '0' |      |                      |       |

| -n = Value a | t POR                                                           | '1' = Bit is set |       | '0' = Bit is clea                  | ared | x = Bit is unkno     | own   |

|              |                                                                 |                  |       |                                    |      |                      |       |

| bit 15-10    | Unimplemen                                                      | ted: Read as 'o  | )'    |                                    |      |                      |       |

| bit 9        | ANSE9: PORTE Analog Function Selection bit <sup>(1)</sup>       |                  |       |                                    |      |                      |       |

|              | 1 = Pin is configured in Analog mode; I/O port read is disabled |                  |       |                                    |      |                      |       |

|              | 0 = Pin is configured in Digital mode; I/O port read is enabled |                  |       |                                    |      |                      |       |

| bit 8-5      | Unimplemented: Read as '0'                                      |                  |       |                                    |      |                      |       |

| bit 4        | ANSE4: PORTE Analog Function Selection bit                      |                  |       |                                    |      |                      |       |

|              | - D' '                                                          | C                |       |                                    |      |                      |       |

- 1 = Pin is configured in Analog mode; I/O port read is disabled

0 = Pin is configured in Digital mode; I/O port read is enabled

- bit 3-0 Unimplemented: Read as '0'

- Note 1: ANSE9 is not available on 64-pin devices.

# REGISTER 11-6: ANSG: PORTG ANALOG FUNCTION SELECTION REGISTER

| U-0      | U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1 | R/W-1  |

|----------|--------|-----|-----|-----|-----|-------|--------|

| _        |        | —   | —   | —   | —   | ANSO  | 6<9:8> |

| bit 15   |        |     |     |     |     |       | bit 8  |

|          |        |     |     |     |     |       |        |

| R/W-1    | R/W-1  | U-0 | U-0 | U-0 | U-0 | U-0   | U-0    |

| ANSC     | G<7:6> | —   | —   | —   | —   | —     | —      |

| bit 7    |        |     |     |     |     |       | bit 0  |

|          |        |     |     |     |     |       |        |

| l egend. |        |     |     |     |     |       |        |

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-10 | Unimplemented: Read as '0'                                                                                                                                   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9-6   | ANSG<9:6>: PORTG Analog Function Selection bits                                                                                                              |

|           | <ul> <li>1 = Pin is configured in Analog mode; I/O port read is disabled</li> <li>0 = Pin is configured in Digital mode; I/O port read is enabled</li> </ul> |

| bit 5-0   | Unimplemented: Read as '0'                                                                                                                                   |

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | —   | U1CTSR5 | U1CTSR4 | U1CTSR3 | U1CTSR2 | U1CTSR1 | U1CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

|        |     |         |         |         |         |         |         |

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

# REGISTER 11-26: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-14 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 13-8  | U1CTSR<5:0>: Assign UART1 Clear-to-Send (U1CTS) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                            |

| bit 5-0   | U1RXR<5:0>: Assign UART1 Receive (U1RX) to Corresponding RPn or RPIn Pin bits         |

# REGISTER 11-27: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | U2CTSR5 | U2CTSR4 | U2CTSR3 | U2CTSR2 | U2CTSR1 | U2CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U2CTSR<5:0>: Assign UART2 Clear-to-Send (U2CTS) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 U2RXR<5:0>: Assign UART2 Receive (U2RX) to Corresponding RPn or RPIn Pin bits

| U-0    | U-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|--------|-----|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

|        | —   | RP5R5 <sup>(1)</sup> | RP5R4 <sup>(1)</sup> | RP5R3 <sup>(1)</sup> | RP5R2 <sup>(1)</sup> | RP5R1 <sup>(1)</sup> | RP5R0 <sup>(1)</sup> |

| bit 15 |     |                      |                      |                      |                      |                      | bit 8                |

|        |     |                      |                      |                      |                      |                      |                      |

| U-0    | U-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

| _      | —   | RP4R5                | RP4R4                | RP4R3                | RP4R2                | RP4R1                | RP4R0                |

| bit 7  |     |                      |                      |                      |                      |                      | bit 0                |

### REGISTER 11-38: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| Legend:           |                                                                    |                      |                    |  |

|-------------------|--------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                   | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP5R<5:0>: RP5 Output Pin Mapping bits <sup>(1)</sup>                                                |

|           | Peripheral Output Number n is assigned to pin, RP5 (see Table 11-4 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | RP4R<5:0>: RP4 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP4 (see Table 11-4 for peripheral function numbers). |

**Note 1:** This pin is not available on 64-pin devices.

# REGISTER 11-39: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| _      | _   | RP7R5 | RP7R4 | RP7R3 | RP7R2 | RP7R1 | RP7R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP6R5 | RP6R4 | RP6R3 | RP6R2 | RP6R1 | RP6R0 |

| bit 7  | •   |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP7R<5:0>: RP7 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP7 (see Table 11-4 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP6R<5:0>:** RP6 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP6 (see Table 11-4 for peripheral function numbers).

# REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters</li> </ul> |

| bit 5   | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Address Detect mode is enabled (if 9-bit mode is not selected, this does not take effect)</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                                                             |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                                                                                                                                                                                                       |

|         | 1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                                                                                                                                                                             |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Parity error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                            |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Framing error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                          |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed (clearing a previously set OERR bit, 1 → 0 transition); will reset the receive buffer and the RSR to the empty state</li> </ul>                                                                                                                                                                                  |

| bit 0   | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                                              |

| Note 1: | The value of this bit only affects the transmit properties of the module when the $IrDA^{\otimes}$ encoder is enabled (IREN = 1).                                                                                                                                                                                                                                                                          |

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

| U-0               | U-0                                                                                   | U-0                                   | U-0             | U-0               | U-0                                           | U-0             | U-0   |  |  |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------|---------------------------------------|-----------------|-------------------|-----------------------------------------------|-----------------|-------|--|--|--|--|--|--|--|--|

| _                 | —                                                                                     | _                                     | _               | _                 | —                                             | —               | _     |  |  |  |  |  |  |  |  |

| bit 15            |                                                                                       | ·                                     |                 |                   |                                               |                 | bit   |  |  |  |  |  |  |  |  |

|                   |                                                                                       |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| R/W-0             | U-0                                                                                   | R/W-0                                 | R/W-0           | R/W-0             | R/W-0                                         | R/W-0           | R/W-0 |  |  |  |  |  |  |  |  |

| BTSEE             | —                                                                                     | DMAEE                                 | BTOEE           | DFN8EE            | CRC16EE                                       | CRC5EE          | PIDEE |  |  |  |  |  |  |  |  |

|                   |                                                                                       |                                       |                 |                   |                                               | EOFEE           |       |  |  |  |  |  |  |  |  |

| bit 7             |                                                                                       |                                       |                 |                   |                                               |                 | bit   |  |  |  |  |  |  |  |  |

|                   |                                                                                       |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| Legend:           |                                                                                       |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| R = Readat        |                                                                                       | W = Writable                          |                 | •                 | nented bit, read                              |                 |       |  |  |  |  |  |  |  |  |

| -n = Value a      | at POR                                                                                | '1' = Bit is set                      |                 | '0' = Bit is clea | ared                                          | x = Bit is unkn | own   |  |  |  |  |  |  |  |  |

| hit 15 0          | Unimplome                                                                             | nted. Deed ee (                       | o'              |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| bit 15-8<br>bit 7 | -                                                                                     | nted: Read as '<br>Stuff Error Interr |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | 1 = Interrup                                                                          |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | 0 = Interrup                                                                          |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| bit 6             | Unimplemented: Read as '0'                                                            |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| bit 5             | DMAEE: DM                                                                             | A Error Interrup                      | t Enable bit    |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | 1 = Interrupt is enabled                                                              |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | 0 = Interrup                                                                          |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| bit 4             | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit                             |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | 1 = Interrup<br>0 = Interrup                                                          |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| bit 3             | -                                                                                     |                                       | ror Interrunt F | nable bit         |                                               |                 |       |  |  |  |  |  |  |  |  |

| bit o             | <b>DFN8EE:</b> Data Field Size Error Interrupt Enable bit<br>1 = Interrupt is enabled |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | 0 = Interrup                                                                          |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| bit 2             | CRC16EE: CRC16 Failure Interrupt Enable bit                                           |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | 1 = Interrup                                                                          |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | 0 = Interrup                                                                          |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| bit 1             | For Device r                                                                          |                                       | Interrunt Enab  | le hit            |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | CRC5EE: CRC5 Host Error Interrupt Enable bit<br>1 = Interrupt is enabled              |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | 0 = Interrupt is disabled                                                             |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | For Host mode:                                                                        |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   |                                                                                       | d-of-Frame (EOF                       | Error interru   | pt Enable bit     |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | 1 = Interrup<br>0 = Interrup                                                          |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

|                   | o inconup                                                                             |                                       |                 |                   |                                               |                 |       |  |  |  |  |  |  |  |  |

| bit 0             |                                                                                       | Check Failure In                      | nterrunt Enable | e hit             | PIDEE: PID Check Failure Interrupt Enable bit |                 |       |  |  |  |  |  |  |  |  |

| bit 0             |                                                                                       |                                       | nterrupt Enable | e bit             |                                               |                 |       |  |  |  |  |  |  |  |  |

# REGISTER 20-20: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

# PIC24FJ1024GA610/GB610 FAMILY

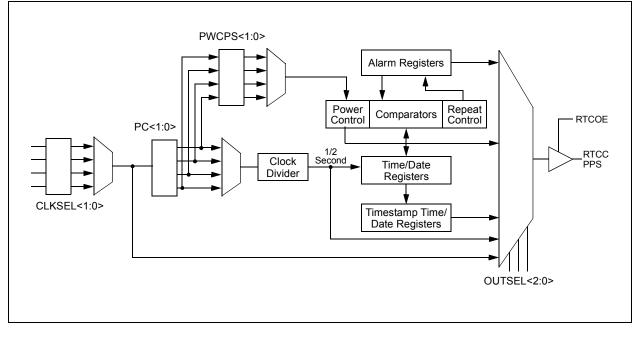

# FIGURE 22-1: RTCC BLOCK DIAGRAM

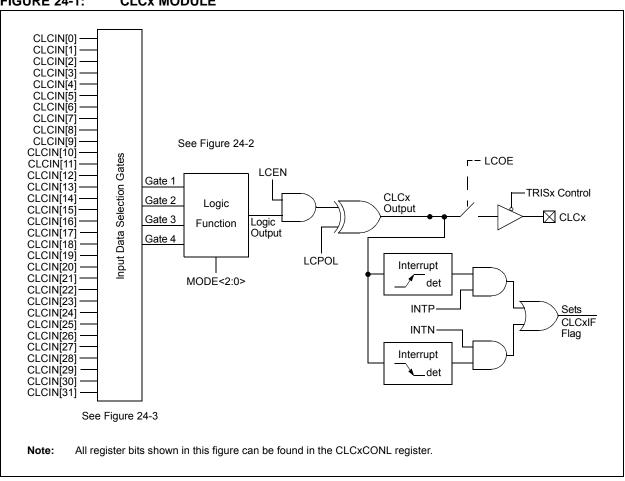

# 24.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins. This provides greater flexibility and potential in embedded designs, since the CLC module can operate outside the limitations of software execution and supports a vast amount of output designs.

There are four input gates to the selected logic function. These four input gates select from a pool of up to 32 signals that are selected using four data source selection multiplexers. Figure 24-1 shows an overview of the module. Figure 24-3 shows the details of the data source multiplexers and logic input gate connections.

#### FIGURE 24-1: **CLCx MODULE**

# 25.4 Achieving Maximum A/D Converter (ADC) Performance

In order to get the shortest overall conversion time (called the "throughput") while maintaining accuracy, several factors must be considered. These are described in detail below.

- Dependence of AVDD If the AVDD supply is < 2.7V, the Charge Pump Enable bit (PUMPEN, AD1CON3<13>) should be set to '1'. The input channel multiplexer has a varying resistance with AVDD (the lower AVDD, the higher the internal switch resistance). The charge pump provides a higher internal AVDD to keep the switch resistance as low as possible.

- Dependence on TAD The ADC timing is driven by TAD, not TCYC. Selecting the TAD time correctly is critical to getting the best ADC throughput. It is important to note that the overall ADC throughput is not simply the 'Conversion Time' of the SAR; it is the combination of the Conversion Time, the Sample Time and additional TAD delays for internal synchronization logic.

- Relationship between TCYC and TAD There is not a fixed 1:1 timing relationship between TCYC and TAD. The fastest possible throughput is fundamentally set by TAD (min), not by TCYC. The TAD time is set as a programmable integer multiple of TCYC by the ADCS<7:0> bits. Referring to Table 33-26, the TAD (min) time is greater than the 4 MHz period of the dedicated ADC RC clock generator. Therefore, TAD must be 2 TCYC in order to use the RC clock for fastest throughput. The TAD (min) is a multiple of 3.597 MHz as opposed to 4 MHz. To run as fast as possible, TCYC must be a multiple of TAD (min) because values of ADCSx are integers. For example, if a standard "color burst" crystal of 14.31818 MHz is used, TCYC is 279.4 ns, which is very close to TAD (min) and the ADC throughput is optimal. Running at 16 MHz will actually reduce the throughput, because TAD will have to be 500 ns as the TCYC of 250 ns violates TAD (min).

- Dependence on driving Source Resistance (Rs) Certain transducers have high output impedance (> 2.5 kΩ). Having a high Rs will require longer sampling time to charge the S/H capacitor through the resistance path (see Figure 25-3). The worst case scenario is a full-range voltage step of AVss to AVDD, with the sampling cap at AVSS. The capacitor time constant is (Rs + Ric + Rss) (CHOLD) and the sample time needs to be 6 time constants minimum (8 preferred). Since the ADC logic timing is TAD-based, the sample time (in TAD) must be long enough, over all conditions, to charge/discharge CHOLD. Do not assume one TAD is sufficient sample time; longer times may be required to achieve the accuracy needed by the application. The value of CHOLD is 40 pF.

A small amount of charge is present at the ADC input pin when the sample switch is closed. If Rs is high, this will generate a DC error exceeding 1 LSB. Keeping Rs < 50 $\Omega$  is recommenced for best results. The error can also be reduced by increasing sample time (a 2 k $\Omega$  value of Rs requires a 3  $\mu$ S sample time to eliminate the error).

• Calculating Throughput – The throughput of the ADC is based on TAD. The throughput is given by:

$$Throughput = \left(\frac{l}{Sample Time + SAR Conversion Time + Clock Sync Time}\right)$$

where:

*Sample Time* is the calculated TAD periods for the application.

*SAR Conversion Time* is 12 TAD for 10-bit and 14 TAD for 12-bit conversions.

*Clock Sync Time* is 2.5 TAD (worst case scenario).

For example, using an 8 MHz FRC means the TCYC = 250 ns. This requires: TAD = 2 TCYC = 500 ns.Therefore, the throughput is:

$$Throughput = \left(\frac{1}{500 \text{ ns} + 14 \cdot 500 \text{ ns} + 2.5 \cdot 500 \text{ ns}}\right) = 114.28 \text{ KS/sec}$$

Note that the clock sync delay could be as little as 1.5 TAD, which could produce 121 KS/sec, but that cannot be ensured as the timing relationship is asynchronous and not specified. The worst case timing of 2.5 TAD should be used to calculate throughput.

For example, if a certain transducer has a 20 k $\Omega$  output impedance, the maximum sample time is determined by:

Sample Time =

$$6 \cdot (RS + RIC + RSS) \cdot CHOLD$$

=  $6 \cdot (20K + 250 + 350) \cdot 40 \, pF$

=  $4.95 \, \mu S$

If TAD = 500 ns, this requires a Sample Time of 4.95 us/500 ns = 10 TAD (for a full-step voltage on the transducer output).

| R/W-0         | U-0                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0           | R/W-0            | R/W-0             | R/W-0           | R/W-0   |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-------------------|-----------------|---------|--|--|--|

| CTMUEN        | — —                                                                                                                                            | CTMUSIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TGEN            | EDGEN            | EDGSEQEN          | IDISSEN         | CTTRIG  |  |  |  |

| bit 15        |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                  | <u> </u>          |                 | bit 8   |  |  |  |

|               |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                  |                   |                 |         |  |  |  |

| R/W-0         | R/W-0                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0           | R/W-0            | R/W-0             | R/W-0           | R/W-0   |  |  |  |

| ITRIM5        | ITRIM4                                                                                                                                         | ITRIM3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ITRIM2          | ITRIM1           | ITRIM0            | IRNG1           | IRNG0   |  |  |  |

| bit 7         |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                  |                   |                 | bit (   |  |  |  |

| Legend:       |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                  |                   |                 |         |  |  |  |

| R = Readable  | e bit                                                                                                                                          | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit             | U = Unimplei     | mented bit, read  | as '0'          |         |  |  |  |

| -n = Value at | POR                                                                                                                                            | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 | '0' = Bit is cle |                   | x = Bit is unkn | own     |  |  |  |

|               |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                  |                   |                 |         |  |  |  |

| bit 15        | CTMUEN: C                                                                                                                                      | TMU Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                  |                   |                 |         |  |  |  |

|               | 1 = Module is                                                                                                                                  | s enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                  |                   |                 |         |  |  |  |

|               | 0 = Module is                                                                                                                                  | s disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                  |                   |                 |         |  |  |  |

| bit 14        | Unimplemer                                                                                                                                     | nted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ,               |                  |                   |                 |         |  |  |  |

| bit 13        | CTMUSIDL:                                                                                                                                      | CTMU Stop in Id                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | dle Mode bit    |                  |                   |                 |         |  |  |  |

|               |                                                                                                                                                | ues module operations module operations module operations and the second s |                 |                  | lle mode          |                 |         |  |  |  |