Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | PIC                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 32MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 1MB (341.5K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj1024gb606t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                                                               | PIC24FJ128GX606                                                                                                                                                | PIC24FJ256GX606 | PIC24FJ512GX606 | PIC24FJ1024GX606 |  |  |  |  |  |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------------------|--|--|--|--|--|

| Operating Frequency                                                    | DC – 32 MHz                                                                                                                                                    |                 |                 |                  |  |  |  |  |  |

| Program Memory (bytes)                                                 | 128K                                                                                                                                                           | 256K            | 512K            | 1024K            |  |  |  |  |  |

| Program Memory (instructions)                                          | 44,032                                                                                                                                                         | 88,064          | 176,128         | 352,256          |  |  |  |  |  |

| Data Memory (bytes)                                                    |                                                                                                                                                                | 3               | 2K              |                  |  |  |  |  |  |

| Interrupt Sources (soft vectors/<br>NMI traps)                         |                                                                                                                                                                | 103             | (97/6)          |                  |  |  |  |  |  |

| I/O Ports                                                              | Ports B, C, D, E, F, G                                                                                                                                         |                 |                 |                  |  |  |  |  |  |

| Total I/O Pins                                                         |                                                                                                                                                                | {               | 53              |                  |  |  |  |  |  |

| Remappable Pins                                                        |                                                                                                                                                                | 29 (28 I/O,     | 1 input only)   |                  |  |  |  |  |  |

| Timers:<br>Total Number (16-bit)                                       |                                                                                                                                                                | 5               | .(1)            |                  |  |  |  |  |  |

| 32-Bit (from paired 16-bit timers)                                     |                                                                                                                                                                |                 | 2               |                  |  |  |  |  |  |

| Input Capture Channels                                                 |                                                                                                                                                                | 6               | (1)             |                  |  |  |  |  |  |

| Output Compare/PWM Channels                                            |                                                                                                                                                                | 6               | (1)             |                  |  |  |  |  |  |

| Input Change Notification Interrupt                                    |                                                                                                                                                                | ł               | 53              |                  |  |  |  |  |  |

| Serial Communications:<br>UART                                         | 6 <sup>(1)</sup>                                                                                                                                               |                 |                 |                  |  |  |  |  |  |

| SPI (3-wire/4-wire)                                                    | 3(1)                                                                                                                                                           |                 |                 |                  |  |  |  |  |  |

| I <sup>2</sup> C                                                       |                                                                                                                                                                |                 | 3               |                  |  |  |  |  |  |

| Configurable Logic Cell (CLC)                                          |                                                                                                                                                                | 4               | (1)             |                  |  |  |  |  |  |

| Parallel Communications<br>(EPMP/PSP)                                  |                                                                                                                                                                | Y               | <i>ï</i> es     |                  |  |  |  |  |  |

| Capture/Compare/PWM/Timer<br>Modules                                   | 3 Multiple Outputs and 4 Single Outputs                                                                                                                        |                 |                 |                  |  |  |  |  |  |

| JTAG Boundary Scan                                                     | Yes                                                                                                                                                            |                 |                 |                  |  |  |  |  |  |

| 12/10-Bit Analog-to-Digital Converter<br>(A/D) Module (input channels) |                                                                                                                                                                |                 | 16              |                  |  |  |  |  |  |

| Analog Comparators                                                     |                                                                                                                                                                |                 | 3               |                  |  |  |  |  |  |

| CTMU Interface                                                         |                                                                                                                                                                | Y               | <i>ï</i> es     |                  |  |  |  |  |  |

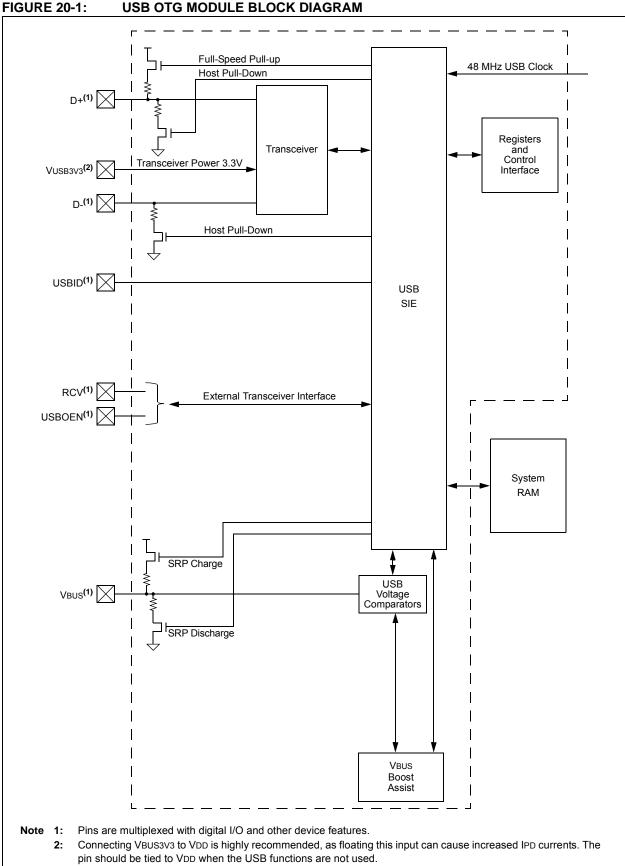

| Universal Serial Bus Controller                                        | Yes (PIC24FJ1024GB606 devices only)                                                                                                                            |                 |                 |                  |  |  |  |  |  |

| Resets (and Delays)                                                    | Core POR, VDD POR, BOR, RESET Instruction,<br>MCLR, WDT, Illegal Opcode, REPEAT Instruction,<br>Hardware Traps, Configuration Word Mismatch<br>(OST, PLL Lock) |                 |                 |                  |  |  |  |  |  |

| Instruction Set                                                        | 76 Base Instructions, Multiple Addressing Mode Variations                                                                                                      |                 |                 |                  |  |  |  |  |  |

| Packages                                                               |                                                                                                                                                                | 64-Pin TQI      | FP and QFN      |                  |  |  |  |  |  |

## TABLE 1-1:DEVICE FEATURES FOR THE PIC24FJ1024GA606/GB606: 64-PIN DEVICES

**Note 1:** Some peripherals are accessible through remappable pins.

|                 |                                     | Pin N                                                                 | umber/Gri | d Locator               |     |                 |             |        |                    |

|-----------------|-------------------------------------|-----------------------------------------------------------------------|-----------|-------------------------|-----|-----------------|-------------|--------|--------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | 64-Pin 64-Pin QFN/<br>FN/TQFP/ 64-Pin QFN/<br>TQFP/ TQFP/ TQFP/ BGA B |           | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer | Description |        |                    |

| RA0             | _                                   | —                                                                     | 17        | 17                      | G3  | G3              | I/O         | DIG/ST | PORTA Digital I/Os |

| RA1             | _                                   | _                                                                     | 38        | 38                      | J6  | J6              | I/O         | DIG/ST |                    |

| RA2             | _                                   | _                                                                     | 58        | 58                      | H11 | H11             | I/O         | DIG/ST |                    |

| RA3             | _                                   | _                                                                     | 59        | 59                      | G10 | G10             | I/O         | DIG/ST |                    |

| RA4             | _                                   | _                                                                     | 60        | 60                      | G11 | G11             | I/O         | DIG/ST |                    |

| RA5             | _                                   | _                                                                     | 61        | 61                      | G9  | G9              | I/O         | DIG/ST |                    |

| RA6             | _                                   | —                                                                     | 91        | 91                      | C5  | C5              | I/O         | DIG/ST |                    |

| RA7             | _                                   | _                                                                     | 92        | 92                      | B5  | B5              | I/O         | DIG/ST |                    |

| RA9             | _                                   | —                                                                     | 28        | 28                      | L2  | L2              | I/O         | DIG/ST |                    |

| RA10            | _                                   | _                                                                     | 29        | 29                      | K3  | K3              | I/O         | DIG/ST |                    |

| RA14            | _                                   | _                                                                     | 66        | 66                      | E11 | E11             | I/O         | DIG/ST |                    |

| RA15            | _                                   | —                                                                     | 67        | 67                      | E8  | E8              | I/O         | DIG/ST |                    |

| RB0             | 16                                  | 16                                                                    | 25        | 25                      | K2  | K2              | I/O         | DIG/ST | PORTB Digital I/Os |

| RB1             | 15                                  | 15                                                                    | 24        | 24                      | K1  | K1              | I/O         | DIG/ST |                    |

| RB2             | 14                                  | 14                                                                    | 23        | 23                      | J2  | J2              | I/O         | DIG/ST |                    |

| RB3             | 13                                  | 13                                                                    | 22        | 22                      | J1  | J1              | I/O         | DIG/ST |                    |

| RB4             | 12                                  | 12                                                                    | 21        | 21                      | H2  | H2              | I/O         | DIG/ST |                    |

| RB5             | 11                                  | 11                                                                    | 20        | 20                      | H1  | H1              | I/O         | DIG/ST |                    |

| RB6             | 17                                  | 17                                                                    | 26        | 26                      | L1  | L1              | I/O         | DIG/ST |                    |

| RB7             | 18                                  | 18                                                                    | 27        | 27                      | J3  | J3              | I/O         | DIG/ST |                    |

| RB8             | 21                                  | 21                                                                    | 32        | 32                      | K4  | K4              | I/O         | DIG/ST |                    |

| RB9             | 22                                  | 22                                                                    | 33        | 33                      | L4  | L4              | I/O         | DIG/ST |                    |

| RB10            | 23                                  | 23                                                                    | 34        | 34                      | L5  | L5              | I/O         | DIG/ST |                    |

| RB11            | 24                                  | 24                                                                    | 35        | 35                      | J5  | J5              | I/O         | DIG/ST |                    |

| RB12            | 27                                  | 27                                                                    | 41        | 41                      | J7  | J7              | I/O         | DIG/ST |                    |

| RB13            | 28                                  | 28                                                                    | 42        | 42                      | L7  | L7              | I/O         | DIG/ST |                    |

| RB14            | 29                                  | 29                                                                    | 43        | 43                      | K7  | K7              | I/O         | DIG/ST |                    |

| RB15            | 30                                  | 30                                                                    | 44        | 44                      | L8  | L8              | I/O         | DIG/ST |                    |

| RC1             | _                                   | _                                                                     | 6         | 6                       | D1  | D1              | I/O         | DIG/ST | PORTC Digital I/Os |

| RC2             | _                                   | _                                                                     | 7         | 7                       | E4  | E4              | I/O         | DIG/ST |                    |

| RC3             | —                                   | _                                                                     | 8         | 8                       | E2  | E2              | I/O         | DIG/ST |                    |

| RC4             | -                                   | _                                                                     | 9         | 9                       | E1  | E1              | I/O         | DIG/ST |                    |

| RC12            | 39                                  | 39                                                                    | 63        | 63                      | F9  | F9              | I/O         | DIG/ST |                    |

| RC13            | 47                                  | 47                                                                    | 73        | 73                      | C10 | C10             | I/O         | DIG/ST |                    |

| RC14            | 48                                  | 48                                                                    | 74        | 74                      | B11 | B11             | I/O         | DIG/ST |                    |

| RC15            | 40                                  | 40                                                                    | 64        | 64                      | F11 | F11             | I/O         | DIG/ST |                    |

#### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated Transceiver

## 2.4 Voltage Regulator Pin (VCAP)

Note: This section applies only to PIC24FJ devices with an on-chip voltage regulator.

Refer to **Section 30.3** "**On-Chip Voltage Regulator**" for details on connecting and using the on-chip regulator.

A low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

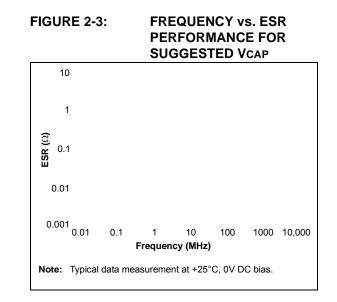

Designers may use Figure 2-3 to evaluate the ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 33.0** "**Electrical Characteristics**" for additional information.

## TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS (0805 CASE SIZE)

| Make   | Part #                  | Nominal<br>Capacitance | Base Tolerance | Rated Voltage |

|--------|-------------------------|------------------------|----------------|---------------|

| TDK    | TDK C2012X5R1E106K085AC |                        | ±10%           | 25V           |

| TDK    | C2012X5R1C106K085AC     | 10 µF                  | ±10%           | 16V           |

| Kemet  | C0805C106M4PACTU        | 10 µF                  | ±10%           | 16V           |

| Murata | GRM21BR61E106KA3L       | 10 µF                  | ±10%           | 25V           |

| Murata | GRM21BR61C106KE15       | 10 µF                  | ±10%           | 16V           |

| U-0    | U-0 | U-0 | U-0 | U-0                 | U-0                | U-0 | U-0   |

|--------|-----|-----|-----|---------------------|--------------------|-----|-------|

| —      | —   | —   | —   | —                   | —                  | —   | —     |

| bit 15 |     |     |     |                     |                    |     | bit 8 |

|        |     |     |     |                     |                    |     |       |

| U-0    | U-0 | U-0 | U-0 | R/C-0               | R/W-1              | U-0 | U-0   |

| —      | —   | —   | —   | IPL3 <sup>(1)</sup> | PSV <sup>(2)</sup> | —   | —     |

| bit 7  |     |     |     |                     |                    |     | bit 0 |

|        |     |     |     |                     |                    |     |       |

| REGISTER 3-2: CORCON: CPU CORE CONTROL REGISTER |

|-------------------------------------------------|

|-------------------------------------------------|

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

| bit 2    | PSV: Program Space Visibility (PSV) in Data Space Enable                                                                      |

|          | <ul> <li>1 = Program space is visible in Data Space</li> <li>0 = Program space is not visible in Data Space</li> </ul>        |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

- **Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level; see Register 3-1 for bit description.

- 2: If PSV = 0, any reads from data memory at 0x8000 and above will cause an address trap error instead of reading from the PSV section of program memory. This bit is not individually addressable.

# **10.0 POWER-SAVING FEATURES**

| Note: | This data sheet summarizes the features<br>of this group of PIC24F devices. It is not<br>intended to be a comprehensive refer-<br>ence source. For more information, refer<br>to the <i>"dsPIC33/PIC24 Family Reference</i> |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Manual", "Power-Saving Features"<br>(DS39698), which is available from the<br>Microchip web site (www.microchip.com).<br>The information in this data sheet<br>supersedes the information in the FRM.                       |

The PIC24FJ1024GA610/GB610 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- · Instruction-Based Sleep and Idle modes

- Software-Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

## 10.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0** "Oscillator Configuration".

## 10.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

The XC16 C compiler offers "built-in" functions for the power-saving modes as follows:

| Idle();  | // | places | part | in | Idle  |  |

|----------|----|--------|------|----|-------|--|

| Sleep(); | 11 | places | part | in | Sleep |  |

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

#### 10.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items, such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

The device will wake-up from Sleep mode on any of the these events:

- On any interrupt source that is individually enabled

- On any form of device Reset

- On a WDT time-out

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; | Put | the | device | into | SLEEP mode |

|--------|-------------|---|-----|-----|--------|------|------------|

| PWRSAV | #IDLE_MODE  | ; | Put | the | device | into | IDLE mode  |

# PIC24FJ1024GA610/GB610 FAMILY

#### REGISTER 10-6: PMD6: PERIPHERAL MODULE DISABLE REGISTER 6

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 15 |     |     |     |     |     |     | bit 8  |

|        |     |     |     |     |     |     |        |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

| _      | —   | —   | —   | —   | —   | —   | SPI3MD |

bit 7

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 SPI3MD: SPI3 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

#### REGISTER 10-7: PMD7: PERIPHERAL MODULE DISABLE REGISTER 7

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0   |

|-------|-----|--------|--------|-----|-----|-----|-------|

| —     | —   | DMA1MD | DMA0MD | —   | —   | —   | —     |

| bit 7 |     |        |        |     |     |     | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as 'O'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-6 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 5    | DMA1MD: DMA1 Controller (Channels 4 through 7) Disable bit |

|          | 1 = Controller is disabled                                 |

|          | 0 = Controller power and clock sources are enabled         |

| bit 4    | DMA0MD: DMA0 Controller (Channels 0 through 3) Disable bit |

|          | 1 = Controller is disabled                                 |

|          | 0 = Controller power and clock sources are enabled         |

| hit 2 0  | Unimplemented, Dood op (o)                                 |

bit 3-0 Unimplemented: Read as '0'

bit 0

## 11.4.3.3 Mapping Limitations

The control schema of the Peripheral Pin Select is extremely flexible. Other than systematic blocks that prevent signal contention, caused by two physical pins being configured as the same functional input or two functional outputs configured as the same pin, there are no hardware enforced lockouts. The flexibility extends to the point of allowing a single input to drive multiple peripherals or a single functional output to drive multiple output pins.

#### 11.4.3.4 Mapping Exceptions for PIC24FJ1024GA610/GB610 Family Devices

Although the PPS registers theoretically allow for inputs to be remapped to up to 64 pins, or for outputs to be remapped from 32 pins, not all of these are implemented in all devices. For 100-pin or 121-pin variants of the PIC24FJ1024GA610/GB610 family devices, 32 remappable input/output pins are available and 12 remappable input pins are available. For 64-pin variants, 29 input/outputs and 1 input are available. The differences in available remappable pins are summarized in Table 11-5.

When developing applications that use remappable pins, users should also keep these things in mind:

- For the RPINRx registers, bit combinations corresponding to an unimplemented pin for a particular device are treated as invalid; the corresponding module will not have an input mapped to it.

- For RPORx registers, the bit fields corresponding to an unimplemented pin will also be unimplemented; writing to these fields will have no effect.

#### 11.4.4 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24F devices include three features to prevent alterations to the peripheral map:

- · Control register lock sequence

- · Continuous state monitoring

- · Configuration bit remapping lock

## 11.4.4.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 46h to OSCCON<7:0>.

- 2. Write 57h to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

#### 11.4.4.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

## 11.4.4.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows users unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

| Device          |       | RPn Pins (I/O)        |       | RPIn Pins        |

|-----------------|-------|-----------------------|-------|------------------|

| Device          | Total | Unimplemented         | Total | Unimplemented    |

| PIC24FJXXXGB606 | 28    | RP5, RP15, RP30, RP31 | 1     | All except RPI37 |

| PIC24FJXXXGX61X | 32    | —                     | 12    | —                |

| PIC24FJXXXGA606 | 29    | RP5, RP15, RP31       | 1     | All except RPI37 |

#### TABLE 11-5: REMAPPABLE PIN EXCEPTIONS FOR PIC24FJ1024GA610/GB610 FAMILY DEVICES

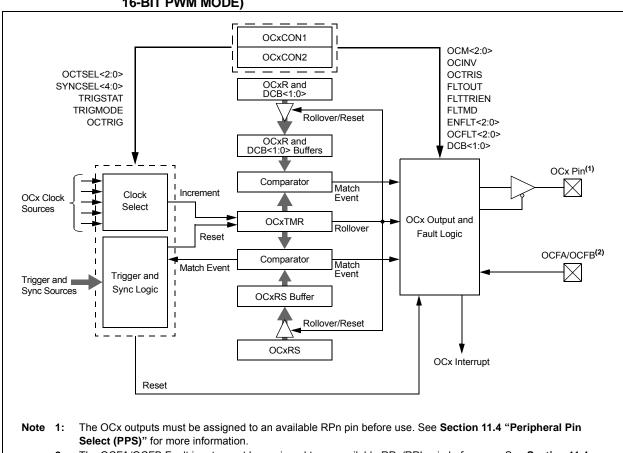

# FIGURE 15-2: OUTPUT COMPARE x BLOCK DIAGRAM (DOUBLE-BUFFERED, 16-BIT PWM MODE)

2: The OCFA/OCFB Fault inputs must be assigned to an available RPn/RPIn pin before use. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

#### 15.3.1 PWM PERIOD

The PWM period is specified by writing to PRy, the Timer Period register. The PWM period can be calculated using Equation 15-1.

## EQUATION 15-1: CALCULATING THE PWM PERIOD<sup>(1)</sup>

PWM Period =  $[(PRy) + 1 \bullet TCY \bullet (Timer Prescale Value)]$

Where: PWM Frequency = 1/[PWM Period]

**Note 1:** Based on TCY = TOSC \* 2; Doze mode and PLL are disabled.

**Note:** A PRy value of N will produce a PWM period of N + 1 time base count cycles. For example, a value of 7, written into the PRy register, will yield a period consisting of 8 time base cycles.

# 17.1 Master Mode Operation

Perform the following steps to set up the SPIx module for Master mode operation:

- 1. Disable the SPIx interrupts in the respective IECx register.

- 2. Stop and reset the SPIx module by clearing the SPIEN bit.

- 3. Clear the receive buffer.

- Clear the ENHBUF bit (SPIxCON1L<0>) if using Standard Buffer mode or set the bit if using Enhanced Buffer mode.

- 5. If SPIx interrupts are not going to be used, skip this step. Otherwise, the following additional steps are performed:

- a) Clear the SPIx interrupt flags/events in the respective IFSx register.

- b) Write the SPIx interrupt priority and sub-priority bits in the respective IPCx register.

- c) Set the SPIx interrupt enable bits in the respective IECx register.

- 6. Write the Baud Rate register, SPIxBRGL.

- 7. Clear the SPIROV bit (SPIxSTATL<6>).

- 8. Write the desired settings to the SPIxCON1L register with MSTEN (SPIxCON1L<5>) = 1.

- Enable SPI operation by setting the SPIEN bit (SPIxCON1L<15>).

- 10. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL/H registers.

# 17.2 Slave Mode Operation

The following steps are used to set up the SPIx module for the Slave mode of operation:

- 1. If using interrupts, disable the SPIx interrupts in the respective IECx register.

- 2. Stop and reset the SPIx module by clearing the SPIEN bit.

- 3. Clear the receive buffer.

- Clear the ENHBUF bit (SPIxCON1L<0>) if using Standard Buffer mode or set the bit if using Enhanced Buffer mode.

- 5. If using interrupts, the following additional steps are performed:

- a) Clear the SPIx interrupt flags/events in the respective IFSx register.

- b) Write the SPIx interrupt priority and subpriority bits in the respective IPCx register.

- c) Set the SPIx interrupt enable bits in the respective IECx register.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Write the desired settings to the SPIxCON1L register with MSTEN (SPIxCON1L<5>) = 0.

- Enable SPI operation by setting the SPIEN bit (SPIxCON1L<15>).

- 9. Transmission (and reception) will start as soon as the master provides the serial clock.

The following additional features are provided in Slave mode:

- Slave Select Synchronization:

- The SSx pin allows a Synchronous Slave mode. If the SSEN bit (SPIxCON1L<7>) is set, transmission and reception are enabled in Slave mode only if the SSx pin is driven to a low state. The port output or other peripheral outputs must not be driven in order to allow the SSx pin to function as an input. If the SSEN bit is set and the SSx pin is driven high, the SDOx pin is no longer driven and will tri-state, even if the module is in the middle of a transmission. An aborted transmission will be tried again the next time the SSx pin is driven low using the data held in the SPIxTXB register. If the SSEN bit is not set, the SSx pin does not affect the module operation in Slave mode.

- SPITBE Status Flag Operation: The SPITBE bit (SPIxSTATL<3>) has a different function in the Slave mode of operation. The following describes the function of SPITBE for various settings of the Slave mode of operation:

- If SSEN (SPIxCON1L<7>) is cleared, the SPITBE bit is cleared when SPIxBUF is loaded by the user code. It is set when the module transfers SPIxTXB to SPIxTXSR. This is similar to the SPITBE bit function in Master mode.

- If SSEN is set, SPITBE is cleared when SPIxBUF is loaded by the user code. However, it is set only when the SPIx module completes data transmission. A transmission will be aborted when the SSx pin goes high and may be retried at a later time. So, each data word is held in SPIxTXB until all bits are transmitted to the receiver.

#### REGISTER 17-6: SPIxBUFL: SPIx BUFFER REGISTER LOW

| R/W-0                              | R/W-0 | R/W-0                              | R/W-0              | R/W-0   | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|------------------------------------|--------------------|---------|-----------------|-------|-------|

|                                    |       |                                    | DAT                | A<15:8> |                 |       |       |

| bit 15                             |       |                                    |                    |         |                 |       | bit 8 |

|                                    |       |                                    |                    |         |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0                              | R/W-0              | R/W-0   | R/W-0           | R/W-0 | R/W-0 |

|                                    |       |                                    | DA                 | TA<7:0> |                 |       |       |

| bit 7                              |       |                                    |                    |         |                 |       | bit 0 |

|                                    |       |                                    |                    |         |                 |       |       |

| Legend:                            |       |                                    |                    |         |                 |       |       |

| R = Readable bit W = Writable bit  |       | U = Unimplemented bit, read as '0' |                    |         | as '0'          |       |       |

| -n = Value at POR '1' = Bit is set |       |                                    | '0' = Bit is clear | red     | x = Bit is unkr | nown  |       |

#### bit 15-0 DATA<15:0>: SPIx FIFO Data bits

When the MODE<32,16> or WLENGTH<4:0> bits select 16 to 9-bit data, the SPIx only uses DATA<15:0>. When the MODE<32,16> or WLENGTH<4:0> bits select 8 to 2-bit data, the SPIx only uses DATA<7:0>.

#### REGISTER 17-7: SPIxBUFH: SPIx BUFFER REGISTER HIGH

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-----------------------------------------|-------|----------|-------|-------|-------|

|                                    |       |                                         | DAT   | A<31:24> |       |       |       |

| bit 15                             |       |                                         |       |          |       |       | bit 8 |

|                                    |       |                                         |       |          |       |       |       |

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |                                         | DAT   | A<23:16> |       |       |       |

| bit 7                              |       |                                         |       |          |       |       | bit 0 |

|                                    |       |                                         |       |          |       |       |       |

| Legend:                            |       |                                         |       |          |       |       |       |

| R = Readable bit W = Writable bit  |       | U = Unimplemented bit, read as '0'      |       |          |       |       |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |          |       | nown  |       |

#### bit 15-0 DATA<31:16>: SPIx FIFO Data bits

When the MODE<32,16> or WLENGTH<4:0> bits select 32 to 25-bit data, the SPIx uses DATA<31:16>. When the MODE<32,16> or WLENGTH<4:0> bits select 24 to 17-bit data, the SPIx only uses DATA<23:16>.

| R/W-0              | U-0                                                  | R/W-0                                                                  | R/W-0                         | R/W-0                                 | R/W-0                   | R/W-0                 | R/W-0                 |

|--------------------|------------------------------------------------------|------------------------------------------------------------------------|-------------------------------|---------------------------------------|-------------------------|-----------------------|-----------------------|

| RXWIEN             | —                                                    | RXMSK5 <sup>(1)</sup>                                                  | RXMSK4 <sup>(1,4)</sup>       | RXMSK3 <sup>(1,3)</sup>               | RXMSK2 <sup>(1,2)</sup> | RXMSK1 <sup>(1)</sup> | RXMSK0 <sup>(1)</sup> |

| bit 15             |                                                      | ·                                                                      |                               |                                       | •                       |                       | bit 8                 |

|                    |                                                      |                                                                        |                               |                                       |                         |                       |                       |

| R/W-0              | U-0                                                  | R/W-0                                                                  | R/W-0                         | R/W-0                                 | R/W-0                   | R/W-0                 | R/W-0                 |

| TXWIEN             | —                                                    | TXMSK5 <sup>(1)</sup>                                                  | TXMSK4 <sup>(1,4)</sup>       | TXMSK3 <sup>(1,3)</sup>               | TXMSK2 <sup>(1,2)</sup> | TXMSK1 <sup>(1)</sup> | TXMSK0 <sup>(1)</sup> |

| bit 7              |                                                      |                                                                        |                               |                                       |                         |                       | bit (                 |

| Legend:            |                                                      |                                                                        |                               |                                       |                         |                       |                       |

| R = Reada          | able bit                                             | W = Writable                                                           | bit                           | U = Unimpleme                         | nted bit, read as       | ʻ0'                   |                       |

| -n = Value         | at POR                                               | '1' = Bit is set                                                       | :                             | '0' = Bit is cleare                   | ed                      | x = Bit is unkn       | own                   |

| bit 14<br>bit 13-8 | RXMSK<5                                              | ented: Read as<br>:0>: RX Buffer                                       | Mask bits <sup>(1,2,3,4</sup> |                                       |                         |                       |                       |

|                    |                                                      | oits; used in con                                                      | -                             |                                       |                         |                       |                       |

| bit 7              |                                                      | Transmit Waterr                                                        |                               |                                       |                         |                       | _                     |

|                    |                                                      | rs transmit buffe<br>es transmit buffe                                 |                               | rmark interrupt w<br>ermark interrupt | /hen TXMSK<5:(          | )> = TXELM<5:         | 0>                    |

| bit 6              | Unimplem                                             | ented: Read as                                                         | <b>s</b> 'O'                  |                                       |                         |                       |                       |

| bit 5-0            | TXMSK<5:0>: TX Buffer Mask bits <sup>(1,2,3,4)</sup> |                                                                        |                               |                                       |                         |                       |                       |

|                    | TX mask b                                            | its; used in conj                                                      | junction with the             | e TXWIEN bit.                         |                         |                       |                       |

| Note 1:            | Mask values this case.                               | s higher than Fl                                                       | FODEPTH are                   | not valid. The m                      | odule will not tri      | gger a match fo       | or any value in       |

| 2:                 | RXMSK2 ar                                            | nd TXMSK2 bits                                                         | are only prese                | nt when FIFODE                        | PTH = 8 or high         | er.                   |                       |

| 3:                 | RXMSK3 ar                                            | RXMSK3 and TXMSK3 bits are only present when FIFODEPTH = 16 or higher. |                               |                                       |                         |                       |                       |

|                    |                                                      |                                                                        |                               |                                       |                         |                       |                       |

## REGISTER 17-10: SPIxIMSKH: SPIx INTERRUPT MASK REGISTER HIGH

**4:** RXMSK4 and TXMSK4 bits are only present when FIFODEPTH = 32.

# PIC24FJ1024GA610/GB610 FAMILY

DS30010074D-page 266

## REGISTER 20-13: U1CNFG2: USB CONFIGURATION REGISTER 2

| U-0          | U-0                               | U-0           | U-0      | U-0                                | U-0  | U-0             | U-0   |

|--------------|-----------------------------------|---------------|----------|------------------------------------|------|-----------------|-------|

| _            | —                                 | —             | —        | —                                  | —    | —               | —     |

| bit 15       |                                   |               |          |                                    |      |                 | bit 8 |

|              |                                   |               |          |                                    |      |                 |       |

| U-0          | U-0                               | U-0           | R/W-0    | R/W-0                              | U-0  | U-0             | U-0   |

| —            | —                                 | _             | PUVBUS   | EXTI2CEN                           | —    | —               | —     |

| bit 7        | ·                                 |               |          |                                    |      |                 | bit 0 |

|              |                                   |               |          |                                    |      |                 |       |

| Legend:      |                                   |               |          |                                    |      |                 |       |

| R = Readab   | le bit                            | W = Writable  | bit      | U = Unimplemented bit, read as '0' |      |                 |       |

| -n = Value a | n = Value at POR '1' = Bit is set |               | t        | '0' = Bit is clea                  | ared | x = Bit is unkn | own   |

|              |                                   |               |          |                                    |      |                 |       |

| bit 15-5     | Unimplemen                        | ted: Read as  | 0'       |                                    |      |                 |       |

| bit 4        | PUVBUS: VB                        | us Pull-Up En | able bit |                                    |      |                 |       |

|              | 1 = Pullun on Veus nin is enabled |               |          |                                    |      |                 |       |

- 1 = Pull-up on VBUS pin is enabled 0 = Pull-up on VBUS pin is disabled

- bit 3 **EXTI2CEN:** I<sup>2</sup>C Interface for External Module Control Enable bit

- 1 = External module(s) is controlled via the  $I^2C$  interface

- 0 = External module(s) is controlled via the dedicated pins

- bit 2-0 Unimplemented: Read as '0'

| R-0, HSC               | U-0                               | R/C-0, HS                           | R/C-0, HS              | U-0                    | U-0                       | U-0                    | U-0                    |

|------------------------|-----------------------------------|-------------------------------------|------------------------|------------------------|---------------------------|------------------------|------------------------|

| BUSY                   | —                                 | ERROR                               | TIMEOUT                | —                      | —                         | —                      | —                      |

| bit 15                 |                                   |                                     |                        |                        |                           |                        | bit 8                  |

|                        |                                   |                                     |                        |                        |                           |                        |                        |

| R/W-0                  | R/W-0                             | R/W-0                               | R/W-0                  | R/W-0                  | R/W-0                     | R/W-0                  | R/W-0                  |

| RADDR23 <sup>(1)</sup> | RADDR22 <sup>(1)</sup>            | RADDR21 <sup>(1)</sup>              | RADDR20 <sup>(1)</sup> | RADDR19 <sup>(1)</sup> | RADDR18 <sup>(1)</sup>    | RADDR17 <sup>(1)</sup> | RADDR16 <sup>(1)</sup> |

| bit 7                  |                                   |                                     |                        |                        |                           |                        | bit C                  |

|                        |                                   |                                     |                        |                        |                           |                        |                        |

| Legend:                | 1.11                              |                                     |                        |                        |                           | 0                      |                        |

| R = Readable           |                                   | W = Writable I                      | DIT                    |                        | ented, read as '          |                        |                        |

| -n = Value at F        |                                   | '1' = Bit is set                    |                        |                        |                           | own                    |                        |

| C = Clearable          | bit                               | HS = Hardward                       | e Settable bit         | HSC = Hardw            | are Settable/Cl           | earable bit            |                        |

| bit 15                 | BUSY: Busy bit (Master mode only) |                                     |                        |                        |                           |                        |                        |

|                        | 1 = Port is bu                    | sy                                  |                        |                        |                           |                        |                        |

|                        | 0 = Port is no                    | t busy                              |                        |                        |                           |                        |                        |

| bit 14                 | Unimplement                       | ted: Read as 'o                     | )'                     |                        |                           |                        |                        |

| bit 13                 | ERROR: Error                      | r bit                               |                        |                        |                           |                        |                        |

|                        |                                   | on error (illegal<br>on completed s |                        | as requested)          |                           |                        |                        |

| bit 12                 | TIMEOUT: Tin                      | ne-out bit                          | -                      |                        |                           |                        |                        |

|                        | 1 = Transaction timed out         |                                     |                        |                        |                           |                        |                        |

|                        | 0 = Transactio                    | on completed s                      | successfully           |                        |                           |                        |                        |

| bit 11-8               | Unimplement                       | ted: Read as 'o                     | )'                     |                        |                           |                        |                        |

| bit 7-0                | RADDR<23:1                        | 6>: Parallel Ma                     | aster Port Rese        | erved Address S        | Space bits <sup>(1)</sup> |                        |                        |

| Note 1: If R           |                                   |                                     |                        | DS address for         |                           | will be FFFFF          | <sup>-</sup> h.        |

## REGISTER 21-2: PMCON2: EPMP CONTROL REGISTER 2

#### REGISTER 24-4: CLCxGLSL: CLCx GATE LOGIC INPUT SELECT LOW REGISTER (CONTINUED)

| bit 8 | G2D1N: Gate 2 Data Source 1 Negated Enable bit                                                                                                        |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = The Data Source 1 inverted signal is enabled for Gate 2</li><li>0 = The Data Source 1 inverted signal is disabled for Gate 2</li></ul>    |

| bit 7 | G1D4T: Gate 1 Data Source 4 True Enable bit                                                                                                           |

|       | <ul><li>1 = The Data Source 4 signal is enabled for Gate 1</li><li>0 = The Data Source 4 signal is disabled for Gate 1</li></ul>                      |

| bit 6 | G1D4N: Gate 1 Data Source 4 Negated Enable bit                                                                                                        |

|       | <ul> <li>1 = The Data Source 4 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 4 inverted signal is disabled for Gate 1</li> </ul> |

| bit 5 | G1D3T: Gate 1 Data Source 3 True Enable bit                                                                                                           |

|       | <ul> <li>1 = The Data Source 3 signal is enabled for Gate 1</li> <li>0 = The Data Source 3 signal is disabled for Gate 1</li> </ul>                   |

| bit 4 | G1D3N: Gate 1 Data Source 3 Negated Enable bit                                                                                                        |

|       | <ul> <li>1 = The Data Source 3 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 3 inverted signal is disabled for Gate 1</li> </ul> |

| bit 3 | G1D2T: Gate 1 Data Source 2 True Enable bit                                                                                                           |

|       | <ul><li>1 = The Data Source 2 signal is enabled for Gate 1</li><li>0 = The Data Source 2 signal is disabled for Gate 1</li></ul>                      |

| bit 2 | G1D2N: Gate 1 Data Source 2 Negated Enable bit                                                                                                        |

|       | <ul> <li>1 = The Data Source 2 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 2 inverted signal is disabled for Gate 1</li> </ul> |

| bit 1 | G1D1T: Gate 1 Data Source 1 True Enable bit                                                                                                           |

|       | <ul><li>1 = The Data Source 1 signal is enabled for Gate 1</li><li>0 = The Data Source 1 signal is disabled for Gate 1</li></ul>                      |

| bit 0 | G1D1N: Gate 1 Data Source 1 Negated Enable bit                                                                                                        |

|       | <ul> <li>1 = The Data Source 1 inverted signal is enabled for Gate 1</li> <li>0 = The Data Source 1 inverted signal is disabled for Gate 1</li> </ul> |

## REGISTER 25-7: ANCFG: A/D BAND GAP REFERENCE CONFIGURATION REGISTER

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|--------------|-----|-----|-----|-----|-----|-----|-----|

| —            | —   |     | —   | —   | —   | —   | —   |

| bit 15 bit 8 |     |     |     |     |     |     |     |

|              |     |     |     |     |     |     |     |

| U-0   | U-0 | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                |

|-------|-----|-----|-----|-----------------------|-----------------------|-----------------------|----------------------|

| —     | —   | —   | —   | VBGUSB <sup>(1)</sup> | VBGADC <sup>(1)</sup> | VBGCMP <sup>(1)</sup> | VBGEN <sup>(1)</sup> |

| bit 7 |     |     |     |                       |                       |                       | bit 0                |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                                                           |

|----------|------------------------------------------------------------------------------------------------------|

| bit 3    | VBGUSB: Band Gap Reference Enable for USB bit <sup>(1)</sup>                                         |

|          | <ul> <li>1 = Band gap reference is enabled</li> <li>0 = Band gap reference is disabled</li> </ul>    |

| bit 2    | VBGADC: Band Gap Reference Enable for A/D bit <sup>(1)</sup>                                         |

|          | 1 = Band gap reference is enabled                                                                    |

|          | 0 = Band gap reference is disabled                                                                   |

| bit 1    | VBGCMP: Band Gap Reference Enable for CTMU and Comparator bit <sup>(1)</sup>                         |

|          | 1 = Band gap reference is enabled                                                                    |

|          | 0 = Band gap reference is disabled                                                                   |

| bit 0    | VBGEN: Band Gap Reference Enable for VREG, BOR, HLVD, FRC, DCO, NVM and A/D Boost bit <sup>(1)</sup> |

|          | 1 = Band gap reference is enabled                                                                    |

|          | 0 = Band gap reference is disabled                                                                   |

|          |                                                                                                      |

**Note 1:** When a module requests a band gap reference voltage, that reference will be enabled automatically after a brief start-up time. The user can manually enable the band gap references using the ANCFG register before enabling the module requesting the band gap reference to avoid this startup time (~1 ms).

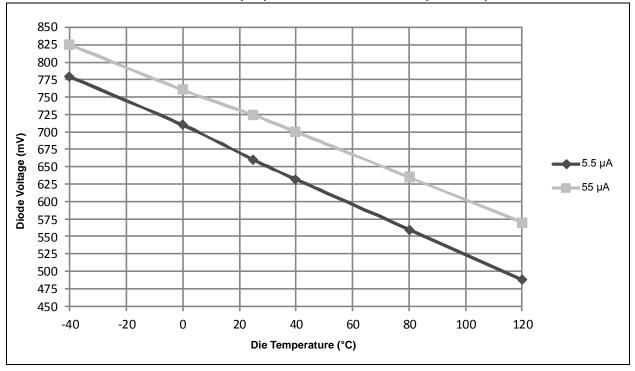

# 28.4 Measuring Die Temperature

The CTMU can be configured to use the A/D to measure the die temperature using dedicated A/D Channel 24. Perform the following steps to measure the diode voltage:

- The internal current source must be set for either 5.5  $\mu$ A (IRNG<1:0> = 0x2) or 55  $\mu$ A (IRNG<1:0> = 0x3).

- In order to route the current source to the diode, the EDG1STAT and EDG2STAT bits must be equal (either both '0' or both '1').

- The CTMREQ bit (AD1CON5<13>) must be set to '1'.

- The A/D Channel Select bits must be 24 (0x18) using a single-ended measurement.

The voltage of the diode will vary over temperature according to the graphs shown below (Figure 28-4). Note that the graphs are different, based on the magnitude of

the current source selected. The slopes are nearly linear over the range of -40°C to +100°C and the temperature can be calculated as follows:

## **EQUATION 28-2:**

For 5.5 µA Current Source:

$$Tdie = \frac{710 \ mV - V diode}{1.8}$$

where Vdiode is in mV, Tdie is in °C

For 55 µA Current Source:

$$Tdie = \frac{760 \ mV - V diode}{1.55}$$

where *Vdiode* is in *mV*, *Tdie* is in °C

## FIGURE 28-4: DIODE VOLTAGE (mV) vs. DIE TEMPERATURE (TYPICAL)

# **30.0 SPECIAL FEATURES**

- **Note:** This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the following sections of the *"dsPIC33/PIC24 Family Reference Manual"*, which are available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

- "Watchdog Timer (WDT)" (DS39697)

- "High-Level Device Integration" (DS39719)

- "Programming and Diagnostics" (DS39716)

PIC24FJ1024GA610/GB610 family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection

- · JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup>

- In-Circuit Emulation

# 30.1 Configuration Bits

The Configuration bits are stored in the last page location of implemented program memory. These bits can be set or cleared to select various device configurations. There are two types of Configuration bits: system operation bits and code-protect bits. The system operation bits determine the power-on settings for system-level components, such as the oscillator and the Watchdog Timer. The code-protect bits prevent program memory from being read and written.

In Dual Partition modes, each partition has its own set of Flash Configuration Words. The full set of Configuration registers in the Active Partition is used to determine the device's configuration; the Configuration Words in the Inactive Partition are used to determine the device's configuration when that partition becomes active. However, some of the Configuration registers in the Inactive Partition (FSEC, FBSLIM and FSIGN) may be used to determine how the Active Partition is able or allowed to access the Inactive Partition.

#### 30.1.1 CONSIDERATIONS FOR CONFIGURING PIC24FJ1024GA610/ GB610 FAMILY DEVICES

In PIC24FJ1024GA610/GB610 family devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in the three words at the top of the on-chip program memory space, known as the Flash Configuration Words. Their specific locations are shown in Table 30-1. The configuration data is automatically loaded from the Flash Configuration Words to the proper Configuration registers during device Resets. After a Reset, configuration reads are performed in the following order:

- Device Calibration Information

- Partition Mode Configuration (FBOOT)

- If Single Partition mode:

- User Configuration Words

If Dual Partition mode:

- Partition 1 Boot Sequence Number

- · Partition 2 Boot Sequence Number

- User Configuration Words from the Active Partition

- Code Protection User Configuration Words from the Inactive Partition

- **Note:** Configuration data is reloaded on all types of device Resets.

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration Word for configuration data. This is to make certain that program code is not stored in this address when the code is compiled.

The upper byte of all Flash Configuration Words in program memory should always be '0000 0000'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '0's to these locations has no effect on device operation.

## TABLE 33-25: A/D MODULE SPECIFICATIONS

| AC CHARACTERISTICS |           |                                                   | Standard Operating Conditions: 2.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |          |                                   |       |                                                                                                |

|--------------------|-----------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|-------|------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic                                    | Min.                                                                                                                                            | Тур      | Max.                              | Units | Conditions                                                                                     |

|                    |           |                                                   | Device \$                                                                                                                                       | Supply   |                                   |       |                                                                                                |

| AD01               | AVDD      | Module VDD Supply                                 | Greater of:<br>VDD – 0.3<br>or 2.2                                                                                                              |          | Lesser of:<br>VDD + 0.3<br>or 3.6 | V     |                                                                                                |

| AD02               | AVss      | Module Vss Supply                                 | Vss – 0.3                                                                                                                                       |          | Vss + 0.3                         | V     |                                                                                                |

|                    |           |                                                   | Reference                                                                                                                                       | e Inputs |                                   |       |                                                                                                |

| AD05               | VREFH     | Reference Voltage High                            | AVss + 1.7                                                                                                                                      |          | AVDD                              | V     |                                                                                                |

| AD06               | VREFL     | Reference Voltage Low                             | AVss                                                                                                                                            |          | AVDD – 1.7                        | V     |                                                                                                |

| AD07               | VREF      | Absolute Reference<br>Voltage                     | AVss – 0.3                                                                                                                                      |          | AVDD + 0.3                        | V     |                                                                                                |

|                    |           |                                                   | Analog                                                                                                                                          | Inputs   |                                   |       | •                                                                                              |

| AD10               | VINH-VINL | Full-Scale Input Span                             | VREFL                                                                                                                                           | _        | VREFH                             | V     | (Note 1)                                                                                       |