Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 1MB (341.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

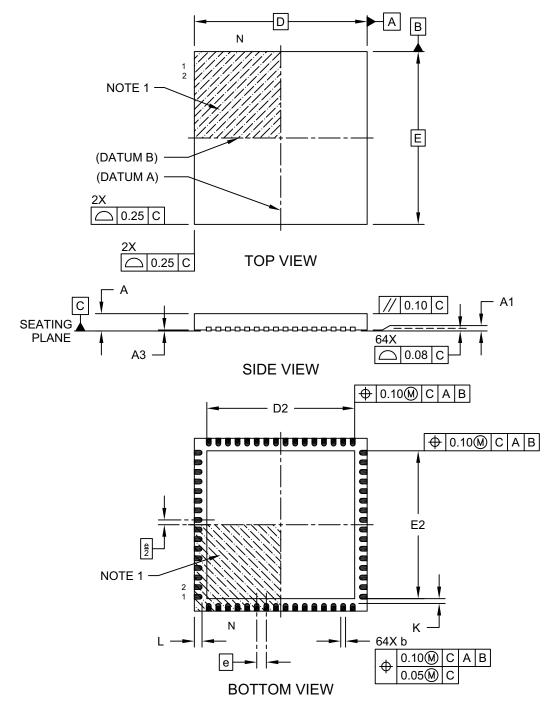

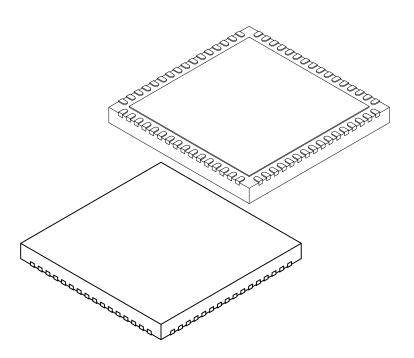

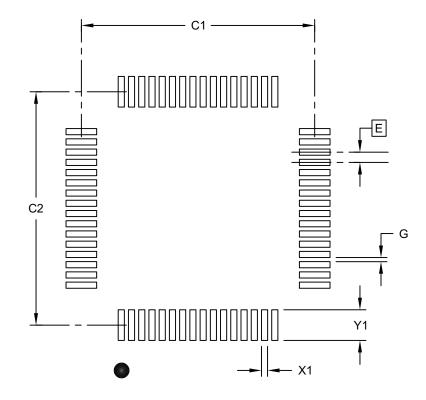

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 121-TFBGA                                                                       |

| Supplier Device Package    | 121-TFBGA (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj1024gb610-i-bg |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.3.3 READING DATA FROM PROGRAM MEMORY USING EDS

The upper 32 Kbytes of Data Space may optionally be mapped into any 16K word page of the program space. This provides transparent access of stored constant data from the Data Space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the Data Space occurs when the MSb of EA is '1' and the DSRPAG<9> is also '1'. The lower 8 bits of DSRPAG are concatenated to the Wn<14:0> bits to form a 23-bit EA to access program memory. The DSRPAG<8> decides which word should be addressed; when the bit is '0', the lower word, and when '1', the upper word of the program memory is accessed.

The entire program memory is divided into 512 EDS pages, from 200h to 3FFh, each consisting of 16K words of data. Pages, 200h to 2FFh, correspond to the lower words of the program memory, while 300h to 3FFh correspond to the upper words of the program memory.

Using this EDS technique, the entire program memory can be accessed. Previously, the access to the upper word of the program memory was not supported. Table 4-15 provides the corresponding 23-bit EDS address for program memory with EDS page and source addresses.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

| DSRPAG<br>(Data Space Read Register) | Source Address while<br>Indirect Addressing | 23-Bit EA Pointing<br>to EDS | Comment                            |

|--------------------------------------|---------------------------------------------|------------------------------|------------------------------------|

| 200h                                 |                                             | 000000h to 007FFEh           | Lower words of 4M program          |

| •                                    |                                             | •                            | instructions; (8 Mbytes) for       |

| •                                    |                                             | •                            | read operations only.              |

| •                                    |                                             | •                            |                                    |

| 2FFh                                 |                                             | 7F8000h to 7FFFFEh           |                                    |

| 300h                                 | 8000h to FFFFh                              | 000001h to 007FFFh           | Upper words of 4M program          |

| •                                    |                                             | •                            | instructions (4 Mbytes remaining;  |

| •                                    |                                             | •                            | 4 Mbytes are phantom bytes) for    |

| •                                    |                                             | •                            | read operations only.              |

| 3FFh                                 |                                             | 7F8001h to 7FFFFFh           |                                    |

| 000h                                 |                                             | Invalid Address              | Address error trap. <sup>(1)</sup> |

## TABLE 4-15: EDS PROGRAM ADDRESS WITH DIFFERENT PAGES AND ADDRESSES

**Note 1:** When the source/destination address is above 8000h and DSRPAG/DSWPAG is '0', an address error trap will occur.

#### EXAMPLE 4-3: EDS READ CODE FROM PROGRAM MEMORY IN ASSEMBLY

| ; Set the EDS page from where the data to be read |                                                |                                                           |  |  |  |  |

|---------------------------------------------------|------------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| mov                                               | #0x0202, w0                                    |                                                           |  |  |  |  |

| mov                                               | w0, DSRPAG                                     | ;page 0x202, consisting lower words, is selected for read |  |  |  |  |

| mov                                               | #0x000A, w1                                    | ;select the location (0x0A) to be read                    |  |  |  |  |

| bset                                              | w1, #15                                        | ;set the MSB of the base address, enable EDS mode         |  |  |  |  |

| ;Read a by                                        | ;Read a byte from the selected location        |                                                           |  |  |  |  |

| mov.b                                             | [w1++], w2                                     | ;read Low byte                                            |  |  |  |  |

| mov.b                                             | [w1++], w3                                     | ;read High byte                                           |  |  |  |  |

| ;Read a wo                                        | rd from the selected locati                    | on                                                        |  |  |  |  |

| mov                                               | [w1], w2                                       | i                                                         |  |  |  |  |

| ;Read Doub                                        | ;Read Double - word from the selected location |                                                           |  |  |  |  |

| mov.d                                             | [w1], w2                                       | ;two word read, stored in w2 and w3                       |  |  |  |  |

| U-0          | U-0                          | R/W-0                                                                       | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |

|--------------|------------------------------|-----------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|-------|--|

| _            | _                            | IC6MD                                                                       | IC5MD           | IC4MD             | IC3MD            | IC2MD           | IC1MD |  |

| bit 15       |                              |                                                                             |                 |                   |                  | •               | bit 8 |  |

| U-0          | U-0                          | R/W-0                                                                       | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |

| _            | —                            | OC6MD                                                                       | OC5MD           | OC4MD             | OC3MD            | OC2MD           | OC1MD |  |

| bit 7        |                              |                                                                             |                 |                   |                  |                 | bit C |  |

| Legend:      |                              |                                                                             |                 |                   |                  |                 |       |  |

| R = Readab   | le bit                       | W = Writable                                                                | bit             | U = Unimplen      | nented bit, read | d as '0'        |       |  |

| -n = Value a | t POR                        | '1' = Bit is set                                                            |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |

| bit 15-14    | Unimplemer                   | nted: Read as '                                                             | )'              |                   |                  |                 |       |  |

| bit 13       | IC6MD: Inpu                  | t Capture 6 Moo                                                             | dule Disable bi | t                 |                  |                 |       |  |

|              | 1 = Module i                 |                                                                             |                 |                   |                  |                 |       |  |

|              | -                            | power and clock                                                             |                 |                   |                  |                 |       |  |

| bit 12       |                              | t Capture 5 Moo                                                             | dule Disable bi | t                 |                  |                 |       |  |

|              | 1 = Module i<br>0 = Module i | is disabled                                                                 | sources are e   | enabled           |                  |                 |       |  |

| bit 11       |                              | t Capture 4 Mod                                                             |                 |                   |                  |                 |       |  |

|              | 1 = Module i                 | •                                                                           |                 |                   |                  |                 |       |  |

|              | 0 = Module                   | power and clock                                                             | sources are e   | enabled           |                  |                 |       |  |

| bit 10       | •                            | t Capture 3 Moo                                                             | dule Disable bi | t                 |                  |                 |       |  |

|              | 1 = Module i<br>0 = Module i | is disabled<br>power and clocł                                              | sources are e   | enabled           |                  |                 |       |  |

| bit 9        | -                            | t Capture 2 Mo                                                              |                 |                   |                  |                 |       |  |

|              | 1 = Module i                 |                                                                             |                 |                   |                  |                 |       |  |

|              |                              | power and clock                                                             |                 |                   |                  |                 |       |  |

| bit 8        |                              | t Capture 1 Moo                                                             | dule Disable bi | t                 |                  |                 |       |  |

|              | 1 = Module i<br>0 = Module j | is disabled power and clock                                                 | sources are e   | enabled           |                  |                 |       |  |

| bit 7-6      | Unimplemer                   | nted: Read as '                                                             | י)              |                   |                  |                 |       |  |

| bit 5        | OC6MD: Out                   | tput Capture 6 N                                                            | /lodule Disable | e bit             |                  |                 |       |  |

|              | 1 = Module i                 |                                                                             |                 |                   |                  |                 |       |  |

| L:1 4        | •                            | power and clock                                                             |                 |                   |                  |                 |       |  |

| bit 4        | 1 = Module i                 | tput Capture 5 N                                                            |                 |                   |                  |                 |       |  |

|              |                              | power and clock                                                             | sources are e   | enabled           |                  |                 |       |  |

| bit 3        | -                            |                                                                             |                 |                   |                  |                 |       |  |

|              |                              | <b>OC4MD:</b> Output Capture 4 Module Disable bit<br>1 = Module is disabled |                 |                   |                  |                 |       |  |

|              | 0 = Module                   | power and clock                                                             | sources are e   | enabled           |                  |                 |       |  |

| bit 2        |                              | tput Capture 3 N                                                            | /lodule Disable | e bit             |                  |                 |       |  |

|              | 1 = Module i                 | is disabled<br>power and clocł                                              |                 | nabled            |                  |                 |       |  |

| bit 1        | -                            | tput Capture 2 N                                                            |                 |                   |                  |                 |       |  |

|              | 1 = Module i                 |                                                                             |                 |                   |                  |                 |       |  |

|              |                              | power and clock                                                             | sources are e   | enabled           |                  |                 |       |  |

| bit 0        | OC1MD: Out                   | tput Capture 1 N                                                            | /lodule Disable | e bit             |                  |                 |       |  |

|              | 1 = Module i                 |                                                                             |                 |                   |                  |                 |       |  |

|              | 0 = Module                   | power and clock                                                             | sources are e   | enabled           |                  |                 |       |  |

## REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE REGISTER 2

| REGISTER 11-14: | RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2 |

|-----------------|------------------------------------------------|

|-----------------|------------------------------------------------|

| U-0    | U-0 | R/W-1     | R/W-1     | R/W-1     | R/W-1     | R/W-1     | R/W-1     |

|--------|-----|-----------|-----------|-----------|-----------|-----------|-----------|

| —      |     | OCTRIG2R5 | OCTRIG2R4 | OCTRIG2R3 | OCTRIG2R2 | OCTRIG2R1 | OCTRIG2R0 |

| bit 15 |     |           |           |           |           |           | bit 8     |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | INT4R5 | INT4R4 | INT4R3 | INT4R2 | INT4R1 | INT4R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                                                         |                      |                    |  |

|-------------------|---------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                        | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15-14 | Unimplemented: Read as '0'                                                           |

|-----------|--------------------------------------------------------------------------------------|

| bit 13-8  | OCTRIG2R<5:0>: Assign Output Compare Trigger 2 to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                           |

| bit 5-0   | INT4R<5:0>: Assign External Interrupt 4 (INT4) to Corresponding RPn or RPIn Pin bits |

## REGISTER 11-15: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | T3CKR5 | T3CKR4 | T3CKR3 | T3CKR2 | T3CKR1 | T3CKR0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | T2CKR5 | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 T3CKR<5:0>: Assign Timer3 Clock to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 T2CKR<5:0>: Assign Timer2 Clock to Corresponding RPn or RPIn Pin bits

## REGISTER 11-18: RPINR6: PERIPHERAL PIN SELECT INPUT REGISTER 6

| U-0    | U-0 | r-1 | r-1 | r-1 | r-1 | r-1 | r-1   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | r-1 | r-1 | r-1 | r-1 | r-1 | r-1   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | —   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           | r = Reserved bit |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

| bit 13-8  | Reserved: Maintain as '1'  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **Reserved**: Maintain as '1'

#### REGISTER 11-19: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | IC2R5 | IC2R4 | IC2R3 | IC2R2 | IC2R1 | IC2R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IC1R5 | IC1R4 | IC1R3 | IC1R2 | IC1R1 | IC1R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 IC2R<5:0>: Assign Input Capture 2 (IC2) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IC1R<5:0>: Assign Input Capture 1 (IC1) to Corresponding RPn or RPIn Pin bits

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | —   | U1CTSR5 | U1CTSR4 | U1CTSR3 | U1CTSR2 | U1CTSR1 | U1CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

|        |     |         |         |         |         |         |         |

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

## REGISTER 11-26: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-14 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 13-8  | U1CTSR<5:0>: Assign UART1 Clear-to-Send (U1CTS) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                            |

| bit 5-0   | U1RXR<5:0>: Assign UART1 Receive (U1RX) to Corresponding RPn or RPIn Pin bits         |

## REGISTER 11-27: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | U2CTSR5 | U2CTSR4 | U2CTSR3 | U2CTSR2 | U2CTSR1 | U2CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | —   | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U2CTSR<5:0>: Assign UART2 Clear-to-Send (U2CTS) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 U2RXR<5:0>: Assign UART2 Receive (U2RX) to Corresponding RPn or RPIn Pin bits

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | SCK3R5 | SCK3R4 | SCK3R3 | SCK3R2 | SCK3R1 | SCK3R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

## **REGISTER 11-34: RPINR28: PERIPHERAL PIN SELECT INPUT REGISTER 28**

| 1 | ~~  |   | nd |     |

|---|-----|---|----|-----|

|   | .eu | е | пu | I - |

bit 7

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as 'O'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK3R<5:0>: Assign SPI3 Clock Input (SCK3IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI3R<5:0>: Assign SPI3 Data Input (SDI3) to Corresponding RPn or RPIn Pin bits    |

#### **REGISTER 11-35: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS3R5 | SS3R4 | SS3R3 | SS3R2 | SS3R1 | SS3R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 SS3R<5:0>: Assign SPI3 Slave Select Input (SS3IN) to Corresponding RPn or RPIn Pin bits bit 0

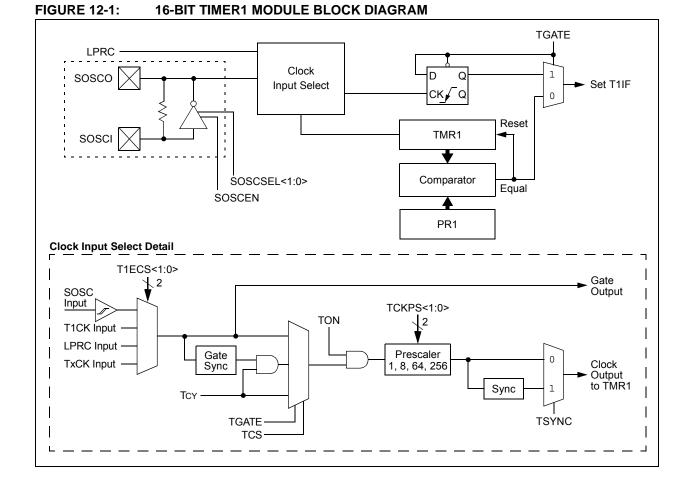

## 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, *"Timers"* (DS39704), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Clear the TON bit (= 0).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS, TECS<1:0> and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

- 7. Set the TON bit (= 1).

© 2015-2016 Microchip Technology Inc.

| U-0        | U-0                                    | R/W-0                             | R/W-0                   | R/W-0             | R/W-0               | R/W-0                       | R/W-0                 |  |

|------------|----------------------------------------|-----------------------------------|-------------------------|-------------------|---------------------|-----------------------------|-----------------------|--|

| <u> </u>   | <u> </u>                               | OCSIDL                            | OCTSEL2                 | OCTSEL1           | OCTSEL0             | ENFLT2 <sup>(2)</sup>       | ENFLT1 <sup>(2)</sup> |  |

| bit 15     |                                        | OCCIDE                            | OUTOLLE                 | OUTOLLT           | OUTOLLU             |                             | bit 8                 |  |

|            |                                        |                                   |                         |                   |                     |                             |                       |  |

| R/W-0      | R/W-0, HSC                             | R/W-0, HSC                        | R/W-0, HSC              | R/W-0             | R/W-0               | R/W-0                       | R/W-0                 |  |

| ENFLT0     | (2) OCFLT2 <sup>(2,3)</sup>            | OCFLT1 <sup>(2,4)</sup>           | OCFLT0 <sup>(2,4)</sup> | TRIGMODE          | OCM2 <sup>(1)</sup> | OCM1 <sup>(1)</sup>         | OCM0 <sup>(1)</sup>   |  |

| bit 7      | 1                                      |                                   | L                       | l                 |                     | •                           | bit 0                 |  |

|            |                                        |                                   |                         |                   |                     |                             |                       |  |

| Legend:    |                                        | HSC = Hardw                       | are Settable/C          | learable bit      |                     |                             |                       |  |

| R = Read   | able bit                               | W = Writable                      | bit                     | U = Unimplem      | nented bit, read    | l as '0'                    |                       |  |

| -n = Value | e at POR                               | '1' = Bit is set                  |                         | '0' = Bit is clea | ared                | x = Bit is unkr             | nown                  |  |

|            |                                        |                                   |                         |                   |                     |                             |                       |  |

| bit 15-14  | Unimplemen                             | ted: Read as '                    | )'                      |                   |                     |                             |                       |  |

| bit 13     | OCSIDL: Out                            | put Compare x                     | Stop in Idle Mo         | ode Control bit   |                     |                             |                       |  |

|            |                                        | ompare x halts                    |                         |                   |                     |                             |                       |  |

|            |                                        |                                   |                         | e in CPU Idle m   | node                |                             |                       |  |

| bit 12-10  |                                        | >: Output Com                     |                         | elect bits        |                     |                             |                       |  |

|            | 111 = Periphe<br>110 = Reserv          | eral clock (Fcy)                  |                         |                   |                     |                             |                       |  |

|            | 101 = Reserv                           |                                   |                         |                   |                     |                             |                       |  |

|            |                                        |                                   | hchronous cloc          | k is supported)   |                     |                             |                       |  |

|            | 011 = Timer5                           | Timer5 clock                      |                         |                   |                     |                             |                       |  |

|            | 010 = Timer4<br>001 = Timer3           |                                   |                         |                   |                     |                             |                       |  |

|            | 001 = Timer3<br>000 = Timer2           |                                   |                         |                   |                     |                             |                       |  |

| bit 9      |                                        | It Input 2 Enab                   | e bit <b>(2)</b>        |                   |                     |                             |                       |  |

|            |                                        | Comparator 1/2                    |                         | ed <sup>(3)</sup> |                     |                             |                       |  |

|            | 0 = Fault 2 is                         |                                   | ,                       |                   |                     |                             |                       |  |

| bit 8      |                                        | lt Input 1 Enab                   |                         |                   |                     |                             |                       |  |

|            | 1 = Fault 1 (0<br>0 = Fault 1 is       | DCFB pin) is er                   | abled <sup>(4)</sup>    |                   |                     |                             |                       |  |

| bit 7      |                                        | It Input 0 Enab                   | e hit(2)                |                   |                     |                             |                       |  |

|            |                                        | DCFA pin) is er                   |                         |                   |                     |                             |                       |  |

|            | 0 = Fault 0 is                         |                                   |                         |                   |                     |                             |                       |  |

| bit 6      | OCFLT2: Out                            | put Compare x                     | PWM Fault 2 (           | (Comparator 1/2   | 2/3) Condition      | Status bit <sup>(2,3)</sup> |                       |  |

|            | 1 = PWM Fa                             | ult 2 has occur                   | ed                      |                   |                     |                             |                       |  |

|            |                                        | Fault 2 has oc                    |                         |                   |                     |                             |                       |  |

| bit 5      |                                        |                                   |                         | (OCFB pin) Cor    | ndition Status b    | bit <sup>(2,4)</sup>        |                       |  |

|            |                                        | ult 1 has occur<br>Fault 1 has oc |                         |                   |                     |                             |                       |  |

|            |                                        | 1 4411 1 1143 00                  | curred                  |                   |                     |                             |                       |  |

| Note 1:    | The OCx output n<br>"Peripheral Pin \$ | Select (PPS)".                    | •                       |                   |                     |                             | Section 11.4          |  |

| 2:         | The Fault input er                     |                                   |                         |                   |                     |                             |                       |  |

| 3:         | The Comparator channels, Compa         |                                   |                         |                   |                     | put controls the            | e OC4-OC6             |  |

| 4:         | The OCFA/OCFB                          | Fault inputs mu                   | ust also be conf        | figured to an av  | ailable RPn/RF      | In pin. For mor             | e information,        |  |

## REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

4: The OCFA/OCFB Fault inputs must also be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

| REGISTER '    | 16-6: CCPx                                                                                                                                                                                                                                                                                                                                                        | CON3H: CCI                                                                                                                                                     | Px CONTRO                                                                                                                                           | 3 HIGH RE                                                                                                             | GISTERS                                                                                |                                                                    |                            |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------|

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                          | R/W-0                                                                                                                                               | U-0                                                                                                                   | R/W-0                                                                                  | R/W-0                                                              | R/W-0                      |

| OETRIG        | OSCNT2                                                                                                                                                                                                                                                                                                                                                            | OSCNT1                                                                                                                                                         | OSCNT0                                                                                                                                              |                                                                                                                       | OUTM2 <sup>(1)</sup>                                                                   | OUTM1 <sup>(1)</sup>                                               | OUTM0 <sup>(1)</sup>       |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                |                                                                                                                                                     |                                                                                                                       |                                                                                        |                                                                    | bit 8                      |

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                          | R/W-0                                                                                                                                               | R/W-0                                                                                                                 | R/W-0                                                                                  | R/W-0                                                              | R/W-0                      |

| _             | _                                                                                                                                                                                                                                                                                                                                                                 | POLACE                                                                                                                                                         | POLBDF <sup>(1)</sup>                                                                                                                               | PSSACE1                                                                                                               | PSSACE0                                                                                | PSSBDF1 <sup>(1)</sup>                                             | PSSBDF0 <sup>(1</sup>      |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                |                                                                                                                                                     |                                                                                                                       |                                                                                        |                                                                    | bit                        |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                |                                                                                                                                                     |                                                                                                                       |                                                                                        |                                                                    |                            |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                                                                             | W = Writable                                                                                                                                                   | bit                                                                                                                                                 | U = Unimplen                                                                                                          | nented bit, read                                                                       | d as '0'                                                           |                            |

| -n = Value at |                                                                                                                                                                                                                                                                                                                                                                   | '1' = Bit is set                                                                                                                                               |                                                                                                                                                     | '0' = Bit is clea                                                                                                     |                                                                                        | x = Bit is unkr                                                    | iown                       |

|               |                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                |                                                                                                                                                     |                                                                                                                       |                                                                                        |                                                                    |                            |

| bit 15        | 1 = For Trigg                                                                                                                                                                                                                                                                                                                                                     | Px Dead-Time<br>ered mode (TR<br>utput pin opera                                                                                                               | IGEN = 1): Mo                                                                                                                                       | odule does not                                                                                                        | drive enabled o                                                                        | output pins unti                                                   | l triggered                |

| bit 14-12     | OSCNT<2:0><br>111 = Extend<br>110 = Extend<br>101 = Extend<br>011 = Extend<br>010 = Extend<br>010 = Extend<br>001 = Extend                                                                                                                                                                                                                                        | : One-Shot Eve<br>s one-shot eve<br>ot extend one- | ent Count bits<br>nt by 7 time ba<br>nt by 6 time ba<br>nt by 5 time ba<br>nt by 4 time ba<br>nt by 3 time ba<br>nt by 2 time ba<br>nt by 1 time ba | ase periods (7 t<br>use periods (6 t<br>use periods (5 t<br>use periods (4 t<br>use periods (3 t<br>use period (2 tir | ime base perio<br>ime base perio<br>ime base perio<br>ime base perio<br>ime base perio | ods total)<br>ods total)<br>ods total)<br>ods total)<br>ods total) |                            |

| bit 11        | Unimplement                                                                                                                                                                                                                                                                                                                                                       | ted: Read as 'd                                                                                                                                                | )'                                                                                                                                                  |                                                                                                                       |                                                                                        |                                                                    |                            |

| bit 10-8      | 111 = Reserv<br>110 = Output<br>101 = Brush I<br>100 = Brush I<br>011 = Reserv<br>010 = Half-Br<br>001 = Push-P                                                                                                                                                                                                                                                   | Scan mode<br>DC Output mod<br>DC Output mod                                                                                                                    | le, forward<br>le, reverse<br>ode<br>e                                                                                                              | bits <sup>(1)</sup>                                                                                                   |                                                                                        |                                                                    |                            |

| bit 7-6       | Unimplement                                                                                                                                                                                                                                                                                                                                                       | ted: Read as 'd                                                                                                                                                | )'                                                                                                                                                  |                                                                                                                       |                                                                                        |                                                                    |                            |

| bit 5         | POLACE: CC<br>1 = Output pi                                                                                                                                                                                                                                                                                                                                       | Px Output Pins<br>n polarity is act<br>n polarity is act                                                                                                       | s, OCMxA, OC<br>ive-low                                                                                                                             | MxC and OCM                                                                                                           | IxE, Polarity Co                                                                       | ontrol bit                                                         |                            |

| bit 4         | 1 = Output pi                                                                                                                                                                                                                                                                                                                                                     | Px Output Pins<br>n polarity is act<br>n polarity is act                                                                                                       | ive-low                                                                                                                                             | MxD and OCM                                                                                                           | xF, Polarity Co                                                                        | ntrol bit <sup>(1)</sup>                                           |                            |

| bit 3-2       | <ul> <li>0 = Output pin polarity is active-high</li> <li>PSSACE&lt;1:0&gt;: PWMx Output Pins, OCMxA, OCMxC and OCMxE, Shutdown State Control bits</li> <li>11 = Pins are driven active when a shutdown event occurs</li> <li>10 = Pins are driven inactive when a shutdown event occurs</li> <li>0x = Pins are tri-stated when a shutdown event occurs</li> </ul> |                                                                                                                                                                |                                                                                                                                                     |                                                                                                                       |                                                                                        |                                                                    |                            |

| bit 1-0       | PSSBDF<1:0                                                                                                                                                                                                                                                                                                                                                        | >: PWMx Outp                                                                                                                                                   | ut Pins, OCMx                                                                                                                                       | B, OCMxD, an                                                                                                          | d OCMxF. Shu                                                                           | itdown State Co                                                    | ontrol bits <sup>(1)</sup> |

|               | 11 = Pins are<br>10 = Pins are                                                                                                                                                                                                                                                                                                                                    | driven active v<br>driven inactive<br>in a high-impe                                                                                                           | /hen a shutdov<br>when a shutdo                                                                                                                     | vn event occurs<br>own event occu                                                                                     | s<br>urs                                                                               |                                                                    |                            |

## REGISTER 16-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

**Note 1:** These bits are implemented in MCCPx modules only.

## REGISTER 17-2: SPIxCON1H: SPIx CONTROL REGISTER 1 HIGH (CONTINUED)

| bit 6   | FRMSYNC: Frame Sync Pulse Direction Control bit                                                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Frame Sync pulse input (slave)                                                                                                                                                 |

|         | 0 = Frame Sync pulse output (master)                                                                                                                                               |

| bit 5   | FRMPOL: Frame Sync/Slave Select Polarity bit                                                                                                                                       |

|         | <ul> <li>1 = Frame Sync pulse/slave select is active-high</li> <li>0 = Frame Sync pulse/slave select is active-low</li> </ul>                                                      |

| bit 4   | MSSEN: Master Mode Slave Select Enable bit                                                                                                                                         |

|         | 1 = SPIx slave select support is enabled with polarity determined by FRMPOL (SSx pin is automatically driven during transmission in Master mode)                                   |

|         | 0 = SPIx slave select support is disabled (SSx pin will be controlled by port IO)                                                                                                  |

| bit 3   | FRMSYPW: Frame Sync Pulse-Width bit                                                                                                                                                |

|         | <ul> <li>1 = Frame Sync pulse is one serial word length wide (as defined by MODE&lt;32,16&gt;/WLENGTH&lt;4:0&gt;)</li> <li>0 = Frame Sync pulse is one clock (SCK) wide</li> </ul> |

| bit 2-0 | FRMCNT<2:0>: Frame Sync Pulse Counter bits                                                                                                                                         |

|         | Controls the number of serial words transmitted per Sync pulse.<br>111 = Reserved                                                                                                  |

|         | 110 = Reserved                                                                                                                                                                     |

|         | 101 = Generates a Frame Sync pulse on every 32 serial words                                                                                                                        |

|         | 100 = Generates a Frame Sync pulse on every 16 serial words                                                                                                                        |

|         | 011 = Generates a Frame Sync pulse on every 8 serial words                                                                                                                         |

|         | 010 = Generates a Frame Sync pulse on every 4 serial words                                                                                                                         |

|         | 001 = Generates a Frame Sync pulse on every 2 serial words (value used by audio protocols)                                                                                         |

|         | 000 = Generates a Frame Sync pulse on each serial word                                                                                                                             |

- **Note 1:** AUDEN can only be written when the SPIEN bit = 0.

- **2:** AUDMONO can only be written when the SPIEN bit = 0 and is only valid for AUDEN = 1.

- **3:** URDTEN is only valid when IGNTUR = 1.

- **4:** AUDMOD<1:0> bits can only be written when the SPIEN bit = 0 and are only valid when AUDEN = 1. When NOT in PCM/DSP mode, this module functions as if FRMSYPW = 1, regardless of its actual value.

TXELM2

TXELM1

**TXELMO**

bit 0

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

|--------|-----|-----------------------|-----------------------|-----------------------|----------|----------|----------|

| —      | _   | RXELM5 <sup>(3)</sup> | RXELM4 <sup>(2)</sup> | RXELM3 <sup>(1)</sup> | RXELM2   | RXELM1   | RXELM0   |

| bit 15 |     |                       |                       |                       |          |          | bit 8    |

|        |     |                       |                       |                       |          |          |          |

| U-0    | U-0 | R-0, HSC              | R-0, HSC              | R-0, HSC              | R-0, HSC | R-0, HSC | R-0, HSC |

TXELM3<sup>(1)</sup>

## REGISTER 17-5: SPIxSTATH: SPIx STATUS REGISTER HIGH

TXELM5<sup>(3)</sup>

| Legend:           | HSC = Hardware Settab | le/Clearable bit       |                    |

|-------------------|-----------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 7

bit 13-8 **RXELM<5:0>:** Receive Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

TXELM4<sup>(2)</sup>

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **TXELM<5:0>:** Transmit Buffer Element Count bits (valid in Enhanced Buffer mode)<sup>(1,2,3)</sup>

Note 1: RXELM3 and TXELM3 bits are only present when FIFODEPTH = 8 or higher.

2: RXELM4 and TXELM4 bits are only present when FIFODEPTH = 16 or higher.

3: RXELM5 and TXELM5 bits are only present when FIFODEPTH = 32.

#### 20.4.2 RECEIVING AN IN TOKEN IN DEVICE MODE

- 1. Attach to a USB host and enumerate as described in Chapter 9 of the *"USB 2.0 Specification"*.

- 2. Create a data buffer and populate it with the data to send to the host.

- 3. In the appropriate (even or odd) TX BD for the desired endpoint:

- a) Set up the status register (BDnSTAT) with the correct data toggle (DATA0/1) value and the byte count of the data buffer.

- b) Set up the address register (BDnADR) with the starting address of the data buffer.

- c) Set the UOWN bit of the status register to '1'.

- When the USB module receives an IN token, it automatically transmits the data in the buffer. Upon completion, the module updates the status register (BDnSTAT) and sets the Token Complete Interrupt Flag, TRNIF (U1IR<3>).

## 20.4.3 RECEIVING AN OUT TOKEN IN DEVICE MODE

- 1. Attach to a USB host and enumerate as described in Chapter 9 of the "USB 2.0 Specification".

- 2. Create a data buffer with the amount of data you are expecting from the host.

- 3. In the appropriate (even or odd) TX BD for the desired endpoint:

- a) Set up the status register (BDnSTAT) with the correct data toggle (DATA0/1) value and the byte count of the data buffer.

- b) Set up the address register (BDnADR) with the starting address of the data buffer.

- c) Set the UOWN bit of the status register to '1'.

- 4. When the USB module receives an OUT token, it automatically receives the data sent by the host to the buffer. Upon completion, the module updates the status register (BDnSTAT) and sets the Token Complete Interrupt Flag, TRNIF (U1IR<3>).

## 20.5 Host Mode Operation

The following sections describe how to perform common Host mode tasks. In Host mode, USB transfers are invoked explicitly by the host software. The host software is responsible for the Acknowledge portion of the transfer. Also, all transfers are performed using the Endpoint 0 Control register (U1EP0) and Buffer Descriptors.

#### 20.5.1 ENABLE HOST MODE AND DISCOVER A CONNECTED DEVICE

- Enable Host mode by setting the HOSTEN bit (U1CON<3>). This causes the Host mode control bits in other USB OTG registers to become available.

- Enable the D+ and D- pull-down resistors by setting the DPPULDWN and DMPULDWN bits (U10TGCON<5:4>). Disable the D+ and Dpull-up resistors by clearing the DPPULUP and DMPULUP bits (U10TGCON<7:6>).

- At this point, SOF generation begins with the SOF counter loaded with 12,000. Eliminate noise on the USB by clearing the SOFEN bit (U1CON<0>) to disable Start-of-Frame (SOF) packet generation.

- 4. Enable the device attached interrupt by setting the ATTACHIE bit (U1IE<6>).

- Wait for the device attached interrupt (U1IR<6> = 1). This is signaled by the USB device changing the state of D+ or D- from '0' to '1' (SE0 to J-state). After it occurs, wait 100 ms for the device power to stabilize.

- Check the state of the JSTATE and SE0 bits in U1CON. If the JSTATE bit (U1CON<7>) is '0', the connecting device is low speed. If the connecting device is low speed, set the LSPDEN and LSPD bits (U1ADDR<7> and U1EP0<7>) to enable low-speed operation.

- Reset the USB device by setting the USBRST bit (U1CON<4>) for at least 50 ms, sending Reset signaling on the bus. After 50 ms, terminate the Reset by clearing USBRST.

- 8. In order to keep the connected device from going into suspend, enable the SOF packet generation by setting the SOFEN bit.

- 9. Wait 10 ms for the device to recover from Reset.

- 10. Perform enumeration as described by Chapter 9 of the "USB 2.0 Specification".

## REGISTER 20-12: U1CNFG1: USB CONFIGURATION REGISTER 1

| —     |

|-------|

| bit 8 |

|       |

| R/W-0 |

| PPB0  |

| bit 0 |

|       |

|       |

| own   |

| )WN   |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

Note 1: This bit is only active when the UTRDIS bit (U1CNFG2<0>) is set.

#### 20.7.2 USB INTERRUPT REGISTERS

#### REGISTER 20-14: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|

| IDIF      | T1MSECIF  | LSTATEIF  | ACTVIF    | SESVDIF   | SESENDIF  | —   | VBUSVDIF  |

| bit 7     |           |           |           |           |           |     | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | K = Write '1' to Clear bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                    |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | IDIF: ID State Change Indicator bit                                                                                                           |

|          | 1 = Change in ID state is detected                                                                                                            |

|          | 0 = No ID state change is detected                                                                                                            |

| bit 6    | T1MSECIF: 1 Millisecond Timer bit                                                                                                             |

|          | 1 = The 1 millisecond timer has expired                                                                                                       |

|          | 0 = The 1 millisecond timer has not expired                                                                                                   |

| bit 5    | LSTATEIF: Line State Stable Indicator bit                                                                                                     |

|          | <ul> <li>1 = USB line state (as defined by the SE0 and JSTATE bits) has been stable for 1 ms, but different from<br/>the last time</li> </ul> |

|          | 0 = USB line state has not been stable for 1 ms                                                                                               |

| bit 4    | ACTVIF: Bus Activity Indicator bit                                                                                                            |

|          | 1 = Activity on the D+/D- lines or VBUS is detected                                                                                           |

|          | 0 = No activity on the D+/D- lines or VBUS is detected                                                                                        |

| bit 3    | SESVDIF: Session Valid Change Indicator bit                                                                                                   |

|          | 1 = VBUS has crossed VA_SESS_END (as defined in the <i>"USB 2.0 Specification"</i> ) <sup>(1)</sup><br>0 = VBUS has not crossed VA_SESS_END   |

| bit 2    | SESENDIF: B-Device VBUS Change Indicator bit                                                                                                  |

|          | 1 = VBUS change on B-device is detected; VBUS has crossed VB_SESS_END (as defined in the "USB 2.0<br>Specification") <sup>(1)</sup>           |

|          | 0 = VBUS has not crossed VB_SESS_END                                                                                                          |

| bit 1    | Unimplemented: Read as '0'                                                                                                                    |

| bit 0    | VBUSVDIF: A-Device VBUS Change Indicator bit                                                                                                  |

|          | 1 = VBUS change on A-device is detected; VBUS has crossed VA_VBUS_VLD (as defined in the "USB 2.0<br>Specification") <sup>(1)</sup>           |