Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | PIC                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 32MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 1MB (341.5K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj1024gb610t-i-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin | Function                                         | Pin | Function                          |

|-----|--------------------------------------------------|-----|-----------------------------------|

| 1   | OCM1C/CTED3/RG15                                 | 51  | RP16/RF3                          |

| 2   | Vdd                                              | 52  | RP30/RF2                          |

| 3   | IC4/CTED4/PMD5/RE5                               | 53  | RP15/RF8                          |

| 4   | SCL3/IC5/PMD6/RE6                                | 54  | RF7                               |

| 5   | SDA3/IC6/PMD7/RE7                                | 55  | INT0/RF6                          |

| 6   | RPI38/OCM1D/RC1                                  | 56  | SDA1/RG3                          |

| 7   | RPI39/OCM2C/RC2                                  | 57  | SCL1/RG2                          |

| 8   | RPI40/OCM2D/RC3                                  | 58  | PMPCS1/SCL2/RA2                   |

| 9   | AN16/RPI41/OCM3C/PMCS2/RC4                       | 59  | SDA2/PMA20/RA3                    |

| 10  | AN17/C1IND/RP21/ICM1/OCM1A/PMA5/RG6              | 60  | TDI/PMA21/RA4                     |

| 11  | AN18/C1INC/RP26/OCM1B/PMA4/RG7                   | 61  | TDO/RA5                           |

| 12  | AN19/C2IND/RP19/ICM2/OCM2A/PMA3/RG8              | 62  | VDD                               |

| 13  | MCLR                                             | 63  | OSCI/CLKI/RC12                    |

| 14  | AN20/C1INC/C2INC/C3INC/RP27/OCM2B/PMA2/PMALU/RG9 | 64  | OSCO/CLKO/RC15                    |

| 15  | Vss                                              | 65  | Vss                               |

| 16  | Vdd                                              | 66  | RPI36/PMA22/RA14                  |

| 17  | TMS/OCM3D/RA0                                    | 67  | RPI35/PMBE1/RA15                  |

| 18  | RPI33/PMCS1/RE8                                  | 68  | CLC4OUT/RP2/U6RTS/U6BCLK/ICM5/RD8 |

| 19  | AN21/ <b>RPI34</b> /PMA19/RE9                    | 69  | RP4/PMACK2/RD9                    |

| 20  | PGEC3/AN5/C1INA/RP18/ICM3/OCM3A/RB5              | 70  | RP3/PMA15/PMCS2/RD10              |

| 21  | PGED3/AN4/C1INB/RP28/OCM3B/RB4                   | 71  | RP12/PMA14/PMCS1/RD11             |

| 22  | AN3/C2INA/RB3                                    | 72  | CLC3OUT/RP11/U6CTS/ICM6/RD0       |

| 23  | AN2/CTCMP/C2INB/RP13/CTED13/RB2                  | 73  | SOSCI/C3IND/RC13                  |

| 24  | PGEC1/ALTCVREF-/ALTVREF-/AN1/RP1/CTED12/RB1      | 74  | SOSCO/C3INC/RPI37/PWRLCLK/RC14    |

| 25  | PGED1/ALTCVREF+/ALTVREF+/AN0/ <b>RP0</b> /RB0    | 75  | Vss                               |

| 26  | PGEC2/AN6/ <b>RP6</b> /RB6                       | 76  | RP24/U5TX/ICM4/RD1                |

| 27  | PGED2/AN7/ <b>RP7</b> /U6TX/RB7                  | 77  | RP23/PMACK1/RD2                   |

| 28  | CVREF-/VREF-/PMA7/RA9                            | 78  | RP22/ICM7/PMBE0/RD3               |

| 29  | CVREF+/VREF+/PMA6/RA10                           | 79  | RPI42/OCM3E/PMD12/RD12            |

| 30  | AVdd                                             | 80  | OCM3F/PMD13/RD13                  |

| 31  | AVss                                             | 81  | RP25/PMWR/PMENB/RD4               |

| 32  | AN8/RP8/PWRGT/RB8                                | 82  | RP20/PMRD/PMWR/RD5                |

| 33  | AN9/TMPR/ <b>RP9</b> /T1CK/RB9                   | 83  | C3INB/U5RX/OC4/PMD14/RD6          |

| 34  | CVREF/AN10/PMA13/RB10                            | 84  | C3INA/U5RTS/U5BCLK/OC5/PMD15/RD7  |

| 35  | AN11/REFI/PMA12/RB11                             | 85  | VCAP                              |

| 36  | Vss                                              | 86  | N/C                               |

| 37  | Vdd                                              | 87  | U5CTS/OC6/PMD11/RF0               |

| 38  | TCK/RA1                                          | 88  | PMD10/RF1                         |

| 39  | <b>RP31</b> /RF13                                | 89  | PMD9/RG1                          |

| 40  | RPI32/CTED7/PMA18/RF12                           | 90  | PMD8/RG0                          |

| 41  | AN12/U6RX/CTED2/PMA11/RB12                       | 91  | AN23/OCM1E/RA6                    |

| 42  | AN13/CTED1/PMA10/RB13                            | 92  | AN22/OCM1F/PMA17/RA7              |

| 43  | AN14/RP14/CTED5/CTPLS/PMA1/PMALH/RB14            | 93  | PMD0/RE0                          |

| 44  | AN15/RP29/CTED6/PMA0/PMALL/RB15                  | 94  | PMD1/RE1                          |

| 45  | Vss                                              | 95  | CTED11/PMA16/RG14                 |

| 46  | Vdd                                              | 96  | OCM2E/RG12                        |

| 47  | RPI43/RD14                                       | 97  | OCM2F/CTED10/RG13                 |

| 48  | <b>RP5</b> /RD15                                 | 98  | PMD2/RE2                          |

| 49  | RP10/PMA9/RF4                                    | 99  | CTED9/PMD3/RE3                    |

| 50  | <b>RP17</b> /PMA8/RF5                            | 100 | HLVDIN/CTED8/PMD4/RE4             |

|     |                                                  |     |                                   |

TABLE 4: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJXXXGA610 TQFP)

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select (PPS) functions.

Note: Pinouts are subject to change.

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                 |                           |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|---------------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer | Description               |

| IOCD0           | 46                                  | 46                               | 72                               | 72                               | D9                      | D9                      | Ι   | ST              | PORTD Interrupt-on-Change |

| IOCD1           | 49                                  | 49                               | 76                               | 76                               | A11                     | A11                     | Ι   | ST              |                           |

| IOCD2           | 50                                  | 50                               | 77                               | 77                               | A10                     | A10                     | Ι   | ST              |                           |

| IOCD3           | 51                                  | 51                               | 78                               | 78                               | B9                      | B9                      | Ι   | ST              |                           |

| IOCD4           | 52                                  | 52                               | 81                               | 81                               | C8                      | C8                      | Ι   | ST              |                           |

| IOCD5           | 53                                  | 53                               | 82                               | 82                               | B8                      | B8                      | Ι   | ST              |                           |

| IOCD6           | 54                                  | 54                               | 83                               | 83                               | D7                      | D7                      | Ι   | ST              |                           |

| IOCD7           | 55                                  | 55                               | 84                               | 84                               | C7                      | C7                      | Ι   | ST              |                           |

| IOCD8           | 42                                  | 42                               | 68                               | 68                               | E9                      | E9                      | Ι   | ST              |                           |

| IOCD9           | 43                                  | 43                               | 69                               | 69                               | E10                     | E10                     | Ι   | ST              |                           |

| IOCD10          | 44                                  | 44                               | 70                               | 70                               | D11                     | D11                     | Ι   | ST              |                           |

| IOCD11          | 45                                  | 45                               | 71                               | 71                               | C11                     | C11                     | Ι   | ST              |                           |

| IOCD12          | _                                   | _                                | 79                               | 79                               | A9                      | A9                      | Ι   | ST              |                           |

| IOCD13          | _                                   | —                                | 80                               | 80                               | D8                      | D8                      | Ι   | ST              |                           |

| IOCD14          | —                                   | —                                | 47                               | 47                               | L9                      | L9                      | Ι   | ST              |                           |

| IOCD15          | _                                   | _                                | 48                               | 48                               | K9                      | K9                      | Ι   | ST              |                           |

| IOCE0           | 60                                  | 60                               | 93                               | 93                               | A4                      | A4                      | Ι   | ST              | PORTE Interrupt-on-Change |

| IOCE1           | 61                                  | 61                               | 94                               | 94                               | B4                      | B4                      | Ι   | ST              |                           |

| IOCE2           | 62                                  | 62                               | 98                               | 98                               | B3                      | B3                      | Ι   | ST              |                           |

| IOCE3           | 63                                  | 63                               | 99                               | 99                               | A2                      | A2                      | Ι   | ST              |                           |

| IOCE4           | 64                                  | 64                               | 100                              | 100                              | A1                      | A1                      | Ι   | ST              |                           |

| IOCE5           | 1                                   | 1                                | 3                                | 3                                | D3                      | D3                      | Ι   | ST              |                           |

| IOCE6           | 2                                   | 2                                | 4                                | 4                                | C1                      | C1                      | Ι   | ST              |                           |

| IOCE7           | 3                                   | 3                                | 5                                | 5                                | D2                      | D2                      | Ι   | ST              |                           |

| IOCE8           |                                     | _                                | 18                               | 18                               | G1                      | G1                      | Ι   | ST              |                           |

| IOCE9           | _                                   | _                                | 19                               | 19                               | G2                      | G2                      | Ι   | ST              |                           |

### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated Transceiver

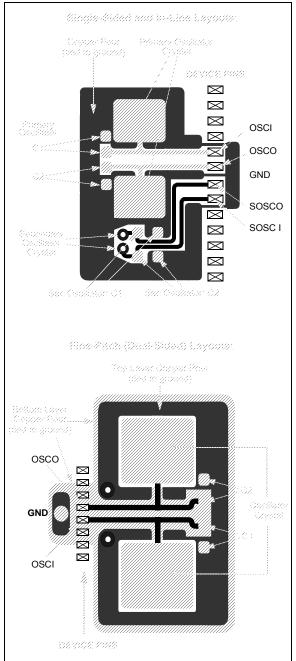

### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator (refer to **Section 9.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

- AN1798, "Crystal Selection for Low-Power Secondary Oscillator"

#### FIGURE 2-5:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| File Name      | Address          | All Resets | File Name        | Address           | All Resets |

|----------------|------------------|------------|------------------|-------------------|------------|

| SPI (CONTINUED | ))               |            | CONFIGURABLE LC  | GIC CELL (CLC) (C | ONTINUED)  |

| SPI1BUFL       | 0400             | 0000       | CLC3CONL         | 047C              | 0000       |

| SPI1BUFH       | 0402             | 0000       | CLC3CONH         | 047E              | 0000       |

| SPI1BRGL       | 0404             | xxxx       | CLC3SELL         | 0480              | 0000       |

| SPI1IMSK1      | 0408             | 0000       | CLC3GLSL         | 0484              | 0000       |

| SPI1IMSK2      | 040A             | 0000       | CLC3GLSH         | 0486              | 0000       |

| SPI1URDTL      | 040C             | 0000       | CLC4CONL         | 0488              | 0000       |

| SPI1URDTH      | 040E             | 0000       | CLC4CONH         | 048A              | 0000       |

| SPI2CON1       | 0410             | 0x00       | CLC4SELL         | 048C              | 0000       |

| SPI2CON2       | 0412             | 0000       | CLC4GLSL         | 0490              | 0000       |

| SPI2CON3       | 0414             | 0000       | CLC4GLSH         | 0492              | 0000       |

| SPI2STATL      | 0418             | 0028       | l <sup>2</sup> C |                   |            |

| SPI2STATH      | 041A             | 0000       | I2C1RCV          | 0494              | 0000       |

| SPI2BUFL       | 041C             | 0000       | I2C1TRN          | 0496              | 00FF       |

| SPI2BUFH       | 041E             | 0000       | I2C1BRG          | 0498              | 0000       |

| SPI2BRGL       | 0420             | xxxx       | I2C1CON1         | 049A              | 1000       |

| SPI2IMSK1      | 0424             | 0000       | I2C1CON2         | 049C              | 0000       |

| SPI2IMSK2      | 0426             | 0000       | I2C1STAT         | 049E              | 0000       |

| SPI2URDTL      | 0428             | 0000       | I2C1ADD          | 04A0              | 0000       |

| SPI2URDTH      | 042A             | 0000       | I2C1MSK          | 04A2              | 0000       |

| SPI3CON1       | 042C             | 0x00       | I2C2RCV          | 04A4              | 0000       |

| SPI3CON2       | 042E             | 0000       | I2C2TRN          | 04A6              | 00FF       |

| SPI3CON3       | 0430             | 0000       | I2C2BRG          | 04A8              | 0000       |

| SPI3STATL      | 0434             | 0028       | I2C2CON1         | 04AA              | 1000       |

| SPI3STATH      | 0436             | 0000       | I2C2CON2         | 04AC              | 0000       |

| SPI3BUFL       | 0438             | 0000       | I2C2STAT         | 04AE              | 0000       |

| SPI3BUFH       | 043A             | 0000       | I2C2ADD          | 04B0              | 0000       |

| SPI3BRGL       | 043C             | xxxx       | I2C2MSK          | 04B2              | 0000       |

| SPI3IMSK1      | 0440             | 0000       | I2C3RCV          | 04B4              | 0000       |

| SPI3IMSK2      | 0442             | 0000       | I2C3TRN          | 04B6              | 00FF       |

| SPI3URDTL      | 0444             | 0000       | I2C3BRG          | 04B8              | 0000       |

| SPI3URDTH      | 0446             | 0000       | I2C3CON1         | 04BA              | 1000       |

| CONFIGURABLE   | LOGIC CELL (CLC) |            | I2C3CON2         | 04BC              | 0000       |

| CLC1CONL       | 0464             | 0000       | I2C3STAT         | 04BE              | 0000       |

| CLC1CONH       | 0466             | 0000       | I2C3ADD          | 04C0              | 0000       |

| CLC1SELL       | 0468             | 0000       | I2C3MSK          | 04C2              | 0000       |

| CLC1GLSL       | 046C             | 0000       | DMA              |                   |            |

| CLC1GLSH       | 046E             | 0000       | DMACON           | 04C4              | 0000       |

| CLC2CONL       | 0470             | 0000       | DMABUF           | 04C6              | 0000       |

| CLC2CONH       | 0472             | 0000       | DMAL             | 04C8              | 0000       |

| CLC2SELL       | 0474             | 0000       | DMAH             | 04CA              | 0000       |

| CLC2GLSL       | 0478             | 0000       | DMACH0           | 04CC              | 0000       |

| CLC2GLSH       | 047A             | 0000       | DMAINT0          | 04CE              | 0000       |

### TABLE 4-8: SFR MAP: 0400h BLOCK

**Legend:** — = unimplemented, read as '0'; x = undefined. Reset values are shown in hexadecimal.

### REGISTER 8-5: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/C-0  | R/C-0 |

|-------|-----|-----|-----|-----|-----|--------|-------|

| —     | —   | —   | —   | —   | —   | ECCDBE | SGHT  |

| bit 7 |     |     |     |     |     |        | bit 0 |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 ECCDBE: ECC Double-Bit Error Trap bit 1 = ECC Double-Bit Error trap has occurred 0 = ECC Double-Bit Error trap has not occurred

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

# 11.3 Interrupt-on-Change (IOC)

The Interrupt-on-Change function of the I/O ports allows the PIC24FJ1024GA610/GB610 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode when the clocks are disabled.

Interrupt-on-Change functionality is enabled on a pin by setting the IOCPx and/or IOCNx register bit for that pin. For example, PORTC has register names, IOCPC and IOCNC, for these functions. Setting a value of '1' in the IOCPx register enables interrupts for low-to-high transitions, while setting a value of '1' in the IOCNx register enables interrupts for high-to-low transitions. Setting a value of '1' in both register bits will enable interrupts for either case (e.g., a pulse on the pin will generate two interrupts). In order for any IOC to be detected, the global IOC Interrupt Enable bit (IEC1<3>) must be set, the IOCON bit (PADCON<15>) set and the associated IFSx flag cleared.

When an interrupt request is generated for a pin, the corresponding status flag (IOCFx register bit) will be set, indicating that a Change-of-State occurred on that pin. The IOCFx register bit will remain set until cleared by writing a zero to it. When any IOCFx flag bit in a given port is set, the corresponding IOCPxF bit in the IOCSTAT register will be set. This flag indicates that a change was detected on one of the bits on the given port. The IOCPxF flag will be cleared when all IOCFx<15:0> bits are cleared.

Multiple individual status flags can be cleared by writing a zero to one or more bits using a Read-Modify-Write operation. If another edge is detected on a pin whose status bit is being cleared during the Read-Modify-Write sequence, the associated change flag will still be set at the end of the Read-Modify-Write sequence. The user should use the instruction sequence (or equivalent) shown in Example 11-1 to clear the Interrupt-on-Change Status registers.

At the end of this sequence, the W0 register will contain a zero for each bit for which the port pin had a change detected. In this way, any indication of a pin changing will not be lost.

Due to the asynchronous and real-time nature of the Interrupt-on-Change, the value read on the port pins may not indicate the state of the port when the change was detected, as a second change can occur during the interval between clearing the flag and reading the port. It is up to the user code to handle this case if it is a possibility in their application. To keep this interval to a minimum, it is recommended that any code modifying the IOCFx registers be run either in the interrupt handler or with interrupts disabled.

Each Interrupt-on-Change (IOC) pin has both a weak pull-up and a weak pull-down connected to it. The pullups act as a current source connected to the pin, while the pull-downs act as a current sink connected to the pin. These eliminate the need for external resistors when push button or keypad devices are connected.

The pull-ups and pull-downs are separately enabled using the IOCPUx registers (for pull-ups) and the IOCPDx registers (for pull-downs). Each IOC pin has individual control bits for its pull-up and pull-down. Setting a control bit enables the weak pull-up or pull-down for the corresponding pin.

**Note:** Pull-ups and pull-downs on pins should always be disabled whenever the pin is configured as a digital output.

### EXAMPLE 11-1: IOC STATUS READ/CLEAR IN ASSEMBLY

| MOV | OxFFFF, WO | ; Initial mask value 0xFFFF -> W0      |

|-----|------------|----------------------------------------|

| XOR | IOCFx, W0  | ; W0 has '1' for each bit set in IOCFx |

| AND | IOCFx      | ; IOCFx & WO ->IOCFx                   |

### EXAMPLE 11-2: PORT READ/WRITE IN ASSEMBLY

| MOV 0xFF00, W0  | ; Configure PORTB<15:8> as inputs |

|-----------------|-----------------------------------|

| MOV W0, TRISB   | ; and PORTB<7:0> as outputs       |

| NOP             | ; Delay 1 cycle                   |

| BTSS PORTB, #13 | ; Next Instruction                |

### EXAMPLE 11-3: PORT READ/WRITE IN 'C'

| TRISB = 0xFF00;                    | // Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|------------------------------------|--------------------------------------------------------------|

| Nop();                             | // Delay 1 cycle                                             |

| <pre>If (PORTBbits.RB13){ };</pre> | // Test if RB13 is a `1'                                     |

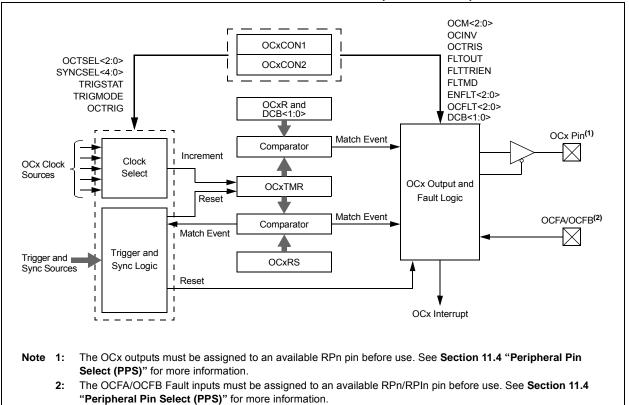

### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

15.2 Compare Operations

In Compare mode (Figure 15-1), the output compare module can be configured for Single-Shot or Continuous mode pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins if available on the OCx module you are using. Otherwise, configure the dedicated OCx output pins.

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate the time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse based on the desired pulse width and the time to the rising edge of the pulse.

- 3. Write the rising edge value to OCxR and the falling edge value to OCxRS.

- 4. Set the Timer Period register, PRy, to a value equal to or greater than the value in OCxRS.

- 5. Set the OCM<2:0> bits for the appropriate compare operation (= 0xx).

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure Trigger operation and TRIGSTAT to select a hardware or software Trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the Trigger or Sync source. If free-running timer operation is required, set the SYNCSELx bits to '00000' (no Sync/Trigger source).

- Select the time base source with the OCTSEL<2:0> bits. If necessary, set the TON bit for the selected timer, which enables the compare time base to count. Synchronous mode operation starts as soon as the time base is enabled; Trigger mode operation starts after a Trigger source event occurs.

### REGISTER 17-1: SPIx CONTROL REGISTER 1 LOW (CONTINUED)

| bit 8 | CKE: SPIx Clock Edge Select bit <sup>(1)</sup>                                                                                                                                                                             |       |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|       | <ul> <li>1 = Transmit happens on transition from active clock state to Idle clock state</li> <li>0 = Transmit happens on transition from Idle clock state to active clock state</li> </ul>                                 |       |

| bit 7 | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(2)</sup>                                                                                                                                                           |       |

|       | 1 = $\overline{SSx}$ pin is used by the macro in Slave mode; $\overline{SSx}$ pin is used as the slave select 0 = $\overline{SSx}$ pin is not used by the macro ( $\overline{SSx}$ pin will be controlled by the port I/O) | input |

| bit 6 | CKP: SPIx Clock Polarity Select bit                                                                                                                                                                                        |       |

|       | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                   |       |

| bit 5 | MSTEN: Master Mode Enable bit                                                                                                                                                                                              |       |

|       | 1 = Master mode<br>0 = Slave mode                                                                                                                                                                                          |       |

| bit 4 | DISSDI: Disable SDIx Input Port bit                                                                                                                                                                                        |       |

|       | <ul> <li>1 = SDIx pin is not used by the module; pin is controlled by the port function</li> <li>0 = SDIx pin is controlled by the module</li> </ul>                                                                       |       |

| bit 3 | DISSCK: Disable SCKx Output Port bit                                                                                                                                                                                       |       |

|       | <ul> <li>1 = SCKx pin is not used by the module; pin is controlled by the port function</li> <li>0 = SCKx pin is controlled by the module</li> </ul>                                                                       |       |

| bit 2 | MCLKEN: Master Clock Enable bit <sup>(3)</sup>                                                                                                                                                                             |       |

|       | <ul> <li>1 = REFO output is used by the BRG</li> <li>0 = Peripheral clock is used by the BRG</li> </ul>                                                                                                                    |       |

| bit 1 | SPIFE: Frame Sync Pulse Edge Select bit                                                                                                                                                                                    |       |

|       | <ul> <li>1 = Frame Sync pulse (Idle-to-active edge) coincides with the first bit clock</li> <li>0 = Frame Sync pulse (Idle-to-active edge) precedes the first bit clock</li> </ul>                                         |       |

| bit 0 | ENHBUF: Enhanced Buffer Mode Enable bit                                                                                                                                                                                    |       |

|       | 1 = Enhanced Buffer mode is enabled<br>0 = Enhanced Buffer mode is disabled                                                                                                                                                |       |

|       |                                                                                                                                                                                                                            |       |

| Note  | When AUDEN = 1, this module functions as if $CKE = 0$ , regardless of its actual value.                                                                                                                                    |       |

- 2: When FRMEN = 1, SSEN is not used.

- **3:** MCLKEN can only be written when the SPIEN bit = 0.

- 4: This channel is not meaningful for DSP/PCM mode as LRC follows the FRMSYPW bit.

# 19.2 Transmitting in 8-Bit Data Mode

- 1. Set up the UARTx:

- a) Write appropriate values for data, parity and Stop bits.

- b) Write appropriate baud rate value to the UxBRG register.

- c) Set up transmit and receive interrupt enable and priority bits.

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt, two cycles after being set).

- 4. Write a data byte to the lower byte of the UxTXREG word. The value will be immediately transferred to the Transmit Shift Register (TSR) and the serial bit stream will start shifting out with the next rising edge of the baud clock.

- Alternatively, the data byte may be transferred while UTXEN = 0 and then the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- 6. A transmit interrupt will be generated as per interrupt control bits, UTXISEL<1:0>.

# 19.3 Transmitting in 9-Bit Data Mode

- 1. Set up the UARTx (as described in **Section 19.2** "**Transmitting in 8-Bit Data Mode**").

- 2. Enable the UARTx.

- 3. Set the UTXEN bit (causes a transmit interrupt).

- 4. Write UxTXREG as a 16-bit value only.

- 5. A word write to UxTXREG triggers the transfer of the 9-bit data to the TSR. The serial bit stream will start shifting out with the first rising edge of the baud clock.

- 6. A transmit interrupt will be generated as per the setting of control bits, UTXISELx.

# 19.4 Break and Sync Transmit Sequence

The following sequence will send a message frame header, made up of a Break, followed by an auto-baud Sync byte.

- 1. Configure the UARTx for the desired mode.

- 2. Set UTXEN and UTXBRK to set up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG; this loads the Sync character into the transmit FIFO.

- 5. After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

# 19.5 Receiving in 8-Bit or 9-Bit Data Mode

- 1. Set up the UARTx (as described in Section 19.2 "Transmitting in 8-Bit Data Mode").

- Enable the UARTx by setting the URXEN bit (UxSTA<12>).

- 3. A receive interrupt will be generated when one or more data characters have been received as per interrupt control bits, URXISEL<1:0>.

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- 5. Read UxRXREG.

The act of reading the UxRXREG character will move the next character to the top of the receive FIFO, including a new set of PERR and FERR values.

# 19.6 Operation of UxCTS and UxRTS Control Pins

UARTx Clear-to-Send (UxCTS) and Request-to-Send (UxRTS) are the two hardware-controlled pins that are associated with the UARTx modules. These two pins allow the UARTx to operate in Simplex and Flow Control mode. They are implemented to control the transmission and reception between the Data Terminal Equipment (DTE). The UEN<1:0> bits in the UxMODE register configure these pins.

# 19.7 Infrared Support

The UARTx module provides two types of infrared UART support: one is the IrDA clock output to support an external IrDA encoder and decoder device (legacy module support), and the other is the full implementation of the IrDA encoder and decoder. Note that because the IrDA modes require a 16x baud clock, they will only work when the BRGH bit (UxMODE<3>) is '0'.

### 19.7.1 IrDA CLOCK OUTPUT FOR EXTERNAL IrDA SUPPORT

To support external IrDA encoder and decoder devices, the BCLKx pin (same as the UxRTS pin) can be configured to generate the 16x baud clock. When UEN<1:0> = 11, the BCLKx pin will output the 16x baud clock if the UARTx module is enabled; it can be used to support the IrDA codec chip.

# 19.7.2 BUILT-IN IrDA ENCODER AND DECODER

The UARTx has full implementation of the IrDA encoder and decoder as part of the UARTx module. The built-in IrDA encoder and decoder functionality is enabled using the IREN bit (UxMODE<12>). When enabled (IREN = 1), the receive pin (UxRX) acts as the input from the infrared receiver. The transmit pin (UxTX) acts as the output to the infrared transmitter.

| R/W-0    | R/W-0                 | R/W-0    | R/W-0    | R/W-0, HC | R/W-0                | R-0, HSC  | R-1, HSC |

|----------|-----------------------|----------|----------|-----------|----------------------|-----------|----------|

| UTXISEL1 | UTXINV <sup>(1)</sup> | UTXISEL0 | URXEN    | UTXBRK    | UTXEN <sup>(2)</sup> | UTXBF     | TRMT     |

| bit 15   |                       |          |          |           |                      |           | bit 8    |

|          |                       |          |          |           |                      |           |          |

|          |                       |          |          |           |                      |           |          |

| R/W-0    | R/W-0                 | R/W-0    | R-1, HSC | R-0, HSC  | R-0, HSC             | R/C-0, HS | R-0, HSC |

### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| Legend: C = Clearable bit  |                           | HSC = Hardware Settable/Clearable bit |                    |  |

|----------------------------|---------------------------|---------------------------------------|--------------------|--|

| R = Readable bit           | W = Writable bit          | U = Unimplemented bit, read as '0'    |                    |  |

| -n = Value at POR          | '1' = Bit is set          | '0' = Bit is cleared                  | x = Bit is unknown |  |

| HS = Hardware Settable bit | HC = Hardware Clearable b | it                                    |                    |  |

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

11 = Reserved; do not use

bit 7

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit<sup>(1)</sup>

|         | IREN = 0:                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UxTX Idle state is '0'                                                                                                                                              |

|         | 0 = UxTX Idle state is '1'                                                                                                                                              |

|         | IREN = 1:                                                                                                                                                               |

|         | 1 = UxTX Idle state is '1'                                                                                                                                              |

|         | 0 = UxTX Idle state is '0'                                                                                                                                              |

| bit 12  | URXEN: UARTx Receive Enable bit                                                                                                                                         |

|         | 1 = Receive is enabled, UxRX pin is controlled by UARTx                                                                                                                 |

|         | 0 = Receive is disabled, UxRX pin is controlled by the port                                                                                                             |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                                        |

|         | 1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;                                                               |

|         | cleared by hardware upon completion                                                                                                                                     |

|         | 0 = Sync Break transmission is disabled or completed                                                                                                                    |

| bit 10  | UTXEN: UARTx Transmit Enable bit <sup>(2)</sup>                                                                                                                         |

|         | 1 = Transmit is enabled, UxTX pin is controlled by UARTx                                                                                                                |

|         | 0 = Transmit is disabled, any pending transmission is aborted and the buffer is reset; UxTX pin is                                                                      |

|         | controlled by the port                                                                                                                                                  |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                                                |

|         | 1 = Transmit buffer is full                                                                                                                                             |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                                             |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                                                     |

|         | 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)                                                                 |

|         | 0 = Transmit Shift Register is not empty, a transmission is in progress or queued                                                                                       |

| Note 4- | The value of this hit only effects the transmit properties of the module when the $IrD^{(R)}$ are derived as the transmit properties of the module when the $IrD^{(R)}$ |

| Note 1: | The value of this bit only affects the transmit properties of the module when the $IrDA^{(R)}$ encoder is enabled                                                       |

|         | (IREN = 1).                                                                                                                                                             |

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

© 2015-2016 Microchip Technology Inc.

bit 0

### REGISTER 20-2: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER PROTOTYPE, CPU MODE (BD0STAT THROUGH BD63STAT)

| R/W-x  | R/W-x              | r-0 | r-0 | R/W-x | R/W-x  | R/W-x, HSC | R/W-x, HSC |

|--------|--------------------|-----|-----|-------|--------|------------|------------|

| UOWN   | DTS <sup>(1)</sup> | —   | —   | DTSEN | BSTALL | BC9        | BC8        |

| bit 15 |                    |     |     |       |        |            | bit 8      |

| R/W-x, HSC |

|------------|------------|------------|------------|------------|------------|------------|------------|

| BC7        | BC6        | BC5        | BC4        | BC3        | BC2        | BC1        | BC0        |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend: r = Reserved bit |                  | HSC = Hardware Setta  | HSC = Hardware Settable/Clearable bit |  |  |

|--------------------------|------------------|-----------------------|---------------------------------------|--|--|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0'    |  |  |

| -n = Value at POR        | '1' = Bit is set | 'r' = Reserved bit    | x = Bit is unknown                    |  |  |

| bit 15    | UOWN: USB Own bit                                                                                                                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>0 = The microcontroller core owns the BD and its corresponding buffer; the USB module ignores all<br/>other fields in the BD</li> </ul>                                                                                                                                                      |

| bit 14    | DTS: Data Toggle Packet bit <sup>(1)</sup>                                                                                                                                                                                                                                                            |

|           | 1 = Data 1 packet                                                                                                                                                                                                                                                                                     |

|           | 0 = Data 0 packet                                                                                                                                                                                                                                                                                     |

| bit 13-12 | Reserved: Maintain as '0'                                                                                                                                                                                                                                                                             |

| bit 11    | DTSEN: Data Toggle Synchronization Enable bit                                                                                                                                                                                                                                                         |

|           | <ul> <li>1 = Data toggle synchronization is enabled; data packets with incorrect Sync value will be ignored</li> <li>0 = No data toggle synchronization is performed</li> </ul>                                                                                                                       |

| bit 10    | BSTALL: Buffer STALL Enable bit                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Buffer STALL is enabled; STALL handshake issued if a token is received that would use the BD in<br/>the given location (UOWN bit remains set, BD value is unchanged); corresponding EPSTALL bit<br/>will get set on any STALL handshake</li> <li>0 = Buffer STALL is disabled</li> </ul> |

| bit 9-0   | BC<9:0>: Byte Count bits                                                                                                                                                                                                                                                                              |

|           | This represents the number of bytes to be transmitted or the maximum number of bytes to be received during a transfer. Upon completion, the byte count is updated by the USB module with the actual number of bytes transmitted or received.                                                          |

| Note 1: ⊺ | his bit is ignored unless DTSEN = 1.                                                                                                                                                                                                                                                                  |

NOTES:

# PIC24FJ1024GA610/GB610 FAMILY

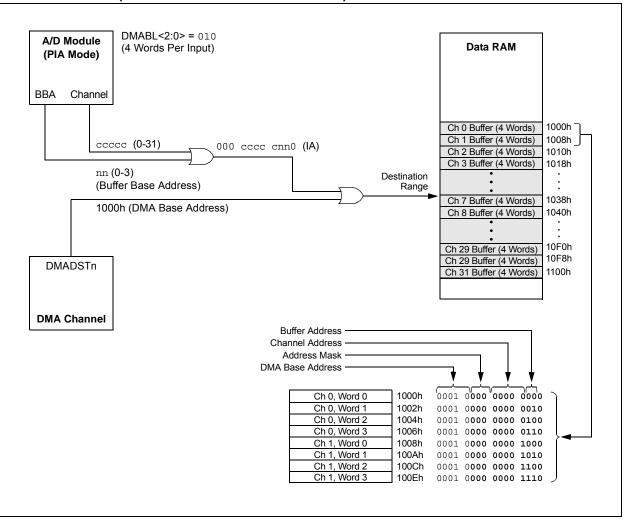

# FIGURE 25-2: EXAMPLE OF BUFFER ADDRESS GENERATION IN PIA MODE (4-WORD BUFFERS PER CHANNEL)

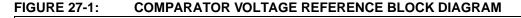

# 27.0 COMPARATOR VOLTAGE REFERENCE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Dual Comparator Module" (DS39710), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

# 27.1 Configuring the Comparator Voltage Reference

The voltage reference module is controlled through the CVRCON register (Register 27-1). The comparator voltage reference provides two ranges of output voltage, each with 32 distinct levels.

The comparator reference supply voltage can come from either VDD and VSS, or the external VREF+ and VREF-. The voltage source is selected by the CVRSS bit (CVRCON<5>).

The settling time of the comparator voltage reference must be considered when changing the CVREF output.

### **REGISTER 30-1: FBOOT CONFIGURATION REGISTER**

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1         | U-1    |

|--------|-----|-----|-----|-----|-----|-------------|--------|

| —      | —   | —   | —   | —   |     | —           | —      |

| bit 15 |     |     |     |     |     |             | bit 8  |

|        |     |     |     |     |     |             |        |

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | R/PO-1      | R/PO-1 |

|        | —   | —   | —   | _   | _   | BTMODE<1:0> |        |

| bit | 7 |

|-----|---|

|-----|---|

| Legend:           | PO = Program Once bit |                                    |                    |  |

|-------------------|-----------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as '1' |                    |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-2 Unimplemented: Read as '1'

bit 1-0 BTMODE<1:0>: Device Partition Mode Configuration Status bits

- 11 = Single Partition mode

- 10 = Dual Partition mode

- 01 = Protected Dual Partition mode (Partition 1 is write-protected when inactive)

- 00 = Reserved; do not use

### **REGISTER 30-2: FBTSEQ CONFIGURATION REGISTER**

| R/PO-1  | R/PO-1  | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |

|---------|---------|--------|--------|--------|--------|--------|--------|

| IBSEQ11 | IBSEQ10 | IBSEQ9 | IBSEQ8 | IBSEQ7 | IBSEQ6 | IBSEQ5 | IBSEQ4 |

| bit 23  |         |        |        |        |        |        | bit 16 |

| R/PO-1 |

|--------|--------|--------|--------|--------|--------|--------|--------|

| IBSEQ3 | IBSEQ2 | IBSEQ1 | IBSEQ0 | BSEQ11 | BSEQ10 | BSEQ9  | BSEQ8  |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/PO-1 |

|--------|--------|--------|--------|--------|--------|--------|--------|

| BSEQ7  | BSEQ6  | BSEQ5  | BSEQ4  | BSEQ3  | BSEQ2  | BSEQ1  | BSEQ0  |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | PO = Program Once bit |                             |                    |

|-------------------|-----------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read | d as '1'           |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared        | x = Bit is unknown |

bit 23-12 **IBSEQ<11:0>:** Inverse Boot Sequence Number bits (Dual Partition modes only) The one's complement of BSEQ<11:0>; must be calculated by the user and written into device programming.

# bit 11-0 **BSEQ<11:0>:** Boot Sequence Number bits (Dual Partition modes only) Relative value defining which partition will be active after a device Reset; the partition containing a lower boot number will be active.

bit 0

| DC CHARACTERISTICS |                          |      |       | Operating Condit<br>temperature |              | <b>DV to 3.6V (unless otherwise stated)</b><br>$D^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |  |  |

|--------------------|--------------------------|------|-------|---------------------------------|--------------|----------------------------------------------------------------------------------------------------|--|--|

| Parameter<br>No.   | Typical <sup>(1)</sup>   | Max  | Units | Operating<br>Temperature        | Vdd          | Conditions                                                                                         |  |  |

| Power-Dov          | vn Current <sup>(4</sup> | 4,5) |       | -                               |              |                                                                                                    |  |  |

| DC60               | 2.5                      | 10   | μA    | -40°C                           |              |                                                                                                    |  |  |

|                    | 3.2                      | 10   | μA    | +25°C                           | 2.0V<br>3.3V |                                                                                                    |  |  |

|                    | 11.5                     | 45   | μA    | +85°C                           |              | – Sleep <sup>(2)</sup>                                                                             |  |  |

|                    | 3.2                      | 10   | μA    | -40°C                           |              | - Sleep, /                                                                                         |  |  |

|                    | 4.0                      | 10   | μA    | +25°C                           |              |                                                                                                    |  |  |

|                    | 12.2                     | 45   | μA    | +85°C                           |              |                                                                                                    |  |  |

| DC61               | 165                      | _    | nA    | -40°C                           |              |                                                                                                    |  |  |

|                    | 190                      | _    | nA    | +25°C                           | 2.0V         |                                                                                                    |  |  |

|                    | 14.5                     |      | μA    | +85°C                           |              | – Low-Voltage Retention Sleep <sup>(3)</sup>                                                       |  |  |

|                    | 220                      |      | nA    | -40°C                           |              |                                                                                                    |  |  |

|                    | 300                      |      | nA    | +25°C                           | 3.3V         |                                                                                                    |  |  |

|                    | 15                       | _    | μA    | +85°C                           |              |                                                                                                    |  |  |

### TABLE 33-6: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The retention low-voltage regulator is disabled; RETEN (RCON<12>) = 0, LPCFG (FPOR<2>) = 1.

3: The retention low-voltage regulator is enabled; RETEN (RCON<12>) = 1, LPCFG (FPOR<2>) = 0.

4: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as outputs and driven low. WDT, etc., are all switched off.

5: These currents are measured on the device containing the most memory in this family.

### TABLE 33-11: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| Operatin     | <b>Operating Conditions:</b> -40°C < TA < +85°C (unless otherwise stated) |                                         |      |     |      |       |                                                                    |  |  |

|--------------|---------------------------------------------------------------------------|-----------------------------------------|------|-----|------|-------|--------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol                                                                    | Characteristics                         | Min  | Тур | Max  | Units | Comments                                                           |  |  |

| DVR          | TVREG                                                                     | Voltage Regulator Start-up Time         |      | 10  |      | μS    | VREGS = 0 with any POR or<br>BOR                                   |  |  |

| DVR10        | Vbg                                                                       | Internal Band Gap Reference             | 1.14 | 1.2 | 1.26 | V     |                                                                    |  |  |

| DVR11        | Tbg                                                                       | Band Gap Reference<br>Start-up Time     | _    | 1   | _    | ms    |                                                                    |  |  |

| DVR20        | Vrgout                                                                    | Regulator Output Voltage                | 1.6  | 1.8 | 2    | V     | VDD > 2.1V                                                         |  |  |

| DVR21        | Cefc                                                                      | External Filter Capacitor Value         | 10   | _   | -    | μF    | Series resistance < $3\Omega$<br>recommended; < $5\Omega$ required |  |  |

| DVR30        | Vlvr                                                                      | Low-Voltage Regulator<br>Output Voltage |      | 1.2 | —    | V     | RETEN = 1, LPCFG = 0                                               |  |  |

# TABLE 33-12: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

| Operati      | Operating Conditions: -40°C < TA < +85°C (unless otherwise stated) |                                          |                                  |      |      |      |       |                           |

|--------------|--------------------------------------------------------------------|------------------------------------------|----------------------------------|------|------|------|-------|---------------------------|

| Param<br>No. | Symbol                                                             | Characteristic                           |                                  |      | Тур  | Max  | Units | Conditions                |

| DC18         | VHLVD                                                              | HLVD Voltage on VDD                      | HLVDL<3:0> = 0100 <sup>(1)</sup> | 3.40 | _    | 3.74 | V     |                           |

|              |                                                                    | Transition                               | HLVDL<3:0> = 0101                | 3.25 | _    | 3.58 | V     |                           |

|              |                                                                    |                                          | HLVDL<3:0> = 0110                | 2.95 | _    | 3.25 | V     |                           |

|              |                                                                    |                                          | HLVDL<3:0> = 0111                | 2.75 | _    | 3.04 | V     |                           |

|              |                                                                    | HLVDL<3:0> = 1000                        | 2.65                             | _    | 2.93 | V    |       |                           |

|              |                                                                    |                                          | HLVDL<3:0> = 1001                | 2.45 |      | 2.75 | V     | VDIR = 1                  |

|              |                                                                    | HLVDL<3:0> = 1010                        | 2.35                             |      | 2.64 | V    |       |                           |

|              |                                                                    | HLVDL<3:0> = 1011                        | 2.25                             |      | 2.50 | V    |       |                           |

|              |                                                                    | HLVDL<3:0> = 1100                        | 2.15                             |      | 2.39 | V    |       |                           |

|              |                                                                    |                                          | HLVDL<3:0> = 1101                | 2.08 |      | 2.28 | V     |                           |

|              |                                                                    |                                          | HLVDL<3:0> = 1110                | 2.00 |      | 2.17 | V     |                           |

| DC101        | VTHL                                                               | HLVD Voltage on<br>HLVDIN Pin Transition | HLVDL<3:0> = 1111                | —    | 1.20 | _    | V     |                           |

| DC105        | TONLVD                                                             | HLVD Module Enable 1                     | īme                              |      | 5    | _    | μS    | From POR or<br>HLVDEN = 1 |

**Note 1:** Trip points for values of HLVD<3:0>, from '0000' to '0011', are not implemented.

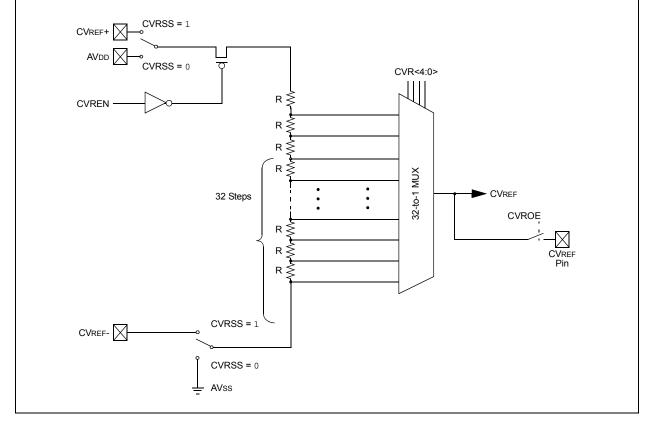

### FIGURE 33-3: EXTERNAL CLOCK TIMING

### TABLE 33-18: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               |                                                                         | Standard Operating Conditions:<br>Operating temperature |                    |                           | 2.0V to 3.6V (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for Industrial |                                      |  |

|--------------------|---------------|-------------------------------------------------------------------------|---------------------------------------------------------|--------------------|---------------------------|---------------------------------------------------------------------------------------|--------------------------------------|--|

| Param<br>No.       | Symbol        | Characteristic                                                          | Min                                                     | Typ <sup>(1)</sup> | Max                       | Units                                                                                 | Conditions                           |  |

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks allowed<br>only in EC mode) | DC<br>4                                                 |                    | 32<br>48                  | MHz<br>MHz                                                                            | EC<br>ECPLL (Note 2)                 |  |

|                    |               | Oscillator Frequency                                                    | 3.5<br>4<br>10<br>12<br>31                              |                    | 10<br>8<br>32<br>24<br>33 | MHz<br>MHz<br>MHz<br>MHz<br>kHz                                                       | XT<br>XTPLL<br>HS<br>HSPLL<br>SOSC   |  |

| OS20               | Tosc          | Tosc = 1/Fosc                                                           | —                                                       | —                  | _                         | —                                                                                     | See Parameter OS10 for<br>Fosc value |  |

| OS25               | Тсү           | Instruction Cycle Time <sup>(3)</sup>                                   | 62.5                                                    | _                  | DC                        | ns                                                                                    |                                      |  |

| OS30               | TosL,<br>TosH | External Clock in (OSCI)<br>High or Low Time                            | 0.45 x Tosc                                             | —                  | _                         | ns                                                                                    | EC                                   |  |

| OS31               | TosR,<br>TosF | External Clock in (OSCI)<br>Rise or Fall Time                           | —                                                       | —                  | 20                        | ns                                                                                    | EC                                   |  |

| OS40               | TckR          | CLKO Rise Time <sup>(4)</sup>                                           | —                                                       | 15                 | 30                        | ns                                                                                    |                                      |  |

| OS41               | TckF          | CLKO Fall Time <sup>(4)</sup>                                           | —                                                       | 15                 | 30                        | ns                                                                                    |                                      |  |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Represents input to the system clock prescaler. PLL dividers and postscalers must still be configured so that the system clock frequency does not exceed the maximum frequency shown in Figure 33-1.

3: Instruction cycle period (TCY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

4: Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 TcY) and high for the Q3-Q4 period (1/2 TcY).

# PIC24FJ1024GA610/GB610 FAMILY

# F

| Flash Program Memory    | 89 |

|-------------------------|----|

| and Table Instructions  |    |

| Control Registers       | 90 |

| Double-Word Programming | 95 |

| Enhanced ICSP Operation | 90 |

| JTAG Operation          | 90 |

| Operations              | 90 |

| Programming Algorithm   | 93 |

| RTSP Operation          |    |

# G

| Guidelines for Getting Started with 16-Bit MCUs | 41 |

|-------------------------------------------------|----|

| Analog/Digital Pins Configuration During ICSP   | 46 |

| External Oscillator Pins                        | 45 |

| ICSP Pins                                       | 44 |

| Master Clear (MCLR) Pin                         | 42 |

| Power Supply Pins                               | 42 |

| Unused I/Os                                     | 46 |

| Voltage Regulator Pin (VCAP)                    | 43 |

# Н

| High/Low-Voltage Detect (HLVD)     | . 387 |

|------------------------------------|-------|

| High/Low-Voltage Detect. See HLVD. |       |

### I

| I/O Ports 1                                       | 49              |

|---------------------------------------------------|-----------------|

| Analog Port Pins Configuration (ANSx) 1           | 50              |

| Configuring Analog/Digital Function of I/O Pins 1 | 150             |

| Input Voltage Levels for Port/Pin Tolerated       |                 |

| Description Input 1                               | 50              |

| Open-Drain Configuration1                         |                 |

| Parallel (PIO)1                                   |                 |

| Peripheral Pin Select1                            |                 |

| Write/Read Timing1                                |                 |

| I <sup>2</sup> C                                  |                 |

| Clock Rates2                                      | 249             |

| Communicating as Master in Single                 |                 |

| Master Environment2                               | 247             |

| Reserved Addresses2                               | 249             |

| Setting Baud Rate as Bus Master2                  | 249             |

| Slave Address Masking                             |                 |

| In-Circuit Debugger                               | 106             |

| Input Capture                                     |                 |

| 32-Bit Cascaded Mode1                             | 194             |

| Operations1                                       | 194             |

| Synchronous and Trigger Modes1                    | 193             |

| Input Capture with Dedicated Timers1              | 93              |

| Instruction Set                                   |                 |

| Overview                                          | 113             |

| Summary4                                          | ¥11             |

| Symbols Used in Opcode Descriptions4              | <b>1</b> 12     |

| Interfacing Program and Data Memory Spaces        | 76              |

| Inter-Integrated Circuit. See I <sup>2</sup> C.   |                 |

| Internet Address4                                 | <del>1</del> 63 |

| Interrupt Controller 1                            |                 |

| Alternate Interrupt Vector Table 1                | 03              |

| Control and Status Registers1                     | 08              |

| Interrupt Vector Details 1                        |                 |

| Interrupt Vector Table (IVT) 1                    | 103             |

| Reset Sequence1                                   | 103             |

| Resources1                                        | 108             |

| Trap Vectors 1                                    | 104             |

| Vector Tables1                                    | 04              |

| Interrupt-on-Change (IOC) 1                       | 154             |

| JTAG Interface                  | 406 |

|---------------------------------|-----|

| к                               |     |

| Key Features                    | 389 |