Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

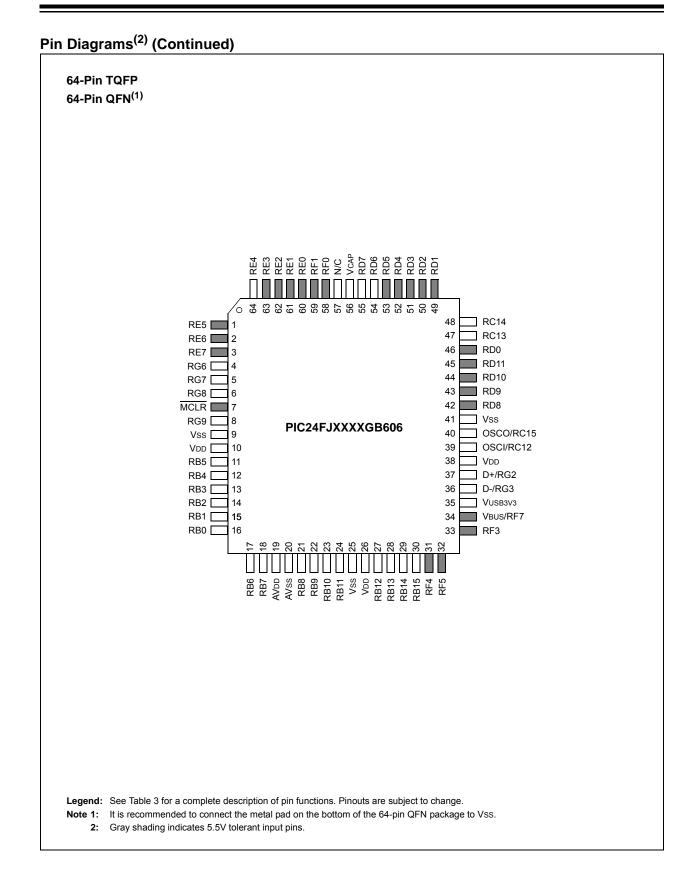

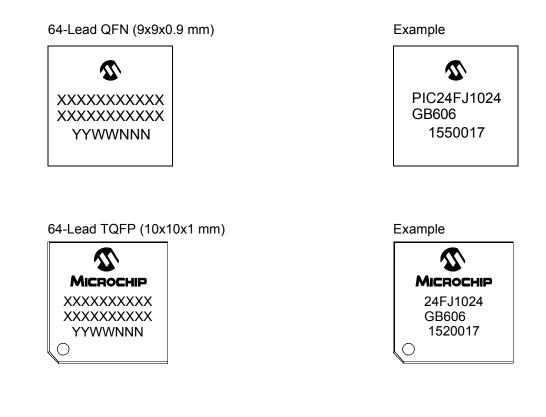

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga606-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

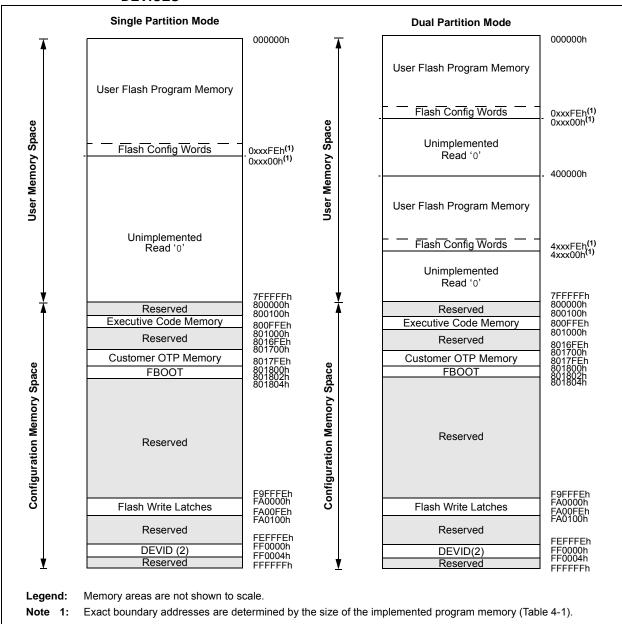

# FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FJ1024GA610/GB610 FAMILY DEVICES

# TABLE 4-1: PROGRAM MEMORY SIZES AND BOUNDARIES<sup>(1)</sup>

|                  | Program Memory   | y Upper Boundary (  |                    |                                |                                |

|------------------|------------------|---------------------|--------------------|--------------------------------|--------------------------------|

| Device           | Single Partition | Dual Partition Mode |                    | Write<br>Blocks <sup>(2)</sup> | Erase<br>Blocks <sup>(2)</sup> |

|                  | Mode             | Active Partition    | Inactive Partition |                                |                                |

| PIC24FJ1024GX6XX | 0ABFFEh (352K)   | 055FFEh (176K)      | 455FFEh (176K)     | 2752                           | 344                            |

| PIC24FJ512GX6XX  | 055FFEh (176K)   | 02AFFEh (88k)       | 42AFFEh (88k)      | 1376                           | 172                            |

| PIC24FJ256GX6XX  | 02AFFEh (88K)    | 0157FEh (44k)       | 4157FEh (44k)      | 688                            | 86                             |

| PIC24FJ128GX6XX  | 015FFEh (44K)    | 00AFFEh (22k)       | 40AFFEh (22k)      | 352                            | 44                             |

Note 1: Includes Flash Configuration Words.

2: 1 Write Block = 128 Instruction Words; 1 Erase Block = 1024 Instruction Words.

| File Name      | Address          | All Resets | File Name        | Address           | All Resets |

|----------------|------------------|------------|------------------|-------------------|------------|

| SPI (CONTINUED | ))               |            | CONFIGURABLE LC  | GIC CELL (CLC) (C | ONTINUED)  |

| SPI1BUFL       | 0400             | 0000       | CLC3CONL         | 047C              | 0000       |

| SPI1BUFH       | 0402             | 0000       | CLC3CONH         | 047E              | 0000       |

| SPI1BRGL       | 0404             | xxxx       | CLC3SELL         | 0480              | 0000       |

| SPI1IMSK1      | 0408             | 0000       | CLC3GLSL         | 0484              | 0000       |

| SPI1IMSK2      | 040A             | 0000       | CLC3GLSH         | 0486              | 0000       |

| SPI1URDTL      | 040C             | 0000       | CLC4CONL         | 0488              | 0000       |

| SPI1URDTH      | 040E             | 0000       | CLC4CONH         | 048A              | 0000       |

| SPI2CON1       | 0410             | 0x00       | CLC4SELL         | 048C              | 0000       |

| SPI2CON2       | 0412             | 0000       | CLC4GLSL         | 0490              | 0000       |

| SPI2CON3       | 0414             | 0000       | CLC4GLSH         | 0492              | 0000       |

| SPI2STATL      | 0418             | 0028       | l <sup>2</sup> C |                   |            |

| SPI2STATH      | 041A             | 0000       | I2C1RCV          | 0494              | 0000       |

| SPI2BUFL       | 041C             | 0000       | I2C1TRN          | 0496              | 00FF       |

| SPI2BUFH       | 041E             | 0000       | I2C1BRG          | 0498              | 0000       |

| SPI2BRGL       | 0420             | xxxx       | I2C1CON1         | 049A              | 1000       |

| SPI2IMSK1      | 0424             | 0000       | I2C1CON2         | 049C              | 0000       |

| SPI2IMSK2      | 0426             | 0000       | I2C1STAT         | 049E              | 0000       |

| SPI2URDTL      | 0428             | 0000       | I2C1ADD          | 04A0              | 0000       |

| SPI2URDTH      | 042A             | 0000       | I2C1MSK          | 04A2              | 0000       |

| SPI3CON1       | 042C             | 0x00       | I2C2RCV          | 04A4              | 0000       |

| SPI3CON2       | 042E             | 0000       | I2C2TRN          | 04A6              | 00FF       |

| SPI3CON3       | 0430             | 0000       | I2C2BRG          | 04A8              | 0000       |

| SPI3STATL      | 0434             | 0028       | I2C2CON1         | 04AA              | 1000       |

| SPI3STATH      | 0436             | 0000       | I2C2CON2         | 04AC              | 0000       |

| SPI3BUFL       | 0438             | 0000       | I2C2STAT         | 04AE              | 0000       |

| SPI3BUFH       | 043A             | 0000       | I2C2ADD          | 04B0              | 0000       |

| SPI3BRGL       | 043C             | xxxx       | I2C2MSK          | 04B2              | 0000       |

| SPI3IMSK1      | 0440             | 0000       | I2C3RCV          | 04B4              | 0000       |

| SPI3IMSK2      | 0442             | 0000       | I2C3TRN          | 04B6              | 00FF       |

| SPI3URDTL      | 0444             | 0000       | I2C3BRG          | 04B8              | 0000       |

| SPI3URDTH      | 0446             | 0000       | I2C3CON1         | 04BA              | 1000       |

| CONFIGURABLE   | LOGIC CELL (CLC) |            | I2C3CON2         | 04BC              | 0000       |

| CLC1CONL       | 0464             | 0000       | I2C3STAT         | 04BE              | 0000       |

| CLC1CONH       | 0466             | 0000       | I2C3ADD          | 04C0              | 0000       |

| CLC1SELL       | 0468             | 0000       | I2C3MSK          | 04C2              | 0000       |

| CLC1GLSL       | 046C             | 0000       | DMA              |                   |            |

| CLC1GLSH       | 046E             | 0000       | DMACON           | 04C4              | 0000       |

| CLC2CONL       | 0470             | 0000       | DMABUF           | 04C6              | 0000       |

| CLC2CONH       | 0472             | 0000       | DMAL             | 04C8              | 0000       |

| CLC2SELL       | 0474             | 0000       | DMAH             | 04CA              | 0000       |

| CLC2GLSL       | 0478             | 0000       | DMACH0           | 04CC              | 0000       |

| CLC2GLSH       | 047A             | 0000       | DMAINT0          | 04CE              | 0000       |

### TABLE 4-8:SFR MAP: 0400h BLOCK

**Legend:** — = unimplemented, read as '0'; x = undefined. Reset values are shown in hexadecimal.

| File Name            | Address | All Resets | File Name         | Address | All Resets |  |

|----------------------|---------|------------|-------------------|---------|------------|--|

| I/O                  |         |            | PORTD (CONTINUED) |         |            |  |

| PADCON               | 065E    | 0000       | ANSD              | 06A6    | FFFF       |  |

| IOCSTAT              | 0660    | 0000       | IOCPD             | 06A8    | 0000       |  |

| PORTA <sup>(1)</sup> | 1 1     |            | IOCND             | 06AA    | 0000       |  |

| TRISA                | 0662    | FFFF       | IOCFD             | 06AC    | 0000       |  |

| PORTA                | 0664    | 0000       | IOCPUD            | 06AE    | 0000       |  |

| LATA                 | 0666    | 0000       | IOCPDD            | 06B0    | 0000       |  |

| ODCA                 | 0668    | 0000       | PORTE             |         | 4          |  |

| ANSA                 | 066A    | FFFF       | TRISE             | 06B2    | FFFF       |  |

| IOCPA                | 066C    | 0000       | PORTE             | 06B4    | 0000       |  |

| IOCNA                | 066E    | 0000       | LATE              | 06B6    | 0000       |  |

| IOCFA                | 0670    | 0000       | ODCE              | 06B8    | 0000       |  |

| IOCPUA               | 0672    | 0000       | ANSE              | 06BA    | FFFF       |  |

| IOCPDA               | 0674    | 0000       | IOCPE             | 06BC    | 0000       |  |

| PORTB                | · ·     |            | IOCNE             | 06BE    | 0000       |  |

| TRISB                | 0676    | FFFF       | IOCFE             | 06C0    | 0000       |  |

| PORTB                | 0678    | 0000       | IOCPUE            | 06C2    | 0000       |  |

| LATB                 | 067A    | 0000       | IOCPDE            | 06C4    | 0000       |  |

| ODCB                 | 067C    | 0000       | PORTF             |         | 1          |  |

| ANSB                 | 067E    | FFFF       | TRISF             | 06C6    | FFFF       |  |

| IOCPB                | 0680    | 0000       | PORTF             | 06C8    | 0000       |  |

| IOCNB                | 0682    | 0000       | LATF              | 06CA    | 0000       |  |

| IOCFB                | 0684    | 0000       | ODCF              | 06CC    | 0000       |  |

| IOCPUB               | 0686    | 0000       | IOCPF             | 06D0    | 0000       |  |

| IOCPDB               | 0688    | 0000       | IOCNF             | 06D2    | 0000       |  |

| PORTC                |         |            | IOCFF             | 06D4    | 0000       |  |

| TRISC                | 068A    | FFFF       | IOCPUF            | 06D6    | 0000       |  |

| PORTC                | 068C    | 0000       | IOCPDF            | 06D8    | 0000       |  |

| LATC                 | 068E    | 0000       | PORTG             |         |            |  |

| ODCC                 | 0690    | 0000       | TRISG             | 06DA    | FFFF       |  |

| ANSC                 | 0692    | FFFF       | PORTG             | 06DC    | 0000       |  |

| IOCPC                | 0694    | 0000       | LATG              | 06DE    | 0000       |  |

| IOCNC                | 0696    | 0000       | ODCG              | 06E0    | 0000       |  |

| IOCFC                | 0698    | 0000       | ANSG              | 06E2    | FFFF       |  |

| IOCPUC               | 069A    | 0000       | IOCPG             | 06E4    | 0000       |  |

| IOCPDC               | 069C    | 0000       | IOCNG             | 06E6    | 0000       |  |

| PORTD                | I       |            | IOCFG             | 06E8    | 0000       |  |

| TRISD                | 069E    | FFFF       | IOCPUG            | 06EA    | 0000       |  |

| PORTD                | 06A0    | 0000       | IOCPDG            | 06EC    | 0000       |  |

| LATD                 | 06A2    | 0000       |                   |         |            |  |

| ODCD                 | 06A4    | 0000       |                   |         |            |  |

## TABLE 4-10:SFR MAP: 0600h BLOCK

$\label{eq:legend: Legend: Legend: Legend: Legend: Legend: Constant of the set of the s$

Note 1: PORTA and all associated bits are unimplemented in 64-pin devices and read as '0'.

| File Name | Address | All Resets | File Name             | Address | All Resets |

|-----------|---------|------------|-----------------------|---------|------------|

| A/D       | ·       | ·          | PERIPHERAL PIN SELECT |         |            |

| ADC1BUF0  | 0712    | xxxx       | RPINR0                | 0790    | 3F3F       |

| ADC1BUF1  | 0714    | xxxx       | RPINR1                | 0792    | 3F3F       |

| ADC1BUF2  | 0716    | xxxx       | RPINR2                | 0794    | 3F3F       |

| ADC1BUF3  | 0718    | xxxx       | RPINR3                | 0796    | 3F3F       |

| ADC1BUF4  | 071A    | xxxx       | RPINR4                | 0798    | 3F3F       |

| ADC1BUF5  | 071C    | xxxx       | RPINR5                | 079A    | 3F3F       |

| ADC1BUF6  | 071E    | xxxx       | RPINR6                | 079C    | 3F3F       |

| ADC1BUF7  | 0720    | xxxx       | RPINR7                | 079E    | 3F3F       |

| ADC1BUF8  | 0722    | xxxx       | RPINR8                | 07A0    | 003F       |

| ADC1BUF9  | 0724    | xxxx       | RPINR11               | 07A6    | 3F3F       |

| ADC1BUF10 | 0726    | xxxx       | RPINR12               | 07A8    | 3F3F       |

| ADC1BUF11 | 0728    | xxxx       | RPINR14               | 07AC    | 3F3F       |

| ADC1BUF12 | 072A    | xxxx       | RPINR15               | 07AE    | 003F       |

| ADC1BUF13 | 072C    | xxxx       | RPINR17               | 07B2    | 3F00       |

| ADC1BUF14 | 072E    | xxxx       | RPINR18               | 07B4    | 3F3F       |

| ADC1BUF15 | 0730    | xxxx       | RPINR19               | 07B6    | 3F3F       |

| ADC1BUF16 | 0732    | xxxx       | RPINR20               | 07B8    | 3F3F       |

| ADC1BUF17 | 0734    | xxxx       | RPINR21               | 07BA    | 3F3F       |

| ADC1BUF18 | 0736    | xxxx       | RPINR22               | 07BC    | 3F3F       |

| ADC1BUF19 | 0738    | xxxx       | RPINR23               | 07BE    | 3F3F       |

| ADC1BUF20 | 073A    | xxxx       | RPINR25               | 07C2    | 3F3F       |

| ADC1BUF21 | 073C    | xxxx       | RPINR27               | 07C6    | 3F3F       |

| ADC1BUF22 | 073E    | xxxx       | RPINR28               | 07C8    | 3F3F       |

| ADC1BUF23 | 0740    | xxxx       | RPINR29               | 07CA    | 003F       |

| ADC1BUF24 | 0742    | xxxx       | RPOR0                 | 07D4    | 0000       |

| ADC1BUF25 | 0744    | xxxx       | RPOR1                 | 07D6    | 0000       |

| AD1CON1   | 0746    | 0000       | RPOR2                 | 07D8    | 0000       |

| AD1CON2   | 0748    | 0000       | RPOR3                 | 07DA    | 0000       |

| AD1CON3   | 074A    | 0000       | RPOR4                 | 07DC    | 0000       |

| AD1CHS    | 074C    | 0000       | RPOR5                 | 07DE    | 0000       |

| AD1CSSH   | 074E    | 0000       | RPOR6                 | 07E0    | 0000       |

| AD1CSSL   | 0750    | 0000       | RPOR7                 | 07E2    | 0000       |

| AD1CON4   | 0752    | 0000       | RPOR8                 | 07E4    | 0000       |

| AD1CON5   | 0754    | 0000       | RPOR9                 | 07E6    | 0000       |

| AD1CHITH  | 0756    | 0000       | RPOR10                | 07E8    | 0000       |

| AD1CHITL  | 0758    | 0000       | RPOR11                | 07EA    | 0000       |

| AD1CTMENH | 075A    | 0000       | RPOR12                | 07EC    | 0000       |

| AD1CTMENL | 075C    | 0000       | RPOR13                | 07EE    | 0000       |

| AD1RESDMA | 075E    | 0000       | RPOR14                | 07F0    | 0000       |

| NVM       |         |            | RPOR15                | 07F2    | 0000       |

| NVMCON    | 0760    | 0000       |                       |         |            |

| NVMADR    | 0762    | xxxx       |                       |         |            |

| NVMADRU   | 0764    | 00xx       |                       |         |            |

| NVMKEY    | 0766    | 0000       |                       |         |            |

TABLE 4-11: SFR MAP: 0700h BLOCK

### EXAMPLE 6-1: ERASING A PROGRAM MEMORY BLOCK ('C' LANGUAGE CODE)

| <pre>// C example using MPLAB XC16     unsigned long progAddr = 0xXXXXXX;     unsigned int offset;</pre> | // Address of row to write               |

|----------------------------------------------------------------------------------------------------------|------------------------------------------|

| //Set up pointer to the first memory location to                                                         | be written                               |

| NVMADRU = progAddr>>16;                                                                                  | // Initialize PM Page Boundary SFR       |

| NVMADR = progAddr & 0xFFFF;                                                                              | // Initialize lower word of address      |

| $NVMCON = 0 \times 4003;$                                                                                | // Initialize NVMCON                     |

| asm("DISI #5");                                                                                          | // Block all interrupts with priority <7 |

|                                                                                                          | // for next 5 instructions               |

| builtin_write_NVM();                                                                                     | // check function to perform unlock      |

|                                                                                                          | // sequence and set WR                   |

### EXAMPLE 6-2: INITIATING A PROGRAMMING SEQUENCE

| DISI  | #5          | ; Block all interrupts with priority <7<br>; for next 5 instructions |

|-------|-------------|----------------------------------------------------------------------|

| MOV.B | #0x55, W0   |                                                                      |

| MOV   | W0, NVMKEY  | ; Write the 0x55 key                                                 |

| MOV.B | #0xAA, W1   | ;                                                                    |

| MOV   | W1, NVMKEY  | ; Write the OxAA key                                                 |

| BSET  | NVMCON, #WR | ; Start the programming sequence                                     |

| NOP   |             | ; Required delays                                                    |

| NOP   |             |                                                                      |

| BTSC  | NVMCON, #15 | ; and wait for it to be                                              |

| BRA   | \$-2        | ; completed                                                          |

# PIC24FJ1024GA610/GB610 FAMILY

### REGISTER 11-20: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-------|-------|-------|-------|-------|-------|

| —      | —   | —     | —     | —     | —     | —     | —     |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| _      |     | IC3R5 | IC3R4 | IC3R3 | IC3R2 | IC3R1 | IC3R0 |

| bit 7  |     | •     |       |       | •     | •     | bit 0 |

|        |     |       |       |       |       |       |       |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 15-6 Unimplemented: Read as '0'

bit 5-0 IC3R<5:0>: Assign Input Capture 3 (IC3) to Corresponding RPn or RPIn Pin bits

### REGISTER 11-21: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0                               | R/W-1  | R/W-1                                                 | R/W-1                                                                                                        | R/W-1                                                                                                                                                         | R/W-1                                                                                                                                                                                              | R/W-1                                                                                                                                                                                                                                     |

|-----------------------------------|--------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| —                                 | OCFBR5 | OCFBR4                                                | OCFBR3                                                                                                       | OCFBR2                                                                                                                                                        | OCFBR1                                                                                                                                                                                             | OCFBR0                                                                                                                                                                                                                                    |

|                                   |        |                                                       |                                                                                                              |                                                                                                                                                               |                                                                                                                                                                                                    | bit 8                                                                                                                                                                                                                                     |

|                                   |        |                                                       |                                                                                                              |                                                                                                                                                               |                                                                                                                                                                                                    |                                                                                                                                                                                                                                           |

| U-0                               | R/W-1  | R/W-1                                                 | R/W-1                                                                                                        | R/W-1                                                                                                                                                         | R/W-1                                                                                                                                                                                              | R/W-1                                                                                                                                                                                                                                     |

| _                                 | OCFAR5 | OCFAR4                                                | OCFAR3                                                                                                       | OCFAR2                                                                                                                                                        | OCFAR1                                                                                                                                                                                             | OCFAR0                                                                                                                                                                                                                                    |

|                                   |        |                                                       |                                                                                                              |                                                                                                                                                               |                                                                                                                                                                                                    | bit 0                                                                                                                                                                                                                                     |

|                                   |        |                                                       |                                                                                                              |                                                                                                                                                               |                                                                                                                                                                                                    |                                                                                                                                                                                                                                           |

|                                   |        |                                                       |                                                                                                              |                                                                                                                                                               |                                                                                                                                                                                                    |                                                                                                                                                                                                                                           |

| R = Readable bit W = Writable bit |        |                                                       | U = Unimplemented bit, read as '0'                                                                           |                                                                                                                                                               |                                                                                                                                                                                                    |                                                                                                                                                                                                                                           |

| -n = Value at POR                 |        | '1' = Bit is set                                      |                                                                                                              | ared                                                                                                                                                          | x = Bit is unknown                                                                                                                                                                                 |                                                                                                                                                                                                                                           |

|                                   |        | U-0 R/W-1<br>— OCFAR5<br>— OCFAR5<br>bit W = Writable | OCFBR5     OCFBR4       U-0     R/W-1     R/W-1       —     OCFAR5     OCFAR4       bit     W = Writable bit | OCFBR5     OCFBR4     OCFBR3       U-0     R/W-1     R/W-1     R/W-1       —     OCFAR5     OCFAR4     OCFAR3       bit     W = Writable bit     U = Unimplem | OCFBR5     OCFBR4     OCFBR3     OCFBR2       U-0     R/W-1     R/W-1     R/W-1       —     OCFAR5     OCFAR4     OCFAR3     OCFAR2       bit     W = Writable bit     U = Unimplemented bit, read | OCFBR5     OCFBR4     OCFBR3     OCFBR2     OCFBR1       U-0     R/W-1     R/W-1     R/W-1     R/W-1       —     OCFAR5     OCFAR4     OCFAR3     OCFAR2     OCFAR1       bit     W = Writable bit     U = Unimplemented bit, read as '0' |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 OCFBR<5:0>: Assign Output Compare Fault B (OCFB) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 OCFAR<5:0>: Assign Output Compare Fault A (OCFA) to Corresponding RPn or RPIn Pin bits

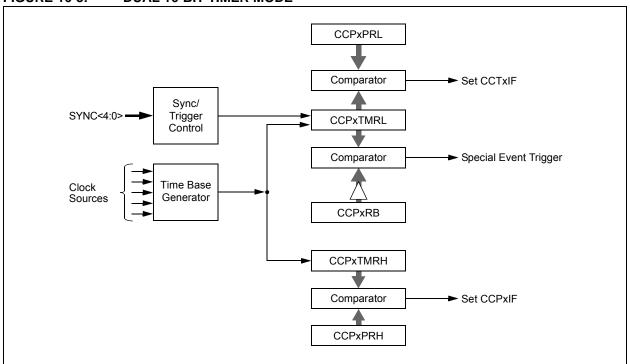

### 16.2 General Purpose Timer

Timer mode is selected when CCSEL = 0 and MOD<3:0> = 0000. The timer can function as a 32-bit timer or a dual 16-bit timer, depending on the setting of the T32 bit (Table 16-1).

| T32<br>(CCPxCON1L<5>) | Operating Mode           |

|-----------------------|--------------------------|

| 0                     | Dual Timer Mode (16-bit) |

| 1                     | Timer Mode (32-bit)      |

TABLE 16-1: TIMER OPERATION MODE

Dual 16-Bit Timer mode provides a simple timer function with two independent 16-bit timer/counters. The primary timer uses the CCPxTMRL and CCPxPRL registers. Only the primary timer can interact with other modules on the device. It generates the MCCPx Sync out signals for use by other MCCPx modules. It can also use the SYNC<4:0> bits signal generated by other modules.

The secondary timer uses the CCPxTMRH and CCPxPRH registers. It is intended to be used only as a periodic interrupt source for scheduling CPU events. It does not generate an output Sync/Trigger signal like the primary time base. In Dual Timer mode, the Secondary Timer Period register, CCPxPRH, generates the MCCPx Compare Event (CCPxIF) used by many other modules on the device.

The 32-Bit Timer mode uses the CCPxTMRL and CCPxTMRH registers, together, as a single 32-bit timer. When CCPxTMRL overflows, CCPxTMRH increments

FIGURE 16-3: DUAL 16-BIT TIMER MODE

by one. This mode provides a simple timer function when it is important to track long time periods. Note that the T32 bit (CCPxCON1L<5>) should be set before the CCPxTMRL or CCPxPRH registers are written to initialize the 32-bit timer.

### 16.2.1 SYNC AND TRIGGER OPERATION

In both 16-bit and 32-bit modes, the timer can also function in either Synchronization ("Sync") or Trigger mode operation. Both use the SYNC<4:0> bits (CCPxCON1H<4:0>) to determine the input signal source. The difference is how that signal affects the timer.

In Sync operation, the Timer Reset or clear occurs when the input selected by SYNC<4:0> is asserted. The timer immediately begins to count again from zero unless it is held for some other reason. Sync operation is used whenever the TRIGEN bit (CCPxCON1H<7>) is cleared. The SYNC<4:0> bits can have any value except '11111'.

In Trigger operation, the timer is held in Reset until the input selected by SYNC<4:0> is asserted; when it occurs, the timer starts counting. Trigger operation is used whenever the TRIGEN bit is set. In Trigger mode, the timer will continue running after a Trigger event as long as the CCPTRIG bit (CCPxSTATL< 7>) is set. To clear CCPTRIG, the TRCLR bit (CCPxSTATL<5>) must be set to clear the Trigger event, reset the timer and hold it at zero until another Trigger event occurs. On PIC24FJ1024GA610/GB610 family devices, Trigger operation can only be used when the system clock is the time base source (CLKSEL<2:0> = 000).

© 2015-2016 Microchip Technology Inc.

# 16.5 Auxiliary Output

The MCCPx and SCCPx modules have an auxiliary (secondary) output that provides other peripherals access to internal module signals. The auxiliary output is intended to connect to other MCCPx or SCCPx modules, or other digital peripherals, to provide these types of functions:

- Time Base Synchronization

- Peripheral Trigger and Clock Inputs

- Signal Gating

The type of output signal is selected using the AUXOUT<1:0> control bits (CCPxCON2H<4:3>). The type of output signal is also dependent on the module operating mode.

On the PIC24FJ1024GA610/GB610 family of devices, only the CTMU discharge Trigger has access to the auxiliary output signal.

| AUXOUT<1:0> | CCSEL | MOD<3:0> | Comments                  | Signal Description                  |

|-------------|-------|----------|---------------------------|-------------------------------------|

| 00          | х     | xxxx     | Auxiliary Output Disabled | No Output                           |

| 01          | 0     | 0000     | Time Base Modes           | Time Base Period Reset or Rollover  |

| 10          |       |          |                           | Special Event Trigger Output        |

| 11          |       |          |                           | No Output                           |

| 01          | 0     | 0001     | Output Compare Modes      | Time Base Period Reset or Rollover  |

| 10          |       | through  |                           | Output Compare Event Signal         |

| 11          |       | 1111     |                           | Output Compare Signal               |

| 01          | 1     | xxxx     | Input Capture Modes       | Time Base Period Reset or Rollover  |

| 10          |       |          |                           | Reflects the Value of the ICDIS bit |

| 11          |       |          |                           | Input Capture Event Signal          |

### TABLE 16-4: AUXILIARY OUTPUT

| R/W-0         | U-0                                                                                                                                     | R/W-0                                                                             | R/W-0          | R/W-0             | R/W-0            | R/W-0            | R/W-0   |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------|-------------------|------------------|------------------|---------|--|--|--|--|

| CCPON         | —                                                                                                                                       | CCPSIDL                                                                           | CCPSLP         | TMRSYNC           | CLKSEL2          | CLKSEL1          | CLKSEL0 |  |  |  |  |

| bit 15        |                                                                                                                                         |                                                                                   |                |                   |                  |                  | bit 8   |  |  |  |  |

|               |                                                                                                                                         |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                   | R/W-0                                                                             | R/W-0          | R/W-0             | R/W-0            | R/W-0            | R/W-0   |  |  |  |  |

| TMRPS1        | TMRPS0                                                                                                                                  | T32                                                                               | CCSEL          | MOD3              | MOD2             | MOD1             | MOD0    |  |  |  |  |

| bit 7         |                                                                                                                                         |                                                                                   |                |                   |                  |                  | bit C   |  |  |  |  |

| Legend:       |                                                                                                                                         |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                   | W = Writable                                                                      | bit            | U = Unimplem      | nented bit, read | d as '0'         |         |  |  |  |  |

| -n = Value at | POR                                                                                                                                     | '1' = Bit is set                                                                  |                | '0' = Bit is clea |                  | x = Bit is unkr  | nown    |  |  |  |  |

|               |                                                                                                                                         |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

| bit 15        | CCPON: CC                                                                                                                               | Px Module Ena                                                                     | ole bit        |                   |                  |                  |         |  |  |  |  |

|               | 1 = Module is                                                                                                                           | s enabled with                                                                    | an operating m | node specified b  | by the MOD<3:    | 0> control bits  |         |  |  |  |  |

|               | 0 = Module is                                                                                                                           |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

| bit 14        | •                                                                                                                                       | ted: Read as '                                                                    |                |                   |                  |                  |         |  |  |  |  |

| bit 13        |                                                                                                                                         | CCPSIDL: CCPx Stop in Idle Mode Bit                                               |                |                   |                  |                  |         |  |  |  |  |

|               | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

| bit 12        |                                                                                                                                         | 0 = Continues module operation in Idle mode<br>CCPSLP: CCPx Sleep Mode Enable bit |                |                   |                  |                  |         |  |  |  |  |

|               | 1 = Module continues to operate in Sleep modes                                                                                          |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | 0 = Module does not operate in Sleep modes                                                                                              |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

| bit 11        | TMRSYNC: Time Base Clock Synchronization bit                                                                                            |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | 1 = Module time base clock is synchronized to the internal system clocks; timing restrictions apply                                     |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | 0 = Module time base clock is not synchronized to the internal system clocks                                                            |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

| bit 10-8      | CLKSEL<2:0>: CCPx Time Base Clock Select bits                                                                                           |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | 111 = TCKIA pin                                                                                                                         |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               |                                                                                                                                         | 110 = TCKIB pin<br>101 = PLL clock                                                |                |                   |                  |                  |         |  |  |  |  |

|               | 100 = 2x peripheral clock                                                                                                               |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | 010 = SOSC clock                                                                                                                        |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | 001 = Reference clock output<br>000 = System clock                                                                                      |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | For MCCP1 and SCCP4:                                                                                                                    |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | 011 = CLC1  output                                                                                                                      |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | For MCCP2 and SCCP5:                                                                                                                    |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | 011 = CLC2 output                                                                                                                       |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | For MCCP3 and SCCP6:<br>011 = CLC3 output                                                                                               |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | For SCCP7:<br>011 = CLC4 output                                                                                                         |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

| bit 7-6       | TMRPS<1:0>: Time Base Prescale Select bits                                                                                              |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               | 11 = 1:64 Prescaler                                                                                                                     |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               |                                                                                                                                         | 10 = 1:16 Prescaler                                                               |                |                   |                  |                  |         |  |  |  |  |

|               | 01 = 1:4 Pres                                                                                                                           |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

|               |                                                                                                                                         |                                                                                   |                |                   |                  |                  |         |  |  |  |  |

| hit 5         | 00 = 1:1 Pres                                                                                                                           |                                                                                   | •t hit         |                   |                  |                  |         |  |  |  |  |

| bit 5         | <b>T32:</b> 32-Bit Ti                                                                                                                   | ime Base Selec                                                                    |                | edge output co    | mpare or input   | canture function | n an    |  |  |  |  |

## REGISTER 16-1: CCPxCON1L: CCPx CONTROL 1 LOW REGISTERS

| REGISTER '    | 16-6: CCPx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CON3H: CCI                                           | Px CONTRO                       | 3 HIGH RE                         | GISTERS              |                        |                            |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-----------------------------------|----------------------|------------------------|----------------------------|

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                | R/W-0                           | U-0                               | R/W-0                | R/W-0                  | R/W-0                      |

| OETRIG        | OSCNT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OSCNT1                                               | OSCNT0                          |                                   | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup>   | OUTM0 <sup>(1)</sup>       |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      |                                 |                                   |                      |                        | bit 8                      |

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                | R/W-0                           | R/W-0                             | R/W-0                | R/W-0                  | R/W-0                      |

| _             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | POLACE                                               | POLBDF <sup>(1)</sup>           | PSSACE1                           | PSSACE0              | PSSBDF1 <sup>(1)</sup> | PSSBDF0 <sup>(1</sup>      |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      |                                 |                                   |                      |                        | bit                        |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      |                                 |                                   |                      |                        |                            |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | W = Writable                                         | bit                             | U = Unimplen                      | nented bit, read     | d as '0'               |                            |

| -n = Value at |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                     |                                 | '0' = Bit is clea                 |                      | x = Bit is unkr        | iown                       |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      |                                 |                                   |                      |                        |                            |

| bit 15        | 1 = For Trigg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | IGEN = 1): Mo                   | odule does not                    | drive enabled o      | output pins unti       | l triggered                |

| bit 14-12     | <ul> <li>0 = Normal output pin operation</li> <li>OSCNT&lt;2:0&gt;: One-Shot Event Count bits</li> <li>111 = Extends one-shot event by 7 time base periods (8 time base periods total)</li> <li>100 = Extends one-shot event by 6 time base periods (7 time base periods total)</li> <li>101 = Extends one-shot event by 5 time base periods (6 time base periods total)</li> <li>100 = Extends one-shot event by 4 time base periods (5 time base periods total)</li> <li>101 = Extends one-shot event by 3 time base periods (4 time base periods total)</li> <li>101 = Extends one-shot event by 2 time base periods (3 time base periods total)</li> <li>101 = Extends one-shot event by 1 time base periods (2 time base periods total)</li> <li>001 = Does not extend one-shot Trigger event</li> </ul> |                                                      |                                 |                                   |                      |                        |                            |

| bit 11        | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      |                                 |                                   |                      |                        |                            |

| bit 10-8      | OUTM<2:0>: PWMx Output Mode Control bits <sup>(1)</sup><br>111 = Reserved<br>110 = Output Scan mode<br>101 = Brush DC Output mode, forward<br>100 = Brush DC Output mode, reverse<br>011 = Reserved<br>010 = Half-Bridge Output mode<br>001 = Push-Pull Output mode<br>000 = Steerable Single Output mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                      |                                 |                                   |                      |                        |                            |

| bit 7-6       | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ted: Read as 'o                                      | )'                              |                                   |                      |                        |                            |

| bit 5         | Unimplemented: Read as '0'<br>POLACE: CCPx Output Pins, OCMxA, OCMxC and OCMxE, Polarity Control bit<br>1 = Output pin polarity is active-low<br>0 = Output pin polarity is active-high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      |                                 |                                   |                      |                        |                            |

| bit 4         | <b>POLBDF:</b> CCPx Output Pins, OCMxB, OCMxD and OCMxF, Polarity Control bit <sup>(1)</sup><br>1 = Output pin polarity is active-low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      |                                 |                                   |                      |                        |                            |

| bit 3-2       | <ul> <li>0 = Output pin polarity is active-high</li> <li>PSSACE&lt;1:0&gt;: PWMx Output Pins, OCMxA, OCMxC and OCMxE, Shutdown State Control bits</li> <li>11 = Pins are driven active when a shutdown event occurs</li> <li>10 = Pins are driven inactive when a shutdown event occurs</li> <li>0x = Pins are tri-stated when a shutdown event occurs</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |                                 |                                   |                      |                        |                            |

| bit 1-0       | PSSBDF<1:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | >: PWMx Outp                                         | ut Pins, OCMx                   | B, OCMxD, an                      | d OCMxF. Shu         | itdown State Co        | ontrol bits <sup>(1)</sup> |

|               | 11 = Pins are<br>10 = Pins are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | driven active v<br>driven inactive<br>in a high-impe | /hen a shutdov<br>when a shutdo | vn event occurs<br>own event occu | s<br>urs             |                        |                            |

## REGISTER 16-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

**Note 1:** These bits are implemented in MCCPx modules only.

# PIC24FJ1024GA610/GB610 FAMILY

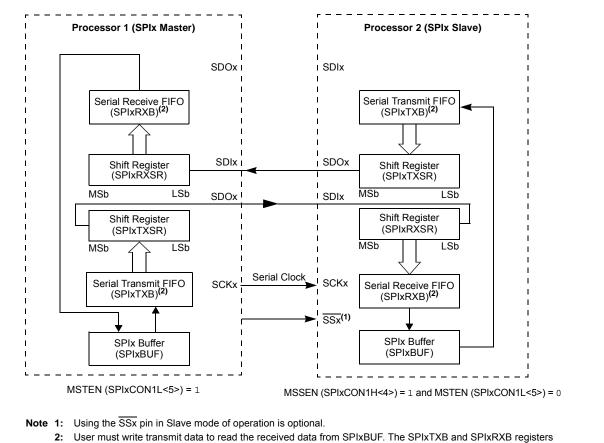

are memory-mapped to SPIxBUF.

# PIC24FJ1024GA610/GB610 FAMILY

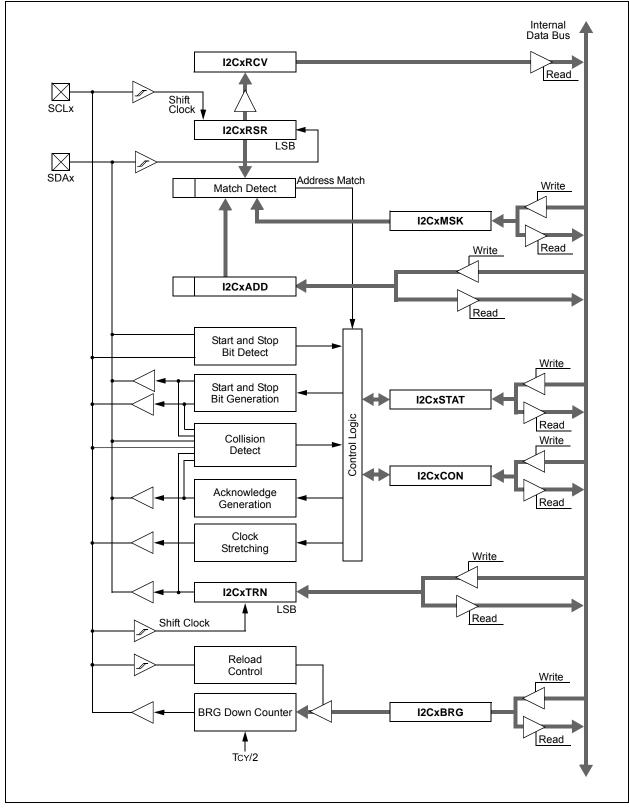

## FIGURE 18-1: I2Cx BLOCK DIAGRAM

| U-0          | U-0                                                                                                                                                                                                | U-0                                                                                                                     | U-0                         | U-0                                                                     | U-0             | U-0             | U-0         |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------|-----------------|-----------------|-------------|--|--|--|--|--|

| _            | _                                                                                                                                                                                                  |                                                                                                                         |                             | —                                                                       | _               | _               | _           |  |  |  |  |  |

| bit 15       |                                                                                                                                                                                                    | ·                                                                                                                       |                             |                                                                         |                 |                 | bita        |  |  |  |  |  |

| U-0          | R/W-0                                                                                                                                                                                              | R/W-0                                                                                                                   | R/W-0                       | R/W-0                                                                   | R/W-0           | R/W-0           | R/W-0       |  |  |  |  |  |

| _            | PCIE                                                                                                                                                                                               | SCIE                                                                                                                    | BOEN                        | SDAHT <sup>(1)</sup>                                                    | SBCDE           | AHEN            | DHEN        |  |  |  |  |  |

| bit 7        |                                                                                                                                                                                                    |                                                                                                                         |                             |                                                                         |                 |                 | bit         |  |  |  |  |  |