Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

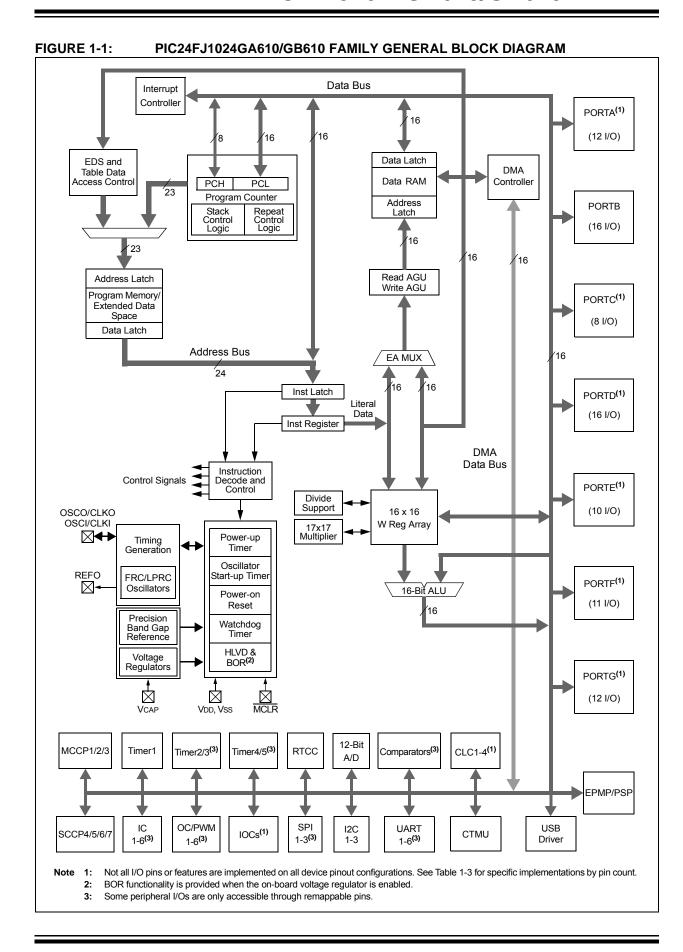

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                 |

|--------------------------|---------------------------------------------------------------------------------|

|                          |                                                                                 |

| oduct Status             | Active                                                                          |

| ore Processor            | PIC                                                                             |

| ore Size                 | 16-Bit                                                                          |

| peed                     | 32MHz                                                                           |

| onnectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| eripherals               | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| umber of I/O             | 53                                                                              |

| ogram Memory Size        | 128KB (43K x 24)                                                                |

| ogram Memory Type        | FLASH                                                                           |

| EPROM Size               | -                                                                               |

| AM Size                  | 32K x 8                                                                         |

| ltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| ta Converters            | A/D 16x10b                                                                      |

| cillator Type            | Internal                                                                        |

| perating Temperature     | -40°C ~ 85°C (TA)                                                               |

| ounting Type             | Surface Mount                                                                   |

| ckage / Case             | 64-TQFP                                                                         |

| ipplier Device Package   | 64-TQFP (10x10)                                                                 |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga606t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 7: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJXXXGB610 BGA) (CONTINUED)

| Pin | Full Pin Name                                 | Pin | Full Pin Name                         |

|-----|-----------------------------------------------|-----|---------------------------------------|

| J1  | AN3/C2INA/RB3                                 | K7  | AN14/RP14/CTED5/CTPLS/PMA1/PMALH/RB14 |

| J2  | AN2/CTCMP/C2INB/RP13/CTED13/RB2               | K8  | VDD                                   |

| J3  | PGED2/AN7/ <b>RP7</b> /U6TX/RB7               | K9  | <b>RP5</b> /RD15                      |

| J4  | AVDD                                          | K10 | RP16/USBID/RF3                        |

| J5  | AN11/REFI/PMA12/RB11                          | K11 | RP30/RF2                              |

| J6  | TCK/RA1                                       | L1  | PGEC2/AN6/ <b>RP6</b> /RB6            |

| J7  | AN12/U6RX/CTED2/PMA11/RB12                    | L2  | CVREF-/VREF-/PMA7/RA9                 |

| J8  | N/C                                           | L3  | AVss                                  |

| J9  | N/C                                           | L4  | AN9/TMPR/RP9/T1CK/RB9                 |

| J10 | <b>RP15</b> /RF8                              | L5  | CVREF/AN10/PMA13/RB10                 |

| J11 | D-/RG3                                        | L6  | <b>RP31</b> /RF13                     |

| K1  | PGEC1/ALTCVREF-/ALTVREF-/AN1/RP1/CTED12/RB1   | L7  | AN13/CTED1/PMA10/RB13                 |

| K2  | PGED1/ALTCVREF+/ALTVREF+/AN0/ <b>RP0</b> /RB0 | L8  | AN15/RP29/CTED6/PMA0/PMALL/RB15       |

| K3  | CVREF+/VREF+/PMA6/RA10                        | L9  | RPI43/RD14                            |

| K4  | AN8/ <b>RP8</b> /PWRGT/RB8                    | L10 | RP10/PMA9/RF4                         |

| K5  | N/C                                           | L11 | RP17/PMA8/RF5                         |

| K6  | RPI32/CTED7/PMA18/RF12                        |     |                                       |

**Legend:** RPn and RPln represent remappable pins for Peripheral Pin Select (PPS) functions.

Note: Pinouts are subject to change.I

© 2015-2016 Microchip Technology Inc.

TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                 |                                                          |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|----------------------------------------------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | 1/0 | Input<br>Buffer | Description                                              |

| PMD0            | 60                                  | 60                               | 93                               | 93                               | A4                      | A4                      | I/O | DIG/<br>ST/TTL  | Parallel Master Port Data (Demultiplexed Master mode) or |

| PMD1            | 61                                  | 61                               | 94                               | 94                               | B4                      | B4                      | I/O | DIG/<br>ST/TTL  | Address/Data (Multiplexed Master modes)                  |

| PMD2            | 62                                  | 62                               | 98                               | 98                               | В3                      | В3                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD3            | 63                                  | 63                               | 99                               | 99                               | A2                      | A2                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD4            | 64                                  | 64                               | 100                              | 100                              | A1                      | A1                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD5            | 1                                   | 1                                | 3                                | 3                                | D3                      | D3                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD6            | 2                                   | 2                                | 4                                | 4                                | C1                      | C1                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD7            | 3                                   | 3                                | 5                                | 5                                | D2                      | D2                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD8            | _                                   | _                                | 90                               | 90                               | A5                      | A5                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD9            | _                                   | _                                | 89                               | 89                               | E6                      | E6                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD10           | _                                   | _                                | 88                               | 88                               | A6                      | A6                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD11           | _                                   | _                                | 87                               | 87                               | В6                      | В6                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD12           | _                                   | _                                | 79                               | 79                               | A9                      | A9                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD13           | _                                   | _                                | 80                               | 80                               | D8                      | D8                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD14           | _                                   | _                                | 83                               | 83                               | D7                      | D7                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMD15           | _                                   | _                                | 84                               | 84                               | C7                      | C7                      | I/O | DIG/<br>ST/TTL  |                                                          |

| PMRD/<br>PMWR   | 53                                  | 53                               | 82                               | 82                               | B8                      | B8                      | I/O | DIG/<br>ST/TTL  | Parallel Master Port Read<br>Strobe/Write Strobe         |

| PMWR/<br>PMENB  | 52                                  | 52                               | 81                               | 81                               | C8                      | C8                      | I/O | DIG/<br>ST/TTL  | Parallel Master Port Write<br>Strobe/Enable Strobe       |

| PWRGT           | 21                                  | 21                               | 32                               | 32                               | K4                      | K4                      | 0   | DIG             | Real-Time Clock Power Control<br>Output                  |

| PWRLCLK         | 48                                  | 48                               | 74                               | 74                               | B11                     | B11                     | I   | ST              | Real-Time Clock 50/60 Hz Clock<br>Input                  |

**Legend:** TTL = TTL input buffer

ANA = Analog level input/output

DIG = Digital input/output

ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated Transceiver

TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                 |                    |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|--------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | 1/0 | Input<br>Buffer | Description        |

| RA0             | _                                   | _                                | 17                               | 17                               | G3                      | G3                      | I/O | DIG/ST          | PORTA Digital I/Os |

| RA1             | _                                   | _                                | 38                               | 38                               | J6                      | J6                      | I/O | DIG/ST          |                    |

| RA2             | _                                   | _                                | 58                               | 58                               | H11                     | H11                     | I/O | DIG/ST          |                    |

| RA3             | _                                   | _                                | 59                               | 59                               | G10                     | G10                     | I/O | DIG/ST          |                    |

| RA4             | _                                   | _                                | 60                               | 60                               | G11                     | G11                     | I/O | DIG/ST          |                    |

| RA5             | _                                   | _                                | 61                               | 61                               | G9                      | G9                      | I/O | DIG/ST          |                    |

| RA6             | _                                   | _                                | 91                               | 91                               | C5                      | C5                      | I/O | DIG/ST          |                    |

| RA7             | _                                   | _                                | 92                               | 92                               | B5                      | B5                      | I/O | DIG/ST          |                    |

| RA9             | _                                   | _                                | 28                               | 28                               | L2                      | L2                      | I/O | DIG/ST          |                    |

| RA10            | _                                   | _                                | 29                               | 29                               | K3                      | K3                      | I/O | DIG/ST          |                    |

| RA14            | _                                   | _                                | 66                               | 66                               | E11                     | E11                     | I/O | DIG/ST          |                    |

| RA15            | _                                   | _                                | 67                               | 67                               | E8                      | E8                      | I/O | DIG/ST          |                    |

| RB0             | 16                                  | 16                               | 25                               | 25                               | K2                      | K2                      | I/O | DIG/ST          | PORTB Digital I/Os |

| RB1             | 15                                  | 15                               | 24                               | 24                               | K1                      | K1                      | I/O | DIG/ST          |                    |

| RB2             | 14                                  | 14                               | 23                               | 23                               | J2                      | J2                      | I/O | DIG/ST          |                    |

| RB3             | 13                                  | 13                               | 22                               | 22                               | J1                      | J1                      | I/O | DIG/ST          |                    |

| RB4             | 12                                  | 12                               | 21                               | 21                               | H2                      | H2                      | I/O | DIG/ST          |                    |

| RB5             | 11                                  | 11                               | 20                               | 20                               | H1                      | H1                      | I/O | DIG/ST          |                    |

| RB6             | 17                                  | 17                               | 26                               | 26                               | L1                      | L1                      | I/O | DIG/ST          |                    |

| RB7             | 18                                  | 18                               | 27                               | 27                               | J3                      | J3                      | I/O | DIG/ST          |                    |

| RB8             | 21                                  | 21                               | 32                               | 32                               | K4                      | K4                      | I/O | DIG/ST          |                    |

| RB9             | 22                                  | 22                               | 33                               | 33                               | L4                      | L4                      | I/O | DIG/ST          |                    |

| RB10            | 23                                  | 23                               | 34                               | 34                               | L5                      | L5                      | I/O | DIG/ST          |                    |

| RB11            | 24                                  | 24                               | 35                               | 35                               | J5                      | J5                      | I/O | DIG/ST          |                    |

| RB12            | 27                                  | 27                               | 41                               | 41                               | J7                      | J7                      | I/O | DIG/ST          |                    |

| RB13            | 28                                  | 28                               | 42                               | 42                               | L7                      | L7                      | I/O | DIG/ST          |                    |

| RB14            | 29                                  | 29                               | 43                               | 43                               | K7                      | K7                      | I/O | DIG/ST          |                    |

| RB15            | 30                                  | 30                               | 44                               | 44                               | L8                      | L8                      | I/O | DIG/ST          |                    |

| RC1             | _                                   | _                                | 6                                | 6                                | D1                      | D1                      | I/O | DIG/ST          | PORTC Digital I/Os |

| RC2             |                                     |                                  | 7                                | 7                                | E4                      | E4                      | I/O | DIG/ST          |                    |

| RC3             |                                     |                                  | 8                                | 8                                | E2                      | E2                      | I/O | DIG/ST          |                    |

| RC4             |                                     | _                                | 9                                | 9                                | E1                      | E1                      | I/O | DIG/ST          |                    |

| RC12            | 39                                  | 39                               | 63                               | 63                               | F9                      | F9                      | I/O | DIG/ST          |                    |

| RC13            | 47                                  | 47                               | 73                               | 73                               | C10                     | C10                     | I/O | DIG/ST          |                    |

| RC14            | 48                                  | 48                               | 74                               | 74                               | B11                     | B11                     | I/O | DIG/ST          |                    |

| RC15            | 40                                  | 40                               | 64                               | 64                               | F11                     | F11                     | I/O | DIG/ST          |                    |

**Legend:** TTL = TTL input buffer

ANA = Analog level input/output DIG = Digital input/output

ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated Transceiver

#### REGISTER 3-2: CORCON: CPU CORE CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/C-0               | R/W-1              | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|--------------------|-----|-------|

| _     | _   | _   | _   | IPL3 <sup>(1)</sup> | PSV <sup>(2)</sup> | _   | _     |

| bit 7 |     |     |     |                     |                    |     | bit 0 |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-4 **Unimplemented:** Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup>

1 = CPU Interrupt Priority Level is greater than 7

0 = CPU Interrupt Priority Level is 7 or less

1 = Program space is visible in Data Space0 = Program space is not visible in Data Space

bit 1-0 **Unimplemented:** Read as '0'

**Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level; see Register 3-1 for bit description.

2: If PSV = 0, any reads from data memory at 0x8000 and above will cause an address trap error instead of reading from the PSV section of program memory. This bit is not individually addressable.

## 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC® MCUs and improve Data Space memory usage efficiency, the PIC24F instruction set supports both word and byte operations. As a consequence of byte accessibility, all EA calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode, [Ws++], will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word, which contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The Most Significant Byte (MSB) is not modified.

A Sign-Extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions operate only on words.

#### 4.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. The remainder of the Data Space is addressable indirectly. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing with a 16-bit address field.

# 4.2.4 SPECIAL FUNCTION REGISTER (SFR) SPACE

The first 2 Kbytes of the Near Data Space, from 0000h to 07FFh, are primarily occupied with Special Function Registers (SFRs). These are used by the PIC24F core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A diagram of the SFR space, showing where the SFRs are actually implemented, is shown in Table 4-3. Each implemented area indicates a 32-byte region where at least one address is implemented as an SFR. A complete list of implemented SFRs, including their addresses, is shown in Tables 4-3 through 4-11.

SFR Space Address xx10 xxA0 xx00 xx20 xx30 xx40 xx50 xx70 xx80 xxB0 xxC0 xxD0 xxE0 xx60 xx90 xxF0 000h Core OSC Reset<sup>(1)</sup> 100h **EPMP** CRC **REFO PMD** Timers CTM RTCC 200h Capture Compare MCCP Comp ANCFG 300h SCCP **UART** SPI I<sup>2</sup>C 400h SPI CLC DMA 500h \_ USB DMA 600h I/O 700h A/D PPS

TABLE 4-3: IMPLEMENTED REGIONS OF SFR DATA SPACE

**Legend:** — = No implemented SFRs in this block

Note 1: Includes HLVD control.

#### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-1  | R-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|--------|------|--------|-----|-----|-----|-----|--------|

| GIE    | DISI | SWTRAP | _   | -   | _   | _   | AIVTEN |

| bit 15 | •    |        | •   |     |     |     | bit 8  |

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| _     | _   | _   | INT4EP | INT3EP | INT2EP | INT1EP | INT0EP |

| bit 7 |     |     |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 GIE: Global Interrupt Enable bit

1 = Interrupts and associated interrupt enable bits are enabled

0 = Interrupts are disabled, but traps are still enabled

bit 14 DISI: DISI Instruction Status bit

1 = DISI instruction is active 0 = DISI instruction is not active

bit 13 SWTRAP: Software Trap Status bit

1 = Software trap is enabled0 = Software trap is disabled

bit 12-9 Unimplemented: Read as '0'

bit 8 AIVTEN: Alternate Interrupt Vector Table Enable bit

1 = Use Alternate Interrupt Vector Table (if enabled in Configuration bits)

0 = Use standard Interrupt Vector Table (default)

bit 7-5 **Unimplemented:** Read as '0'

bit 4 INT4EP: External Interrupt 4 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 3 INT3EP: External Interrupt 3 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 2 INT2EP: External Interrupt 2 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 1 INT1EP: External Interrupt 1 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 0 INT0EP: External Interrupt 0 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE REGISTER 1

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0   |

|--------|-------|-------|-------|-------|-----|-----|-------|

| T5MD   | T4MD  | T3MD  | T2MD  | T1MD  | _   | _   | _     |

| bit 15 |       |       |       |       |     |     | bit 8 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0  | U-0 | U-0 | R/W-0  |

|--------|-------|-------|--------|--------|-----|-----|--------|

| I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _   | _   | ADC1MD |

| bit 7  |       |       |        |        |     |     | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 T5MD: Timer5 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 14 T4MD: Timer4 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 13 **T3MD:** Timer3 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 12 T2MD: Timer2 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 11 T1MD: Timer1 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 10-8 **Unimplemented:** Read as '0'

bit 7 I2C1MD: I2C1 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 6 **U2MD:** UART2 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 5 U1MD: UART1 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 4 SPI2MD: SPI2 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 3 SPI1MD: SPI1 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 2-1 Unimplemented: Read as '0'

bit 0 ADC1MD: A/D Converter Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

#### REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0 |

|--------|-----|-----|-----|-----|-------|--------|-------|

| _      | _   | _   | _   | _   | CMPMD | RTCCMD | PMPMD |

| bit 15 |     |     |     |     |       |        | bit 8 |

| R/W-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0  | R/W-0  | U-0   |

|-------|-----|-----|-----|-------|--------|--------|-------|

| CRCMD | _   | _   | _   | U3MD  | I2C3MD | I2C2MD | _     |

| bit 7 |     |     |     |       |        |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10 CMPMD: Triple Comparator Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 9 RTCCMD: RTCC Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 8 PMPMD: Enhanced Parallel Master Port Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 7 CRCMD: CRC Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 6-4 **Unimplemented:** Read as '0'

bit 3 **U3MD:** UART3 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 2 I2C3MD: I2C3 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 1 I2C2MD: I2C2 Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 0 **Unimplemented:** Read as '0'

#### 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. In an application that needs to use more than one peripheral multiplexed on a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of any one of many digital peripherals to any one of these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The PPS feature is used with a range of up to 44 pins, depending on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

PIC24FJ1024GA610/GB610 family devices support a larger number of remappable input/output pins than remappable input only pins. In this device family, there are up to 44 remappable input/output pins, depending on the pin count of the particular device selected. These pins are numbered, RP0 through RP31, and RPI32 through RPI43.

See Table 1-1 for a summary of pinout options in each package offering.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals.

PPS is not available for these peripherals:

- I<sup>2</sup>C (input and output)

- · Input Change Notifications

- EPMP Signals (input and output)

- Analog (inputs and outputs)

- INT0

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

# 11.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g., output compare, UART transmit) will take priority over general purpose digital functions on a pin, such as EPMP and port I/O. Specialized digital outputs will take priority over PPS outputs on the same pin. The pin diagrams list peripheral outputs in the order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pinselectable peripheral inputs will never take ownership of a pin. The pin's output buffer will be controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in Digital mode, then the PPS input will operate correctly. If an analog function is enabled on the pin, the PPS input will be disabled.

# 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

#### 11.4.3.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral; that is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-12 through Register 11-35).

Each register contains one or two sets of 6-bit fields, with each set associated with one of the pin-selectable peripherals. Programming a given peripheral's bit field with an appropriate 6-bit value maps the RPn/RPln pin with that value to that peripheral. For any given device, the valid range of values for any of the bit fields corresponds to the maximum number of Peripheral Pin Selections supported by the device.

TABLE 11-3: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)<sup>(1)</sup>

| Input Name                   | Function Name | Register      | Function Mapping<br>Bits |

|------------------------------|---------------|---------------|--------------------------|

| Output Compare Trigger 1     | OCTRIG1       | RPINR0<5:0>   | OCTRIG1R<5:0>            |

| External Interrupt 1         | INT1          | RPINR0<13:8>  | INT1R<5:0>               |

| External Interrupt 2         | INT2          | RPINR1<5:0>   | INT2R<5:0>               |

| External Interrupt 3         | INT3          | RPINR1<13:8>  | INT3R<5:0>               |

| External Interrupt 4         | INT4          | RPINR2<5:0>   | INT4R<5:0>               |

| Output Compare Trigger 2     | OCTRIG2       | RPINR2<13:8>  | OCTRIG2R<5:0>            |

| Timer2 External Clock        | T2CK          | RPINR3<5:0>   | T2CKR<5:0>               |

| Timer3 External Clock        | T3CK          | RPINR3<13:8>  | T3CKR<5:0>               |

| Timer4 External Clock        | T4CK          | RPINR4<5:0>   | T4CKR<5:0>               |

| Timer5 External Clock        | T5CK          | RPINR4<13:8>  | T5CKR<5:0>               |

| Input Capture 1              | IC1           | RPINR7<5:0>   | IC1R<5:0>                |

| Input Capture 2              | IC2           | RPINR7<13:8>  | IC2R<5:0>                |

| Input Capture 3              | IC3           | RPINR8<5:0>   | IC3R<5:0>                |

| Output Compare Fault A       | OCFA          | RPINR11<5:0>  | OCFAR<5:0>               |

| Output Compare Fault B       | OCFB          | RPINR11<13:8> | OCFBR<5:0>               |

| CCP Clock Input A            | TCKIA         | RPINR12<5:0>  | TCKIAR<5:0>              |

| CCP Clock Input B            | TCKIB         | RPINR12<13:8> | TCKIBR<5:0>              |

| UART3 Receive                | U3RX          | RPINR17<13:8> | U3RXR<5:0>               |

| UART1 Receive                | U1RX          | RPINR18<5:0>  | U1RXR<5:0>               |

| UART1 Clear-to-Send          | U1CTS         | RPINR18<13:8> | U1CTSR<5:0>              |

| UART2 Receive                | U2RX          | RPINR19<5:0>  | U2RXR<5:0>               |

| UART2 Clear-to-Send          | U2CTS         | RPINR19<13:8> | U2CTSR<5:0>              |

| SPI1 Data Input              | SDI1          | RPINR20<5:0>  | SDI1R<5:0>               |

| SPI1 Clock Input             | SCK1IN        | RPINR20<13:8> | SCK1R<5:0>               |

| SPI1 Slave Select Input      | SS1IN         | RPINR21<5:0>  | SS1R<5:0>                |

| UART3 Clear-to-Send          | U3CTS         | RPINR21<13:8> | U3CTSR<5:0>              |

| SPI2 Data Input              | SDI2          | RPINR22<5:0>  | SDI2R<5:0>               |

| SPI2 Clock Input             | SCK2IN        | RPINR22<13:8> | SCK2R<5:0>               |

| SPI2 Slave Select Input      | SS2IN         | RPINR23<5:0>  | SS2R<5:0>                |

| Generic Timer External Clock | TxCK          | RPINR23<13:8> | TXCKR<5:0>               |

| CLC Input A                  | CLCINA        | RPINR25<5:0>  | CLCINAR<5:0>             |

| CLC Input B                  | CLCINB        | RPINR25<13:8> | CLCINBR<5:0>             |

| UART4 Receive                | U4RX          | RPINR27<5:0>  | U4RXR<5:0>               |

| UART4 Clear-to-Send          | U4CTS         | RPINR27<13:8> | U4CTSR<5:0>              |

| SPI3 Data Input              | SDI3          | RPINR28<5:0>  | SDI3R<5:0>               |

| SPI3 Clock Input             | SCK3IN        | RPINR28<13:8> | SCK3R<5:0>               |

| SPI3 Slave Select Input      | SS3IN         | RPINR29<5:0>  | SS3R<5:0>                |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger (ST) input buffers.

#### REGISTER 15-2: OCXCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

```

bit 4-0

SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits

11111 = OCx Sync out<sup>(1)</sup>

11110 = OCTRIG1 pin

11101 = OCTRIG2 pin

11100 = CTMU Trigger<sup>(2)</sup>

11011 = A/D interrupt<sup>(2)</sup>

11010 = CMP3 Trigger<sup>(2)</sup>

11001 = CMP2 Trigger^{(2)}

11000 = CMP1 Trigger^{(2)}

10111 = SCCP5 IC/OC interrupt

10110 = SCCP4 IC/OC interrupt

10101 = MCCP3 IC/OC interrupt

10100 = MCCP2 IC/OC interrupt

10011 = MCCP1 IC/OC interrupt

10010 = IC3 interrupt^{(2)}

10001 = IC2 interrupt<sup>(2)</sup>

10000 = IC1 interrupt<sup>(2)</sup>

01111 = SCCP7 IC/OC interrupt

01110 = SCCP6 IC/OC interrupt

01101 = Timer3 match event

01100 = Timer2 match event (default)

01011 = Timer1 match event

01010 = SCCP7 Sync/Trigger out

01001 = SCCP6 Sync/Trigger out

01000 = SCCP5 Sync/Trigger out

00111 = SCCP4 Sync/Trigger out

00110 = MCCP3 Sync/Trigger out

00101 = MCCP2 Sync/Trigger out

00100 = MCCP1 Sync/Trigger out

00011 = OC5 Sync/Trigger out<sup>(1)</sup>

00010 = OC3 Sync/Trigger out<sup>(1)</sup>

00001 = OC1 Sync/Trigger out<sup>(1)</sup>

00000 = Off, Free-Running mode with no synchronization and rollover at FFFFh

```

- **Note 1:** Never use an Output Compare x module as its own Trigger source, either by selecting this mode or another equivalent SYNCSELx setting.

- 2: Use these inputs as Trigger sources only and never as Sync sources.

- 3: The DCB<1:0> bits are double-buffered in the PWM modes only (OCM<2:0> (OCxCON1<2:0>) = 111, 110).

| NOTES: |  |  |  |  |

|--------|--|--|--|--|

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

|        |  |  |  |  |

# 21.0 ENHANCED PARALLEL MASTER PORT (EPMP)

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Enhanced Parallel Master Port (EPMP)" (DS39730), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Enhanced Parallel Master Port (EPMP) module provides a parallel, 4-bit (Master mode only), 8-bit (Master and Slave modes) or 16-bit (Master mode only) data bus interface to communicate with off-chip modules, such as memories, FIFOs, LCD controllers and other microcontrollers. This module can serve as either the master or the slave on the communication bus.

For EPMP Master modes, all external addresses are mapped into the internal Extended Data Space (EDS). This is done by allocating a region of the EDS for each Chip Select, and then assigning each Chip Select to a particular external resource, such as a memory or external controller. This region should not be assigned to another device resource, such as RAM or SFRs. To perform a write or read on an external resource, the CPU simply performs a write or read within the address range assigned for the EPMP.

Key features of the EPMP module are:

- Extended Data Space (EDS) Interface Allows Direct Access from the CPU

- Up to 23 Programmable Address Lines

- · Up to 2 Chip Select lines

- Up to 2 Acknowledgment Lines (one per Chip Select)

- · 4-Bit, 8-Bit or 16-Bit Wide Data Bus

- Programmable Strobe Options (per Chip Select):

- Individual read and write strobes or:

- Read/Write strobe with enable strobe

- Programmable Address/Data Multiplexing

- · Programmable Address Wait States

- Programmable Data Wait States (per Chip Select)

- Programmable Polarity on Control Signals (per Chip Select)

- · Legacy Parallel Slave Port Support

- · Enhanced Parallel Slave Support:

- Address support

- 4-byte deep auto-incrementing buffer

### 21.1 Specific Package Variations

While all PIC24FJ1024GA610/GB610 family devices implement the EPMP, I/O pin constraints place some limits on 16-Bit Master mode operations in some package types. This is reflected in the number of dedicated Chip Select pins implemented and the number of dedicated address lines that are available. The differences are summarized in Table 21-1. All available EPMP pin functions are summarized in Table 21-2.

For 64-pin devices, the dedicated Chip Select pins (PMCS1 and PMCS2) are not implemented. In addition, only 16 address lines (PMA<15:0>) are available. If required, PMA14 and PMA15 can be remapped to function as PMCS1 and PMCS2, respectively.

The memory space addressable by the device depends on the number of address lines available, as well as the number of Chip Select signals required for the application. Devices with lower pin counts are more affected by Chip Select requirements, as these take away address lines. Table 21-1 shows the maximum addressable range for each pin count.

#### 21.2 PMDOUT1 and PMDOUT2 Registers

The EPMP Data Output 1 and Data Output 2 registers are used only in Slave mode for buffered output data. These registers act as a buffer for outgoing data.

#### 21.3 PMDIN1 and PMDIN2 Registers

The EPMP Data Input 1 and Data Input 2 registers are used in Slave modes to buffer incoming data. These registers hold data that is asynchronously clocked in.

In Master mode, PMDIN1 is the holding register for incoming data.

| TARI F 21-1. | FPMP FFATURE | DIFFERENCES BY | DEVICE PIN COUNT |

|--------------|--------------|----------------|------------------|

|              |              |                |                  |

| Device                            | Dedicated Chip<br>Select |     | Address | Data<br>Lines | Address Range (bytes) |                     |                     |

|-----------------------------------|--------------------------|-----|---------|---------------|-----------------------|---------------------|---------------------|

|                                   | CS1                      | CS2 | Lines   | Lilles        | No CS                 | 1 CS <sup>(1)</sup> | 2 CS <sup>(1)</sup> |

| PIC24FJXXXGX606 (64-Pin)          | _                        | _   | 16      | 8             | 64K                   | 32K                 | 16K                 |

| PIC24FJXXXGX610 (100-Pin/121-Pin) | Х                        | Х   | 23      | 16            |                       | 16M                 |                     |

**Note 1:** PMA14 and PMA15 can be remapped to be dedicated Chip Selects.

#### REGISTER 21-8: PMSTAT: EPMP STATUS REGISTER (SLAVE MODE ONLY)

| R-0, HSC | R/W-0, HS | U-0 | U-0 | R-0, HSC            | R-0, HSC            | R-0, HSC            | R-0, HSC            |

|----------|-----------|-----|-----|---------------------|---------------------|---------------------|---------------------|

| IBF      | IBOV      | _   | _   | IB3F <sup>(1)</sup> | IB2F <sup>(1)</sup> | IB1F <sup>(1)</sup> | IB0F <sup>(1)</sup> |

| bit 15   |           |     |     |                     |                     |                     | bit 8               |

| R-1, HSC | R/W-0, HS | U-0 | U-0 | R-1, HSC | R-1, HSC | R-1, HSC | R-1, HSC |

|----------|-----------|-----|-----|----------|----------|----------|----------|

| OBE      | OBUF      | _   | _   | OB3E     | OB2E     | OB1E     | OB0E     |

| bit 7    |           |     |     |          |          |          | bit 0    |

| Legend:           | egend: HS = Hardware Settable bit |                                    | Clearable bit      |  |

|-------------------|-----------------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set                  | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15 IBF: Input Buffer Full Status bit

1 = All writable Input Buffer registers are full

0 = Some or all of the writable Input Buffer registers are empty

bit 14 IBOV: Input Buffer Overflow Status bit

1 = A write attempt to a full Input register occurred (must be cleared in software)

0 = No overflow occurred

bit 13-12 **Unimplemented:** Read as '0'

bit 11-8 **IB3F:IB0F:** Input Buffer x Status Full bits<sup>(1)</sup>

1 = Input buffer contains unread data (reading the buffer will clear this bit)

0 = Input buffer does not contain unread data

bit 7 **OBE:** Output Buffer Empty Status bit

1 = All readable Output Buffer registers are empty

0 = Some or all of the readable Output Buffer registers are full

bit 6 **OBUF:** Output Buffer Underflow Status bit

1 = A read occurred from an empty Output Buffer register (must be cleared in software)

0 = No underflow occurred

bit 5-4 **Unimplemented:** Read as '0'

bit 3-0 **OB3E:OB0E:** Output Buffer x Status Empty bit

1 = Output Buffer x is empty (writing data to the buffer will clear this bit)

0 = Output Buffer x contains untransmitted data

**Note 1:** Even though an individual bit represents the byte in the buffer, the bits corresponding to the word (Byte 0 and 1, or Byte 2 and 3) get cleared, even on byte reading.

#### 24.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCONL

- CLCxCONH

- CLCxSEL

- CLCxGLSL

- CLCxGLSH

The CLCx Control registers (CLCxCONL and CLCxCONH) are used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables.

The CLCx Input MUX Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Input Select registers (CLCxGLSL and CLCxGLSH) allow the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

#### REGISTER 24-1: CLCxCONL: CLCx CONTROL REGISTER (LOW)

| R/W-0  | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | U-0 | U-0   |

|--------|-----|-----|-----|-------|-------|-----|-------|

| LCEN   | _   | _   | _   | INTP  | INTN  | _   | _     |

| bit 15 |     |     |     |       |       |     | bit 8 |

| R/W-0 | R-0   | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----|-----|-------|-------|-------|

| LCOE  | LCOUT | LCPOL | _   | _   | MODE2 | MODE1 | MODE0 |

| bit 7 |       |       |     |     |       |       | bit 0 |

| Leaend  |  |

|---------|--|

| Legenia |  |

| -       |  |

bit 6

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 LCEN: CLCx Enable bit

1 = CLCx is enabled and mixing input signals0 = CLCx is disabled and has logic zero outputs

bit 14-12 Unimplemented: Read as '0'

bit 11 INTP: CLCx Positive Edge Interrupt Enable bit

1 = Interrupt will be generated when a rising edge occurs on LCOUT

0 = Interrupt will not be generated

bit 10 INTN: CLCx Negative Edge Interrupt Enable bit

1 = Interrupt will be generated when a falling edge occurs on LCOUT

0 = Interrupt will not be generated

bit 9-8 **Unimplemented:** Read as '0' bit 7 **LCOE:** CLCx Port Enable bit

1 = CLCx port pin output is enabled 0 = CLCx port pin output is disabled

LCOUT: CLCx Data Output Status bit

1 = CLCx output high

0 = CLCx output low

bit 5 LCPOL: CLCx Output Polarity Control bit

1 = The output of the module is inverted

0 = The output of the module is not inverted

bit 4-3 **Unimplemented:** Read as '0'

#### 25.2 Extended DMA Operations

In addition to the standard features available on all 12-bit A/D Converters, PIC24FJ1024GA610/GB610 family devices implement a limited extension of DMA functionality. This extension adds features that work with the device's DMA Controller to expand the A/D module's data storage abilities beyond the module's built-in buffer.

The Extended DMA functionality is controlled by the DMAEN bit (AD1CON1<11>); setting this bit enables the functionality. The DMABM bit (AD1CON1<12>) configures how the DMA feature operates.

#### 25.2.1 EXTENDED BUFFER MODE

Extended Buffer mode (DMABM = 1) maps the A/D Data Buffer registers and data from all channels above 26 into a user-specified area of data RAM. This allows users to read the conversion results of channels above 26, which do not have their own memory-mapped A/D buffer locations, from data memory.

To accomplish this, the DMA must be configured in Peripheral Indirect Addressing mode and the DMA destination address must point to the beginning of the buffer. The DMA count must be set to generate an interrupt after the desired number of conversions.

In Extended Buffer mode, the A/D control bits will function similarly to non-DMA modes. The BUFREGEN bit will still select between FIFO mode and Channel-Aligned mode, but the number of words in the destination FIFO will be determined by the SMPI<4:0> bits in DMA mode. In FIFO mode, the BUFM bit will still split the output FIFO into two sets of 13 results (the SMPIx bits should be set accordingly), and the BUFS bit will still indicate which set of results is being written to and which can be read.

#### 25.2.2 PIA MODE

When DMABM = 0, the A/D module is configured to function with the DMA Controller for Peripheral Indirect Addressing (PIA) mode operations. In this mode, the A/D module generates an 11-bit Indirect Address (IA). This is ORed with the destination address in the DMA Controller to define where the A/D conversion data will be stored.

In PIA mode, the buffer space is created as a series of contiguous smaller buffers, one per analog channel. The size of the channel buffer determines how many analog channels can be accommodated. The size of the buffer is selected by the DMABL<2:0> bits (AD1CON4<2:0>). The size options range from a single word per buffer to 128 words. Each channel is allocated a buffer of this size, regardless of whether or not the channel will actually have conversion data.

The IA is created by combining the base address within a channel buffer with three to five bits (depending on the buffer size) to identify the channel. The base address ranges from zero to seven bits wide, depending on the buffer size. The address is right-padded with a '0' in order to maintain address alignment in the Data Space. The concatenated channel and base address bits are then left-padded with zeros, as necessary, to complete the 11-bit IA.

The IA is configured to auto-increment which channel is written in each analog input's sub-buffer during write operations by using the SMPIx bits (AD1CON2<6:2>).

As with PIA operations for any DMA-enabled module, the base destination address in the DMADSTn register must be masked properly to accommodate the IA. Table 25-1 shows how complete addresses are formed. Note that the address masking varies for each buffer size option. Because of masking requirements, some address ranges may not be available for certain buffer sizes. Users should verify that the DMA base address is compatible with the buffer size selected.

Figure 25-2 shows how the parts of the address define the buffer locations in data memory. In this case, the module "allocates" 256 bytes of data RAM (1000h to 1100h) for 32 buffers of four words each. However, this is not a hard allocation and nothing prevents these locations from being used for other purposes. For example, in the current case, if Analog Channels 1, 3 and 8 are being sampled and converted, conversion data will only be written to the channel buffers, starting at 1008h, 1018h and 1040h. The holes in the PIA buffer space can be used for any other purpose. It is the user's responsibility to keep track of buffer locations and prevent data overwrites.

#### REGISTER 30-3: FSEC CONFIGURATION REGISTER

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   | _   | _   | _   | _   | _   | _      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| R/PO-1       | U-1 | U-1 | U-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |  |  |

|--------------|-----|-----|-----|--------|--------|--------|--------|--|--|

| AIVTDIS      | _   | _   | _   | CSS2   | CSS1   | CSS0   | CWRP   |  |  |

| bit 15 bit 8 |     |     |     |        |        |        |        |  |  |

| R/PO-1 | R/PO-1 | R/PO-1 | U-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |

|--------|--------|--------|-----|--------|--------|--------|--------|

| GSS1   | GSS0   | GWRP   | _   | BSEN   | BSS1   | BSS0   | BWRP   |

| bit 7  |        |        |     |        |        |        | bit 0  |

**Legend:** PO = Program Once bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '1'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-16 **Unimplemented:** Read as '1'

bit 15 AIVTDIS: Alternate Interrupt Vector Table Disable bit

1 = Disables AIVT; INTCON2<8> (AIVTEN) bit is not available 0 = Enables AIVT; INTCON2<8> (AIVTEN) bit is available

bit 14-12 Unimplemented: Read as '1'

bit 11-9 CSS<2:0>: Configuration Segment Code Protection Level bits

111 = No protection (other than CWRP)

110 = Standard security 10x = Enhanced security 0xx = High security

bit 8 **CWRP:** Configuration Segment Program Write Protection bit

1 = Configuration Segment is not write-protected0 = Configuration Segment is write-protected

bit 7-6 GSS<1:0>: General Segment Code Protection Level bits

11 = No protection (other than GWRP)

10 = Standard security 0x = High security

bit 5 **GWRP:** General Segment Program Write Protection bit

1 = General Segment is not write-protected0 = General Segment is write-protected

bit 4 Unimplemented: Read as '1' bit 3 BSEN: Boot Segment Control bit

**BSEN:** Boot Segment Control bit 1 = No Boot Segment is enabled

0 = Boot Segment size is determined by BSLIM<12:0>

bit 2-1 BSS<1:0>: Boot Segment Code Protection Level bits

11 = No protection (other than BWRP)

10 = Standard security 0x = High security

bit 0 BWRP: Boot Segment Program Write Protection bit

1 = Boot Segment can be written0 = Boot Segment is write-protected

**TABLE 33-11: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS**

| Operating Conditions: -40°C < TA < +85°C (unless otherwise stated) |        |                                         |      |     |      |       |                                                                 |  |

|--------------------------------------------------------------------|--------|-----------------------------------------|------|-----|------|-------|-----------------------------------------------------------------|--|

| Param<br>No.                                                       | Symbol | Characteristics                         | Min  | Тур | Max  | Units | Comments                                                        |  |

| DVR                                                                | TVREG  | Voltage Regulator Start-up Time         | _    | 10  | _    | μS    | VREGS = 0 with any POR or BOR                                   |  |

| DVR10                                                              | VBG    | Internal Band Gap Reference             | 1.14 | 1.2 | 1.26 | V     |                                                                 |  |

| DVR11                                                              | TBG    | Band Gap Reference<br>Start-up Time     | _    | 1   | _    | ms    |                                                                 |  |

| DVR20                                                              | VRGOUT | Regulator Output Voltage                | 1.6  | 1.8 | 2    | V     | VDD > 2.1V                                                      |  |

| DVR21                                                              | CEFC   | External Filter Capacitor Value         | 10   | _   |      | μF    | Series resistance < $3\Omega$ recommended; < $5\Omega$ required |  |

| DVR30                                                              | VLVR   | Low-Voltage Regulator<br>Output Voltage | _    | 1.2 | _    | V     | RETEN = 1, LPCFG = 0                                            |  |

TABLE 33-12: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

| Operating Conditions: -40°C < TA < +85°C (unless otherwise stated) |            |                                       |                                  |      |      |      |       |                           |

|--------------------------------------------------------------------|------------|---------------------------------------|----------------------------------|------|------|------|-------|---------------------------|

| Param<br>No.                                                       | Symbol     | Characteristic                        |                                  |      | Тур  | Max  | Units | Conditions                |

| DC18                                                               | DC18 VHLVD | HLVD Voltage on VDD Transition        | HLVDL<3:0> = 0100 <sup>(1)</sup> | 3.40 | _    | 3.74 | V     | VDIR = 1                  |

|                                                                    |            |                                       | HLVDL<3:0> = 0101                | 3.25 | _    | 3.58 | V     |                           |

|                                                                    |            |                                       | HLVDL<3:0> = 0110                | 2.95 | _    | 3.25 | V     |                           |

|                                                                    |            |                                       | HLVDL<3:0> = 0111                | 2.75 | _    | 3.04 | V     |                           |

|                                                                    |            |                                       | HLVDL<3:0> = 1000                | 2.65 | _    | 2.93 | V     |                           |

|                                                                    |            |                                       | HLVDL<3:0> = 1001                | 2.45 | _    | 2.75 | V     |                           |

|                                                                    |            |                                       | HLVDL<3:0> = 1010                | 2.35 | _    | 2.64 | V     |                           |

|                                                                    |            | HLVDL<3:0> = 1011                     | 2.25                             | _    | 2.50 | V    |       |                           |

|                                                                    |            | HLVDL<3:0> = 1100                     | 2.15                             | _    | 2.39 | V    |       |                           |

|                                                                    |            |                                       | HLVDL<3:0> = 1101                | 2.08 | _    | 2.28 | V     |                           |

|                                                                    |            |                                       | HLVDL<3:0> = 1110                | 2.00 |      | 2.17 | V     |                           |

| DC101                                                              | VTHL       | HLVD Voltage on HLVDIN Pin Transition | HLVDL<3:0> = 1111                |      | 1.20 |      | V     |                           |

| DC105                                                              | TONLVD     | HLVD Module Enable Time               |                                  | -    | 5    | _    | μS    | From POR or<br>HLVDEN = 1 |

**Note 1:** Trip points for values of HLVD<3:0>, from '0000' to '0011', are not implemented.