Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga610-i-bg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

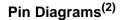

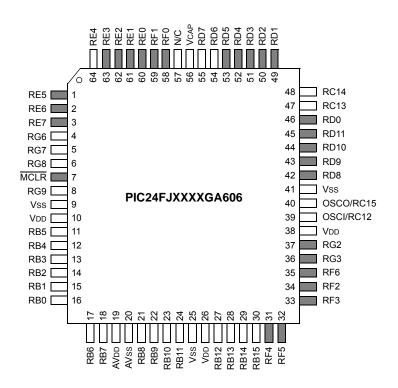

Legend: See Table 2 for a complete description of pin functions. Pinouts are subject to change.

Note 1: It is recommended to connect the metal pad on the bottom of the 64-pin QFN package to Vss.

2: Gray shading indicates 5.5V tolerant input pins.

TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                 |                    |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|--------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | 1/0 | Input<br>Buffer | Description        |

| RA0             | _                                   | _                                | 17                               | 17                               | G3                      | G3                      | I/O | DIG/ST          | PORTA Digital I/Os |

| RA1             | _                                   | _                                | 38                               | 38                               | J6                      | J6                      | I/O | DIG/ST          |                    |

| RA2             | _                                   | _                                | 58                               | 58                               | H11                     | H11                     | I/O | DIG/ST          |                    |

| RA3             | _                                   | _                                | 59                               | 59                               | G10                     | G10                     | I/O | DIG/ST          |                    |

| RA4             | _                                   | _                                | 60                               | 60                               | G11                     | G11                     | I/O | DIG/ST          |                    |

| RA5             | _                                   | _                                | 61                               | 61                               | G9                      | G9                      | I/O | DIG/ST          |                    |

| RA6             | _                                   | _                                | 91                               | 91                               | C5                      | C5                      | I/O | DIG/ST          |                    |

| RA7             | _                                   | _                                | 92                               | 92                               | B5                      | B5                      | I/O | DIG/ST          |                    |

| RA9             | _                                   | _                                | 28                               | 28                               | L2                      | L2                      | I/O | DIG/ST          |                    |

| RA10            | _                                   | _                                | 29                               | 29                               | K3                      | K3                      | I/O | DIG/ST          |                    |

| RA14            | _                                   | _                                | 66                               | 66                               | E11                     | E11                     | I/O | DIG/ST          |                    |

| RA15            | _                                   | _                                | 67                               | 67                               | E8                      | E8                      | I/O | DIG/ST          |                    |

| RB0             | 16                                  | 16                               | 25                               | 25                               | K2                      | K2                      | I/O | DIG/ST          | PORTB Digital I/Os |

| RB1             | 15                                  | 15                               | 24                               | 24                               | K1                      | K1                      | I/O | DIG/ST          |                    |

| RB2             | 14                                  | 14                               | 23                               | 23                               | J2                      | J2                      | I/O | DIG/ST          |                    |

| RB3             | 13                                  | 13                               | 22                               | 22                               | J1                      | J1                      | I/O | DIG/ST          |                    |

| RB4             | 12                                  | 12                               | 21                               | 21                               | H2                      | H2                      | I/O | DIG/ST          |                    |

| RB5             | 11                                  | 11                               | 20                               | 20                               | H1                      | H1                      | I/O | DIG/ST          |                    |

| RB6             | 17                                  | 17                               | 26                               | 26                               | L1                      | L1                      | I/O | DIG/ST          |                    |

| RB7             | 18                                  | 18                               | 27                               | 27                               | J3                      | J3                      | I/O | DIG/ST          |                    |

| RB8             | 21                                  | 21                               | 32                               | 32                               | K4                      | K4                      | I/O | DIG/ST          |                    |

| RB9             | 22                                  | 22                               | 33                               | 33                               | L4                      | L4                      | I/O | DIG/ST          |                    |

| RB10            | 23                                  | 23                               | 34                               | 34                               | L5                      | L5                      | I/O | DIG/ST          |                    |

| RB11            | 24                                  | 24                               | 35                               | 35                               | J5                      | J5                      | I/O | DIG/ST          |                    |

| RB12            | 27                                  | 27                               | 41                               | 41                               | J7                      | J7                      | I/O | DIG/ST          |                    |

| RB13            | 28                                  | 28                               | 42                               | 42                               | L7                      | L7                      | I/O | DIG/ST          |                    |

| RB14            | 29                                  | 29                               | 43                               | 43                               | K7                      | K7                      | I/O | DIG/ST          |                    |

| RB15            | 30                                  | 30                               | 44                               | 44                               | L8                      | L8                      | I/O | DIG/ST          |                    |

| RC1             | _                                   | _                                | 6                                | 6                                | D1                      | D1                      | I/O | DIG/ST          | PORTC Digital I/Os |

| RC2             |                                     |                                  | 7                                | 7                                | E4                      | E4                      | I/O | DIG/ST          |                    |

| RC3             |                                     |                                  | 8                                | 8                                | E2                      | E2                      | I/O | DIG/ST          |                    |

| RC4             |                                     |                                  | 9                                | 9                                | E1                      | E1                      | I/O | DIG/ST          |                    |

| RC12            | 39                                  | 39                               | 63                               | 63                               | F9                      | F9                      | I/O | DIG/ST          |                    |

| RC13            | 47                                  | 47                               | 73                               | 73                               | C10                     | C10                     | I/O | DIG/ST          |                    |

| RC14            | 48                                  | 48                               | 74                               | 74                               | B11                     | B11                     | I/O | DIG/ST          |                    |

| RC15            | 40                                  | 40                               | 64                               | 64                               | F11                     | F11                     | I/O | DIG/ST          |                    |

**Legend:** TTL = TTL input buffer

ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated Transceiver

#### REGISTER 9-6: OSCDIV: OSCILLATOR DIVISOR REGISTER

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-----------|-------|-------|-------|

| _      |       |       |       | DIV<14:8> |       |       |       |

| bit 15 |       |       |       |           |       |       | bit 8 |

| R/W-0 | R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | DIV<  | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-0 **DIV<14:0>:** Reference Clock Divider bits

Specifies the 1/2 period of the reference clock in the source clocks (ex: Period of ref\_clk\_output = [Reference Source \* 2] \* DIV<14:0>). 111111111111111 = Oscillator frequency divided by 65,534 (32,767 \* 2) 111111111111111 = Oscillator frequency divided by 65,532 (32,766 \* 2)

•

00000000000011 = Oscillator frequency divided by 6 (3 \* 2)

000000000000010 = Oscillator frequency divided by 4 (2 \* 2)

00000000000000 = Oscillator frequency is unchanged (no divider)

#### REGISTER 11-1: ANSA: PORTA ANALOG FUNCTION SELECTION REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1 | R/W-1                | U-0   |

|--------|-----|-----|-----|-----|-------|----------------------|-------|

| _      | _   | _   | _   | _   | ANSA< | 10:9> <sup>(1)</sup> | _     |

| bit 15 |     |     |     |     |       |                      | bit 8 |

| R/W-1 | R/W-1                | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|----------------------|-----|-----|-----|-----|-----|-------|

| ANSA< | <7:6> <sup>(1)</sup> | _   | _   | _   | _   | _   | _     |

| bit 7 |                      |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10-9 ANSA<10:9>: PORTA Analog Function Selection bits<sup>(1)</sup>

1 = Pin is configured in Analog mode; I/O port read is disabled 0 = Pin is configured in Digital mode; I/O port read is enabled

bit 8 Unimplemented: Read as '0'

bit 7-6 ANSA<7:6>: PORTA Analog Function Selection bits<sup>(1)</sup>

1 = Pin is configured in Analog mode; I/O port read is disabled 0 = Pin is configured in Digital mode; I/O port read is enabled

bit 5-0 **Unimplemented:** Read as '0'

**Note 1:** ANSA<10:9,7> bits are not available on 64-pin devices.

#### REGISTER 11-2: ANSB: PORTB ANALOG FUNCTION SELECTION REGISTER

| R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | ANSB  | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | ANSE  | 3<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 ANSB<15:0>: PORTB Analog Function Selection bits

1 = Pin is configured in Analog mode; I/O port read is disabled

0 = Pin is configured in Digital mode; I/O port read is enabled

**TABLE 16-5: SYNCHRONIZATION SOURCES**

| SYNC<4:0> | Synchronization Source                             |  |  |  |  |

|-----------|----------------------------------------------------|--|--|--|--|

| 11111     | None; Timer with Rollover on CCPxPR Match or FFFFh |  |  |  |  |

| 11110     | Reserved                                           |  |  |  |  |

| 11101     | Reserved                                           |  |  |  |  |

| 11100     | CTMU Trigger                                       |  |  |  |  |

| 11011     | A/D Start Conversion                               |  |  |  |  |

| 11010     | CMP3 Trigger                                       |  |  |  |  |

| 11001     | CMP2 Trigger                                       |  |  |  |  |

| 11000     | CMP1 Trigger                                       |  |  |  |  |

| 10111     | Reserved                                           |  |  |  |  |

| 10110     | Reserved                                           |  |  |  |  |

| 10101     | Reserved                                           |  |  |  |  |

| 10100     | Reserved                                           |  |  |  |  |

| 10011     | CLC4 Out                                           |  |  |  |  |

| 10010     | CLC3 Out                                           |  |  |  |  |

| 10001     | CLC2 Out                                           |  |  |  |  |

| 10000     | CLC1 Out                                           |  |  |  |  |

| 01111     | Reserved                                           |  |  |  |  |

| 01110     | Reserved                                           |  |  |  |  |

| 01101     | Reserved                                           |  |  |  |  |

| 01100     | Reserved                                           |  |  |  |  |

| 01011     | INT2 Pad                                           |  |  |  |  |

| 01010     | INT1 Pad                                           |  |  |  |  |

| 01001     | INTO Pad                                           |  |  |  |  |

| 01000     | SCCP7 Sync Out                                     |  |  |  |  |

| 00111     | SCCP6 Sync Out                                     |  |  |  |  |

| 00110     | SCCP5 Sync Out                                     |  |  |  |  |

| 00101     | SCCP4 Sync Out                                     |  |  |  |  |

| 00100     | MCCP3 Sync Out                                     |  |  |  |  |

| 00011     | MCCP2 Sync Out                                     |  |  |  |  |

| 00010     | MCCP1 Sync Out                                     |  |  |  |  |

| 00001     | MCCPx/SCCPx Sync Out <sup>(1)</sup>                |  |  |  |  |

| 00000     | MCCPx/SCCPx Timer Sync Out <sup>(1)</sup>          |  |  |  |  |

Note 1: CCP1 when connected to CCP1, CCP2 when connected to CCP2, etc.

#### REGISTER 16-6: CCPxCON3H: CCPx CONTROL 3 HIGH REGISTERS

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0 | R/W-0                | R/W-0                | R/W-0                |

|--------|--------|--------|--------|-----|----------------------|----------------------|----------------------|

| OETRIG | OSCNT2 | OSCNT1 | OSCNT0 | _   | OUTM2 <sup>(1)</sup> | OUTM1 <sup>(1)</sup> | OUTM0 <sup>(1)</sup> |

| bit 15 |        |        |        |     |                      |                      | bit 8                |

| U-0   | U-0 | R/W-0  | R/W-0                 | R/W-0   | R/W-0   | R/W-0                  | R/W-0                  |

|-------|-----|--------|-----------------------|---------|---------|------------------------|------------------------|

| _     | _   | POLACE | POLBDF <sup>(1)</sup> | PSSACE1 | PSSACE0 | PSSBDF1 <sup>(1)</sup> | PSSBDF0 <sup>(1)</sup> |

| bit 7 |     |        |                       |         |         |                        | bit 0                  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 **OETRIG:** CCPx Dead-Time Select bit

1 = For Triggered mode (TRIGEN = 1): Module does not drive enabled output pins until triggered

0 = Normal output pin operation

bit 14-12 OSCNT<2:0>: One-Shot Event Count bits

111 = Extends one-shot event by 7 time base periods (8 time base periods total)

110 = Extends one-shot event by 6 time base periods (7 time base periods total)

101 = Extends one-shot event by 5 time base periods (6 time base periods total)

100 = Extends one-shot event by 4 time base periods (5 time base periods total)

011 = Extends one-shot event by 3 time base periods (4 time base periods total)

010 = Extends one-shot event by 2 time base periods (3 time base periods total)

001 = Extends one-shot event by 1 time base period (2 time base periods total)

000 = Does not extend one-shot Trigger event

bit 11 **Unimplemented:** Read as '0'

bit 10-8 OUTM<2:0>: PWMx Output Mode Control bits<sup>(1)</sup>

111 = Reserved

110 = Output Scan mode

101 = Brush DC Output mode, forward

100 = Brush DC Output mode, reverse

011 = Reserved

010 = Half-Bridge Output mode

001 = Push-Pull Output mode

000 = Steerable Single Output mode

bit 7-6 **Unimplemented:** Read as '0'

bit 5 POLACE: CCPx Output Pins, OCMxA, OCMxC and OCMxE, Polarity Control bit

1 = Output pin polarity is active-low

0 = Output pin polarity is active-high

bit 4 **POLBDF:** CCPx Output Pins, OCMxB, OCMxD and OCMxF, Polarity Control bit<sup>(1)</sup>

1 = Output pin polarity is active-low

0 = Output pin polarity is active-high

bit 3-2 PSSACE<1:0>: PWMx Output Pins, OCMxA, OCMxC and OCMxE, Shutdown State Control bits

11 = Pins are driven active when a shutdown event occurs

10 = Pins are driven inactive when a shutdown event occurs

0x = Pins are tri-stated when a shutdown event occurs

bit 1-0 PSSBDF<1:0>: PWMx Output Pins, OCMxB, OCMxD, and OCMxF, Shutdown State Control bits<sup>(1)</sup>

11 = Pins are driven active when a shutdown event occurs

10 = Pins are driven inactive when a shutdown event occurs

0x = Pins are in a high-impedance state when a shutdown event occurs

**Note 1:** These bits are implemented in MCCPx modules only.

#### REGISTER 17-2: SPIXCON1H: SPIX CONTROL REGISTER 1 HIGH

| R/W-0                | R/W-0     | R/W-0  | R/W-0  | R/W-0                  | R/W-0                 | R/W-0                  | R/W-0                  |

|----------------------|-----------|--------|--------|------------------------|-----------------------|------------------------|------------------------|

| AUDEN <sup>(1)</sup> | SPISGNEXT | IGNROV | IGNTUR | AUDMONO <sup>(2)</sup> | URDTEN <sup>(3)</sup> | AUDMOD1 <sup>(4)</sup> | AUDMOD0 <sup>(4)</sup> |

| bit 15               |           |        |        |                        |                       |                        | bit 8                  |

| R/W-0 | R/W-0   | R/W-0  | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|---------|--------|-------|---------|---------|---------|---------|

| FRMEN | FRMSYNC | FRMPOL | MSSEN | FRMSYPW | FRMCNT2 | FRMCNT1 | FRMCNT0 |

| bit 7 |         |        |       |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 AUDEN: Audio Codec Support Enable bit<sup>(1)</sup>

- 1 = Audio protocol is enabled; MSTEN controls the direction of both the SCKx and Frame (a.k.a. LRC), and this module functions as if FRMEN = 1, FRMSYNC = MSTEN, FRMCNT<2:0> = 001 and SMP = 0, regardless of their actual values

- 0 = Audio protocol is disabled

- bit 14 SPISGNEXT: SPIx Sign-Extend RX FIFO Read Data Enable bit

- 1 = Data from RX FIFO is sign-extended

- 0 = Data from RX FIFO is not sign-extended

- bit 13 IGNROV: Ignore Receive Overflow bit

- 1 = A Receive Overflow (ROV) is NOT a critical error; during ROV, data in the FIFO is not overwritten by the receive data

- 0 = A ROV is a critical error that stops SPI operation

- bit 12 **IGNTUR:** Ignore Transmit Underrun bit

- 1 = A Transmit Underrun (TUR) is NOT a critical error and data indicated by URDTEN is transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 11 AUDMONO: Audio Data Format Transmit bit<sup>(2)</sup>

- 1 = Audio data is mono (i.e., each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 10 **URDTEN:** Transmit Underrun Data Enable bit<sup>(3)</sup>

- 1 = Transmits data out of SPIxURDTL/H register during Transmit Underrun conditions

- 0 = Transmits the last received data during Transmit Underrun conditions

- bit 9-8 AUDMOD<1:0>: Audio Protocol Mode Selection bits<sup>(4)</sup>

- 11 = PCM/DSP mode

- 10 = Right Justified mode: This module functions as if SPIFE = 1, regardless of its actual value

- 01 = Left Justified mode: This module functions as if SPIFE = 1, regardless of its actual value

- 00 = I<sup>2</sup>S mode: This module functions as if SPIFE = 0, regardless of its actual value

- bit 7 FRMEN: Framed SPIx Support bit

- 1 = Framed SPIx support is enabled ( $\overline{SSx}$  pin is used as the FSYNC input/output)

- 0 = Framed SPIx support is disabled

- **Note 1:** AUDEN can only be written when the SPIEN bit = 0.

- **2:** AUDMONO can only be written when the SPIEN bit = 0 and is only valid for AUDEN = 1.

- 3: URDTEN is only valid when IGNTUR = 1.

- **4:** AUDMOD<1:0> bits can only be written when the SPIEN bit = 0 and are only valid when AUDEN = 1. When NOT in PCM/DSP mode, this module functions as if FRMSYPW = 1, regardless of its actual value.

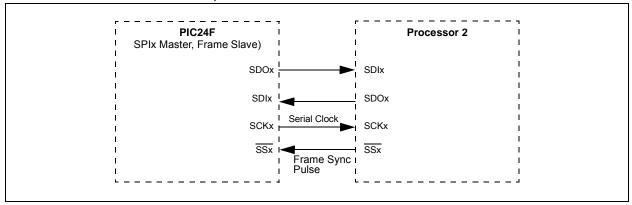

FIGURE 17-5: SPIX MASTER, FRAME SLAVE CONNECTION DIAGRAM

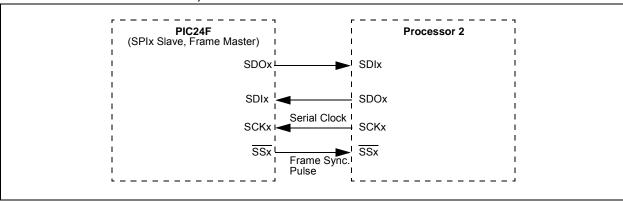

FIGURE 17-6: SPIX SLAVE, FRAME MASTER CONNECTION DIAGRAM

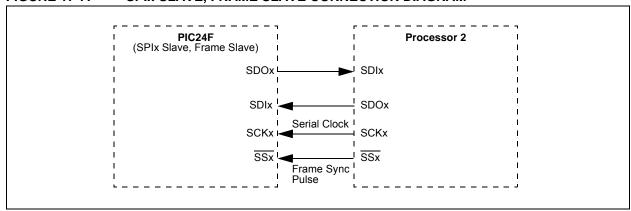

FIGURE 17-7: SPIX SLAVE, FRAME SLAVE CONNECTION DIAGRAM

**EQUATION 17-1: RELATIONSHIP BETWEEN DEVICE AND SPIx CLOCK SPEED**

$$Baud\ Rate = \frac{FPB}{(2*(SPIxBRG+1))}$$

Where:

FPB is the Peripheral Bus Clock Frequency.

#### 19.1 UARTx Baud Rate Generator (BRG)

The UARTx module includes a dedicated, 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 19-1 shows the formula for computation of the baud rate when BRGH = 0.

# EQUATION 19-1: UARTX BAUD RATE WITH BRGH = $0^{(1,2)}$

Baud Rate =

$$\frac{FCY}{16 \cdot (UxBRG + 1)}$$

$$UxBRG = \frac{FCY}{16 \cdot Baud Rate} - 1$$

**Note 1:** Fcy denotes the instruction cycle clock frequency (Fosc/2).

2: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

Example 19-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is Fcy/16 (for UxBRG = 0) and the minimum baud rate possible is Fcy/(16 \* 65536).

Equation 19-2 shows the formula for computation of the baud rate when BRGH = 1.

# EQUATION 19-2: UARTX BAUD RATE WITH BRGH = $1^{(1,2)}$

Baud Rate =

$$\frac{FCY}{4 \cdot (UxBRG + 1)}$$

$$UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$$

**Note 1:** Fcy denotes the instruction cycle clock frequency.

2: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is Fcy/4 (for UxBRG = 0) and the minimum baud rate possible is Fcy/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

## **EXAMPLE 19-1:** BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

Desired Baud Rate = FCY/(16 (UxBRG + 1))

Solving for UxBRG Value:

UxBRG = ((FCY/Desired Baud Rate)/16) - 1

UxBRG = ((4000000/9600)/16) - 1

UxBRG = 25

Calculated Baud Rate = 4000000/(16(25+1))

= 9615

Error = (Calculated Baud Rate – Desired Baud Rate)

Desired Baud Rate = (9615 – 9600)/9600

= 0.16%

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

# REGISTER 20-2: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER PROTOTYPE, CPU MODE (BD0STAT THROUGH BD63STAT)

| R/W-x  | R/W-x              | r-0 | r-0 | R/W-x | R/W-x  | R/W-x, HSC | R/W-x, HSC |

|--------|--------------------|-----|-----|-------|--------|------------|------------|

| UOWN   | DTS <sup>(1)</sup> | _   | _   | DTSEN | BSTALL | BC9        | BC8        |

| bit 15 |                    |     |     |       |        |            | bit 8      |

| R/W-x, HSC |

|------------|------------|------------|------------|------------|------------|------------|------------|

| BC7        | BC6        | BC5        | BC4        | BC3        | BC2        | BC1        | BC0        |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:           | r = Reserved bit | HSC = Hardware Settable/Clearable  | e bit      |

|-------------------|------------------|------------------------------------|------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |            |

| -n = Value at POR | '1' = Bit is set | 'r' = Reserved bit                 | is unknown |

bit 15 UOWN: USB Own bit

0 = The microcontroller core owns the BD and its corresponding buffer; the USB module ignores all other fields in the BD

bit 14 DTS: Data Toggle Packet bit<sup>(1)</sup>

1 = Data 1 packet 0 = Data 0 packet

bit 13-12 **Reserved:** Maintain as '0'

bit 11 DTSEN: Data Toggle Synchronization Enable bit

1 = Data toggle synchronization is enabled; data packets with incorrect Sync value will be ignored

0 = No data toggle synchronization is performed

bit 10 BSTALL: Buffer STALL Enable bit

1 = Buffer STALL is enabled; STALL handshake issued if a token is received that would use the BD in the given location (UOWN bit remains set, BD value is unchanged); corresponding EPSTALL bit will get set on any STALL handshake

0 = Buffer STALL is disabled

bit 9-0 **BC<9:0>:** Byte Count bits

This represents the number of bytes to be transmitted or the maximum number of bytes to be received during a transfer. Upon completion, the byte count is updated by the USB module with the actual number of bytes transmitted or received.

**Note 1:** This bit is ignored unless DTSEN = 1.

Note:

#### 20.3.1 CLEARING USB OTG INTERRUPTS

Unlike device-level interrupts, the USB OTG interrupt status flags are not freely writable in software. All USB OTG flag bits are implemented as hardware set only bits. Additionally, these bits can only be cleared in software by writing a '1' to their locations (i.e., performing a MOV type instruction). Writing a '0' to a flag bit (i.e., a BCLR instruction) has no effect.

Throughout this data sheet, a bit that can only be cleared by writing a '1' to its location is referred to as "Write '1' to Clear". In register descriptions; this function is indicated by the descriptor, "K".

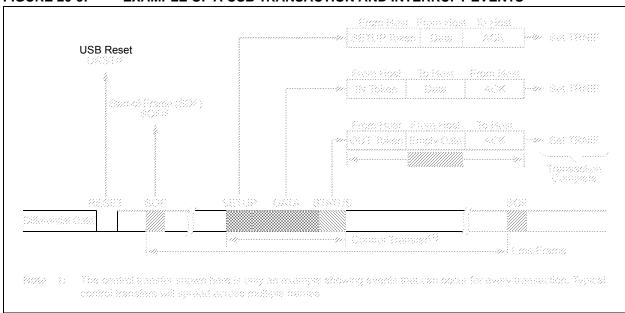

#### FIGURE 20-9: EXAMPLE OF A USB TRANSACTION AND INTERRUPT EVENTS

#### 20.4 Device Mode Operation

The following section describes how to perform a common Device mode task. In Device mode, USB transfers are performed at the transfer level. The USB module automatically performs the status phase of the transfer.

#### 20.4.1 ENABLING DEVICE MODE

- Reset the Ping-Pong Buffer Pointers by setting, then clearing, the Ping-Pong Buffer Reset bit, PPBRST (U1CON<1>).

- 2. Disable all interrupts (U1IE and U1EIE = 00h).

- Clear any existing interrupt flags by writing FFh to U1IR and U1EIR.

- 4. Verify that VBUS is present (non-OTG devices only).

- Enable the USB module by setting the USBEN bit (U1CON<0>).

- Set the OTGEN bit (U1OTGCON<2>) to enable OTG operation.

- Enable the Endpoint 0 buffer to receive the first setup packet by setting the EPRXEN and EPHSHK bits for Endpoint 0 (U1EP0<3,0> = 1).

- 8. Power up the USB module by setting the USBPWR bit (U1PWRC<0>).

- 9. Enable the D+ pull-up resistor to signal an attach by setting the DPPULUP bit (U1OTGCON<7>).

# 20.5.3 SEND A FULL-SPEED BULK DATA TRANSFER TO A TARGET DEVICE

- Follow the procedure described in Section 20.5.1

"Enable Host Mode and Discover a Connected

Device" and Section 20.5.2 "Complete a Control Transaction to a Connected Device" to

discover and configure a device.

- To enable transmit and receive transfers with handshaking enabled, write 1Dh to U1EP0. If the target device is a low-speed device, also set the LSPD (U1EP0<7>) bit. If you want the hardware to automatically retry indefinitely if the target device asserts a NAK on the transfer, clear the Retry Disable bit, RETRYDIS (U1EP0<6>).

- Set up the BD for the current (even or odd) TX EP0 to transfer up to 64 bytes.

- 4. Set the USB device address of the target device in the address register (U1ADDR<6:0>).

- Write an OUT token to the desired endpoint to U1TOK. This triggers the module's transmit state machines to begin transmitting the token and the data.

- 6. Wait for the Token Complete Interrupt Flag, TRNIF. This indicates that the BD has been released back to the microprocessor and the transfer has completed. If the Retry Disable bit (RETRYDIS) is set, the handshake (ACK, NAK, STALL or ERROR (0Fh)) is returned in the BD PID field. If a STALL interrupt occurs, the pending packet must be dequeued and the error condition in the target device cleared. If a detach interrupt occurs (SE0 for more than 2.5 μs), then the target has detached (U1IR<0> is set).

- 7. Once the Token Complete Interrupt Flag occurs (TRNIF is set), the BD can be examined and the next data packet queued by returning to Step 2.

Note: USB speed, transceiver and pull-ups should only be configured during the module setup phase. It is not recommended to change these settings while the module is enabled.

#### 20.6 OTG Operation

# 20.6.1 SESSION REQUEST PROTOCOL (SRP)

An OTG A-device may decide to power down the VBUS supply when it is not using the USB link through the Session Request Protocol (SRP). SRP can only be initiated at full speed. Software may do this by configuring a GPIO pin to disable an external power transistor, or voltage regulator enable signal, which controls the VBUS supply. When the VBUS supply is powered down, the A-device is said to have ended a USB session.

An OTG A-device or embedded host may repower the VBUS supply at any time (initiate a new session). An OTG B-device may also request that the OTG A-device repower the VBUS supply (initiate a new session). This is accomplished via Session Request Protocol (SRP).

Prior to requesting a new session, the B-device must first check that the previous session has definitely ended. To do this, the B-device must check for two conditions:

- 1. VBUS supply is below the session valid voltage.

- 2. Both D+ and D- have been low for at least 2 ms.

The B-device will be notified of Condition 1 by the SESENDIF (U10TGIR<2>) interrupt. Software will have to manually check for Condition 2.

Note: When the A-device powers down the VBUS supply, the B-device must disconnect its pull-up resistor from power. If the device is self-powered, it can do this by clearing DPPULUP (U1OTGCON<7>) and DMPULUP (U1OTGCON<6>).

The B-device may aid in achieving Condition 1 by discharging the VBUS supply through a resistor. Software may do this by setting VBUSDIS (U1OTGCON<0>).

After these initial conditions are met, the B-device may begin requesting the new session. The B-device begins by pulsing the D+ data line. Software should do this by setting DPPULUP (U1OTGCON<7>). The data line should be held high for 5 to 10 ms.

The B-device then proceeds by pulsing the VBUS supply. Software should do this by setting PUVBUS (U1CNFG2<4>). When an A-device detects SRP signaling (either via the ATTACHIF (U1IR<6>) interrupt or via the SESVDIF (U1OTGIR<3>) interrupt), the A-device must restore the VBUS supply by properly configuring the general purpose I/O port pin controlling the external power source.

The B-device should not monitor the state of the VBUS supply while performing VBUS supply pulsing. When the B-device does detect that the VBUS supply has been restored (via the SESVDIF (U10TGIR<3>) interrupt), the B-device must reconnect to the USB link by pulling up D+ or D- (via the DPPULUP or DMPULUP bit).

The A-device must complete the SRP by driving USB Reset signaling.

#### **REGISTER 20-6: U1STAT: USB STATUS REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R-0, HSC            | U-0 | U-0   |

|----------|----------|----------|----------|----------|---------------------|-----|-------|

| ENDPT3   | ENDPT2   | ENDPT1   | ENDPT0   | DIR      | PPBI <sup>(1)</sup> | _   | _     |

| bit 7    |          |          |          |          |                     |     | bit 0 |

Legend:U = Unimplemented bit, read as '0'R = Readable bitW = Writable bitHSC = Hardware Settable/Clearable bit-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-4 **ENDPT<3:0>:** Number of the Last Endpoint Activity bits

(Represents the number of the BDT updated by the last USB transfer.)

1111 = Endpoint 15

1110 = Endpoint 14

•

0001 = Endpoint 1

0000 = Endpoint 0

bit 3 DIR: Last BD Direction Indicator bit

1 = The last transaction was a transmit transfer (TX)

0 = The last transaction was a receive transfer (RX)

bit 2 **PPBI:** Ping-Pong BD Pointer Indicator bit<sup>(1)</sup>

1 = The last transaction was to the odd BD bank

0 = The last transaction was to the even BD bank

bit 1-0 **Unimplemented:** Read as '0'

**Note 1:** This bit is only valid for endpoints with available even and odd BD registers.

#### REGISTER 23-1: CRCCON1: CRC CONTROL 1 REGISTER

| R/W-0  | U-0 | R/W-0 | R-0, HSC |

|--------|-----|-------|----------|----------|----------|----------|----------|

| CRCEN  | _   | CSIDL | VWORD4   | VWORD3   | VWORD2   | VWORD1   | VWORD0   |

| bit 15 |     |       |          |          |          |          | bit 8    |

| R-0, HSC | R-1, HSC | R/W-0   | R/W-0, HC | R/W-0   | U-0 | U-0 | U-0   |

|----------|----------|---------|-----------|---------|-----|-----|-------|

| CRCFUL   | CRCMPT   | CRCISEL | CRCGO     | LENDIAN | _   | _   | _     |

| bit 7    |          |         |           |         |     |     | bit 0 |

| Legend: HC = Hardware Clearable bit |                  | HSC = Hardware Settable/Clearable bit |                    |  |  |

|-------------------------------------|------------------|---------------------------------------|--------------------|--|--|

| R = Readable bit                    | W = Writable bit | U = Unimplemented bit, read as '0'    |                    |  |  |

| -n = Value at POR                   | '1' = Bit is set | '0' = Bit is cleared                  | x = Bit is unknown |  |  |

bit 15 CRCEN: CRC Enable bit

1 = Enables module

0 = Disables module; all state machines, pointers and CRCWDAT/CRCDATH registers reset; other SFRs are NOT reset

bit 14 Unimplemented: Read as '0'

bit 13 CSIDL: CRC Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-8 VWORD<4:0>: CRC Pointer Value bits

Indicates the number of valid words in the FIFO. Has a maximum value of 8 when PLEN<4:0> ≥ 7 or 16 when PLEN<4:0> < 7

when PLEN<4:0>  $\leq$  7.

bit 7 CRCFUL: CRC FIFO Full bit

1 = FIFO is full 0 = FIFO is not full

bit 6 CRCMPT: CRC FIFO Empty bit

1 = FIFO is empty

0 = FIFO is not empty

bit 5 CRCISEL: CRC Interrupt Selection bit

1 = Interrupt on FIFO is empty; the final word of data is still shifting through the CRC

0 = Interrupt on shift is complete and results are ready

bit 4 CRCGO: Start CRC bit

1 = Starts CRC serial shifter0 = CRC serial shifter is turned off

bit 3 LENDIAN: Data Shift Direction Select bit

1 = Data word is shifted into the CRC, starting with the LSb (little-endian)

0 = Data word is shifted into the CRC, starting with the MSb (big-endian)

bit 2-0 **Unimplemented:** Read as '0'

#### REGISTER 25-1: AD1CON1: A/D CONTROL REGISTER 1 (CONTINUED)

bit 1 SAMP: A/D Sample Enable bit

1 = A/D Sample-and-Hold amplifiers are sampling 0 = A/D Sample-and-Hold amplifiers are holding

bit 0 **DONE:** A/D Conversion Status bit

1 = A/D conversion cycle has completed

0 = A/D conversion cycle has not started or is in progress

Note 1: This bit is only available when Extended DMA and buffer features are available (DMAEN = 1).

#### REGISTER 25-6: AD1CHS: A/D SAMPLE SELECT REGISTER

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| CH0NB2 | CH0NB1 | CH0NB0 | CH0SB4 | CH0SB3 | CH0SB2 | CH0SB1 | CH0SB0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| CH0NA2 | CH0NA1 | CH0NA0 | CH0SA4 | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 CH0NB<2:0>: Sample B Channel 0 Negative Input Select bits

1xx = Unimplemented

01x = Unimplemented

001 = Unimplemented

000 **= AV**ss

bit 12-8 CH0SB<4:0>: Sample B Channel 0 Positive Input Select bits

$11110 = AVDD^{(1)}$

11101 = AVss<sup>(1)</sup>

11100 = Band Gap Reference (VBG)(1)

11011 = Reserved

11010 = Reserved

11001 = No channels connected (used for CTMU)

11000 = No channels connected (used for CTMU temperature sensor)

10111 = AN23

10110 **= AN22**

10101 **= AN21**

10100 **= AN20**

10011 **= AN19**

10010 = AN18

10001 **= AN17**

10000 **= AN16**

01111 **= AN15**

01110 **= AN14**

01101 **= AN13**

01100 = AN12

01011 **= AN11**

01010 **= AN10**

01001 **= AN9**

01000 **= AN8**

00111 = AN7

00110 **= AN6**

00101 **= AN5**

00100 **= AN4**

00011 **= AN3**

00010 **= AN2**

00001 **= AN1**

00000 **= AN0**

bit 7-5 CH0NA<2:0>: Sample A Channel 0 Negative Input Select bits

Same definitions as for CHONB<2:0>.

bit 4-0 CH0SA<4:0>: Sample A Channel 0 Positive Input Select bits

Same definitions as for CHOSB<4:0>.

Note 1: These input channels do not have corresponding memory-mapped result buffers.

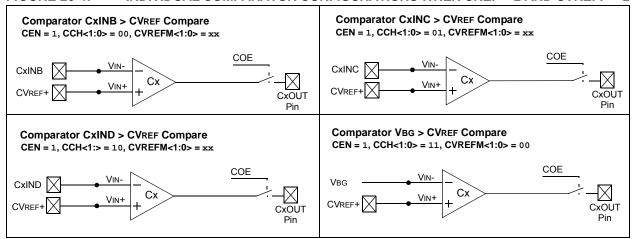

#### FIGURE 26-4: INDIVIDUAL COMPARATOR CONFIGURATIONS WHEN CREF = 1 AND CVREFP = 1

TABLE 30-1: CONFIGURATION WORD ADDRESSES

| Configuration         | Single Partition Mode               |                                                          |                  |                 |  |  |  |

|-----------------------|-------------------------------------|----------------------------------------------------------|------------------|-----------------|--|--|--|

| Registers             | PIC24FJ1024GX6XX                    | PIC24FJ512GX6XX                                          | PIC24FJ256GX6XX  | PIC24FJ128GX6XX |  |  |  |

| FSEC                  | 0ABF00h                             | 055F00h                                                  | 02AF00h          | 015F00h         |  |  |  |

| FBSLIM                | 0ABF10h                             | 055F10h                                                  | 02AF10h          | 015F10h         |  |  |  |

| FSIGN                 | 0ABF14h                             | 055F14h                                                  | 02AF14h          | 015F14h         |  |  |  |

| FOSCSEL               | 0ABF18h                             | 055F18h                                                  | 02AF18h          | 015F18h         |  |  |  |

| FOSC                  | 0ABF1Ch                             | 055F1Ch                                                  | 02AF1Ch          | 015F1Ch         |  |  |  |

| FWDT                  | 0ABF20h                             | 055F20h                                                  | 02AF20h          | 015F20h         |  |  |  |

| FPOR                  | 0ABF24h                             | 055F24h                                                  | 02AF24h          | 015F24h         |  |  |  |

| FICD                  | 0ABF28h                             | 055F28h                                                  | 02AF28h          | 015F28h         |  |  |  |

| FDEVOPT1              | 0ABF2Ch                             | 055F2Ch                                                  | 02AF2Ch          | 015F2Ch         |  |  |  |

| FBOOT                 | 801800h                             |                                                          |                  |                 |  |  |  |

|                       | Dual Partition Modes <sup>(1)</sup> |                                                          |                  |                 |  |  |  |

| FSEC <sup>(2)</sup>   | 055F00h/455F00h                     | 02AF00h/42AF00h                                          | 015700h/415700h  | 00AF00h/40AF00h |  |  |  |

| FBSLIM <sup>(2)</sup> | 055F10h/455F10h                     | 02AF10h/42AF10h                                          | 015710h/415710h  | 00AF10h/40AF10h |  |  |  |

| FSIGN <sup>(2)</sup>  | 055F14h/455F14h                     | 02AF14h/42AF14h                                          | 015714h/ 415714h | 00AF14h/40AF14h |  |  |  |

| FOSCSEL               | 055F18h/455F18h                     | 02AF18h/42AF18h                                          | 015718h/415718h  | 00AF18h/40AF18h |  |  |  |

| FOSC                  | 055F1Ch/455F1Ch                     | 02AF1Ch/42AF1Ch                                          | 01571Ch/41571Ch  | 00AF1Ch/40AF1Ch |  |  |  |

| FWDT                  | 055F20h/455F20h                     | 02AF20h/42AF20h                                          | 015720h/415720h  | 00AF20h/40AF20h |  |  |  |

| FPOR                  | 055F24h/ 455F24h                    | 02AF24h/42AF24h                                          | 015724h/415724h  | 00AF24h/40AF24h |  |  |  |

| FICD                  | 055F28h/455F28h                     | 02AF28h/42AF28h                                          | 015728h/415728h  | 00AF28h/40AF28h |  |  |  |

| FDEVOPT1              | 055F2Ch/455F2Ch                     | 02AF2Ch/42AF2Ch                                          | 01572Ch/41572Ch  | 00AF2Ch/40AF2Ch |  |  |  |

| FBTSEQ <sup>(3)</sup> | 055FFCh/455FFCh                     | 055FFCh/455FFCh 02AFFCh/42AFFCh 0157FCh/4157FCh 00AFFCh/ |                  | 00AFFCh/40AFFCh |  |  |  |

| FBOOT                 | 801800h                             |                                                          |                  |                 |  |  |  |

Note 1: Addresses shown for Dual Partition modes are for the Active/Inactive Partitions, respectively.

**<sup>2:</sup>** Changes to these Inactive Partition Configuration Words affect how the Active Partition accesses the Inactive Partition.

<sup>3:</sup> FBTSEQ is a 24-bit Configuration Word, using all three bytes of the program memory width.

#### REGISTER 30-3: FSEC CONFIGURATION REGISTER

| U-1           | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 |

|---------------|-----|-----|-----|-----|-----|-----|-----|

| _             | _   | _   | _   | _   | _   | _   | _   |

| bit 23 bit 16 |     |     |     |     |     |     |     |

| R/PO-1  | U-1 | U-1 | U-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |

|---------|-----|-----|-----|--------|--------|--------|--------|

| AIVTDIS | _   | _   | _   | CSS2   | CSS1   | CSS0   | CWRP   |

| bit 15  |     |     |     |        |        |        | bit 8  |

| R/PO-1 | R/PO-1 | R/PO-1 | U-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |

|--------|--------|--------|-----|--------|--------|--------|--------|

| GSS1   | GSS0   | GWRP   | _   | BSEN   | BSS1   | BSS0   | BWRP   |

| bit 7  |        |        |     |        |        |        | bit 0  |

**Legend:** PO = Program Once bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '1'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-16 **Unimplemented:** Read as '1'

bit 15 AIVTDIS: Alternate Interrupt Vector Table Disable bit

1 = Disables AIVT; INTCON2<8> (AIVTEN) bit is not available 0 = Enables AIVT; INTCON2<8> (AIVTEN) bit is available

bit 14-12 Unimplemented: Read as '1'

bit 11-9 CSS<2:0>: Configuration Segment Code Protection Level bits

111 = No protection (other than CWRP)

110 = Standard security 10x = Enhanced security 0xx = High security

bit 8 **CWRP:** Configuration Segment Program Write Protection bit

1 = Configuration Segment is not write-protected0 = Configuration Segment is write-protected

bit 7-6 GSS<1:0>: General Segment Code Protection Level bits

11 = No protection (other than GWRP)

10 = Standard security 0x = High security

bit 5 **GWRP:** General Segment Program Write Protection bit

1 = General Segment is not write-protected0 = General Segment is write-protected

bit 4 Unimplemented: Read as '1' bit 3 BSEN: Boot Segment Control bit

**BSEN:** Boot Segment Control bit 1 = No Boot Segment is enabled

0 = Boot Segment size is determined by BSLIM<12:0>

bit 2-1 BSS<1:0>: Boot Segment Code Protection Level bits

11 = No protection (other than BWRP)

10 = Standard security 0x = High security

bit 0 BWRP: Boot Segment Program Write Protection bit

1 = Boot Segment can be written0 = Boot Segment is write-protected