Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga610t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ1024GB610 PIC24FJ1024GA610

- PIC24FJ512GB610

- PIC24FJ512GA610

PIC24FJ256GA610

- PIC24FJ256GB610

- PIC24FJ128GB610 PIC24FJ128GA610

- PIC24FJ1024GB606 PIC24FJ1024GA606

- PIC24FJ512GB606 PIC24FJ512GA606

- PIC24FJ256GB606

- PIC24FJ256GA606

- PIC24FJ128GB606 PIC24FJ128GA606

The PIC24FJ1024GA610/GB610 family introduces many new analog features to the extreme low-power Microchip devices. This is a 16-bit microcontroller family with a broad peripheral feature set and enhanced computational performance. This family also offers a new migration option for those high-performance applications which may be outgrowing their 8-bit platforms, but do not require the numerical processing power of a Digital Signal Processor (DSP).

Table 1-3 lists the functions of the various pins shown in the pinout diagrams.

## 1.1 Core Features

## 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers (DSCs). The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 32 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- Operational performance up to 16 MIPS

## 1.1.2 POWER-SAVING TECHNOLOGY

The PIC24FJ1024GA610/GB610 family of devices includes Retention Sleep, a low-power mode with essential circuits being powered from a separate low-voltage regulator.

This new low-power mode also supports the continuous operation of the low-power, on-chip Real-Time Clock/ Calendar (RTCC), making it possible for an application to keep time while the device is otherwise asleep.

Aside from this new feature, PIC24FJ1024GA610/GB610 family devices also include all of the legacy power-saving features of previous PIC24F microcontrollers, such as:

- On-the-Fly Clock Switching, allowing the selection of a lower power clock during run time

- Doze Mode Operation, for maintaining peripheral clock speed while slowing the CPU clock

- Instruction-Based Power-Saving Modes, for quick invocation of the Idle and the Sleep modes

#### 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC24FJ1024GA610/GB610 family offer six different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes

- Two External Clock (EC) modes

- A Phase-Locked Loop (PLL) frequency multiplier, which allows clock speeds of up to 32 MHz

- A Digitally Controlled Oscillator (DCO) with multiple frequencies and fast wake-up time

- A Fast Internal Oscillator (FRC), a nominal 8 MHz output, with multiple frequency divider options

- A separate Low-Power Internal RC Oscillator (LPRC), 31 kHz nominal, for low-power, timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

## 1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve. The consistent pinout scheme used throughout the entire family also aids in migrating from one device to the next larger device, or even in jumping from 64-pin to 100-pin devices.

The PIC24F family is pin-compatible with devices in the dsPIC33 family, and shares some compatibility with the pinout schema for PIC18 and dsPIC30. This extends the ability of applications to grow from the relatively simple, to the powerful and complex, yet still selecting a Microchip device.

| REGISTER 5-1: | DMACON: DMA ENGINE CONTROL REGISTER |

|---------------|-------------------------------------|

|               |                                     |

| R/W-0         | U-0                                | U-0           | U-0    | U-0                                | U-0 | U-0                | U-0    |  |  |

|---------------|------------------------------------|---------------|--------|------------------------------------|-----|--------------------|--------|--|--|

| DMAEN         | —                                  | —             | _      | —                                  | —   | —                  | —      |  |  |

| bit 15        |                                    |               |        | -<br>-                             |     | •                  | bit 8  |  |  |

|               |                                    |               |        |                                    |     |                    |        |  |  |

| U-0           | U-0                                | U-0           | U-0    | U-0                                | U-0 | U-0                | R/W-0  |  |  |

| —             | —                                  | —             | —      | —                                  | —   | —                  | PRSSEL |  |  |

| bit 7 bit 0   |                                    |               |        |                                    |     |                    |        |  |  |

|               |                                    |               |        |                                    |     |                    |        |  |  |

| Legend:       |                                    |               |        |                                    |     |                    |        |  |  |

| R = Readable  | e bit                              | W = Writable  | bit    | U = Unimplemented bit, read as '0' |     |                    |        |  |  |

| -n = Value at | -n = Value at POR '1' = Bit is set |               |        | '0' = Bit is cleared               |     | x = Bit is unknown |        |  |  |

|               |                                    |               |        |                                    |     |                    |        |  |  |

| bit 15        | DMAEN: DM                          | A Module Enab | le bit |                                    |     |                    |        |  |  |

|               | 1 - Enchlos                        | modulo        |        |                                    |     |                    |        |  |  |

1 = Enables module

0 = Disables module and terminates all active DMA operation(s)

bit 14-1 Unimplemented: Read as '0'

bit 0 PRSSEL: Channel Priority Scheme Selection bit

1 = Round-robin scheme

0 = Fixed priority scheme

| U-0                                                                                       | U-0                             | U-0                                                                                                                                                           | r-0             | U-0                                 | R/W-0            | R/W-0                 | R/W-0                  |  |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------|------------------|-----------------------|------------------------|--|--|--|

| _                                                                                         | —                               | -                                                                                                                                                             | —               | —                                   | NULLW            | RELOAD <sup>(1)</sup> | CHREQ <sup>(3)</sup>   |  |  |  |

| bit 15                                                                                    |                                 |                                                                                                                                                               |                 |                                     |                  |                       | bit 8                  |  |  |  |

| R/W-0                                                                                     | R/W-0                           | R/W-0                                                                                                                                                         | R/W-0           | R/W-0                               | R/W-0            | R/W-0                 | R/W-0                  |  |  |  |

| SAMODE                                                                                    | _                               | DAMODE1                                                                                                                                                       | DAMODE0         | TRMODE1                             | TRMODE0          | SIZE                  | CHEN                   |  |  |  |

| bit 7                                                                                     |                                 |                                                                                                                                                               |                 |                                     |                  |                       | bit 0                  |  |  |  |

|                                                                                           |                                 | n Decement                                                                                                                                                    | L :4            |                                     |                  |                       |                        |  |  |  |

| Legend:r = Reserved bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                 |                                                                                                                                                               |                 |                                     |                  |                       |                        |  |  |  |

| -n = Value                                                                                |                                 | '1' = Bit is set                                                                                                                                              |                 | '0' = Bit is clea                   |                  | x = Bit is unkn       | 0000                   |  |  |  |

|                                                                                           | alfor                           | I - DILIS SEL                                                                                                                                                 |                 |                                     | areu             |                       | OWIT                   |  |  |  |

| bit 15-13                                                                                 | Unimplemen                      | ted: Read as '                                                                                                                                                | 0'              |                                     |                  |                       |                        |  |  |  |

| bit 12                                                                                    | Reserved: M                     | aintain as '0'                                                                                                                                                |                 |                                     |                  |                       |                        |  |  |  |

| bit 11                                                                                    | Unimplemen                      | ted: Read as '                                                                                                                                                | 0'              |                                     |                  |                       |                        |  |  |  |

| bit 10                                                                                    | NULLW: Null                     | Write Mode bit                                                                                                                                                | :               |                                     |                  |                       |                        |  |  |  |

|                                                                                           |                                 |                                                                                                                                                               |                 | n for every writ                    | e to DMADSTr     | า                     |                        |  |  |  |

|                                                                                           | 0 = No dummy write is initiated |                                                                                                                                                               |                 |                                     |                  |                       |                        |  |  |  |

| bit 9                                                                                     |                                 | RELOAD: Address and Count Reload bit <sup>(1)</sup>                                                                                                           |                 |                                     |                  |                       |                        |  |  |  |

|                                                                                           |                                 | 1 = DMASRCn, DMADSTn and DMACNTn registers are reloaded to their previous values upon the<br>start of the next operation                                      |                 |                                     |                  |                       |                        |  |  |  |

|                                                                                           |                                 |                                                                                                                                                               |                 | n are not reload                    | led on the start | of the next ope       | eration <sup>(2)</sup> |  |  |  |

| bit 8                                                                                     |                                 | 0 = DMASRCn, DMADSTn and DMACNTn are not reloaded on the start of the next operation <sup>(2)</sup><br>CHREQ: DMA Channel Software Request bit <sup>(3)</sup> |                 |                                     |                  |                       |                        |  |  |  |

|                                                                                           |                                 |                                                                                                                                                               |                 | ; automatically                     | cleared upon c   | completion of a       | DMA transfer           |  |  |  |

|                                                                                           | 0 = NO DMA                      | 0 = No DMA request is pending                                                                                                                                 |                 |                                     |                  |                       |                        |  |  |  |

| bit 7-6                                                                                   |                                 | 0>: Source Add                                                                                                                                                |                 |                                     |                  |                       |                        |  |  |  |

|                                                                                           |                                 |                                                                                                                                                               |                 | ect Addressing                      |                  |                       |                        |  |  |  |

|                                                                                           |                                 |                                                                                                                                                               |                 | the SIZE bit af<br>the SIZE bit aft |                  |                       |                        |  |  |  |

|                                                                                           |                                 |                                                                                                                                                               |                 | a transfer com                      |                  |                       |                        |  |  |  |

| bit 5-4                                                                                   | DAMODE<1:                       | 0>: Destination                                                                                                                                               | Address Mod     | e Selection bits                    | ;                |                       |                        |  |  |  |

|                                                                                           |                                 |                                                                                                                                                               |                 | ect Addressing                      |                  |                       |                        |  |  |  |

|                                                                                           |                                 |                                                                                                                                                               |                 | the SIZE bit aff                    |                  |                       |                        |  |  |  |

|                                                                                           |                                 |                                                                                                                                                               |                 | he SIZE bit afte<br>a transfer comp |                  | mpietion              |                        |  |  |  |

| bit 3-2                                                                                   |                                 | 0>: Transfer M                                                                                                                                                | -               | -                                   |                  |                       |                        |  |  |  |

|                                                                                           |                                 | ed Continuous                                                                                                                                                 |                 |                                     |                  |                       |                        |  |  |  |

|                                                                                           | 10 = Continue                   | ous mode                                                                                                                                                      |                 |                                     |                  |                       |                        |  |  |  |

|                                                                                           | •                               | ed One-Shot m                                                                                                                                                 | ode             |                                     |                  |                       |                        |  |  |  |

| <b>h</b> :+ 4                                                                             | 00 = One-Sh                     |                                                                                                                                                               |                 |                                     |                  |                       |                        |  |  |  |

| bit 1                                                                                     |                                 | ize Selection b                                                                                                                                               | IL              |                                     |                  |                       |                        |  |  |  |

|                                                                                           | 1 = Byte (8-bi<br>0 = Word (16- |                                                                                                                                                               |                 |                                     |                  |                       |                        |  |  |  |

| bit 0                                                                                     |                                 | Channel Enabl                                                                                                                                                 | e bit           |                                     |                  |                       |                        |  |  |  |

|                                                                                           | 1 = The corre                   | sponding chan                                                                                                                                                 | nel is enabled  |                                     |                  |                       |                        |  |  |  |

|                                                                                           | 0 = The corre                   | sponding chan                                                                                                                                                 | nel is disabled |                                     |                  |                       |                        |  |  |  |

| Note 1:                                                                                   | Only the original               | DMACNTn is re                                                                                                                                                 | equired to be s | tored to recove                     | r the original D | MASRCn and [          | OMADSTn.               |  |  |  |

| 2:                                                                                        | DMASRCn, DMA                    |                                                                                                                                                               |                 | -                                   |                  | de transfers          |                        |  |  |  |

|                                                                                           | (DMACHn<2> = )                  |                                                                                                                                                               |                 |                                     |                  |                       |                        |  |  |  |

| •                                                                                         |                                 | · ·                                                                                                                                                           |                 | <b>O !</b>                          |                  | aution of TDN         |                        |  |  |  |

#### REGISTER 5-2: DMACHn: DMA CHANNEL n CONTROL REGISTER

3: The number of transfers executed while CHREQ is set depends on the configuration of TRMODE<1:0>.

| R/W-0                             | U-0                                                                                                                                                                                                | U-0                                 | U-0               | U-0               | U-0               | U-0             | U-0   |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------|-------------------|-------------------|-----------------|-------|--|--|

| NSTDIS                            | _                                                                                                                                                                                                  |                                     | —                 | _                 | —                 | —               | _     |  |  |

| bit 15                            |                                                                                                                                                                                                    |                                     |                   |                   |                   |                 | bit 8 |  |  |

|                                   |                                                                                                                                                                                                    |                                     |                   |                   |                   |                 |       |  |  |

| U-0                               | U-0                                                                                                                                                                                                | U-0                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0           | U-0   |  |  |

|                                   | _                                                                                                                                                                                                  |                                     | MATHERR           | ADDRERR           | STKERR            | OSCFAIL         | —     |  |  |

| bit 7                             |                                                                                                                                                                                                    |                                     |                   |                   |                   |                 | bit 0 |  |  |

|                                   |                                                                                                                                                                                                    |                                     |                   |                   |                   |                 |       |  |  |

| Legend:                           |                                                                                                                                                                                                    |                                     |                   |                   |                   |                 |       |  |  |

| R = Readable bit W = Writable bit |                                                                                                                                                                                                    |                                     |                   | U = Unimplem      | ented bit, read a | as '0'          |       |  |  |

| -n = Value at                     | POR                                                                                                                                                                                                | '1' = Bit is set                    | t                 | '0' = Bit is clea | ired              | x = Bit is unkn | iown  |  |  |

| bit 15                            | NSTDIS: Interrupt Nesting Disable bit<br>1 = Interrupt nesting is disabled<br>0 = Interrupt nesting is enabled                                                                                     |                                     |                   |                   |                   |                 |       |  |  |

| bit 14-5                          | •                                                                                                                                                                                                  | Unimplemented: Read as '0'          |                   |                   |                   |                 |       |  |  |

| bit 4                             | •                                                                                                                                                                                                  | Math Error Sta                      |                   |                   |                   |                 |       |  |  |

|                                   |                                                                                                                                                                                                    | or trap has oco<br>or trap has not  |                   |                   |                   |                 |       |  |  |

| bit 3                             | 1 = Address                                                                                                                                                                                        | error trap has                      |                   |                   |                   |                 |       |  |  |

| bit 2                             | <ul> <li>0 = Address error trap has not occurred</li> <li>STKERR: Stack Error Trap Status bit</li> <li>1 = Stack error trap has occurred</li> <li>0 = Stack error trap has not occurred</li> </ul> |                                     |                   |                   |                   |                 |       |  |  |

| bit 1                             | <b>OSCFAIL:</b> C<br>1 = Oscillato                                                                                                                                                                 | Dscillator Failur<br>Failure trap h | re Trap Status bi | it                |                   |                 |       |  |  |

| bit 0                             | Unimpleme                                                                                                                                                                                          | nted: Read as                       | ʻ0'               |                   |                   |                 |       |  |  |

|                                   |                                                                                                                                                                                                    |                                     |                   |                   |                   |                 |       |  |  |

#### REGISTER 8-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| REGISTER 9      | -3: 0501                                                                                                                              | IUN: FRC 0                   | SCILLATOR                            | IUNE REGIS                   | IER                          |                              |                              |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|--|--|--|

| R/W-0           | U-0                                                                                                                                   | R/W-0                        | R/W-1                                | R-0                          | R/W-0                        | R-0                          | R/W-0                        |  |  |  |

| STEN            | —                                                                                                                                     | STSIDL                       | STSRC <sup>(1)</sup>                 | STLOCK                       | STLPOL                       | STOR                         | STORPOL                      |  |  |  |

| bit 15          |                                                                                                                                       |                              |                                      |                              |                              |                              | bit 8                        |  |  |  |

|                 |                                                                                                                                       | DAMA                         | DAMA                                 | DAALO                        | DAALO                        | DAMA                         | DAMO                         |  |  |  |

| U-0             | U-0                                                                                                                                   | R/W-0<br>TUN5 <sup>(2)</sup> | R/W-0<br>TUN4 <sup>(2)</sup>         | R/W-0<br>TUN3 <sup>(2)</sup> | R/W-0<br>TUN2 <sup>(2)</sup> | R/W-0<br>TUN1 <sup>(2)</sup> | R/W-0<br>TUN0 <sup>(2)</sup> |  |  |  |

|                 |                                                                                                                                       |                              |                                      |                              |                              |                              |                              |  |  |  |

| bit 7           |                                                                                                                                       |                              |                                      |                              |                              |                              | bit 0                        |  |  |  |

| Legend:         |                                                                                                                                       |                              |                                      |                              |                              |                              |                              |  |  |  |

| R = Readable    | bit                                                                                                                                   | W = Writable                 | bit                                  | U = Unimplen                 | nented bit, read             | d as '0'                     |                              |  |  |  |

| -n = Value at F | POR                                                                                                                                   | '1' = Bit is set             |                                      | '0' = Bit is clea            | ared                         | x = Bit is unk               | nown                         |  |  |  |

| bit 15          | STEN: FRC S                                                                                                                           | Self-Tune Enab               | le bit                               |                              |                              |                              |                              |  |  |  |

|                 |                                                                                                                                       | Ų                            | led; TUNx bits<br>bled; applicatior  |                              |                              | UNx bits                     |                              |  |  |  |

| bit 14          | Unimplemen                                                                                                                            | ted: Read as '               | 0'                                   |                              |                              |                              |                              |  |  |  |

| bit 13          | STSIDL: FRC Self-Tune Stop in Idle bit                                                                                                |                              |                                      |                              |                              |                              |                              |  |  |  |

|                 |                                                                                                                                       | ng stops during              |                                      |                              |                              |                              |                              |  |  |  |

| bit 12          | <ul> <li>0 = Self-tuning continues during Idle mode</li> <li>STSRC: FRC Self-Tune Reference Clock Source bit<sup>(1)</sup></li> </ul> |                              |                                      |                              |                              |                              |                              |  |  |  |

|                 | 1 = FRC is tuned to approximately match the USB host clock tolerance                                                                  |                              |                                      |                              |                              |                              |                              |  |  |  |

|                 |                                                                                                                                       |                              | imately match t                      |                              |                              | се                           |                              |  |  |  |

| bit 11          | STLOCK: FR                                                                                                                            | C Self-Tune Lo               | ock Status bit                       |                              |                              |                              |                              |  |  |  |

|                 |                                                                                                                                       |                              | tly within ±0.2%<br>be within ±0.2%  |                              |                              |                              |                              |  |  |  |

| bit 10          |                                                                                                                                       |                              | ock Interrupt Po                     | -                            |                              |                              |                              |  |  |  |

|                 |                                                                                                                                       | •                            | t is generated v<br>t is generated v |                              |                              |                              |                              |  |  |  |

| bit 9           | STOR: FRC S                                                                                                                           | Self-Tune Out                | of Range Status                      | s bit                        |                              |                              |                              |  |  |  |

|                 |                                                                                                                                       |                              | error is beyond<br>is within the tu  | 0                            |                              | <b>U</b>                     | med                          |  |  |  |

| bit 8           | STORPOL: F                                                                                                                            | RC Self-Tune                 | Out of Range I                       | nterrupt Polarity            | y bit                        |                              |                              |  |  |  |

|                 |                                                                                                                                       |                              | interrupt is ger<br>interrupt is ger |                              |                              |                              |                              |  |  |  |

| bit 7-6         | Unimplemen                                                                                                                            | ted: Read as '               | 0'                                   |                              |                              |                              |                              |  |  |  |

| bit 5-0         |                                                                                                                                       | RC Oscillator 7              | •                                    |                              |                              |                              |                              |  |  |  |

|                 | 011111 = Ma<br>011110 =                                                                                                               | aximum frequei               | ncy deviation                        |                              |                              |                              |                              |  |  |  |

|                 | •••<br>000001 =                                                                                                                       |                              |                                      |                              |                              |                              |                              |  |  |  |

|                 |                                                                                                                                       | enter frequency              | , oscillator is ru                   | nning at factory             | / calibrated free            | quency                       |                              |  |  |  |

|                 | • • •                                                                                                                                 |                              |                                      |                              |                              |                              |                              |  |  |  |

|                 | 100001 =<br>100000 = Min                                                                                                              | nimum frequen                | cv deviation                         |                              |                              |                              |                              |  |  |  |

|                 |                                                                                                                                       | -                            | -                                    |                              |                              |                              |                              |  |  |  |

| Note 1: Use     | e of either cloc                                                                                                                      | k tuning refere              | nce source has                       | specific applic              | ation requirem               | ents. See Sec                | tion 9.5 "FRC                |  |  |  |

#### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

- Note 1: Use of either clock tuning reference source has specific application requirements. See Section 9.5 "FRC Active Clock Tuning" for details.

- **2:** These bits are read-only when STEN = 1.

NOTES:

## 16.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the MCCP/SCCP modules, refer to the "dsPIC33/PIC24 Family Reference Manual", "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS33035A), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

PIC24FJ1024GA610/GB610 family devices include several Capture/Compare/PWM/Timer base modules, which provide the functionality of three different peripherals of earlier PIC24F devices. The module can operate in one of three major modes:

- · General Purpose Timer

- Input Capture

- Output Compare/PWM

The module is provided in two different forms, distinguished by the number of PWM outputs that the module can generate. Single Capture/Compare/PWM (SCCPs) output modules provide only one PWM output. Multiple Capture/Compare/PWM (MCCPs) output modules can provide up to six outputs and an extended range of power control features, depending on the pin count of the particular device. All other features of the modules are identical. The SCCPx and MCCPx modules can be operated only in one of the three major modes at any time. The other modes are not available unless the module is reconfigured for the new mode.

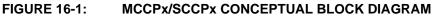

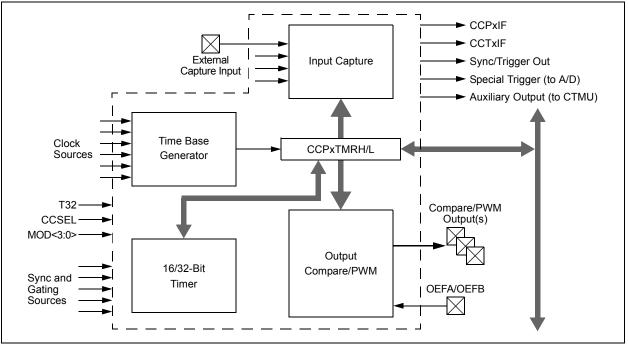

A conceptual block diagram for the module is shown in Figure 16-1. All three modules share a time base generator and a common Timer register pair (CCPxTMRH/L); other shared hardware components are added as a particular mode requires.

Each module has a total of 8 control and status registers:

- CCPxCON1L (Register 16-1)

- CCPxCON1H (Register 16-2)

- CCPxCON2L (Register 16-3)

- CCPxCON2H (Register 16-4)

- CCPxCON3L (Register 16-5)

- CCPxCON3H (Register 16-6)

- CCPxSTATL (Register 16-7)

- CCPxSTATH (Register 16-8)

Each module also includes 8 buffer/counter registers that serve as Timer Value registers or data holding buffers:

- CCPxTMRH/CCPxTMRL (Timer High/Low Counters)

- CCPxPRH/CCPxPRL (Timer Period High/Low)

- CCPxRA (Primary Output Compare Data Buffer)

- CCPxRB (Secondary Output Compare Data Buffer)

- CCPxBUFH/CCPxBUFL (Input Capture High/Low Buffers)

## 17.1 Master Mode Operation

Perform the following steps to set up the SPIx module for Master mode operation:

- 1. Disable the SPIx interrupts in the respective IECx register.

- 2. Stop and reset the SPIx module by clearing the SPIEN bit.

- 3. Clear the receive buffer.

- Clear the ENHBUF bit (SPIxCON1L<0>) if using Standard Buffer mode or set the bit if using Enhanced Buffer mode.

- 5. If SPIx interrupts are not going to be used, skip this step. Otherwise, the following additional steps are performed:

- a) Clear the SPIx interrupt flags/events in the respective IFSx register.

- b) Write the SPIx interrupt priority and sub-priority bits in the respective IPCx register.

- c) Set the SPIx interrupt enable bits in the respective IECx register.

- 6. Write the Baud Rate register, SPIxBRGL.

- 7. Clear the SPIROV bit (SPIxSTATL<6>).

- 8. Write the desired settings to the SPIxCON1L register with MSTEN (SPIxCON1L<5>) = 1.

- Enable SPI operation by setting the SPIEN bit (SPIxCON1L<15>).

- 10. Write the data to be transmitted to the SPIxBUFL and SPIxBUFH registers. Transmission (and reception) will start as soon as data is written to the SPIxBUFL/H registers.

# 17.2 Slave Mode Operation

The following steps are used to set up the SPIx module for the Slave mode of operation:

- 1. If using interrupts, disable the SPIx interrupts in the respective IECx register.

- 2. Stop and reset the SPIx module by clearing the SPIEN bit.

- 3. Clear the receive buffer.

- Clear the ENHBUF bit (SPIxCON1L<0>) if using Standard Buffer mode or set the bit if using Enhanced Buffer mode.

- 5. If using interrupts, the following additional steps are performed:

- a) Clear the SPIx interrupt flags/events in the respective IFSx register.

- b) Write the SPIx interrupt priority and subpriority bits in the respective IPCx register.

- c) Set the SPIx interrupt enable bits in the respective IECx register.

- 6. Clear the SPIROV bit (SPIxSTATL<6>).

- 7. Write the desired settings to the SPIxCON1L register with MSTEN (SPIxCON1L<5>) = 0.

- Enable SPI operation by setting the SPIEN bit (SPIxCON1L<15>).

- 9. Transmission (and reception) will start as soon as the master provides the serial clock.

The following additional features are provided in Slave mode:

- Slave Select Synchronization:

- The SSx pin allows a Synchronous Slave mode. If the SSEN bit (SPIxCON1L<7>) is set, transmission and reception are enabled in Slave mode only if the SSx pin is driven to a low state. The port output or other peripheral outputs must not be driven in order to allow the SSx pin to function as an input. If the SSEN bit is set and the SSx pin is driven high, the SDOx pin is no longer driven and will tri-state, even if the module is in the middle of a transmission. An aborted transmission will be tried again the next time the SSx pin is driven low using the data held in the SPIxTXB register. If the SSEN bit is not set, the SSx pin does not affect the module operation in Slave mode.

- SPITBE Status Flag Operation: The SPITBE bit (SPIxSTATL<3>) has a different function in the Slave mode of operation. The following describes the function of SPITBE for various settings of the Slave mode of operation:

- If SSEN (SPIxCON1L<7>) is cleared, the SPITBE bit is cleared when SPIxBUF is loaded by the user code. It is set when the module transfers SPIxTXB to SPIxTXSR. This is similar to the SPITBE bit function in Master mode.

- If SSEN is set, SPITBE is cleared when SPIxBUF is loaded by the user code. However, it is set only when the SPIx module completes data transmission. A transmission will be aborted when the SSx pin goes high and may be retried at a later time. So, each data word is held in SPIxTXB until all bits are transmitted to the receiver.

# 17.4 SPI Control Registers

#### REGISTER 17-1: SPIx CON1L: SPIx CONTROL REGISTER 1 LOW

| R/W-0                                                              | U-0                                                                                                                                               | R/W-0                                     | R/W-0         | R/W-0                   | R/W-0                   | R/W-0          | R/W-0              |  |  |  |  |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------|-------------------------|-------------------------|----------------|--------------------|--|--|--|--|

| SPIEN                                                              | —                                                                                                                                                 | SPISIDL                                   | DISSDO        | MODE32 <sup>(1,4)</sup> | MODE16 <sup>(1,4)</sup> | SMP            | CKE <sup>(1)</sup> |  |  |  |  |

| bit 15                                                             |                                                                                                                                                   |                                           |               | L.                      |                         |                | bit 8              |  |  |  |  |

|                                                                    |                                                                                                                                                   |                                           |               |                         |                         |                |                    |  |  |  |  |

| R/W-0                                                              | R/W-0                                                                                                                                             | R/W-0                                     | R/W-0         | R/W-0                   | R/W-0                   | R/W-0          | R/W-0              |  |  |  |  |

| SSEN <sup>(2)</sup>                                                | CKP                                                                                                                                               | MSTEN                                     | DISSDI        | DISSCK                  | MCLKEN <sup>(3)</sup>   | SPIFE          | ENHBUF             |  |  |  |  |

| bit 7                                                              |                                                                                                                                                   |                                           |               |                         |                         |                | bit C              |  |  |  |  |

|                                                                    |                                                                                                                                                   |                                           |               |                         |                         |                |                    |  |  |  |  |

| Legend:                                                            |                                                                                                                                                   |                                           |               |                         |                         |                |                    |  |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                                                                                                                                   |                                           |               |                         |                         |                |                    |  |  |  |  |

| -n = Value a                                                       | t POR                                                                                                                                             | '1' = Bit is set                          |               | '0' = Bit is clea       | ared                    | x = Bit is unk | nown               |  |  |  |  |

| bit 15                                                             | SPIEN: SPIX C                                                                                                                                     | )n hit                                    |               |                         |                         |                |                    |  |  |  |  |

| DIC 15                                                             |                                                                                                                                                   |                                           |               |                         |                         |                |                    |  |  |  |  |

|                                                                    | <ul> <li>1 = Enables module</li> <li>0 = Turns off and resets module, disables clocks, disables interrupt event generation, allows SFR</li> </ul> |                                           |               |                         |                         |                |                    |  |  |  |  |

|                                                                    | modificatio                                                                                                                                       |                                           | ,             |                         | ·                       | 0              |                    |  |  |  |  |

| bit 14                                                             | Unimplement                                                                                                                                       | Unimplemented: Read as '0'                |               |                         |                         |                |                    |  |  |  |  |

| bit 13                                                             | SPISIDL: SPIX                                                                                                                                     | Stop in Idle M                            | lode bit      |                         |                         |                |                    |  |  |  |  |

|                                                                    |                                                                                                                                                   | 1 = Halts in CPU Idle mode                |               |                         |                         |                |                    |  |  |  |  |

|                                                                    |                                                                                                                                                   | 0 = Continues to operate in CPU Idle mode |               |                         |                         |                |                    |  |  |  |  |

| bit 12                                                             | DISSDO: Disa                                                                                                                                      |                                           |               |                         |                         |                |                    |  |  |  |  |

|                                                                    | 1 = SDOx pin i<br>0 = SDOx pin i                                                                                                                  |                                           |               | oin is controlled       | by the port funct       | tion           |                    |  |  |  |  |

| bit 11-10                                                          | MODE<32,16>                                                                                                                                       | -                                         |               | 4)                      |                         |                |                    |  |  |  |  |

|                                                                    | _AUDEN = 0:                                                                                                                                       |                                           |               |                         |                         |                |                    |  |  |  |  |

|                                                                    | MODE32                                                                                                                                            | MODE16                                    | COMMUNI       | CATION                  |                         |                |                    |  |  |  |  |

|                                                                    | 1                                                                                                                                                 | x                                         | 32-Bit        |                         |                         |                |                    |  |  |  |  |

|                                                                    | 0                                                                                                                                                 | 1                                         | 16-Bit        |                         |                         |                |                    |  |  |  |  |

|                                                                    | 0<br>AUDEN = 1:                                                                                                                                   | 0                                         | 8-Bit         |                         |                         |                |                    |  |  |  |  |

|                                                                    | MODE32                                                                                                                                            | MODE16                                    | COMMUNI       | CATION                  |                         |                |                    |  |  |  |  |

|                                                                    | 1                                                                                                                                                 | 1                                         |               | a, 32-Bit FIFO, 3       | 2-Bit Channel/6         | 4-Bit Frame    |                    |  |  |  |  |

|                                                                    | 1                                                                                                                                                 | 0                                         |               | a, 32-Bit FIFO, 3       |                         |                |                    |  |  |  |  |

|                                                                    | 0                                                                                                                                                 | 1                                         |               | a, 16-Bit FIFO, 3       |                         |                |                    |  |  |  |  |

|                                                                    | 0                                                                                                                                                 | 0                                         | 16-Bit Data   | a, 16-Bit FIFO, 1       | 6-Bit Channel/3         | 2-Bit Frame    |                    |  |  |  |  |

| bit 9                                                              | SMP: SPIx Da                                                                                                                                      | ta Input Samp                             | le Phase bit  |                         |                         |                |                    |  |  |  |  |

|                                                                    | Master Mode:                                                                                                                                      |                                           |               |                         |                         |                |                    |  |  |  |  |

|                                                                    | 1 = Input data                                                                                                                                    |                                           |               |                         |                         |                |                    |  |  |  |  |

|                                                                    | -                                                                                                                                                 | is sampled at                             |               | data output time        | ;                       |                |                    |  |  |  |  |

|                                                                    | <u>Slave Mode:</u><br>Input data is al                                                                                                            | ways sampled                              | at the middle | e of data output        | time, regardless        | of the SMP     | settina.           |  |  |  |  |

|                                                                    | ·                                                                                                                                                 |                                           |               | •                       |                         |                |                    |  |  |  |  |

|                                                                    | When AUDEN = 1                                                                                                                                    |                                           |               | CKE = 0, regard         | dless of its actua      | al value.      |                    |  |  |  |  |

|                                                                    | Vhen FRMEN = 1                                                                                                                                    |                                           |               | hit - o                 |                         |                |                    |  |  |  |  |

| 3: N                                                               | ICLKEN can only                                                                                                                                   | be written wh                             |               | DII = 0.                |                         |                |                    |  |  |  |  |

4: This channel is not meaningful for DSP/PCM mode as LRC follows the FRMSYPW bit.

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "UART" (DS39708), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins. The UART module includes an IrDA<sup>®</sup> encoder/decoder unit.

The PIC24FJ1024GA610/GB610 family devices are equipped with six UART modules, referred to as UART1, UART2, UART3, UART4, UART5 and UART6.

The primary features of the UARTx modules are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with the UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Range from up to 1 Mbps and Down to 15 Hz at 16 MIPS in 16x mode

- Baud Rates Range from up to 4 Mbps and Down to 61 Hz at 16 MIPS in 4x mode

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Separate Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- Polarity Control for Transmit and Receive Lines

- · Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- Includes DMA Support

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 19-1. The UARTx module consists of these key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

**Note:** Throughout this section, references to register and bit names that may be associated with a specific UART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the Status register for either UART1, UART2, UART3, UART4, UART5 or UART6.

## REGISTER 22-2: RTCCON1H: RTCC CONTROL REGISTER 1 (HIGH)

| R/W-0                                                                                              | R/W-0                                                                                          | U-0              | U-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0         |  |  |  |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------|-----------------|-------------------|------------------|-----------------|---------------|--|--|--|

| ALRMEN                                                                                             | CHIME                                                                                          | _                | _               | AMASK3            | AMASK2           | AMASK1          | AMASK0        |  |  |  |

| bit 15                                                                                             |                                                                                                |                  |                 |                   |                  |                 | bit 8         |  |  |  |

| DAVA                                                                                               | DAMO                                                                                           | DAMA             | DAMA            | DAALO             | DAMO             | DAMA            | DAMA          |  |  |  |

| R/W-0                                                                                              | R/W-0                                                                                          | R/W-0            | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0         |  |  |  |

| ALMRPT7                                                                                            | ALMRPT6                                                                                        | ALMRPT5          | ALMRPT4         | ALMRPT3           | ALMRPT2          | ALMRPT1         | ALMRPT0       |  |  |  |