Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb606-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Pin Diagrams<sup>(1)</sup> (Continued)

| , | 1             | 2        | 3            | 4         | 5         | 6        | 7         | 8         | 9         | 10          | 11          |

|---|---------------|----------|--------------|-----------|-----------|----------|-----------|-----------|-----------|-------------|-------------|

| A | O<br>RE4      | RE3      | <b>R</b> G13 | RE0       | RG0       | RF1      | ⊖<br>N/C  | ⊖<br>N/C  | RD12      | RD2         | RD1         |

| в | O<br>N/C      | RG15     | RE2          | RE1       | O<br>RA7  | RF0      | O<br>VCAP | RD5       | RD3       | O<br>Vss    | O<br>RC14   |

| с | RE6           | O<br>VDD | RG12         | RG14      | O<br>RA6  | O<br>N/C | O<br>RD7  | RD4       | O<br>N/C  | O<br>RC13   | RD11        |

| D | RC1           | RE7      | RE5          | O<br>N/C  | O<br>N/C  | O<br>N/C | O<br>RD6  | RD13      | RD0       | O<br>N/C    | RD10        |

| E | O<br>RC4      | RC3      | O<br>RG6     | RC2       | ⊖<br>N/C  | RG1      | O<br>N/C  | RA15      | RD8       | RD9         | RA14        |

| F | MCLR          | O<br>RG8 | O<br>RG9     | O<br>RG7  | O<br>Vss  | O<br>N/C | O<br>N/C  |           | O<br>RC12 | O<br>Vss    | O<br>RC15   |

| G | RE8           | O<br>RE9 | RA0          | O<br>N/C  |           | O<br>Vss | O<br>Vss  | O<br>N/C  | RA5       | RA3         | RA4         |

| н | O<br>RB5      | O<br>RB4 | O<br>N/C     | O<br>N/C  | O<br>N/C  |          | ⊖<br>N/C  | UBUS/RF7  | UUSB3V3   | O<br>D+/RG2 | RA2         |

| J | O<br>RB3      | O<br>RB2 | O<br>RB7     | O<br>AVDD | O<br>RB11 | RA1      | O<br>RB12 | ⊖<br>N/C  | O<br>N/C  | RF8         | O<br>D-/RG3 |

| к | O<br>RB1      | O<br>RB0 | O<br>RA10    | O<br>RB8  | ∩<br>N/C  | RF12     | O<br>RB14 |           | RD15      | RF3         | RF2         |

| L | O<br>RB6      | O<br>RA9 | O<br>AVss    | O<br>RB9  | O<br>RB10 | RF13     | O<br>RB13 | O<br>RB15 | RD14      | RF4         | RF5         |

|   | ole 7 for a c |          |              |           |           |          |           |           |           |             |             |

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                 |                                                                |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|----------------------------------------------------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer | Description                                                    |

| PMA8            | 32                                  | 32                               | 50                               | 50                               | L11                     | L11                     | I/O | DIG/<br>ST/TTL  | Parallel Master Port Address<br>(Demultiplexed Master mode) or |

| PMA9            | 31                                  | 31                               | 49                               | 49                               | L10                     | L10                     | I/O | DIG/<br>ST/TTL  | Address/Data (Multiplexed<br>Master modes)                     |

| PMA10           | 28                                  | 28                               | 42                               | 42                               | L7                      | L7                      | I/O | DIG/<br>ST/TTL  |                                                                |

| PMA11           | 27                                  | 27                               | 41                               | 41                               | J7                      | J7                      | I/O | DIG/<br>ST/TTL  |                                                                |

| PMA12           | 24                                  | 24                               | 35                               | 35                               | J5                      | J5                      | I/O | DIG/<br>ST/TTL  |                                                                |

| PMA13           | 23                                  | 23                               | 34                               | 34                               | L5                      | L5                      | I/O | DIG/<br>ST/TTL  |                                                                |

| PMA16           | _                                   | _                                | 95                               | 95                               | C4                      | C4                      | 0   | DIG             |                                                                |

| PMA17           | _                                   |                                  | 92                               | 92                               | B5                      | B5                      | 0   | DIG             |                                                                |

| PMA18           | _                                   |                                  | 40                               | 40                               | K6                      | K6                      | 0   | DIG             |                                                                |

| PMA19           | —                                   |                                  | 19                               | 19                               | G2                      | G2                      | 0   | DIG             |                                                                |

| PMA2/<br>PMALU  | 8                                   | 8                                | 14                               | 14                               | F3                      | F3                      | 0   | DIG             | Parallel Master Port Address<2>/<br>Address Latch Upper        |

| PMA3            | 6                                   | 6                                | 12                               | 12                               | F2                      | F2                      | 0   | DIG             | Parallel Master Port Address                                   |

| PMA4            | 5                                   | 5                                | 11                               | 11                               | F4                      | F4                      | 0   | DIG             |                                                                |

| PMA5            | 4                                   | 4                                | 10                               | 10                               | E3                      | E3                      | 0   | DIG             |                                                                |

| PMA20           | _                                   | _                                | 59                               | 59                               | G10                     | G10                     | 0   | DIG             | Parallel Master Port Address                                   |

| PMA21           | —                                   | _                                | 60                               | 60                               | G11                     | G11                     | 0   | DIG             | (Demultiplexed Master mode) or                                 |

| PMA22           | _                                   | —                                | 66                               | 66                               | E11                     | E11                     | 0   | DIG             | Address/Data (Multiplexed<br>Master modes)                     |

| PMACK1          | 50                                  | 50                               | 77                               | 77                               | A10                     | A10                     | I   | ST/TTL          | Parallel Master Port<br>Acknowledge Input 1                    |

| PMACK2          | 43                                  | 43                               | 69                               | 69                               | E10                     | E10                     | I   | ST/TTL          | Parallel Master Port<br>Acknowledge Input 2                    |

| PMBE0           | 51                                  | 51                               | 78                               | 78                               | B9                      | B9                      | 0   | DIG             | Parallel Master Port Byte<br>Enable 0 Strobe                   |

| PMBE1           | -                                   | —                                | 67                               | 67                               | E8                      | E8                      | 0   | DIG             | Parallel Master Port Byte<br>Enable 1 Strobe                   |

| PMCS1           | _                                   | —                                | 18                               | 18                               | G1                      | G1                      | 0   | DIG             | Parallel Master Port Chip<br>Select 1 Strobe                   |

| PMCS2           | _                                   | —                                | 9                                | 9                                | E1                      | E1                      | 0   | DIG             | Parallel Master Port Chip<br>Select 2 Strobe                   |

| PMPCS1          | -                                   | —                                | 58                               | 58                               | H11                     | H11                     | 0   | DIG             | Parallel Master Port Chip<br>Select 1                          |

### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend:

TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

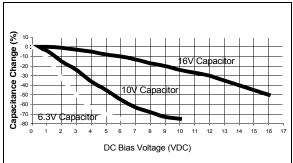

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R) or -20%/ +80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE CHARACTERISTICS

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at a minimum of 16V for the 1.8V core voltage. Suggested capacitors are shown in Table 2-1.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming (ICSP) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" pins (i.e., PGECx/PGEDx), programmed into the device, match the physical connections for the ICSP to the Microchip debugger/ emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 31.0 "Development Support"**.

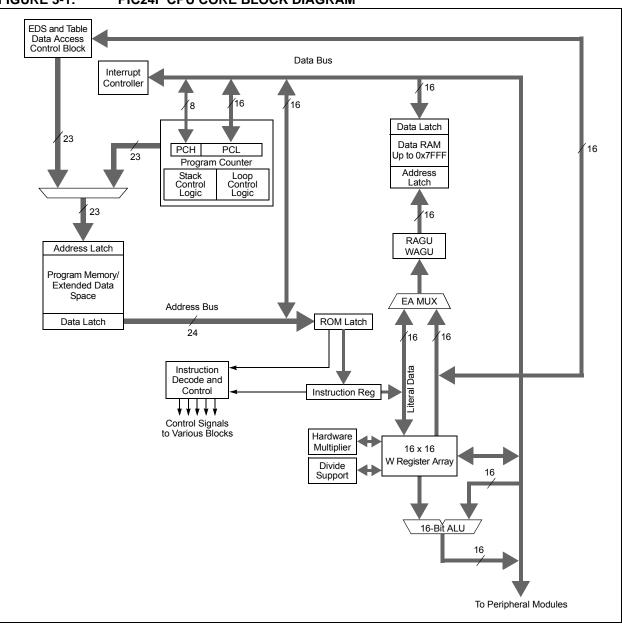

### FIGURE 3-1: PIC24F CPU CORE BLOCK DIAGRAM

| TABLE 3-1: CI | PU CORE REGISTERS |

|---------------|-------------------|

|---------------|-------------------|

| Register(s) Name | Description                        |  |  |  |

|------------------|------------------------------------|--|--|--|

| W0 through W15   | Working Register Array             |  |  |  |

| PC               | 23-Bit Program Counter             |  |  |  |

| SR               | ALU STATUS Register                |  |  |  |

| SPLIM            | Stack Pointer Limit Value Register |  |  |  |

| TBLPAG           | Table Memory Page Address Register |  |  |  |

| RCOUNT           | REPEAT Loop Counter Register       |  |  |  |

| CORCON           | CPU Control Register               |  |  |  |

| DISICNT          | Disable Interrupt Count Register   |  |  |  |

| DSRPAG           | Data Space Read Page Register      |  |  |  |

| DSWPAG           | Data Space Write Page Register     |  |  |  |

### 6.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 128 instructions or 384 bytes. RTSP allows the user to erase blocks of eight rows (1024 instructions) at a time and to program one row at a time. It is also possible to program two instruction word blocks.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 3072 bytes and 384 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 128 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused address should be programmed with FFFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set the Table Pointer to point to the programming latches, do a series of TBLWT instructions to load the buffers and set the NVMADRU/NVMADR registers to point to the destination. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing is *not* recommended.

All of the Table Write operations are single-word writes (2 instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

### 6.3 JTAG Operation

The PIC24F family supports JTAG boundary scan. Boundary scan can improve the manufacturing process by verifying pin to PCB connectivity.

### 6.4 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an onboard bootloader, known as the Program Executive (PE), to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 6.5 Control Registers

There are four SFRs used to read and write the program Flash memory: NVMCON, NVMADRU, NVMADR and NVMKEY.

The NVMCON register (Register 6-1) controls which blocks are to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 6.6 "Programming Operations"** for further details.

The NVMADRU/NVMADR registers contain the upper byte and lower word of the destination of the NVM write or erase operation. Some operations (chip erase, Inactive Partition erase) operate on fixed locations and do not require an address value.

### 6.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

In Dual Partition mode, programming or erasing the Inactive Partition will not stall the processor; the code in the Active Partition will still execute during the programming operation.

It is important to mask interrupts for a minimum of 5 instruction cycles during Flash programming. This can be done in Assembly using the DISI instruction (see Example 6-1).

| DANCO           |                                                                                                                                                          |                                                         |                 |                              |                  |                 |          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------|------------------------------|------------------|-----------------|----------|

| R/W-0           | U-0                                                                                                                                                      | R/W-0                                                   | R/W-0           | R/W-0                        | U-0              | R/W-0           | R-0      |

| ROEN            |                                                                                                                                                          | ROSIDL                                                  | ROOUT           | ROSLP                        | —                | ROSWEN          | ROACTIVE |

| bit 15          |                                                                                                                                                          |                                                         |                 |                              |                  |                 | bit 8    |

| U-0             | U-0                                                                                                                                                      | U-0                                                     | U-0             | R/W-0                        | R/W-0            | R/W-0           | R/W-0    |

| _               |                                                                                                                                                          | _                                                       | _               | ROSEL3                       | ROSEL2           | ROSEL1          | ROSEL0   |

| bit 7           |                                                                                                                                                          |                                                         |                 |                              |                  |                 | bit 0    |

|                 |                                                                                                                                                          |                                                         |                 |                              |                  |                 |          |

| Legend:         |                                                                                                                                                          |                                                         |                 |                              |                  |                 |          |

| R = Readable    | bit                                                                                                                                                      | W = Writable                                            | bit             | U = Unimplen                 | nented bit, read | 1 as '0'        |          |

| -n = Value at F | POR                                                                                                                                                      | '1' = Bit is set                                        |                 | '0' = Bit is clea            | ared             | x = Bit is unkr | nown     |

| bit 15          | 1 = Reference                                                                                                                                            | ence Oscillator<br>e Oscillator mo<br>e Oscillator is d | dule is enabled | 1                            |                  |                 |          |

| bit 14          | Unimplement                                                                                                                                              | ted: Read as '                                          | 0'              |                              |                  |                 |          |

| bit 13          | ROSIDL: REF                                                                                                                                              | O Stop in Idle                                          | Mode bit        |                              |                  |                 |          |

|                 |                                                                                                                                                          | ues module op<br>s module opera                         |                 | levice enters Idl<br>de      | e mode           |                 |          |

| bit 12          | ROOUT: Refe                                                                                                                                              | erence Clock O                                          | utput Enable b  | bit                          |                  |                 |          |

|                 |                                                                                                                                                          | e clock is driver<br>e clock is not d                   |                 | •                            |                  |                 |          |

| bit 11          | ROSLP: Refe                                                                                                                                              | rence Oscillato                                         | or Output Stop  | in Sleep bit                 |                  |                 |          |

|                 |                                                                                                                                                          | e Oscillator cor<br>e Oscillator is d                   |                 |                              |                  |                 |          |

| bit 10          | Unimplement                                                                                                                                              | ted: Read as '                                          | 0'              |                              |                  |                 |          |

| bit 9           | ROSWEN: Re                                                                                                                                               | eference Clock                                          | RODIV<14:0>     | /ROTRIM<0:8>                 | Switch Enable    | e bit           |          |

|                 |                                                                                                                                                          | ock divider; cloo<br>der switch has                     |                 | ching is currently           | y in progress    |                 |          |

| bit 8           | ROACTIVE: F                                                                                                                                              | Reference Cloc                                          | k Request Sta   | tus bit                      |                  |                 |          |

|                 |                                                                                                                                                          |                                                         |                 | not change the pdate the REF |                  | s)              |          |

| bit 7-4         | Unimplement                                                                                                                                              | ted: Read as '                                          | 0'              |                              |                  |                 |          |

| bit 3-0         | ROSEL<3:0>                                                                                                                                               | : Reference Cl                                          | ock Source Se   | elect bits                   |                  |                 |          |

|                 | 1111-1001 =<br>1000 = REFI<br>0111 = Reser<br>0110 = PLL (<br>0101 = SOSC<br>0100 = LPRC<br>0011 = FRC<br>0010 = POSC<br>0001 = Peript<br>0000 = Oscilla | pin<br>ved<br>4/6/8x or 96 MI<br>C<br>heral clock       | Hz)             |                              |                  |                 |          |

### REGISTER 9-8: REFOCONL: REFERENCE OSCILLATOR CONTROL REGISTER LOW

| REGISTER 16-7: | CCPxSTATL: CCPx STATUS REGISTER LOW |  |

|----------------|-------------------------------------|--|

|                |                                     |  |

| U-0          | U-0          | U-0                                    | U-0             | U-0                       | W-0                | U-0             | U-0                |

|--------------|--------------|----------------------------------------|-----------------|---------------------------|--------------------|-----------------|--------------------|

| _            |              |                                        |                 | _                         | ICGARM             |                 | _                  |

| bit 15       |              |                                        |                 |                           |                    |                 | bit 8              |

|              | 14/4 0       | 14/4 0                                 | <b>D</b> /0.0   | <b>D</b> (0, 0            | <b>D</b> /0.0      | <b>D</b> /0.0   | <b>D</b> /0.0      |

| R-0          | W1-0         | W1-0                                   | R/C-0           | R/C-0                     | R/C-0              | R/C-0           | R/C-0              |

| CCPTRIG      | TRSET        | TRCLR                                  | ASEVT           | SCEVT                     | ICDIS              | ICOV            | ICBNE              |

| bit 7        |              |                                        |                 |                           |                    |                 | bit                |

| Legend:      |              | C = Clearable                          | e bit           | W = Writable              | bit                |                 |                    |

| R = Readab   | le bit       | W1 = Write '1                          | ' Only bit      | U = Unimpler              | mented bit, read   | as '0'          |                    |

| -n = Value a | It POR       | '1' = Bit is set                       | :               | '0' = Bit is cle          | ared               | x = Bit is unkr | nown               |

|              |              |                                        |                 |                           |                    |                 |                    |

| bit 15-11    | Unimplemer   | nted: Read as '                        | 0'              |                           |                    |                 |                    |

| bit 10       |              | put Capture Ga                         |                 |                           |                    |                 |                    |

|              |              | ' to this location = 01 or 10; real    |                 | nput Capture              | x module for a     | one-shot gatin  | ig event whe       |

| bit 9-8      | Unimplemer   | nted: Read as '                        | 0'              |                           |                    |                 |                    |

| bit 7        | CCPTRIG: C   | CPx Trigger St                         | atus bit        |                           |                    |                 |                    |

|              |              | as been triggere                       |                 | 0                         |                    |                 |                    |

|              |              | as not been trig                       | -               | eld in Reset              |                    |                 |                    |

| bit 6        |              | Px Trigger Set F                       | -               |                           |                    |                 | ( - 1)             |

| L:1 F        |              |                                        |                 | when TRIGEN               | I = 1 (location al | ways reads as   | ·0 <sup>·</sup> ). |

| bit 5        |              | Px Trigger Clea                        | •               | Triggor whon <sup>-</sup> |                    | ation alwaya r  |                    |

| bit 4        |              | Px Auto-Shutdo                         |                 |                           | TRIGEN = 1 (loc    | alion always r  | eaus as $0$ ).     |

| DIL 4        |              |                                        |                 |                           | n the shutdown s   |                 |                    |

|              |              | utputs operate r                       |                 |                           |                    | hate            |                    |

| bit 3        | SCEVT: Sing  | gle Edge Compa                         | are Event Statu | s bit                     |                    |                 |                    |

|              | 0            | edge compare                           |                 |                           |                    |                 |                    |

|              | -            | edge compare                           |                 | occurred                  |                    |                 |                    |

| bit 2        | -            | Capture x Disa                         |                 |                           |                    |                 |                    |

|              |              | ו Input Capture<br>ו Input Capture     | • • •           | •                         | ate a capture eve  | ent             |                    |

| bit 1        |              | Capture x Buffe                        |                 | -                         | event              |                 |                    |

|              |              | ut Capture x FIF                       |                 |                           |                    |                 |                    |

|              |              | ut Capture x FIF                       |                 |                           |                    |                 |                    |

| bit 0        | ICBNE: Inpu  | t Capture x Buf                        | fer Status bit  |                           |                    |                 |                    |

|              |              |                                        |                 |                           |                    |                 |                    |

| bit o        | 1 = Input Ca | apture x buffer l<br>apture x buffer i | has data availa | ble                       |                    |                 |                    |

### REGISTER 19-5: UxBRG: UARTx BAUD RATE GENERATOR REGISTER

| R/W-0                                                                | R/W-0  | R/W-0                                                    | R/W-0 | R/W-0    | R/W-0   | R/W-0   | R/W-0  |

|----------------------------------------------------------------------|--------|----------------------------------------------------------|-------|----------|---------|---------|--------|

|                                                                      |        |                                                          | BRG   | 6<15:8>  |         |         |        |

| bit 15                                                               |        |                                                          |       |          |         |         | bit 8  |

| R/W-0                                                                | R/W-0  | R/W-0                                                    | R/W-0 | R/W-0    | R/W-0   | R/W-0   | R/W-0  |

| 10.00-0                                                              | 1000-0 | 10,00-0                                                  |       | G<7:0>   | 10.00-0 | 10.00-0 | 1000-0 |

| bit 7                                                                |        |                                                          |       |          |         |         | bit 0  |

| Legend:                                                              |        |                                                          |       |          |         |         |        |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |        |                                                          |       | d as '0' |         |         |        |

| -n = Value at I                                                      | POR    | '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |          | nown    |         |        |

bit 15-0 BRG<15:0>: Baud Rate Divisor bits

### REGISTER 19-6: UxADMD: UARTx ADDRESS DETECT AND MATCH REGISTER

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| ADMMASK7 | ADMMASK6 | ADMMASK5 | ADMMASK4 | ADMMASK3 | ADMMASK2 | ADMMASK1 | ADMMASK0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| ADMADDR7 | ADMADDR6 | ADMADDR5 | ADMADDR4 | ADMADDR3 | ADMADDR2 | ADMADDR1 | ADMADDR0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | ADMMASK<7:0>: ADMADDR<7:0> (UxADMD<7:0>) Masking bits                                                                                                |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | For ADMMASKx:                                                                                                                                        |

|          | 1 = ADMADDRx is used to detect the address match                                                                                                     |

|          | 0 = ADMADDRx is not used to detect the address match                                                                                                 |

| bit 7-0  | ADMADDR<7:0>: Address Detect Task Off-Load bits                                                                                                      |

|          | Used with the ADMMASK<7:0> bits (UxADMD<15:8> to off-load the task of detecting the address character from the processor during Address Detect mode. |

### 20.7.2 USB INTERRUPT REGISTERS

### REGISTER 20-14: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER (HOST MODE ONLY)

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|--------------|-----|-----|-----|-----|-----|-----|-----|

| —            | —   | —   | —   | —   | —   | —   | —   |

| bit 15 bit 8 |     |     |     |     |     |     |     |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|

| IDIF      | T1MSECIF  | LSTATEIF  | ACTVIF    | SESVDIF   | SESENDIF  | —   | VBUSVDIF  |

| bit 7     |           |           |           |           |           |     | bit 0     |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | K = Write '1' to Clear bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                    |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | IDIF: ID State Change Indicator bit                                                                                                           |

|          | 1 = Change in ID state is detected                                                                                                            |

|          | 0 = No ID state change is detected                                                                                                            |

| bit 6    | T1MSECIF: 1 Millisecond Timer bit                                                                                                             |

|          | 1 = The 1 millisecond timer has expired                                                                                                       |

|          | 0 = The 1 millisecond timer has not expired                                                                                                   |

| bit 5    | LSTATEIF: Line State Stable Indicator bit                                                                                                     |

|          | <ul> <li>1 = USB line state (as defined by the SE0 and JSTATE bits) has been stable for 1 ms, but different from<br/>the last time</li> </ul> |

|          | 0 = USB line state has not been stable for 1 ms                                                                                               |

| bit 4    | ACTVIF: Bus Activity Indicator bit                                                                                                            |

|          | 1 = Activity on the D+/D- lines or VBUS is detected                                                                                           |

|          | 0 = No activity on the D+/D- lines or VBUS is detected                                                                                        |

| bit 3    | SESVDIF: Session Valid Change Indicator bit                                                                                                   |

|          | 1 = VBUS has crossed VA_SESS_END (as defined in the <i>"USB 2.0 Specification"</i> ) <sup>(1)</sup><br>0 = VBUS has not crossed VA_SESS_END   |

| bit 2    | SESENDIF: B-Device VBUS Change Indicator bit                                                                                                  |

|          | 1 = VBUS change on B-device is detected; VBUS has crossed VB_SESS_END (as defined in the "USB 2.0<br>Specification") <sup>(1)</sup>           |

|          | 0 = VBUS has not crossed VB_SESS_END                                                                                                          |

| bit 1    | Unimplemented: Read as '0'                                                                                                                    |

| bit 0    | VBUSVDIF: A-Device VBUS Change Indicator bit                                                                                                  |

|          | 1 = VBUS change on A-device is detected; VBUS has crossed VA_VBUS_VLD (as defined in the "USB 2.0<br>Specification") <sup>(1)</sup>           |

|          | 0 = No VBUS change on A-device is detected                                                                                                    |

| Note 1:  | VBUS threshold crossings may either be rising or falling.                                                                                     |

|          |                                                                                                                                               |

**Note:** Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits, at the moment of the write, to become cleared.

### REGISTER 21-8: PMSTAT: EPMP STATUS REGISTER (SLAVE MODE ONLY)

| R-0, HSC        | R/W-0, HS                                                                             | U-0                                                      | U-0                           | R-0, HSC                            | R-0, HSC            | R-0, HSC            | R-0, HSC            |  |

|-----------------|---------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|-------------------------------------|---------------------|---------------------|---------------------|--|

| IBF             | IBOV                                                                                  | —                                                        | —                             | IB3F <sup>(1)</sup>                 | IB2F <sup>(1)</sup> | IB1F <sup>(1)</sup> | IB0F <sup>(1)</sup> |  |

| bit 15          |                                                                                       |                                                          |                               |                                     |                     | •                   | bit 8               |  |

| <b>D</b> ( 1100 |                                                                                       |                                                          |                               | <u> </u>                            |                     | <b>D</b> ( 1100     |                     |  |

| R-1, HSC        | R/W-0, HS                                                                             | U-0                                                      | U-0                           | R-1, HSC                            | R-1, HSC            | R-1, HSC            | R-1, HSC            |  |

| OBE             | OBUF                                                                                  | —                                                        | _                             | OB3E                                | OB2E                | OB1E                | OB0E                |  |

| bit 7           |                                                                                       |                                                          |                               |                                     |                     |                     | bit                 |  |

| Legend:         |                                                                                       | HS = Hardware                                            | e Settable bit                | HSC = Hardw                         | are Settable/C      | learable bit        |                     |  |

| R = Readable    | e bit                                                                                 | W = Writable b                                           | oit                           | U = Unimplem                        | nented bit, read    | l as '0'            |                     |  |

| -n = Value at   | POR                                                                                   | '1' = Bit is set                                         |                               | '0' = Bit is clea                   | ared                | x = Bit is unkr     | nown                |  |

| bit 14          | <ul> <li>0 = Some or</li> <li><b>IBOV:</b> Input B</li> <li>1 = A write at</li> </ul> | Buffer Overflow Stempt to a full li                      | le Input Buffer<br>Status bit | registers are er<br>ccurred (must b |                     | oftware)            |                     |  |

|                 | 0 = No overfl                                                                         |                                                          |                               |                                     |                     |                     |                     |  |

| bit 13-12       | •                                                                                     | ted: Read as '0                                          |                               |                                     |                     |                     |                     |  |

| bit 11-8        | 1 = Input buff                                                                        | put Buffer x Sta<br>fer contains unr<br>fer does not cor | ead data (read                | ling the buffer w                   | ill clear this bit  | )                   |                     |  |

| bit 7           | 1 = All readal                                                                        | Buffer Empty Sible Output Buffer all of the readal       | er registers are              | empty<br>fer registers are          | full                |                     |                     |  |

| bit 6           | OBUF: Output Buffer Underflow Status bit                                              |                                                          |                               |                                     |                     |                     |                     |  |

|                 | 1 = A read or<br>0 = No under                                                         |                                                          | empty Output                  | Buffer register                     | (must be cleare     | ed in software)     |                     |  |

| bit 5-4         | Unimplemen                                                                            | ted: Read as '0                                          | ,                             |                                     |                     |                     |                     |  |

| h:+ 0 0         | -                                                                                     | Output Buffer >                                          |                               | ' bit                               |                     |                     |                     |  |

| bit 3-0         |                                                                                       | •                                                        |                               |                                     | clear this bit)     |                     |                     |  |

**Note 1:** Even though an individual bit represents the byte in the buffer, the bits corresponding to the word (Byte 0 and 1, or Byte 2 and 3) get cleared, even on byte reading.

| U-0                                | U-0     | R/W-0   | R/W-0   | R/W-0                              | R/W-0   | R/W-0           | R/W-0   |  |

|------------------------------------|---------|---------|---------|------------------------------------|---------|-----------------|---------|--|

| —                                  | _       | HRTEN1  | HRTEN0  | HRONE3                             | HRONE2  | HRONE1          | HRONE0  |  |

| bit 15 bit 8                       |         |         |         |                                    |         |                 |         |  |

|                                    |         |         |         |                                    |         |                 |         |  |

| U-0                                | R/W-0   | R/W-0   | R/W-0   | R/W-0                              | R/W-0   | R/W-0           | R/W-0   |  |

| —                                  | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3                            | MINONE2 | MINONE1         | MINONE0 |  |

| bit 7                              |         |         |         |                                    |         |                 | bit 0   |  |

|                                    |         |         |         |                                    |         |                 |         |  |

| Legend:                            |         |         |         |                                    |         |                 |         |  |

| R = Readable bit W = Writable bit  |         |         | oit     | U = Unimplemented bit, read as '0' |         |                 |         |  |

| -n = Value at POR '1' = Bit is set |         |         |         | '0' = Bit is clea                  | ared    | x = Bit is unkn | iown    |  |

### REGISTER 22-16: TSATIMEH: RTCC TIMESTAMP A TIME REGISTER (HIGH)<sup>(1)</sup>

| bit 15-14 | Unimplemented: Read as '0'                                         |

|-----------|--------------------------------------------------------------------|

| bit 13-12 | HRTEN<1:0>: Binary Coded Decimal Value of Hours '10' Digit bits    |

|           | Contains a value from 0 to 2.                                      |

| bit 11-8  | HRONE<3:0>: Binary Coded Decimal Value of Hours '1' Digit bits     |

|           | Contains a value from 0 to 9.                                      |

| bit 7     | Unimplemented: Read as '0'                                         |

| bit 6-4   | MINTEN<2:0>: Binary Coded Decimal Value of Minutes '10' Digit bits |

|           | Contains a value from 0 to 5.                                      |

| bit 3-0   | MINONE<3:0>: Binary Coded Decimal Value of Minutes '1' Digit bits  |

|           | Contains a value from 0 to 9.                                      |

**Note 1:** If TSAEN = 0, bits<15:0> can be used for persistence storage throughout a non-Power-on Reset (MCLR, WDT, etc.).

### 23.1 User Interface

### 23.1.1 POLYNOMIAL INTERFACE

The CRC module can be programmed for CRC polynomials of up to the  $32^{nd}$  order, using up to 32 bits.

Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation. Functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing the bit disables the XOR.

For example, consider two CRC polynomials, one a 16-bit and the other a 32-bit equation.

### EQUATION 23-1: 16-BIT, 32-BIT CRC POLYNOMIALS

### X16 + X12 + X5 + 1

and

$\begin{array}{c} X32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 + \\ X8 + X7 + X5 + X4 + X2 + X + 1 \end{array}$

To program these polynomials into the CRC generator, set the register bits, as shown in Table 23-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The '0' bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length 32, it is assumed that the  $32^{nd}$  bit will be used. Therefore, the X<31:1> bits do not have the  $32^{nd}$  bit.

### 23.1.2 DATA INTERFACE

The module incorporates a FIFO that works with a variable data width. Input data width can be configured to any value between 1 and 32 bits using the DWIDTH<4:0> bits (CRCCON2<12:8>). When the data width is greater than 15, the FIFO is 4 words deep. When the DWIDTHx bits are between 15 and 8, the FIFO is 8 words deep. When the DWIDTHx bits are less than 8, the FIFO is 16 words deep.

The data for which the CRC is to be calculated must first be written into the FIFO. Even if the data width is less than 8, the smallest data element that can be written into the FIFO is 1 byte. For example, if the DWIDTHx bits are 5, then the size of the data is DWIDTH<4:0> + 1 or 6. The data is written as a whole byte; the two unused upper bits are ignored by the module.

Once data is written into the MSb of the CRCDAT registers (that is, the MSb as defined by the data width), the value of the VWORD<4:0> bits (CRCCON1<12:8>) increments by one. For example, if the DWIDTHx bits are 24, the VWORDx bits will increment when bit 7 of CRCDATH is written. Therefore, CRCDATL must always be written to before CRCDATH.

The CRC engine starts shifting data when the CRCGO bit (CRCCON1<4>) is set and the value of the VWORDx bits is greater than zero.

Each word is copied out of the FIFO into a buffer register, which decrements the VWORDx bits. The data is then shifted out of the buffer. The CRC engine continues shifting at a rate of two bits per instruction cycle, until the VWORDx bits reach zero. This means that for a given data width, it takes half that number of instructions for each word to complete the calculation. For example, it takes 16 cycles to calculate the CRC for a single word of 32-bit data.

When the VWORDx bits reach the maximum value for the configured value of the DWIDTHx bits (4, 8 or 16), the CRCFUL bit (CRCCON1<7>) becomes set. When the VWORDx bits reach zero, the CRCMPT bit (CRCCON1<6>) becomes set. The FIFO is emptied and the VWORD<4:0> bits are set to '00000' whenever CRCEN is '0'.

At least one instruction cycle must pass after a write to CRCWDAT before a read of the VWORDx bits is done.

### TABLE 23-1: CRC SETUP EXAMPLES FOR 16 AND 32-BIT POLYNOMIALS

| CRC Control Bits | Bit Values          |                     |  |  |  |  |

|------------------|---------------------|---------------------|--|--|--|--|

|                  | 16-Bit Polynomial   | 32-Bit Polynomial   |  |  |  |  |

| PLEN<4:0>        | 01111               | 11111               |  |  |  |  |

| X<31:16>         | 0000 0000 0000 0001 | 0000 0100 1100 0001 |  |  |  |  |

| X<15:1>          | 0001 0000 0010 000  | 0001 1101 1011 011  |  |  |  |  |

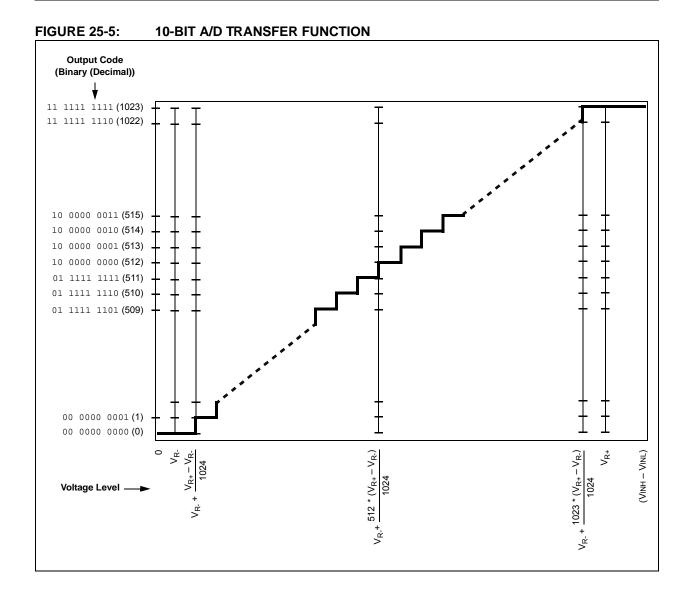

| AC CH        | ARACTER               | Standard Operating Conditions: 2.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |           |     |      |       |                            |  |  |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|------|-------|----------------------------|--|--|

| Param<br>No. | Symbol                | Characteristic                                                                                                                                  | Min.      | Тур | Max. | Units | Conditions                 |  |  |

|              | Clock Parameters      |                                                                                                                                                 |           |     |      |       |                            |  |  |

| AD50         | TAD                   | A/D Clock Period                                                                                                                                | 278       |     | _    | ns    |                            |  |  |

| AD51         | tRC                   | A/D Internal RC Oscillator Period                                                                                                               | _         | 250 | _    | ns    |                            |  |  |

|              |                       | Conve                                                                                                                                           | ersion Ra | te  |      |       |                            |  |  |

| AD55         | tCONV                 | SAR Conversion Time, 12-Bit Mode                                                                                                                |           | 14  |      | Tad   |                            |  |  |

| AD55A        |                       | SAR Conversion Time, 10-Bit Mode                                                                                                                | _         | 12  | _    | Tad   |                            |  |  |

| AD56         | FCNV                  | Throughput Rate                                                                                                                                 | _         |     | 200  | ksps  | AVDD > 2.7V <sup>(2)</sup> |  |  |

| AD57         | <b>t</b> SAMP         | Sample Time                                                                                                                                     |           | 1   |      | TAD   | (Note 1)                   |  |  |

|              | Clock Synchronization |                                                                                                                                                 |           |     |      |       |                            |  |  |

| AD61         | tpss                  | Sample Start Delay from Setting<br>Sample bit (SAMP)                                                                                            | 1.5       |     | 2.5  | Tad   |                            |  |  |

## TABLE 33-26: A/D CONVERSION TIMING REQUIREMENTS<sup>(1)</sup>

**Note 1:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

2: Throughput rate is based on AD55 + AD57 + AD61 and the period of TAD.

### 34.0 PACKAGING INFORMATION

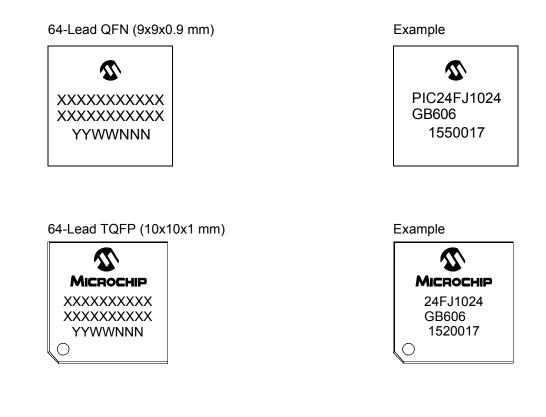

### 34.1 Package Marking Information

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|-------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carrie                      | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                            |

© 2015-2016 Microchip Technology Inc.

# Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

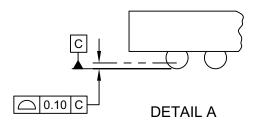

### 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

DETAIL 1

|                          | MILLIMETERS |           |           |      |  |

|--------------------------|-------------|-----------|-----------|------|--|

| Dimension                | Limits      | MIN       | NOM       | MAX  |  |

| Number of Leads          | N           |           | 64        |      |  |

| Lead Pitch               | е           |           | 0.50 BSC  |      |  |

| Overall Height           | Α           | -         | -         | 1.20 |  |

| Molded Package Thickness | A2          | 0.95      | 1.00      | 1.05 |  |

| Standoff                 | A1          | 0.05      | -         | 0.15 |  |

| Foot Length              | L           | 0.45      | 0.60      | 0.75 |  |

| Footprint                | L1 1.00 REF |           |           |      |  |

| Foot Angle               | ø           | 0°        | 3.5°      | 7°   |  |

| Overall Width            | E           |           | 12.00 BSC |      |  |

| Overall Length           | D           | 12.00 BSC |           |      |  |

| Molded Package Width     | E1          | 10.00 BSC |           |      |  |

| Molded Package Length    | D1          |           | 10.00 BSC |      |  |

| Lead Thickness           | С           | 0.09      | -         | 0.20 |  |

| Lead Width               | b           | 0.17      | 0.22      | 0.27 |  |

| Mold Draft Angle Top     | α           | 11°       | 12°       | 13°  |  |

| Mold Draft Angle Bottom  | β           | 11°       | 12°       | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085C Sheet 2 of 2

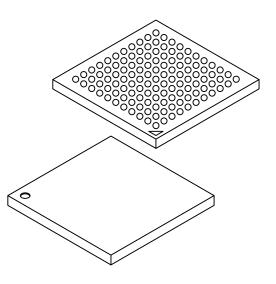

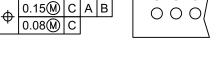

# 121-Ball Plastic Thin Profile Fine Pitch Ball Grid Array (BG) - 10x10x1.10 mm Body [TFBGA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

NX Øb

000

0 O C

|                    | Units    |                | MILLIMETERS |      |  |

|--------------------|----------|----------------|-------------|------|--|

| Dimensio           | n Limits | MIN            | NOM         | MAX  |  |

| Number of Contacts | Ν        |                | 121         |      |  |

| Contact Pitch      | е        | 0.80 BSC       |             |      |  |

| Overall Height     | Α        | 1.00 1.10 1.20 |             | 1.20 |  |

| Ball Height        | A1       | 0.25           | 0.30        | 0.35 |  |

| Overall Width      | E        | 10.00 BSC      |             |      |  |

| Array Width        | E1       | 8.00 BSC       |             |      |  |

| Overall Length     | D        | 10.00 BSC      |             |      |  |

| Array Length       | D1       | 8.00 BSC       |             |      |  |

| Contact Diameter   | b        | 0.35 0.40 0.45 |             |      |  |

Notes:

- 1. Ball A1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 3. The outer rows and colums of balls are located with respect to datums A and B.

- 4. Ball interface to package body: 0.37mm nominal diameter.

Microchip Technology Drawing C04-148 Rev F Sheet 2 of 2

# PIC24FJ1024GA610/GB610 FAMILY

### F

| Flash Program Memory    | 89 |

|-------------------------|----|

| and Table Instructions  |    |

| Control Registers       | 90 |

| Double-Word Programming | 95 |

| Enhanced ICSP Operation | 90 |

| JTAG Operation          | 90 |

| Operations              | 90 |

| Programming Algorithm   | 93 |

| RTSP Operation          |    |

### G

| Guidelines for Getting Started with 16-Bit MCUs | 41 |

|-------------------------------------------------|----|

| Analog/Digital Pins Configuration During ICSP   | 46 |

| External Oscillator Pins                        | 45 |

| ICSP Pins                                       | 44 |

| Master Clear (MCLR) Pin                         | 42 |

| Power Supply Pins                               | 42 |

| Unused I/Os                                     | 46 |

| Voltage Regulator Pin (VCAP)                    | 43 |

### Н

| High/Low-Voltage Detect (HLVD)     | . 387 |

|------------------------------------|-------|

| High/Low-Voltage Detect. See HLVD. |       |

### I

| I/O Ports 1                                       | 49              |

|---------------------------------------------------|-----------------|

| Analog Port Pins Configuration (ANSx) 1           | 50              |

| Configuring Analog/Digital Function of I/O Pins 1 | 150             |

| Input Voltage Levels for Port/Pin Tolerated       |                 |

| Description Input 1                               | 50              |

| Open-Drain Configuration1                         |                 |

| Parallel (PIO)1                                   |                 |

| Peripheral Pin Select1                            |                 |

| Write/Read Timing1                                |                 |

| I <sup>2</sup> C                                  |                 |

| Clock Rates2                                      | 249             |

| Communicating as Master in Single                 |                 |

| Master Environment2                               | 247             |

| Reserved Addresses2                               | 249             |

| Setting Baud Rate as Bus Master2                  | 249             |

| Slave Address Masking                             |                 |

| In-Circuit Debugger                               | 106             |

| Input Capture                                     |                 |

| 32-Bit Cascaded Mode1                             | 194             |

| Operations1                                       | 194             |

| Synchronous and Trigger Modes1                    | 193             |

| Input Capture with Dedicated Timers1              | 93              |

| Instruction Set                                   |                 |

| Overview                                          | 113             |

| Summary4                                          | ¥11             |

| Symbols Used in Opcode Descriptions4              | <b>1</b> 12     |

| Interfacing Program and Data Memory Spaces        | 76              |

| Inter-Integrated Circuit. See I <sup>2</sup> C.   |                 |

| Internet Address4                                 | <del>1</del> 63 |

| Interrupt Controller 1                            |                 |

| Alternate Interrupt Vector Table 1                | 03              |

| Control and Status Registers1                     | 08              |

| Interrupt Vector Details 1                        |                 |

| Interrupt Vector Table (IVT) 1                    | 103             |

| Reset Sequence1                                   | 103             |

| Resources1                                        | 108             |

| Trap Vectors 1                                    | 104             |

| Vector Tables1                                    | 04              |

| Interrupt-on-Change (IOC) 1                       | 154             |

| JTAG Interface                  | 406 |

|---------------------------------|-----|

| к                               |     |

| Key Features                    | 389 |

| L                               |     |

| Low-Voltage/Retention Regulator | 403 |

### Μ

J

| Memory Organization                         | 53  |

|---------------------------------------------|-----|

| Program Memory Space                        | 53  |

| Microchip Internet Web Site                 | 463 |

| MPLAB ASM30 Assembler, Linker, Librarian    | 408 |

| MPLAB Integrated Development                |     |

| Environment Software                        | 407 |

| MPLAB PM3 Device Programmer                 | 409 |

| MPLAB REAL ICE In-Circuit Emulator System   | 409 |

| MPLINK Object Linker/MPLIB Object Librarian | 408 |

|                                             |     |

### Ν

| Near Data Space 6 | 60 |

|-------------------|----|

|-------------------|----|

### Ο

| -                                            |     |

|----------------------------------------------|-----|

| On-Chip Voltage Regulator                    | 403 |

| POR                                          | 403 |

| Standby Mode                                 | 403 |

| Oscillator Configuration                     | 115 |

| Clock Switching                              | 126 |

| Sequence                                     | 126 |

| Configuration Bit Values for Clock Selection | 117 |

| Control Registers                            | 117 |

| FRC Self-Tuning                              | 127 |

| Initial Configuration on POR                 | 116 |

| USB Operation                                | 128 |

| Special Considerations                       | 130 |

| Output Compare with Dedicated Timers         | 199 |

| Operating Modes                              | 199 |

| 32-Bit Cascaded Mode                         | 199 |

| Synchronous and Trigger Modes                | 199 |

| Operations                                   | 200 |

### Ρ

| Packaging                      |     |

|--------------------------------|-----|

| Details                        | 443 |

| Marking                        | 441 |

| Peripheral Enable Bits         | 139 |

| Peripheral Module Disable Bits | 139 |

| Peripheral Pin Select (PPS)    | 159 |

| Available Peripherals and Pins | 159 |

| Configuration Control          | 162 |

| Considerations for Selection   | 163 |

| Control Registers              | 164 |

| Input Mapping                  | 160 |

| Mapping Exceptions             | 162 |

| Output Mapping                 | 161 |

| Peripheral Priority            | 159 |

| Selectable Input Sources       | 160 |

| Selectable Output Sources      | 161 |

| PIC24FJ1024GA610/GB610 Family  |     |

| Pinout Descriptions            | 26  |

|                                |     |