Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb606-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

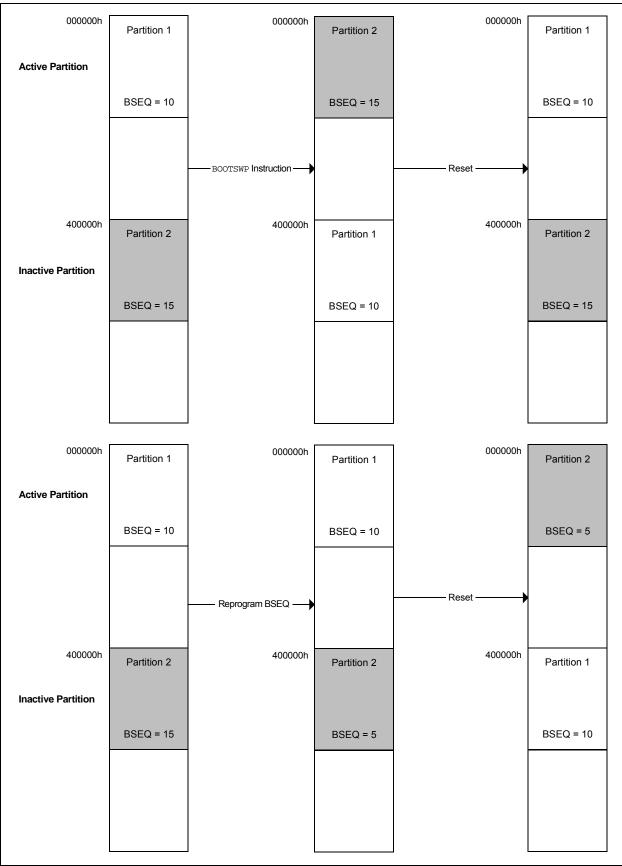

#### FIGURE 4-2: RELATIONSHIP BETWEEN PARTITIONS 1/2 AND ACTIVE/INACTIVE PARTITIONS

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCUs and improve Data Space memory usage efficiency, the PIC24F instruction set supports both word and byte operations. As a consequence of byte accessibility, all EA calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode, [Ws++], will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word, which contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The Most Significant Byte (MSB) is not modified.

A Sign-Extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions operate only on words.

#### 4.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. The remainder of the Data Space is addressable indirectly. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing with a 16-bit address field.

#### 4.2.4 SPECIAL FUNCTION REGISTER (SFR) SPACE

The first 2 Kbytes of the Near Data Space, from 0000h to 07FFh, are primarily occupied with Special Function Registers (SFRs). These are used by the PIC24F core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A diagram of the SFR space, showing where the SFRs are actually implemented, is shown in Table 4-3. Each implemented area indicates a 32-byte region where at least one address is implemented as an SFR. A complete list of implemented SFRs, including their addresses, is shown in Tables 4-3 through 4-11.

|      | _        |                      |      |      |        |      | SFR S | pace Ad | Idress |      |        |                |      |      |      |       |

|------|----------|----------------------|------|------|--------|------|-------|---------|--------|------|--------|----------------|------|------|------|-------|

|      | xx00     | xx10                 | xx20 | xx30 | xx40   | xx50 | xx60  | xx70    | xx80   | xx90 | xxA0   | xxB0           | xxC0 | xxD0 | xxE0 | xxF0  |

| 000h | 00h Core |                      |      |      |        |      |       |         |        |      |        |                |      |      |      |       |

| 100h | OSC      | Reset <sup>(1)</sup> |      | EPMP |        | CRC  | REFO  | PN      | ИD     |      | Timers |                | CTM  |      | RTCC |       |

| 200h |          | Capture              |      |      | Compar | е    |       |         |        | MC   | CP     |                |      |      | Comp | ANCFG |

| 300h |          |                      |      |      | SCCP   |      |       |         |        |      |        | ι              | JART |      |      | SPI   |

| 400h |          |                      | SPI  |      |        | —    |       | CLC     |        |      | I      | <sup>2</sup> C |      |      | DMA  |       |

| 500h | D        | MA                   |      | _    |        |      |       | US      | SB     |      |        | _              |      | _    | _    | _     |

| 600h | _        | _                    |      | _    |        |      |       |         |        | I/C  | )      |                |      |      |      | _     |

| 700h | _        |                      |      | A/D  |        |      | _     | _       | _      |      |        |                | PPS  |      |      |       |

#### TABLE 4-3: IMPLEMENTED REGIONS OF SFR DATA SPACE

Legend: - = No implemented SFRs in this block

Note 1: Includes HLVD control.

| File Name                        | Address         | All Resets | File Name                                          | Address | All Resets |  |  |

|----------------------------------|-----------------|------------|----------------------------------------------------|---------|------------|--|--|

| MULTIPLE OUTPUT (<br>(CONTINUED) | CAPTURE/COMPARE | /PWM       | MULTIPLE OUTPUT CAPTURE/COMPARE/PWM<br>(CONTINUED) |         |            |  |  |

| CCP2RAL                          | 02A8            | 0000       | CCP3PRL                                            | 02C8    | FFFF       |  |  |

| CCP2RAH                          | 02AA            | 0000       | CCP3PRH                                            | 02CA    | FFFF       |  |  |

| CCP2RBL                          | 02AC            | 0000       | CCP3RAL                                            | 02CC    | 0000       |  |  |

| CCP2RBH                          | 02AE            | 0000       | CCP3RAH                                            | 02CE    | 0000       |  |  |

| CCP2BUFL                         | 02B0            | 0000       | CCP3RBL                                            | 02D0    | 0000       |  |  |

| CCP2BUFH                         | 02B2            | 0000       | CCP3RBH                                            | 02D2    | 0000       |  |  |

| CCP3CON1L                        | 02B4            | 0000       | CCP3BUFL                                           | 02D4    | 0000       |  |  |

| CCP3CON1H                        | 02B6            | 0000       | CCP3BUFH                                           | 02D6    | 0000       |  |  |

| CCP3CON2L                        | 02B8            | 0000       | COMPARATORS                                        |         |            |  |  |

| CCP3CON2H                        | 02BA            | 0100       | CMSTAT                                             | 02E6    | 0000       |  |  |

| CCP3CON3L                        | 02BC            | 0000       | CVRCON                                             | 02E8    | 00xx       |  |  |

| CCP3CON3H                        | 02BE            | 0000       | CM1CON                                             | 02EA    | 0000       |  |  |

| CCP3STATL                        | 02C0            | 00x0       | CM2CON                                             | 02EC    | 0000       |  |  |

| CCP3STATH                        | 02C2            | 0000       | CM3CON                                             | 02EE    | 0000       |  |  |

| CCP3TMRL                         | O2C4            | 0000       | ANALOG CONFIGU                                     | RATION  |            |  |  |

| CCP3TMRH                         | 02C6            | 0000       | ANCFG                                              | 02F4    | 0000       |  |  |

#### TABLE 4-6: SFR MAP: 0200h BLOCK (CONTINUED)

$\label{eq:legend: Legend: Legend: Legend: Legend: Legend: Constant of the set of the s$

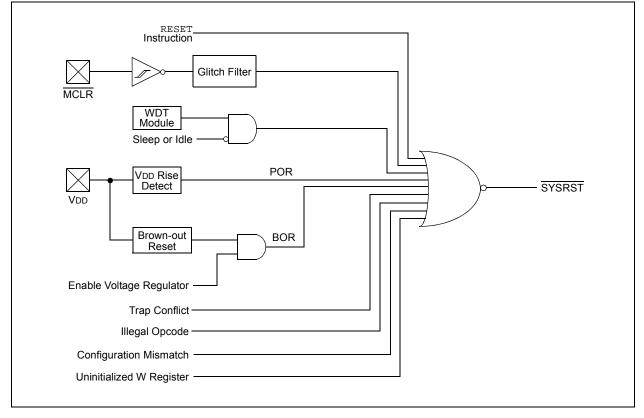

### 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Reset" (DS39712), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Note: Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A POR will clear all bits, except for the BOR and POR (RCON<1:0>) bits, which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register values after a device Reset will be meaningful.

#### FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

© 2015-2016 Microchip Technology Inc.

### 9.1 CPU Clocking Scheme

The system clock source can be provided by one of five sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

- Digitally Controlled Oscillator (DCO)

- · Fast Internal RC (FRC) Oscillator

- · Low-Power Internal RC (LPRC) Oscillator

The Primary Oscillator and FRC sources have the option of using the internal PLL block, which can generate a 96 MHz USB module PLL clock, or a 4x, 6x or 8x PLL clock. If the 96 MHz PLL is used, the PLL clocks can then be postscaled, if necessary, and used as the system clock. If the 4x, 6x or 8x PLL multipliers are selected, the PLL clock can be used directly as a system clock. Refer to Section 9.6 "PLL Oscillator Modes and USB Operation" for additional information. The internal FRC provides an 8 MHz clock source.

Each clock source (POSC, SOSC, DCO, FRC and LPRC) can be used as an input to an additional divider, which can then be used to produce a divided clock source for use as a system clock (OSCFDIV).

The selected clock source is used to generate the processor and peripheral clock sources. The processor clock source is divided by two to produce the internal instruction cycle clock, FCY. In this document, the instruction cycle clock is also denoted by FOSC/2. The internal instruction cycle clock, FOSC/2, can be provided on the OSCO I/O pin for some Primary Oscillator configurations.

#### 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (refer to **Section 30.1 "Configuration Bits"** for further details). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a Power-on Reset. The OSCFDIV clock source is the default (unprogrammed) selection; the default input source to the OSCFDIV divider is the FRC clock source. Other oscillators may be chosen by programming these bit locations.

The Configuration bits allow users to choose between the various clock modes shown in Table 9-1.

#### 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (FOSC<7:6>) are used to jointly configure device clock switching and the Fail-Safe Clock Monitor (FSCM). Clock switching is enabled only when FCKSM<1> is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00').

#### **REGISTER 11-1:** ANSA: PORTA ANALOG FUNCTION SELECTION REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1                     | R/W-1 | U-0   |

|--------|-----|-----|-----|-----|---------------------------|-------|-------|

| —      | —   | —   | —   | —   | ANSA<10:9> <sup>(1)</sup> |       | —     |

| bit 15 |     |     |     |     |                           |       | bit 8 |

| R/W-1 | R/W-1    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|----------|-----|-----|-----|-----|-----|-------|

| ANSA< | :7:6>(1) | —   | —   | —   | —   | —   | —     |

| bit 7 |          |     |     |     |     |     | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ıd as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-11 | Unimplemented: Read as '0'                                                                                                                                   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10-9  | ANSA<10:9>: PORTA Analog Function Selection bits <sup>(1)</sup>                                                                                              |

|           | <ul> <li>1 = Pin is configured in Analog mode; I/O port read is disabled</li> <li>0 = Pin is configured in Digital mode; I/O port read is enabled</li> </ul> |

| bit 8     | Unimplemented: Read as '0'                                                                                                                                   |

| bit 7-6   | ANSA<7:6>: PORTA Analog Function Selection bits <sup>(1)</sup>                                                                                               |

|           | <ul> <li>1 = Pin is configured in Analog mode; I/O port read is disabled</li> <li>0 = Pin is configured in Digital mode; I/O port read is enabled</li> </ul> |

| bit 5-0   | Unimplemented: Read as '0'                                                                                                                                   |

**Note 1:** ANSA<10:9,7> bits are not available on 64-pin devices.

#### REGISTER 11-2: ANSB: PORTB ANALOG FUNCTION SELECTION REGISTER

| R/W-1                              | R/W-1 | R/W-1          | R/W-1                                 | R/W-1        | R/W-1           | R/W-1     | R/W-1 |

|------------------------------------|-------|----------------|---------------------------------------|--------------|-----------------|-----------|-------|

|                                    |       |                | ANS                                   | B<15:8>      |                 |           |       |

| bit 15                             |       |                |                                       |              |                 |           | bit 8 |

|                                    |       |                |                                       |              |                 |           |       |

| R/W-1                              | R/W-1 | R/W-1          | R/W-1                                 | R/W-1        | R/W-1           | R/W-1     | R/W-1 |

|                                    |       |                | ANS                                   | B<7:0>       |                 |           |       |

| bit 7                              |       |                |                                       |              |                 |           | bit 0 |

|                                    |       |                |                                       |              |                 |           |       |

| Legend:                            |       |                |                                       |              |                 |           |       |

| R = Readable                       | bit   | W = Writable b | oit                                   | U = Unimplem | nented bit, rea | id as '0' |       |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cleared x = Bit is unkno |              |                 | nown      |       |

bit 15-0 ANSB<15:0>: PORTB Analog Function Selection bits

1 = Pin is configured in Analog mode; I/O port read is disabled

0 = Pin is configured in Digital mode; I/O port read is enabled

| U-0    | U-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|--------|-----|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

|        | —   | RP5R5 <sup>(1)</sup> | RP5R4 <sup>(1)</sup> | RP5R3 <sup>(1)</sup> | RP5R2 <sup>(1)</sup> | RP5R1 <sup>(1)</sup> | RP5R0 <sup>(1)</sup> |

| bit 15 |     |                      |                      |                      |                      |                      | bit 8                |

|        |     |                      |                      |                      |                      |                      |                      |

| U-0    | U-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

| _      | —   | RP4R5                | RP4R4                | RP4R3                | RP4R2                | RP4R1                | RP4R0                |

| bit 7  |     |                      |                      |                      |                      |                      | bit 0                |

#### REGISTER 11-38: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP5R<5:0>: RP5 Output Pin Mapping bits <sup>(1)</sup>                                                |

|           | Peripheral Output Number n is assigned to pin, RP5 (see Table 11-4 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | RP4R<5:0>: RP4 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP4 (see Table 11-4 for peripheral function numbers). |

**Note 1:** This pin is not available on 64-pin devices.

#### REGISTER 11-39: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| _      | _   | RP7R5 | RP7R4 | RP7R3 | RP7R2 | RP7R1 | RP7R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP6R5 | RP6R4 | RP6R3 | RP6R2 | RP6R1 | RP6R0 |

| bit 7  | •   |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP7R<5:0>: RP7 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP7 (see Table 11-4 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP6R<5:0>:** RP6 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP6 (see Table 11-4 for peripheral function numbers).

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

|        | —   | —   | —   | —   | —   | —   | IC32  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0       | R/W-0, HS | U-0 | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-1    |

|-------------|-----------|-----|----------|----------|----------|----------|----------|

| ICTRIG      | TRIGSTAT  | —   | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7 bit ( |           |     |          |          |          |          |          |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-9 | Unimplemented: Read as '0'                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8    | IC32: Cascade Two Input Capture Modules Enable bit (32-bit operation)                                                                                                                     |

|          | <ul> <li>1 = ICx and ICy operate in cascade as a 32-bit module (this bit must be set in both modules)</li> <li>0 = ICx functions independently as a 16-bit module</li> </ul>              |

| bit 7    | ICTRIG: Input Capture x Sync/Trigger Select bit                                                                                                                                           |

|          | <ul> <li>1 = Triggers ICx from the source designated by the SYNCSELx bits</li> <li>0 = Synchronizes ICx with the source designated by the SYNCSELx bits</li> </ul>                        |

| bit 6    | TRIGSTAT: Timer Trigger Status bit                                                                                                                                                        |

|          | <ul> <li>1 = Timer source has been triggered and is running (set in hardware, can be set in software)</li> <li>0 = Timer source has not been triggered and is being held clear</li> </ul> |

| bit 5    | Unimplemented: Read as '0'                                                                                                                                                                |

- **Note 1:** Use these inputs as Trigger sources only and never as Sync sources.

- 2: Never use an Input Capture x module as its own Trigger source by selecting this mode.

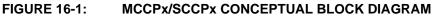

### 16.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the MCCP/SCCP modules, refer to the "dsPIC33/PIC24 Family Reference Manual", "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS33035A), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

PIC24FJ1024GA610/GB610 family devices include several Capture/Compare/PWM/Timer base modules, which provide the functionality of three different peripherals of earlier PIC24F devices. The module can operate in one of three major modes:

- · General Purpose Timer

- Input Capture

- Output Compare/PWM

The module is provided in two different forms, distinguished by the number of PWM outputs that the module can generate. Single Capture/Compare/PWM (SCCPs) output modules provide only one PWM output. Multiple Capture/Compare/PWM (MCCPs) output modules can provide up to six outputs and an extended range of power control features, depending on the pin count of the particular device. All other features of the modules are identical. The SCCPx and MCCPx modules can be operated only in one of the three major modes at any time. The other modes are not available unless the module is reconfigured for the new mode.

A conceptual block diagram for the module is shown in Figure 16-1. All three modules share a time base generator and a common Timer register pair (CCPxTMRH/L); other shared hardware components are added as a particular mode requires.

Each module has a total of 8 control and status registers:

- CCPxCON1L (Register 16-1)

- CCPxCON1H (Register 16-2)

- CCPxCON2L (Register 16-3)

- CCPxCON2H (Register 16-4)

- CCPxCON3L (Register 16-5)

- CCPxCON3H (Register 16-6)

- CCPxSTATL (Register 16-7)

- CCPxSTATH (Register 16-8)

Each module also includes 8 buffer/counter registers that serve as Timer Value registers or data holding buffers:

- CCPxTMRH/CCPxTMRL (Timer High/Low Counters)

- CCPxPRH/CCPxPRL (Timer Period High/Low)

- CCPxRA (Primary Output Compare Data Buffer)

- CCPxRB (Secondary Output Compare Data Buffer)

- CCPxBUFH/CCPxBUFL (Input Capture High/Low Buffers)

## 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC24FJ1024GA610/GB610 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Serial Peripheral Interface (SPI) with Audio Codec Support" (DS70005136), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces. All devices in the PIC24FJ1024GA610/GB610 family include three SPI modules.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through a FIFO buffer. The FIFO level depends on the configured mode.

Variable length data can be transmitted and received from 2 to 32 bits.

| Note: | Do not perform Read-Modify-Write opera-      |

|-------|----------------------------------------------|

|       | tions (such as bit-oriented instructions) on |

|       | the SPIxBUF register in either Standard or   |

|       | Enhanced Buffer mode.                        |

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The module also supports Audio modes. Four different Audio modes are available.

- I<sup>2</sup>S mode

- Left Justified

- · Right Justified

- PCM/DSP

In each of these modes, the serial clock is free-running and audio data is always transferred.

If an audio protocol data transfer takes place between two devices, then usually one device is the master and the other is the slave. However, audio data can be transferred between two slaves. Because the audio protocols require free-running clocks, the master can be a third party controller. In either case, the master generates two free-running clocks: SCKx and LRC (Left, Right Channel Clock/SSx/FSYNC). The SPI serial interface consists of four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

The SPI module has the ability to generate three interrupts reflecting the events that occur during the data communication. The following types of interrupts can be generated:

- 1. Receive interrupts are signalled by SPIxRXIF. This event occurs when:

- RX watermark interrupt

- SPIROV = 1

- SPIRBF = 1

- SPIRBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 2. Transmit interrupts are signalled by SPIxTXIF. This event occurs when:

- TX watermark interrupt

- SPITUR = 1

- SPITBF = 1

- SPITBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 3. General interrupts are signalled by SPIxIF. This event occurs when

- FRMERR = 1

- SPIBUSY = 1

- SRMT = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

A block diagram of the module in Enhanced Buffer mode is shown in Figure 17-1.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1, SPI2 or SPI3. Special Function Registers will follow a similar notation. For example, SPIxCON1 and SPIxCON2 refer to the control registers for any of the three SPI modules.

# 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70000195), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Inter-Integrated Circuit (I<sup>2</sup>C) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, display drivers, A/D Converters, etc.

The I<sup>2</sup>C module supports these features:

- Independent Master and Slave Logic

- 7-Bit and 10-Bit Device Addresses

- General Call Address as Defined in the l<sup>2</sup>C Protocol

- Clock Stretching to Provide Delays for the Processor to Respond to a Slave Data Request

- Both 100 kHz and 400 kHz Bus Specifications

- Configurable Address Masking

- Multi-Master modes to Prevent Loss of Messages

in Arbitration

- Bus Repeater mode, Allowing the Acceptance of All Messages as a Slave, Regardless of the Address

- Automatic SCL

- A block diagram of the module is shown in Figure 18-1.

# 18.1 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communications protocol for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDAx and SCLx.

- 2. Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Repeat Steps 4 and 5 until all data bytes are sent.

- 8. Assert a Repeated Start condition on SDAx and SCLx.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDAx and SCLx.

#### REGISTER 20-6: U1STAT: USB STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R-0, HSC            | U-0 | U-0   |

|----------|----------|----------|----------|----------|---------------------|-----|-------|

| ENDPT3   | ENDPT2   | ENDPT1   | ENDPT0   | DIR      | PPBI <sup>(1)</sup> | —   | —     |

| bit 7    |          |          |          |          |                     |     | bit 0 |

| Legend:           | U = Unimplemented bit, read | d as '0'                  |                    |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | HSC = Hardware Settable/C | Clearable bit      |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

| bit 7-4 | <b>ENDPT&lt;3:0&gt;:</b> Number of the Last Endpoint Activity bits (Represents the number of the BDT updated by the last USB transfer.)<br>1111 = Endpoint 15<br>1110 = Endpoint 14 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                                                                   |

|         | •                                                                                                                                                                                   |

|         | 0001 = Endpoint 1                                                                                                                                                                   |

|         | 0000 = Endpoint 0                                                                                                                                                                   |

| bit 3   | DIR: Last BD Direction Indicator bit                                                                                                                                                |

|         | 1 = The last transaction was a transmit transfer (TX)                                                                                                                               |

|         | 0 = The last transaction was a receive transfer (RX)                                                                                                                                |

| bit 2   | PPBI: Ping-Pong BD Pointer Indicator bit <sup>(1)</sup>                                                                                                                             |

|         | 1 = The last transaction was to the odd BD bank                                                                                                                                     |

|         | 0 = The last transaction was to the even BD bank                                                                                                                                    |

| bit 1-0 | Unimplemented: Read as '0'                                                                                                                                                          |

**Note 1:** This bit is only valid for endpoints with available even and odd BD registers.

# PIC24FJ1024GA610/GB610 FAMILY

| U-0          | U-0                                                                                                                                     | U-0                                                                                                                                                                   | U-0             | U-0               | U-0               | U-0             | U-0      |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-------------------|-----------------|----------|--|--|--|

|              | _                                                                                                                                       | _                                                                                                                                                                     |                 |                   | —                 | _               | _        |  |  |  |

| bit 15       |                                                                                                                                         |                                                                                                                                                                       |                 |                   |                   |                 | bit 8    |  |  |  |

|              |                                                                                                                                         |                                                                                                                                                                       |                 |                   |                   |                 |          |  |  |  |

| R/W-0        | R/W-0                                                                                                                                   | R/W-0                                                                                                                                                                 | R/W-0           | R/W-0             | R/W-0             | R/W-0           | R/W-0    |  |  |  |

| STALLIE      | ATTACHIE <sup>(1)</sup>                                                                                                                 | RESUMEIE                                                                                                                                                              | IDLEIE          | TRNIE             | SOFIE             | UERRIE          | URSTIE   |  |  |  |

|              |                                                                                                                                         |                                                                                                                                                                       |                 |                   |                   |                 | DETACHIE |  |  |  |

| bit 7        |                                                                                                                                         |                                                                                                                                                                       |                 |                   |                   |                 | bit (    |  |  |  |

|              |                                                                                                                                         |                                                                                                                                                                       |                 |                   |                   |                 |          |  |  |  |

| Legend:      | la hit                                                                                                                                  |                                                                                                                                                                       | :.              |                   | antad bit was     |                 |          |  |  |  |

| R = Readab   |                                                                                                                                         | W = Writable b                                                                                                                                                        | IC              | U = Unimplem      |                   |                 |          |  |  |  |

| -n = Value a | TPOR                                                                                                                                    | '1' = Bit is set                                                                                                                                                      |                 | '0' = Bit is clea | ared              | x = Bit is unkr | nown     |  |  |  |

| bit 6        | 0 = Interrupt i<br>ATTACHIE: P<br>1 = Interrupt i<br>0 = Interrupt i                                                                    | eripheral Attach<br>is enabled                                                                                                                                        | Interrupt bit   | (Host mode onl    | y) <sup>(1)</sup> |                 |          |  |  |  |

| bit 5        | RESUMEIE: F<br>1 = Interrupt<br>0 = Interrupt                                                                                           |                                                                                                                                                                       | ot bit          |                   |                   |                 |          |  |  |  |

| bit 4        | <b>IDLEIE:</b> Idle [<br>1 = Interrupt ]<br>0 = Interrupt ]                                                                             |                                                                                                                                                                       | bit             |                   |                   |                 |          |  |  |  |

| bit 3        | <ul> <li>TRNIE: Token Processing Complete Interrupt bit</li> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul> |                                                                                                                                                                       |                 |                   |                   |                 |          |  |  |  |

| bit 2        | 1 = Interrupt                                                                                                                           | <ul> <li>0 = Interrupt is disabled</li> <li>SOFIE: Start-of-Frame Token Interrupt bit</li> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul> |                 |                   |                   |                 |          |  |  |  |

| bit 1        | •                                                                                                                                       | B Error Condition                                                                                                                                                     | n Interrupt bit |                   |                   |                 |          |  |  |  |

- 0 = Interrupt is disabled

- bit 0 URSTIE or DETACHIE: USB Reset Interrupt (Device mode) or USB Detach Interrupt (Host mode) Enable bit

- 1 = Interrupt is enabled

- 0 = Interrupt is disabled

- Note 1: This bit is unimplemented in Device mode, read as '0'.

| R/W-0                        | U-0                                                                                                                                                                                      | R/W-0                                                                                                                                                                  | R/W-0                             | R/W-0             | U-0              | R/W-0           | R/W-0 |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------|------------------|-----------------|-------|--|--|--|

| PMPEN                        | _                                                                                                                                                                                        | PSIDL                                                                                                                                                                  | ADRMUX1                           | ADRMUX0           |                  | MODE1           | MODE0 |  |  |  |

| bit 15                       |                                                                                                                                                                                          |                                                                                                                                                                        |                                   |                   |                  |                 | bit 8 |  |  |  |

| R/W-0                        | R/W-0                                                                                                                                                                                    | R/W-0                                                                                                                                                                  | R/W-0                             | U-0               | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| CSF1                         | CSF0                                                                                                                                                                                     | ALP                                                                                                                                                                    | ALMODE                            |                   | BUSKEEP          | IRQM1           | IRQM0 |  |  |  |

| bit 7                        | 0010                                                                                                                                                                                     |                                                                                                                                                                        | TEMODE                            |                   | DOORLEI          | intogini        | bit   |  |  |  |

|                              |                                                                                                                                                                                          |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

| <b>Legend:</b><br>R = Readat | hit                                                                                                                                                                                      | W = Writable                                                                                                                                                           | hit                               | II = I Inimplen   | nented bit, read | l as '0'        |       |  |  |  |

| -n = Value a                 |                                                                                                                                                                                          | '1' = Bit is se                                                                                                                                                        |                                   | '0' = Bit is clea |                  | x = Bit is unkn | iown  |  |  |  |

|                              |                                                                                                                                                                                          |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

| bit 15                       | -                                                                                                                                                                                        | rallel Master Po                                                                                                                                                       | ort Enable bit                    |                   |                  |                 |       |  |  |  |

|                              | 1 = EPMP is<br>0 = EPMP is                                                                                                                                                               |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

| bit 14                       |                                                                                                                                                                                          | nted: Read as                                                                                                                                                          | ʻ∩'                               |                   |                  |                 |       |  |  |  |

| bit 13                       | •                                                                                                                                                                                        |                                                                                                                                                                        |                                   | ode bit           |                  |                 |       |  |  |  |

|                              |                                                                                                                                                                                          | <ul> <li>PSIDL: Parallel Master Port Stop in Idle Mode bit</li> <li>1 = Discontinues module operation when device enters Idle mode</li> </ul>                          |                                   |                   |                  |                 |       |  |  |  |

|                              | 0 = Continues module operation in Idle mode                                                                                                                                              |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

| bit 12-11                    | ADRMUX<1:0>: Address/Data Multiplexing Selection bits                                                                                                                                    |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

|                              | <ul> <li>11 = Lower address bits are multiplexed with data bits using 3 address phases</li> <li>10 = Lower address bits are multiplexed with data bits using 2 address phases</li> </ul> |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

|                              | 10 = Lower address bits are multiplexed with data bits using 2 address phases<br>01 = Lower address bits are multiplexed with data bits using 1 address phase                            |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

|                              |                                                                                                                                                                                          |                                                                                                                                                                        | ear on separate                   |                   |                  |                 |       |  |  |  |

| bit 10                       | Unimpleme                                                                                                                                                                                | nted: Read as                                                                                                                                                          | ʻ0'                               |                   |                  |                 |       |  |  |  |

| bit 9-8                      | MODE<1:0>: Parallel Port Mode Select bits                                                                                                                                                |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

|                              | 11 = Master mode                                                                                                                                                                         |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

|                              |                                                                                                                                                                                          | 10 = Enhanced PSP; pins used are PMRD, PMWR, PMCS, PMD<7:0> and PMA<1:0><br>01 = Buffered PSP; pins used are PMRD, PMWR, PMCS and PMD<7:0>                             |                                   |                   |                  |                 |       |  |  |  |

|                              | 00 = Legacy Parallel Slave Port; pins used are PMRD, PMRD, PMWR, PMCS and PMD<7:0>                                                                                                       |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

| bit 7-6                      | CSF<1:0>: (                                                                                                                                                                              | Chip Select Fur                                                                                                                                                        | iction bits                       |                   |                  |                 |       |  |  |  |

|                              |                                                                                                                                                                                          | 11 = Reserved                                                                                                                                                          |                                   |                   |                  |                 |       |  |  |  |

|                              |                                                                                                                                                                                          | 10 = PMA15 is used for Chip Select 2, PMA14 is used for Chip Select 1<br>01 = PMA15 is used for Chip Select 2, PMCS1 is used for Chip Select 1                         |                                   |                   |                  |                 |       |  |  |  |

|                              | 01 = PMCS1 is used for Chip Select 2, PMCS1 is used for Chip Select 1<br>00 = PMCS2 is used for Chip Select 2, PMCS1 is used for Chip Select 1                                           |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

| bit 5                        | ALP: Addres                                                                                                                                                                              | s Latch Polarit                                                                                                                                                        | y bit                             |                   |                  |                 |       |  |  |  |

|                              | 1 = Active-high (PMALL, PMALH and PMALU)<br>0 = Active-low (PMALL, PMALH and PMALU)                                                                                                      |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

| hit 1                        |                                                                                                                                                                                          | •                                                                                                                                                                      |                                   | _U)               |                  |                 |       |  |  |  |

| bit 4                        | ALMODE: Address Latch Strobe Mode bit<br>1 = Enables "smart" address strobes (each address phase is only present if the current access would                                             |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

|                              |                                                                                                                                                                                          |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

|                              | cause a different address in the latch than the previous address)<br>0 = Disables "smart" address strobes                                                                                |                                                                                                                                                                        |                                   |                   |                  |                 |       |  |  |  |

| bit 3                        | =                                                                                                                                                                                        | nted: Read as                                                                                                                                                          | '0'                               |                   |                  |                 |       |  |  |  |

| bit 2                        |                                                                                                                                                                                          | Bus Keeper bit                                                                                                                                                         |                                   |                   |                  |                 |       |  |  |  |

|                              |                                                                                                                                                                                          | <ul> <li>1 = Data bus keeps its last value when not actively being driven</li> <li>0 = Data bus is in a high-impedance state when not actively being driven</li> </ul> |                                   |                   |                  |                 |       |  |  |  |

| bit 1-0                      |                                                                                                                                                                                          | Interrupt Requ                                                                                                                                                         | -                                 |                   | , 0              |                 |       |  |  |  |

|                              |                                                                                                                                                                                          |                                                                                                                                                                        | when Read Buff<br>peration when F |                   |                  |                 |       |  |  |  |

|                              | 10 = Reserv                                                                                                                                                                              |                                                                                                                                                                        |                                   |                   |                  |                 | J /   |  |  |  |

|                              |                                                                                                                                                                                          |                                                                                                                                                                        | at the end of a i                 | read/write cycle  | e                |                 |       |  |  |  |

|                              |                                                                                                                                                                                          | rrupt is generat                                                                                                                                                       |                                   |                   |                  |                 |       |  |  |  |

#### REGISTER 21-1: PMCON1: EPMP CONTROL REGISTER 1

| U-0                               | U-0     | R/W-0            | R/W-0                              | R/W-0                | R/W-0   | R/W-0              | R/W-0   |

|-----------------------------------|---------|------------------|------------------------------------|----------------------|---------|--------------------|---------|

| —                                 | _       | HRTEN1           | HRTEN0                             | HRONE3               | HRONE2  | HRONE1             | HRONE0  |

| bit 15                            |         |                  |                                    |                      |         |                    | bit 8   |

|                                   |         |                  |                                    |                      |         |                    |         |

| U-0                               | R/W-0   | R/W-0            | R/W-0                              | R/W-0                | R/W-0   | R/W-0              | R/W-0   |

| —                                 | MINTEN2 | MINTEN1          | MINTEN0                            | MINONE3              | MINONE2 | MINONE1            | MINONE0 |

| bit 7                             |         |                  |                                    |                      |         |                    | bit 0   |

|                                   |         |                  |                                    |                      |         |                    |         |

| Legend:                           |         |                  |                                    |                      |         |                    |         |

| R = Readable bit W = Writable bit |         | oit              | U = Unimplemented bit, read as '0' |                      |         |                    |         |

| -n = Value at POR                 |         | '1' = Bit is set |                                    | '0' = Bit is cleared |         | x = Bit is unknown |         |

# REGISTER 22-16: TSATIMEH: RTCC TIMESTAMP A TIME REGISTER (HIGH)<sup>(1)</sup>

| bit 15-14 | Unimplemented: Read as '0'                                         |

|-----------|--------------------------------------------------------------------|

| bit 13-12 | HRTEN<1:0>: Binary Coded Decimal Value of Hours '10' Digit bits    |

|           | Contains a value from 0 to 2.                                      |

| bit 11-8  | HRONE<3:0>: Binary Coded Decimal Value of Hours '1' Digit bits     |

|           | Contains a value from 0 to 9.                                      |

| bit 7     | Unimplemented: Read as '0'                                         |

| bit 6-4   | MINTEN<2:0>: Binary Coded Decimal Value of Minutes '10' Digit bits |

|           | Contains a value from 0 to 5.                                      |

| bit 3-0   | MINONE<3:0>: Binary Coded Decimal Value of Minutes '1' Digit bits  |

|           | Contains a value from 0 to 9.                                      |

**Note 1:** If TSAEN = 0, bits<15:0> can be used for persistence storage throughout a non-Power-on Reset (MCLR, WDT, etc.).

#### REGISTER 24-1: CLCxCONL: CLCx CONTROL REGISTER (LOW) (CONTINUED)

- bit 2-0 MODE<2:0>: CLCx Mode bits

- 111 = Cell is a 1-input transparent latch with S and R

- 110 = Cell is a JK flip-flop with R

- 101 = Cell is a 2-input D flip-flop with R

- 100 = Cell is a 1-input D flip-flop with S and R

- 011 = Cell is an SR latch

- 010 = Cell is a 4-input AND

- 001 = Cell is an OR-XOR

- 000 = Cell is a AND-OR

#### REGISTER 24-2: CLCxCONH: CLCx CONTROL REGISTER (HIGH)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   |     |     |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | G4POL | G3POL | G2POL | G1POL |

| bit 7 |     |     |     |       |       |       | bit 0 |

#### l egend:

| Legenu.           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                                                  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | G4POL: Gate 4 Polarity Control bit                                                                                                                          |

|          | <ul> <li>1 = The output of Channel 4 logic is inverted when applied to the logic cell</li> <li>0 = The output of Channel 4 logic is not inverted</li> </ul> |

| bit 2    | G3POL: Gate 3 Polarity Control bit                                                                                                                          |

|          | <ul><li>1 = The output of Channel 3 logic is inverted when applied to the logic cell</li><li>0 = The output of Channel 3 logic is not inverted</li></ul>    |

| bit 1    | G2POL: Gate 2 Polarity Control bit                                                                                                                          |

|          | <ul> <li>1 = The output of Channel 2 logic is inverted when applied to the logic cell</li> <li>0 = The output of Channel 2 logic is not inverted</li> </ul> |

| bit 0    | G1POL: Gate 1 Polarity Control bit                                                                                                                          |

|          | <ul> <li>1 = The output of Channel 1 logic is inverted when applied to the logic cell</li> <li>0 = The output of Channel 1 logic is not inverted</li> </ul> |

NOTES:

NOTES:

| Configuration         | Single Partition Mode |                 |                         |                 |  |  |  |  |

|-----------------------|-----------------------|-----------------|-------------------------|-----------------|--|--|--|--|

| Registers             | PIC24FJ1024GX6XX      | PIC24FJ512GX6XX | PIC24FJ256GX6XX         | PIC24FJ128GX6XX |  |  |  |  |

| FSEC                  | 0ABF00h               | 055F00h         | 02AF00h                 | 015F00h         |  |  |  |  |

| FBSLIM                | 0ABF10h               | 055F10h         | 02AF10h                 | 015F10h         |  |  |  |  |

| FSIGN                 | 0ABF14h               | 055F14h         | 02AF14h                 | 015F14h         |  |  |  |  |

| FOSCSEL               | 0ABF18h               | 055F18h         | 02AF18h                 | 015F18h         |  |  |  |  |