Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb606t-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.3.3 READING DATA FROM PROGRAM MEMORY USING EDS

The upper 32 Kbytes of Data Space may optionally be mapped into any 16K word page of the program space. This provides transparent access of stored constant data from the Data Space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the Data Space occurs when the MSb of EA is '1' and the DSRPAG<9> is also '1'. The lower 8 bits of DSRPAG are concatenated to the Wn<14:0> bits to form a 23-bit EA to access program memory. The DSRPAG<8> decides which word should be addressed; when the bit is '0', the lower word, and when '1', the upper word of the program memory is accessed.

The entire program memory is divided into 512 EDS pages, from 200h to 3FFh, each consisting of 16K words of data. Pages, 200h to 2FFh, correspond to the lower words of the program memory, while 300h to 3FFh correspond to the upper words of the program memory.

Using this EDS technique, the entire program memory can be accessed. Previously, the access to the upper word of the program memory was not supported. Table 4-15 provides the corresponding 23-bit EDS address for program memory with EDS page and source addresses.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

| DSRPAG<br>(Data Space Read Register) |                |                    | Comment                            |  |

|--------------------------------------|----------------|--------------------|------------------------------------|--|

| 200h                                 |                | 000000h to 007FFEh | Lower words of 4M program          |  |

| •                                    |                | •                  | instructions; (8 Mbytes) for       |  |

| •                                    |                | •                  | read operations only.              |  |

| •                                    |                | •                  |                                    |  |

| 2FFh                                 |                | 7F8000h to 7FFFFEh |                                    |  |

| 300h                                 | 8000h to FFFFh | 000001h to 007FFFh | Upper words of 4M program          |  |

| •                                    |                | •                  | instructions (4 Mbytes remaining;  |  |

| •                                    |                | •                  | 4 Mbytes are phantom bytes) for    |  |

| •                                    |                | •                  | read operations only.              |  |

| 3FFh                                 |                | 7F8001h to 7FFFFFh |                                    |  |

| 000h                                 |                | Invalid Address    | Address error trap. <sup>(1)</sup> |  |

#### TABLE 4-15: EDS PROGRAM ADDRESS WITH DIFFERENT PAGES AND ADDRESSES

**Note 1:** When the source/destination address is above 8000h and DSRPAG/DSWPAG is '0', an address error trap will occur.

#### EXAMPLE 4-3: EDS READ CODE FROM PROGRAM MEMORY IN ASSEMBLY

| ; Set the I | EDS page from where the dat | a to be read                                              |

|-------------|-----------------------------|-----------------------------------------------------------|

| mov         | #0x0202, w0                 |                                                           |

| mov         | w0, DSRPAG                  | ;page 0x202, consisting lower words, is selected for read |

| mov         | #0x000A, w1                 | ;select the location (0x0A) to be read                    |

| bset        | w1, #15                     | ;set the MSB of the base address, enable EDS mode         |

| ;Read a by  | te from the selected locati | on                                                        |

| mov.b       | [w1++], w2                  | ;read Low byte                                            |

| mov.b       | [w1++], w3                  | ;read High byte                                           |

| ;Read a wo  | rd from the selected locati | on                                                        |

| mov         | [w1], w2                    | i                                                         |

| ;Read Doub  | le - word from the selected | location                                                  |

| mov.d       | [w1], w2                    | ;two word read, stored in w2 and w3                       |

# 6.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 128 instructions or 384 bytes. RTSP allows the user to erase blocks of eight rows (1024 instructions) at a time and to program one row at a time. It is also possible to program two instruction word blocks.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 3072 bytes and 384 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 128 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused address should be programmed with FFFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set the Table Pointer to point to the programming latches, do a series of TBLWT instructions to load the buffers and set the NVMADRU/NVMADR registers to point to the destination. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing is *not* recommended.

All of the Table Write operations are single-word writes (2 instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 6.3 JTAG Operation

The PIC24F family supports JTAG boundary scan. Boundary scan can improve the manufacturing process by verifying pin to PCB connectivity.

# 6.4 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an onboard bootloader, known as the Program Executive (PE), to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

#### 6.5 Control Registers

There are four SFRs used to read and write the program Flash memory: NVMCON, NVMADRU, NVMADR and NVMKEY.

The NVMCON register (Register 6-1) controls which blocks are to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 6.6 "Programming Operations"** for further details.

The NVMADRU/NVMADR registers contain the upper byte and lower word of the destination of the NVM write or erase operation. Some operations (chip erase, Inactive Partition erase) operate on fixed locations and do not require an address value.

## 6.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

In Dual Partition mode, programming or erasing the Inactive Partition will not stall the processor; the code in the Active Partition will still execute during the programming operation.

It is important to mask interrupts for a minimum of 5 instruction cycles during Flash programming. This can be done in Assembly using the DISI instruction (see Example 6-1).

#### REGISTER 8-5: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/C-0  | R/C-0 |

|-------|-----|-----|-----|-----|-----|--------|-------|

| —     | —   | —   | —   | —   | —   | ECCDBE | SGHT  |

| bit 7 |     |     |     |     |     |        | bit 0 |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'

bit 1 ECCDBE: ECC Double-Bit Error Trap bit 1 = ECC Double-Bit Error trap has occurred 0 = ECC Double-Bit Error trap has not occurred

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

| REGISTER 9      | -3: 0501                 | IUN: FRC 0                   | SCILLATOR                            | IUNE REGIS                   | IER                          |                              |                              |

|-----------------|--------------------------|------------------------------|--------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|

| R/W-0           | U-0                      | R/W-0                        | R/W-1                                | R-0                          | R/W-0                        | R-0                          | R/W-0                        |

| STEN            | —                        | STSIDL                       | STSRC <sup>(1)</sup>                 | STLOCK                       | STLPOL                       | STOR                         | STORPOL                      |

| bit 15          |                          |                              |                                      |                              |                              |                              | bit 8                        |

|                 |                          | DAMA                         | DAMA                                 | DAALO                        | DAALO                        | DAMA                         | DAMO                         |

| U-0             | U-0                      | R/W-0<br>TUN5 <sup>(2)</sup> | R/W-0<br>TUN4 <sup>(2)</sup>         | R/W-0<br>TUN3 <sup>(2)</sup> | R/W-0<br>TUN2 <sup>(2)</sup> | R/W-0<br>TUN1 <sup>(2)</sup> | R/W-0<br>TUN0 <sup>(2)</sup> |

|                 | _                        | TUN5'-'                      | TUN4                                 | TUN3                         | TUN2                         | TUN'T-                       | 1                            |

| bit 7           |                          |                              |                                      |                              |                              |                              | bit 0                        |

| Legend:         |                          |                              |                                      |                              |                              |                              |                              |

| R = Readable    | bit                      | W = Writable                 | bit                                  | U = Unimplen                 | nented bit, read             | d as '0'                     |                              |

| -n = Value at F | POR                      | '1' = Bit is set             |                                      | '0' = Bit is clea            | ared                         | x = Bit is unk               | nown                         |

| bit 15          | STEN: FRC S              | Self-Tune Enab               | le bit                               |                              |                              |                              |                              |

|                 |                          | Ų                            | led; TUNx bits<br>bled; applicatior  |                              |                              | UNx bits                     |                              |

| bit 14          | Unimplemen               | ted: Read as '               | 0'                                   |                              |                              |                              |                              |

| bit 13          |                          | C Self-Tune Sto              | •                                    |                              |                              |                              |                              |

|                 |                          | ng stops during              | Idle mode<br>uring Idle mode         |                              |                              |                              |                              |

| bit 12          |                          | -                            | erence Clock S                       |                              |                              |                              |                              |

|                 |                          |                              | imately match t                      |                              | ock tolerance                |                              |                              |

|                 |                          |                              | imately match t                      |                              |                              | се                           |                              |

| bit 11          | STLOCK: FR               | C Self-Tune Lo               | ock Status bit                       |                              |                              |                              |                              |

|                 |                          |                              | tly within ±0.2%<br>be within ±0.2%  |                              |                              |                              |                              |

| bit 10          |                          |                              | ock Interrupt Po                     | -                            |                              |                              |                              |

|                 |                          | •                            | t is generated v<br>t is generated v |                              |                              |                              |                              |

| bit 9           | STOR: FRC S              | Self-Tune Out                | of Range Status                      | s bit                        |                              |                              |                              |

|                 |                          |                              | error is beyond<br>is within the tu  | 0                            |                              | <b>U</b>                     | med                          |

| bit 8           | STORPOL: F               | RC Self-Tune                 | Out of Range I                       | nterrupt Polarity            | y bit                        |                              |                              |

|                 |                          |                              | interrupt is ger<br>interrupt is ger |                              |                              |                              |                              |

| bit 7-6         | Unimplemen               | ted: Read as '               | 0'                                   |                              |                              |                              |                              |

| bit 5-0         |                          | RC Oscillator 7              | •                                    |                              |                              |                              |                              |

|                 | 011111 = Ma<br>011110 =  | aximum frequei               | ncy deviation                        |                              |                              |                              |                              |

|                 | •••<br>000001 =          |                              |                                      |                              |                              |                              |                              |

|                 |                          | enter frequency              | , oscillator is ru                   | nning at factory             | / calibrated free            | quency                       |                              |

|                 | • • •                    |                              |                                      |                              |                              |                              |                              |

|                 | 100001 =<br>100000 = Min | nimum frequen                | cv deviation                         |                              |                              |                              |                              |

|                 |                          | -                            | -                                    |                              |                              |                              |                              |

| Note 1: Use     | e of either cloc         | k tuning refere              | nce source has                       | specific applic              | ation requirem               | ents. See Sec                | tion 9.5 "FRC                |

#### REGISTER 9-3: OSCTUN: FRC OSCILLATOR TUNE REGISTER

- Note 1: Use of either clock tuning reference source has specific application requirements. See Section 9.5 "FRC Active Clock Tuning" for details.

- **2:** These bits are read-only when STEN = 1.

# REGISTER 9-7: OSCFDIV: OSCILLATOR FRACTIONAL DIVISOR REGISTER<sup>(1)</sup>

| R/W-0         | R/W-0                | R/W-0                    | R/W-0         | R/W-0                              | R/W-0            | R/W-0             | R/W-0 |  |  |  |

|---------------|----------------------|--------------------------|---------------|------------------------------------|------------------|-------------------|-------|--|--|--|

|               |                      |                          | TRIM          | 1<0:7>                             |                  |                   |       |  |  |  |

| bit 15        |                      |                          |               |                                    |                  |                   | bit 8 |  |  |  |

|               |                      |                          |               |                                    |                  |                   |       |  |  |  |

| R/W-0         | U-0                  | U-0                      | U-0           | U-0                                | U-0              | U-0               | U-0   |  |  |  |

| TRIM8         |                      |                          | _             |                                    | _                |                   |       |  |  |  |

| bit 7         |                      |                          |               | ·                                  | •                |                   | bit 0 |  |  |  |

|               |                      |                          |               |                                    |                  |                   |       |  |  |  |

| Legend:       |                      |                          |               |                                    |                  |                   |       |  |  |  |

| R = Readable  | e bit                | W = Writable t           | bit           | U = Unimplen                       | nented bit, read | d as '0'          |       |  |  |  |

| -n = Value at | POR                  | '1' = Bit is set         |               | '0' = Bit is cleared x = Bit is un |                  |                   | iown  |  |  |  |

|               |                      |                          |               |                                    |                  |                   |       |  |  |  |

| bit 15-7      | TRIM<0:8>: Trim bits |                          |               |                                    |                  |                   |       |  |  |  |

|               |                      | ctional additive to      |               |                                    | 1/2 period of t  | he oscillator clo | ock.  |  |  |  |

|               |                      | $_0 = 0/512 (0.0)$       |               |                                    |                  |                   |       |  |  |  |

|               |                      | $_{1} = 1/512 (0.00)$    | ,             |                                    |                  |                   |       |  |  |  |

|               | 0000_0001_           | _0 = 2/512 (0.00         | 390625) divis | or added to DIV                    | x value          |                   |       |  |  |  |

|               | •                    |                          |               |                                    |                  |                   |       |  |  |  |

|               | •                    |                          |               |                                    |                  |                   |       |  |  |  |

|               | 100000000            | = 256/512 (0.            | 5000) divisor | added to DIVx                      | value            |                   |       |  |  |  |

|               | •                    |                          | ,             |                                    |                  |                   |       |  |  |  |

|               | •                    |                          |               |                                    |                  |                   |       |  |  |  |

|               | •                    |                          |               |                                    |                  |                   |       |  |  |  |

|               | 1111_1111_           | _0 = 510/512 (0.         | 99609375) div | visor added to E                   | DIVx value       |                   |       |  |  |  |

|               | 1111_1111_           | _1 <b>= 511/512 (0</b> . | 998046875) d  | ivisor added to                    | DIVx value       |                   |       |  |  |  |

| bit 6-0       | Unimplemer           | nted: Read as '0         | 3             |                                    |                  |                   |       |  |  |  |

**Note 1:** TRIMx values greater than zero are ONLY valid when DIVx values are greater than zero.

#### REGISTER 10-5: PMD5: PERIPHERAL MODULE DISABLE REGISTER 5

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   |     | _   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0  |

|-------|--------|--------|--------|--------|--------|--------|--------|

| —     | CCP7MD | CCP6MD | CCP5MD | CCP4MD | CCP3MD | CCP2MD | CCP1MD |

| bit 7 |        |        |        |        |        |        | bit 0  |

| Legend:    |          |                                  |                       |                    |  |  |  |  |  |  |

|------------|----------|----------------------------------|-----------------------|--------------------|--|--|--|--|--|--|

| R = Reada  | ble bit  | W = Writable bit                 | U = Unimplemented bit | , read as '0'      |  |  |  |  |  |  |

| -n = Value | at POR   | '1' = Bit is set                 | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |  |  |

|            |          |                                  |                       |                    |  |  |  |  |  |  |

| bit 15-7   | Unimplem | nented: Read as '0'              |                       |                    |  |  |  |  |  |  |

| bit 6      | CCP7MD:  | SCCP7 Module Disable bit         |                       |                    |  |  |  |  |  |  |

|            | 1 = Modu | le is disabled                   |                       |                    |  |  |  |  |  |  |

|            | 0 = Modu | le power and clock sources       | are enabled           |                    |  |  |  |  |  |  |

| bit 5      | CCP6MD:  | SCCP6 Module Disable bit         |                       |                    |  |  |  |  |  |  |

|            | 1 = Modu | le is disabled                   |                       |                    |  |  |  |  |  |  |

|            | 0 = Modu | le power and clock sources       | are enabled           |                    |  |  |  |  |  |  |

| bit 4      | CCP5MD:  | CCP5MD: SCCP5 Module Disable bit |                       |                    |  |  |  |  |  |  |

|            |          | le is disabled                   |                       |                    |  |  |  |  |  |  |

|            | 0 = Modu | le power and clock sources       | are enabled           |                    |  |  |  |  |  |  |

| bit 3      | CCP4MD:  | MCCP4 Module Disable bit         |                       |                    |  |  |  |  |  |  |

|            | 1 = Modu | le is disabled                   |                       |                    |  |  |  |  |  |  |

|            | 0 = Modu | le power and clock sources       | are enabled           |                    |  |  |  |  |  |  |

| bit 2      | CCP3MD:  | MCCP3 Module Disable bit         |                       |                    |  |  |  |  |  |  |

|            | 1 = Modu | le is disabled                   |                       |                    |  |  |  |  |  |  |

|            | 0 = Modu | le power and clock sources       | are enabled           |                    |  |  |  |  |  |  |

| bit 1      | CCP2MD:  | MCCP2 Module Disable bit         |                       |                    |  |  |  |  |  |  |

|            | 1 = Modu | le is disabled                   |                       |                    |  |  |  |  |  |  |

|            | 0 = Modu | le power and clock sources       | are enabled           |                    |  |  |  |  |  |  |

| bit 0      | CCP1MD:  | MCCP1 Module Disable bit         |                       |                    |  |  |  |  |  |  |

|            | 1 = Modu | le is disabled                   |                       |                    |  |  |  |  |  |  |

|            | 0 = Modu | le power and clock sources       | are enabled           |                    |  |  |  |  |  |  |

#### REGISTER 20-2: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER PROTOTYPE, CPU MODE (BD0STAT THROUGH BD63STAT)

| R/W-x  | R/W-x              | r-0 | r-0 | R/W-x | R/W-x  | R/W-x, HSC | R/W-x, HSC |

|--------|--------------------|-----|-----|-------|--------|------------|------------|

| UOWN   | DTS <sup>(1)</sup> | —   | —   | DTSEN | BSTALL | BC9        | BC8        |

| bit 15 |                    |     |     |       |        |            | bit 8      |

| R/W-x, HSC |

|------------|------------|------------|------------|------------|------------|------------|------------|

| BC7        | BC6        | BC5        | BC4        | BC3        | BC2        | BC1        | BC0        |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:         r = Reserved bit         HSC = Hardware Settable/Clear |                  | ble/Clearable bit     |                    |

|------------------------------------------------------------------------|------------------|-----------------------|--------------------|

| R = Readable bit                                                       | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR                                                      | '1' = Bit is set | 'r' = Reserved bit    | x = Bit is unknown |

| bit 15    | UOWN: USB Own bit                                                                                                                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>0 = The microcontroller core owns the BD and its corresponding buffer; the USB module ignores all<br/>other fields in the BD</li> </ul>                                                                                                                                                      |

| bit 14    | DTS: Data Toggle Packet bit <sup>(1)</sup>                                                                                                                                                                                                                                                            |

|           | 1 = Data 1 packet                                                                                                                                                                                                                                                                                     |

|           | 0 = Data 0 packet                                                                                                                                                                                                                                                                                     |

| bit 13-12 | Reserved: Maintain as '0'                                                                                                                                                                                                                                                                             |

| bit 11    | DTSEN: Data Toggle Synchronization Enable bit                                                                                                                                                                                                                                                         |

|           | <ul> <li>1 = Data toggle synchronization is enabled; data packets with incorrect Sync value will be ignored</li> <li>0 = No data toggle synchronization is performed</li> </ul>                                                                                                                       |

| bit 10    | BSTALL: Buffer STALL Enable bit                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Buffer STALL is enabled; STALL handshake issued if a token is received that would use the BD in<br/>the given location (UOWN bit remains set, BD value is unchanged); corresponding EPSTALL bit<br/>will get set on any STALL handshake</li> <li>0 = Buffer STALL is disabled</li> </ul> |

| bit 9-0   | BC<9:0>: Byte Count bits                                                                                                                                                                                                                                                                              |

|           | This represents the number of bytes to be transmitted or the maximum number of bytes to be received during a transfer. Upon completion, the byte count is updated by the USB module with the actual number of bytes transmitted or received.                                                          |

| Note 1: ⊺ | his bit is ignored unless DTSEN = 1.                                                                                                                                                                                                                                                                  |

#### 25.4 Achieving Maximum A/D Converter (ADC) Performance

In order to get the shortest overall conversion time (called the "throughput") while maintaining accuracy, several factors must be considered. These are described in detail below.

- Dependence of AVDD If the AVDD supply is < 2.7V, the Charge Pump Enable bit (PUMPEN, AD1CON3<13>) should be set to '1'. The input channel multiplexer has a varying resistance with AVDD (the lower AVDD, the higher the internal switch resistance). The charge pump provides a higher internal AVDD to keep the switch resistance as low as possible.

- Dependence on TAD The ADC timing is driven by TAD, not TCYC. Selecting the TAD time correctly is critical to getting the best ADC throughput. It is important to note that the overall ADC throughput is not simply the 'Conversion Time' of the SAR; it is the combination of the Conversion Time, the Sample Time and additional TAD delays for internal synchronization logic.

- Relationship between TCYC and TAD There is not a fixed 1:1 timing relationship between TCYC and TAD. The fastest possible throughput is fundamentally set by TAD (min), not by TCYC. The TAD time is set as a programmable integer multiple of TCYC by the ADCS<7:0> bits. Referring to Table 33-26, the TAD (min) time is greater than the 4 MHz period of the dedicated ADC RC clock generator. Therefore, TAD must be 2 TCYC in order to use the RC clock for fastest throughput. The TAD (min) is a multiple of 3.597 MHz as opposed to 4 MHz. To run as fast as possible, TCYC must be a multiple of TAD (min) because values of ADCSx are integers. For example, if a standard "color burst" crystal of 14.31818 MHz is used, TCYC is 279.4 ns, which is very close to TAD (min) and the ADC throughput is optimal. Running at 16 MHz will actually reduce the throughput, because TAD will have to be 500 ns as the TCYC of 250 ns violates TAD (min).

- Dependence on driving Source Resistance (Rs) Certain transducers have high output impedance (> 2.5 kΩ). Having a high Rs will require longer sampling time to charge the S/H capacitor through the resistance path (see Figure 25-3). The worst case scenario is a full-range voltage step of AVss to AVDD, with the sampling cap at AVSS. The capacitor time constant is (Rs + Ric + Rss) (CHOLD) and the sample time needs to be 6 time constants minimum (8 preferred). Since the ADC logic timing is TAD-based, the sample time (in TAD) must be long enough, over all conditions, to charge/discharge CHOLD. Do not assume one TAD is sufficient sample time; longer times may be required to achieve the accuracy needed by the application. The value of CHOLD is 40 pF.

A small amount of charge is present at the ADC input pin when the sample switch is closed. If Rs is high, this will generate a DC error exceeding 1 LSB. Keeping Rs < 50 $\Omega$  is recommenced for best results. The error can also be reduced by increasing sample time (a 2 k $\Omega$  value of Rs requires a 3  $\mu$ S sample time to eliminate the error).

• Calculating Throughput – The throughput of the ADC is based on TAD. The throughput is given by:

$$Throughput = \left(\frac{l}{Sample Time + SAR Conversion Time + Clock Sync Time}\right)$$

where:

*Sample Time* is the calculated TAD periods for the application.

*SAR Conversion Time* is 12 TAD for 10-bit and 14 TAD for 12-bit conversions.

*Clock Sync Time* is 2.5 TAD (worst case scenario).

For example, using an 8 MHz FRC means the TCYC = 250 ns. This requires: TAD = 2 TCYC = 500 ns.Therefore, the throughput is:

$$Throughput = \left(\frac{1}{500 \text{ ns} + 14 \cdot 500 \text{ ns} + 2.5 \cdot 500 \text{ ns}}\right) = 114.28 \text{ KS/sec}$$

Note that the clock sync delay could be as little as 1.5 TAD, which could produce 121 KS/sec, but that cannot be ensured as the timing relationship is asynchronous and not specified. The worst case timing of 2.5 TAD should be used to calculate throughput.

For example, if a certain transducer has a 20 k $\Omega$  output impedance, the maximum sample time is determined by:

Sample Time =

$$6 \cdot (RS + RIC + RSS) \cdot CHOLD$$

=  $6 \cdot (20K + 250 + 350) \cdot 40 \, pF$

=  $4.95 \, \mu S$

If TAD = 500 ns, this requires a Sample Time of 4.95 us/500 ns = 10 TAD (for a full-step voltage on the transducer output).

| R/W-0        | R/W-0                                                                                                 | R/W-0                                                                                                                                                       | R/W-0           | U-0                 | U-0              | R/W-0            | R/W-0          |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|------------------|------------------|----------------|--|--|--|

| ASEN         | LPEN                                                                                                  | CTMREQ                                                                                                                                                      | BGREQ           |                     |                  | ASINT1           | ASINT0         |  |  |  |

| bit 15       |                                                                                                       | •                                                                                                                                                           |                 |                     |                  |                  | bit            |  |  |  |

|              |                                                                                                       |                                                                                                                                                             |                 | <b>D</b> 444 A      | 5444.6           | <b>B</b> 844 6   |                |  |  |  |

| U-0          | U-0                                                                                                   | U-0                                                                                                                                                         | U-0             | R/W-0               | R/W-0            | R/W-0            | R/W-0          |  |  |  |

|              | —                                                                                                     | —                                                                                                                                                           |                 | WM1                 | WM0              | CM1              | CM0            |  |  |  |

| bit 7        |                                                                                                       |                                                                                                                                                             |                 |                     |                  |                  | bit            |  |  |  |

| Legend:      |                                                                                                       |                                                                                                                                                             |                 |                     |                  |                  |                |  |  |  |

| R = Readab   | ole bit                                                                                               | W = Writable I                                                                                                                                              | oit             | U = Unimplem        | ented bit, read  | d as '0'         |                |  |  |  |

| -n = Value a | it POR                                                                                                | '1' = Bit is set                                                                                                                                            |                 | '0' = Bit is clea   | ared             | x = Bit is unkr  | iown           |  |  |  |

| bit 15       | ASEN: Auto-S                                                                                          | Scan Enable bit                                                                                                                                             | ·               |                     |                  |                  |                |  |  |  |

|              | 1 = Auto-scar                                                                                         |                                                                                                                                                             |                 |                     |                  |                  |                |  |  |  |

|              | 0 = Auto-scar                                                                                         | n is disabled                                                                                                                                               |                 |                     |                  |                  |                |  |  |  |

| bit 14       | LPEN: Low-P                                                                                           | ower Enable bi                                                                                                                                              | t               |                     |                  |                  |                |  |  |  |

|              | <ul> <li>1 = Low power is enabled after scan</li> <li>0 = Full power is enabled after scan</li> </ul> |                                                                                                                                                             |                 |                     |                  |                  |                |  |  |  |

| L:1 1 0      |                                                                                                       |                                                                                                                                                             |                 |                     |                  |                  |                |  |  |  |

| bit 13       | <b>CTMREQ:</b> CTMU Request bit<br>1 = CTMU is enabled when the A/D is enabled and active             |                                                                                                                                                             |                 |                     |                  |                  |                |  |  |  |

|              | 0 = CTMU is not enabled by the A/D                                                                    |                                                                                                                                                             |                 |                     |                  |                  |                |  |  |  |

| bit 12       |                                                                                                       | d Gap Request                                                                                                                                               |                 |                     |                  |                  |                |  |  |  |

|              | 1 = Band gap                                                                                          |                                                                                                                                                             | en the A/D is e | nabled and acti     | ve               |                  |                |  |  |  |

| bit 11-10    | Unimplemen                                                                                            | ted: Read as 'd                                                                                                                                             | )'              |                     |                  |                  |                |  |  |  |

| bit 9-8      | ASINT<1:0>:                                                                                           | Auto-Scan (Th                                                                                                                                               | reshold Detect  | ) Interrupt Mode    | e bits           |                  |                |  |  |  |

|              | 10 = Interrupt                                                                                        | after valid com                                                                                                                                             | pare has occu   |                     |                  | compare has c    | occurred       |  |  |  |

| bit 7-4      | Unimplemen                                                                                            | ted: Read as 'd                                                                                                                                             | )'              |                     |                  |                  |                |  |  |  |

| bit 3-2      | <b>WM&lt;1:0&gt;:</b> W                                                                               | rite Mode bits                                                                                                                                              |                 |                     |                  |                  |                |  |  |  |

|              | 11 = Reserved                                                                                         |                                                                                                                                                             |                 |                     |                  |                  |                |  |  |  |

|              | 10 = Auto-compare only (conversion results are not saved, but interrupts are generated when a valid   |                                                                                                                                                             |                 |                     |                  |                  |                |  |  |  |

|              |                                                                                                       | match occurs, as defined by the CMx and ASINTx bits)<br>01 = Convert and save (conversion results are saved to locations as determined by the register bits |                 |                     |                  |                  |                |  |  |  |

|              | when a match occurs, as defined by the CMx bits)                                                      |                                                                                                                                                             |                 |                     |                  |                  |                |  |  |  |

|              | 0,1                                                                                                   | •                                                                                                                                                           |                 | saved to a loca     | tion determine   | ed by the Buffer | register bits) |  |  |  |

| bit 1-0      |                                                                                                       | mpare Mode bi                                                                                                                                               |                 |                     |                  |                  |                |  |  |  |

|              |                                                                                                       | Window mode<br>by the correspo                                                                                                                              |                 |                     | conversion res   | sult is outside  | ot the windo   |  |  |  |

|              | 10 = Inside W                                                                                         |                                                                                                                                                             | alid match occ  |                     | ersion result is | inside the wind  | low defined b  |  |  |  |

|              |                                                                                                       |                                                                                                                                                             |                 | rs if the result is | greater than t   | he value in the  | correspondir   |  |  |  |

|              | Buffer re                                                                                             | egister                                                                                                                                                     |                 |                     | -                | ue in the corres | -              |  |  |  |

|              | register                                                                                              |                                                                                                                                                             |                 |                     |                  |                  |                |  |  |  |

#### REGISTER 25-5: AD1CON5: A/D CONTROL REGISTER 5

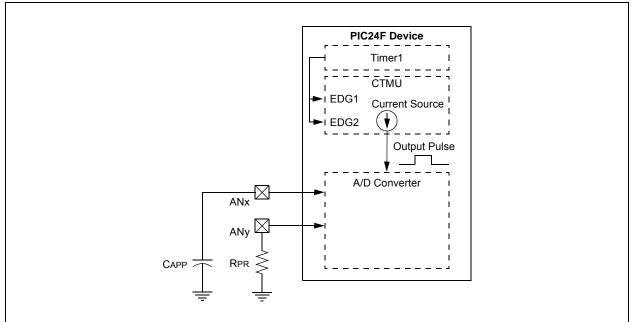

# FIGURE 28-1: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR CAPACITANCE MEASUREMENT

#### 28.2 Measuring Time/Routing Current Source to A/D Input Pin

Time measurements on the pulse width can be similarly performed using the A/D module's Internal Capacitor (CAD) and a precision resistor for current calibration. Figure 28-2 displays the external connections used for time measurements, and how the CTMU and A/D modules are related in this application. This example also shows both edge events coming from the external CTEDx pins, but other configurations using internal edge sources are possible.

This mode is enabled by clearing the TGEN bit (CTMUCON1L<12>). The current source is tied to the input of the A/D after the sampling switch. Therefore, the A/D bit, SAMP, must be set to '1' in order for the current to be routed through the channel selection MUX to the desired pin.

## 28.3 Pulse Generation and Delay

The CTMU module can also generate an output pulse with edges that are not synchronous with the device's system clock. More specifically, it can generate a pulse with a programmable delay from an edge event input to the module. When the module is configured for pulse generation delay by setting the TGEN bit (CTMUCON1<12>), the internal current source is connected to the B input of Comparator 2. A Capacitor (CDELAY) is connected to the Comparator 2 pin, C2INB, and the Comparator Voltage Reference, CVREF, is connected to C2INA. CVREF is then configured for a specific trip point. The module begins to charge CDELAY when an edge event is detected. When CDELAY charges above the CVREF trip point, a pulse is output on CTPLS. The length of the pulse delay is determined by the value of CDELAY and the CVREF trip point.

Figure 28-3 illustrates the external connections for pulse generation, as well as the relationship of the different analog modules required. While CTED1 is shown as the input pulse source, other options are available. A detailed discussion on pulse generation with the CTMU module is provided in the "dsPIC33/ PIC24 Family Reference Manual".

# PIC24FJ1024GA610/GB610 FAMILY

# **REGISTER 30-11: FDEVOPT1 CONFIGURATION REGISTER**

| Legend: |     | PO = Progran |         |                                 |         |         |           |

|---------|-----|--------------|---------|---------------------------------|---------|---------|-----------|

| bit 7   |     | _            | ALTVREF | SUSCHPUT                        | TMPRPIN | ALTCMPI | <br>bit 0 |

| U-1     | U-1 | U-1          | R/PO-1  | R/PO-1<br>SOSCHP <sup>(1)</sup> | R/PO-1  | R/PO-1  | U-1       |

| bit 15  |     |              |         |                                 |         |         | bit 8     |

|         |     | —            |         | —                               |         | —       | —         |

| U-1     | U-1 | U-1          | U-1     | U-1                             | U-1     | U-1     | U-1       |

| bit 23  |     |              |         |                                 |         |         | bit 16    |

| —       | —   | —            | —       | —                               | —       | —       | —         |

| U-1     | U-1 | U-1          | U-1     | U-1                             | U-1     | U-1     | U-1       |

| bit 4 | ALTVREF: Alternate Voltage Reference Location Enable bit (100-pin and 121-pin devices only)<br>1 = VREF+ and CVREF+ on RA10, VREF- and CVREF- on RA9<br>0 = VREF+ and CVREF+ on RB0, VREF- and CVREF- on RB1 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | <b>SOSCHP:</b> SOSC High-Power Enable bit (valid only when SOSCSEL = 1) <sup>(1)</sup>                                                                                                                       |

|       | 1 = SOSC High-Power mode is enabled<br>0 = SOSC Low-Power mode is enabled                                                                                                                                    |

| bit 2 | <b>TMPRPIN:</b> Tamper Pin Enable bit<br>1 = TMPR pin function is disabled                                                                                                                                   |

|       | 0 = TMPR pin function is enabled                                                                                                                                                                             |

| bit 1 | ALTCMPI: Alternate Comparator Input Enable bit                                                                                                                                                               |

|       | 1 = C1INC, C2INC and C3INC are on their standard pin locations                                                                                                                                               |

|       | 0 = C1INC, C2INC and C3INC are on RG9                                                                                                                                                                        |

| bit 0 | Unimplemented: Read as '1'                                                                                                                                                                                   |

|       |                                                                                                                                                                                                              |

**Note 1:** High-Power mode is for crystals with 35K ESR (typical). Low-Power mode is for crystals with more than 65K ESR.

#### TABLE 33-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |           |                                                                             | Standard Operating Conditions:2.0V to 3.6V (unless other<br>-40°C $\leq$ TA $\leq$ +85°C for Inc.Operating temperature-40°C $\leq$ TA $\leq$ +85°C for Inc. |     |          |       |                                                    |

|--------------------|-----------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------|----------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic                                                              | Min                                                                                                                                                         | Тур | Max      | Units | Conditions                                         |

| Operati            | ng Voltag | e                                                                           |                                                                                                                                                             |     |          |       |                                                    |

| DC10               | Vdd       | Supply Voltage                                                              | 2.0                                                                                                                                                         | _   | 3.6      | V     | BOR is disabled                                    |

|                    |           |                                                                             | VBOR                                                                                                                                                        | _   | 3.6      | V     | BOR is enabled                                     |

| DC12               | Vdr       | RAM Data Retention<br>Voltage <sup>(1)</sup>                                | Greater of:<br>VPORREL or<br>VBOR                                                                                                                           | _   |          | V     | VBOR is used only if BOR<br>is enabled (BOREN = 1) |

| DC16               | VPOR      | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal            | Vss                                                                                                                                                         | _   | _        | V     | (Note 2)                                           |

| DC17A              | SVDD      | Recommended<br>VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal | 1V/20 ms                                                                                                                                                    | _   | 1V/10 µS | sec   | (Note 2, Note 4)                                   |

| DC17B              | VBOR      | Brown-out Reset<br>Voltage on VDD Transition,<br>High-to-Low                | 2.0                                                                                                                                                         | 2.1 | 2.2      | V     | (Note 3)                                           |

**Note 1:** This is the limit to which VDD may be lowered and the RAM contents will always be retained.

**2:** If the VPOR or SVDD parameters are not met, or the application experiences slow power-down VDD ramp rates, it is recommended to enable and use BOR.

**3:** On a rising VDD power-up sequence, application firmware execution begins at the higher of the VPORREL or VBOR level (when BOREN = 1).

4: VDD rise times outside this window may not internally reset the processor and are not parametrically tested.

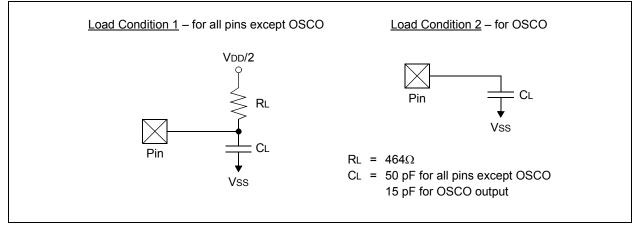

# 33.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC24FJ1024GA610/GB610 family AC characteristics and timing parameters.

#### TABLE 33-16: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)          |

|--------------------|--------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial    |

|                    | Operating voltage VDD range as described in Section 33.1 "DC Characteristics". |

#### FIGURE 33-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 33-17: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosco  | OSCO/CLKO Pin         | _   | —                  | 15  | pF    | In XT and HS modes when<br>external clock is used to drive<br>OSCI |

| DO56         | Сю     | All I/O Pins and OSCO | _   | _                  | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            |     | _                  | 400 | pF    | In I <sup>2</sup> C mode                                           |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 33-25: A/D MODULE SPECIFICATIONS

| AC CHARACTERISTICS |           |                                                   | Standard Operating Conditions: 2.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |          |                                   |       |                                                                                                |

|--------------------|-----------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|-------|------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic                                    | Min.                                                                                                                                            | Тур      | Max.                              | Units | Conditions                                                                                     |

|                    |           |                                                   | Device \$                                                                                                                                       | Supply   |                                   |       |                                                                                                |

| AD01               | AVDD      | Module VDD Supply                                 | Greater of:<br>VDD – 0.3<br>or 2.2                                                                                                              |          | Lesser of:<br>VDD + 0.3<br>or 3.6 | V     |                                                                                                |

| AD02               | AVss      | Module Vss Supply                                 | Vss – 0.3                                                                                                                                       |          | Vss + 0.3                         | V     |                                                                                                |

|                    |           |                                                   | Reference                                                                                                                                       | e Inputs |                                   |       |                                                                                                |

| AD05               | VREFH     | Reference Voltage High                            | AVss + 1.7                                                                                                                                      |          | AVDD                              | V     |                                                                                                |

| AD06               | VREFL     | Reference Voltage Low                             | AVss                                                                                                                                            |          | AVDD – 1.7                        | V     |                                                                                                |

| AD07               | VREF      | Absolute Reference<br>Voltage                     | AVss – 0.3                                                                                                                                      |          | AVDD + 0.3                        | V     |                                                                                                |

|                    |           |                                                   | Analog                                                                                                                                          | Inputs   |                                   |       |                                                                                                |

| AD10               | VINH-VINL | Full-Scale Input Span                             | VREFL                                                                                                                                           | _        | VREFH                             | V     | (Note 1)                                                                                       |

| AD11               | Vin       | Absolute Input Voltage                            | AVss - 0.3                                                                                                                                      | _        | AVDD + 0.3                        | V     |                                                                                                |

| AD12               | VINL      | Absolute VINL Input<br>Voltage                    | AVss – 0.3                                                                                                                                      | _        | AVDD/3                            | V     |                                                                                                |

| AD13               |           | Leakage Current                                   | _                                                                                                                                               | ±1.0     | ±610                              | nA    | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = $3V$ ,<br>Source Impedance = $2.5 \text{ k}\Omega$ |

| AD17               | Rin       | Recommended Impedance<br>of Analog Voltage Source | —                                                                                                                                               | _        | 2.5K                              | Ω     | 10-bit                                                                                         |

|                    |           |                                                   | A/D Acc                                                                                                                                         | curacy   |                                   |       | •                                                                                              |

| AD20B              | Nr        | Resolution                                        | —                                                                                                                                               | 12       | —                                 | bits  |                                                                                                |

| AD21B              | INL       | Integral Nonlinearity                             | -                                                                                                                                               | ±1       | < ±2                              | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |

| AD22B              | DNL       | Differential Nonlinearity                         | —                                                                                                                                               |          | < ±1                              | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |

| AD23B              | Gerr      | Gain Error                                        | —                                                                                                                                               | ±1       | ±4                                | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |

| AD24B              | EOFF      | Offset Error                                      | —                                                                                                                                               | ±1       | ±2                                | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3V                                                 |

| AD25B              |           | Monotonicity <sup>(1)</sup>                       | _                                                                                                                                               | —        | _                                 | _     | Guaranteed                                                                                     |

| Note 1: | Measurements are taken with the external | VREF+ and VREF- used as the A | /D voltage reference. |

|---------|------------------------------------------|-------------------------------|-----------------------|

|         |                                          |                               |                       |

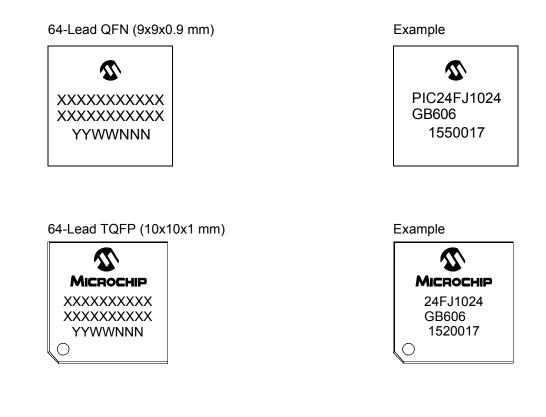

# 34.0 PACKAGING INFORMATION

# 34.1 Package Marking Information

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|-------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carrie                      | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                            |

© 2015-2016 Microchip Technology Inc.