Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb606t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0  | Device Overview                                             |       |

|------|-------------------------------------------------------------|-------|

| 2.0  | Guidelines for Getting Started with 16-Bit Microcontrollers | 41    |

| 3.0  | CPU                                                         |       |

| 4.0  | Memory Organization                                         |       |

| 5.0  | Direct Memory Access Controller (DMA)                       |       |

| 6.0  | Flash Program Memory                                        | 89    |

| 7.0  | Resets                                                      | 97    |

| 8.0  | Interrupt Controller                                        | . 103 |

| 9.0  | Oscillator Configuration                                    | . 115 |

| 10.0 | Power-Saving Features                                       | . 137 |

| 11.0 | I/O Ports                                                   | . 149 |

| 12.0 | Timer1                                                      | . 185 |

| 13.0 | Timer2/3 and Timer4/5                                       | . 187 |

|      | Input Capture with Dedicated Timers                         |       |

|      | Output Compare with Dedicated Timers                        |       |

|      | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)           |       |

|      | Serial Peripheral Interface (SPI)                           |       |

|      | Inter-Integrated Circuit (I <sup>2</sup> C)                 |       |

|      | Universal Asynchronous Receiver Transmitter (UART)          |       |

|      | Universal Serial Bus with On-The-Go Support (USB OTG)       |       |

|      | Enhanced Parallel Master Port (EPMP)                        |       |

|      | Real-Time Clock and Calendar with Timestamp                 |       |

|      | 32-Bit Programmable Cyclic Redundancy Check (CRC) Generator |       |

|      | Configurable Logic Cell (CLC)                               |       |

|      | 12-Bit A/D Converter with Threshold Detect                  |       |

|      | Triple Comparator Module                                    |       |

|      | Comparator Voltage Reference                                |       |

|      | Charge Time Measurement Unit (CTMU)                         |       |

| 29.0 | High/Low-Voltage Detect (HLVD)                              | . 387 |

|      | Special Features                                            |       |

|      | Development Support                                         |       |

|      | Instruction Set Summary                                     |       |

|      | Electrical Characteristics                                  |       |

|      | Packaging Information                                       |       |

|      | ndix A: Revision History                                    |       |

|      |                                                             |       |

|      | Aicrochip Web Site                                          |       |

|      | omer Change Notification Service                            |       |

|      | omer Support                                                |       |

| Prod | uct Identification System                                   | . 465 |

## 1.2 DMA Controller

PIC24FJ1024GA610/GB610 family devices have a Direct Memory Access (DMA) Controller. This module acts in concert with the CPU, allowing data to move between data memory and peripherals without the intervention of the CPU, increasing data throughput and decreasing execution time overhead. Eight independently programmable channels make it possible to service multiple peripherals at virtually the same time, with each channel peripheral performing a different operation. Many types of data transfer operations are supported.

## 1.3 Other Special Features

- Peripheral Pin Select: The Peripheral Pin Select (PPS) feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

- **Configurable Logic Cell:** The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins.

- **Timing Modules:** The PIC24FJ1024GA610/GB610 family provides five independent, general purpose, 16-bit timers (four of which can be combined into two 32-bit timers). The devices also include 3 multiple output and 4 single output advanced Capture/Compare/PWM/Timer peripherals, and 6 independent legacy Input Capture and 6 independent legacy Output Compare modules.

- Communications: The PIC24FJ1024GA610/ GB610 family incorporates a range of serial communication peripherals to handle a range of application requirements. There are 3 independent I<sup>2</sup>C modules that support both Master and Slave modes of operation. Devices also have, through the PPS feature, 6 independent UARTs with built-in IrDA<sup>®</sup> encoders/decoders and 3 SPI modules.

- Analog Features: All members of the PIC24FJ1024GA610/GB610 family include the new 12-bit A/D Converter (A/D) module and a triple comparator module. The A/D module incorporates a range of new features that allow the converter to assess and make decisions on incoming data, reducing CPU overhead for routine A/D conversions. The comparator module includes three analog comparators that are configurable for a wide range of operations.

- **CTMU Interface:** In addition to their other analog features, members of the PIC24FJ1024GA610/ GB610 family include the CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- Enhanced Parallel Master/Parallel Slave Port: This module allows rapid and transparent access to the microcontroller data bus, and enables the CPU to directly address external data memory. The parallel port can function in Master or Slave mode, accommodating data widths of 4, 8 or 16 bits and address widths of up to 23 bits in Master modes.

- Real-Time Clock and Calendar (RTCC): This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

## 1.4 Details on Individual Family Members

Devices in the PIC24FJ1024GA610/GB610 family are available in 64-pin, 100-pin and 121-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in six ways:

- Flash program memory (128 Kbytes for PIC24FJ128GX6XX devices, 256 Kbytes for PIC24FJ256GX6XX devices, 512 Kbytes for PIC24FJ512GX6XX devices and 1024 Kbytes for PIC24FJ1024GX6XX devices).

- Available I/O pins and ports (53 pins on 6 ports for 64-pin devices and 85 pins on 7 ports for 100-pin and 121-pin devices).

- Available Interrupt-on-Change Notification (IOC) inputs (53 on 64-pin devices and 85 on 100-pin and 121-pin devices).

- 4. Available remappable pins (29 pins on 64-pin devices, 44 pins on 100-pin and 121-pin devices).

- Available USB peripheral (available on PIC24FJXXXGB6XX devices; not available on PIC24FJXXXGA6XX devices).

- 6. Analog input channels (16 channels for 64-pin devices and 24 channels for 100-pin and 121-pin devices).

All other features for devices in this family are identical. These are summarized in Table 1-1, Table 1-2 and Table 1-3.

A list of the pin features available on the PIC24FJ1024GA610/GB610 family devices, sorted by function, is shown in Table 1-3. Note that this table shows the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

|                 |                                     | Pin N                            | umber/Gri                        |                                  |                         |                         |     |                 |                    |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|--------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer | Description        |

| RA0             | _                                   | —                                | 17                               | 17                               | G3                      | G3                      | I/O | DIG/ST          | PORTA Digital I/Os |

| RA1             | _                                   | _                                | 38                               | 38                               | J6                      | J6                      | I/O | DIG/ST          |                    |

| RA2             | _                                   | _                                | 58                               | 58                               | H11                     | H11                     | I/O | DIG/ST          |                    |

| RA3             | _                                   | _                                | 59                               | 59                               | G10                     | G10                     | I/O | DIG/ST          |                    |

| RA4             | _                                   | _                                | 60                               | 60                               | G11                     | G11                     | I/O | DIG/ST          |                    |

| RA5             | _                                   | _                                | 61                               | 61                               | G9                      | G9                      | I/O | DIG/ST          |                    |

| RA6             | _                                   | —                                | 91                               | 91                               | C5                      | C5                      | I/O | DIG/ST          |                    |

| RA7             | _                                   | _                                | 92                               | 92                               | B5                      | B5                      | I/O | DIG/ST          |                    |

| RA9             | _                                   | —                                | 28                               | 28                               | L2                      | L2                      | I/O | DIG/ST          |                    |

| RA10            | _                                   | _                                | 29                               | 29                               | K3                      | K3                      | I/O | DIG/ST          |                    |

| RA14            | _                                   | _                                | 66                               | 66                               | E11                     | E11                     | I/O | DIG/ST          |                    |

| RA15            | _                                   | —                                | 67                               | 67                               | E8                      | E8                      | I/O | DIG/ST          |                    |

| RB0             | 16                                  | 16                               | 25                               | 25                               | K2                      | K2                      | I/O | DIG/ST          | PORTB Digital I/Os |

| RB1             | 15                                  | 15                               | 24                               | 24                               | K1                      | K1                      | I/O | DIG/ST          |                    |

| RB2             | 14                                  | 14                               | 23                               | 23                               | J2                      | J2                      | I/O | DIG/ST          |                    |

| RB3             | 13                                  | 13                               | 22                               | 22                               | J1                      | J1                      | I/O | DIG/ST          |                    |

| RB4             | 12                                  | 12                               | 21                               | 21                               | H2                      | H2                      | I/O | DIG/ST          |                    |

| RB5             | 11                                  | 11                               | 20                               | 20                               | H1                      | H1                      | I/O | DIG/ST          |                    |

| RB6             | 17                                  | 17                               | 26                               | 26                               | L1                      | L1                      | I/O | DIG/ST          |                    |

| RB7             | 18                                  | 18                               | 27                               | 27                               | J3                      | J3                      | I/O | DIG/ST          |                    |

| RB8             | 21                                  | 21                               | 32                               | 32                               | K4                      | K4                      | I/O | DIG/ST          |                    |

| RB9             | 22                                  | 22                               | 33                               | 33                               | L4                      | L4                      | I/O | DIG/ST          |                    |

| RB10            | 23                                  | 23                               | 34                               | 34                               | L5                      | L5                      | I/O | DIG/ST          |                    |

| RB11            | 24                                  | 24                               | 35                               | 35                               | J5                      | J5                      | I/O | DIG/ST          |                    |

| RB12            | 27                                  | 27                               | 41                               | 41                               | J7                      | J7                      | I/O | DIG/ST          |                    |

| RB13            | 28                                  | 28                               | 42                               | 42                               | L7                      | L7                      | I/O | DIG/ST          |                    |

| RB14            | 29                                  | 29                               | 43                               | 43                               | K7                      | K7                      | I/O | DIG/ST          |                    |

| RB15            | 30                                  | 30                               | 44                               | 44                               | L8                      | L8                      | I/O | DIG/ST          |                    |

| RC1             | _                                   | _                                | 6                                | 6                                | D1                      | D1                      | I/O | DIG/ST          | PORTC Digital I/Os |

| RC2             | _                                   | _                                | 7                                | 7                                | E4                      | E4                      | I/O | DIG/ST          |                    |

| RC3             | —                                   | _                                | 8                                | 8                                | E2                      | E2                      | I/O | DIG/ST          |                    |

| RC4             | -                                   | _                                | 9                                | 9                                | E1                      | E1                      | I/O | DIG/ST          |                    |

| RC12            | 39                                  | 39                               | 63                               | 63                               | F9                      | F9                      | I/O | DIG/ST          |                    |

| RC13            | 47                                  | 47                               | 73                               | 73                               | C10                     | C10                     | I/O | DIG/ST          |                    |

| RC14            | 48                                  | 48                               | 74                               | 74                               | B11                     | B11                     | I/O | DIG/ST          |                    |

| RC15            | 40                                  | 40                               | 64                               | 64                               | F11                     | F11                     | I/O | DIG/ST          |                    |

#### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated Transceiver

# 4.3.3 READING DATA FROM PROGRAM MEMORY USING EDS

The upper 32 Kbytes of Data Space may optionally be mapped into any 16K word page of the program space. This provides transparent access of stored constant data from the Data Space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the Data Space occurs when the MSb of EA is '1' and the DSRPAG<9> is also '1'. The lower 8 bits of DSRPAG are concatenated to the Wn<14:0> bits to form a 23-bit EA to access program memory. The DSRPAG<8> decides which word should be addressed; when the bit is '0', the lower word, and when '1', the upper word of the program memory is accessed.

The entire program memory is divided into 512 EDS pages, from 200h to 3FFh, each consisting of 16K words of data. Pages, 200h to 2FFh, correspond to the lower words of the program memory, while 300h to 3FFh correspond to the upper words of the program memory.

Using this EDS technique, the entire program memory can be accessed. Previously, the access to the upper word of the program memory was not supported. Table 4-15 provides the corresponding 23-bit EDS address for program memory with EDS page and source addresses.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

| DSRPAG<br>(Data Space Read Register) | Source Address while<br>Indirect Addressing | 23-Bit EA Pointing<br>to EDS | Comment                            |  |

|--------------------------------------|---------------------------------------------|------------------------------|------------------------------------|--|

| 200h                                 |                                             | 000000h to 007FFEh           | Lower words of 4M program          |  |

| •                                    |                                             | •                            | instructions; (8 Mbytes) for       |  |

| •                                    |                                             | •                            | read operations only.              |  |

| •                                    |                                             | •                            |                                    |  |

| 2FFh                                 |                                             | 7F8000h to 7FFFFEh           |                                    |  |

| 300h                                 | 8000h to FFFFh                              | 000001h to 007FFFh           | Upper words of 4M program          |  |

| •                                    |                                             | •                            | instructions (4 Mbytes remaining;  |  |

| •                                    |                                             | •                            | 4 Mbytes are phantom bytes) for    |  |

| •                                    |                                             | •                            | read operations only.              |  |

| 3FFh                                 |                                             | 7F8001h to 7FFFFFh           |                                    |  |

| 000h                                 |                                             | Invalid Address              | Address error trap. <sup>(1)</sup> |  |

## TABLE 4-15: EDS PROGRAM ADDRESS WITH DIFFERENT PAGES AND ADDRESSES

**Note 1:** When the source/destination address is above 8000h and DSRPAG/DSWPAG is '0', an address error trap will occur.

#### EXAMPLE 4-3: EDS READ CODE FROM PROGRAM MEMORY IN ASSEMBLY

| ; Set the EDS page from where the data to be read |                                         |                                                           |  |  |  |  |

|---------------------------------------------------|-----------------------------------------|-----------------------------------------------------------|--|--|--|--|

| mov                                               | #0x0202, w0                             |                                                           |  |  |  |  |

| mov                                               | w0, DSRPAG                              | ;page 0x202, consisting lower words, is selected for read |  |  |  |  |

| mov                                               | #0x000A, w1                             | ;select the location (0x0A) to be read                    |  |  |  |  |

| bset                                              | w1, #15                                 | ;set the MSB of the base address, enable EDS mode         |  |  |  |  |

| ;Read a by                                        | ;Read a byte from the selected location |                                                           |  |  |  |  |

| mov.b                                             | [w1++], w2                              | ;read Low byte                                            |  |  |  |  |

| mov.b                                             | [w1++], w3                              | ;read High byte                                           |  |  |  |  |

| ;Read a wo                                        | rd from the selected locati             | on                                                        |  |  |  |  |

| mov                                               | [w1], w2                                | i                                                         |  |  |  |  |

| ;Read Doub                                        | le - word from the selected             | location                                                  |  |  |  |  |

| mov.d                                             | [w1], w2                                | ;two word read, stored in w2 and w3                       |  |  |  |  |

## 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "PIC24F Flash Program Memory" (DS30009715), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The PIC24FJ1024GA610/GB610 family of devices contains internal Flash program memory for storing and executing application code. The program memory is readable, writable and erasable. The Flash memory can be programmed in four ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- JTAG

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FJ1024GA610/GB610 family device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (named PGECx and PGEDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 128 instructions (384 bytes) at a time and erase program memory in blocks of 1024 instructions (3072 bytes) at a time.

The device implements a 7-bit Error Correcting Code (ECC). The NVM block contains a logic to write and read ECC bits to and from the Flash memory. The Flash is programmed at the same time as the corresponding ECC parity bits. The ECC provides improved resistance to Flash errors. ECC single bit errors can be transparently corrected. ECC Double-Bit Errors (ECCDBE) result in a trap.

## 6.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 6-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

I 1 I. 24 Bits  $\neg$ Using Program Counter 0 Program 0 Counter Working Reg EA Using TBLPAG Reg Table 1/0Instruction -16 Bits 8 Bits |♠∕ User/Configuration Byte 24-Bit EA Space Select Select T 1 1 I.

FIGURE 6-1: ADDRESSING FOR TABLE REGISTERS

NOTES:

## 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:256, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

#### 10.4 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMD Control registers.

Both bits have similar functions in enabling or disabling their associated module. Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect and read values will be invalid. Many peripheral modules have a corresponding PMD bit.

In contrast, disabling a module by clearing its XXXEN bit disables its functionality, but leaves its registers available to be read and written to. This reduces power consumption, but not by as much as setting the PMD bit does. Most peripheral modules have an enable bit; exceptions include input capture, output compare and RTCC.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature allows further reduction of power consumption during Idle mode, enhancing power savings for extremely critical power applications.

## 11.3 Interrupt-on-Change (IOC)

The Interrupt-on-Change function of the I/O ports allows the PIC24FJ1024GA610/GB610 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode when the clocks are disabled.

Interrupt-on-Change functionality is enabled on a pin by setting the IOCPx and/or IOCNx register bit for that pin. For example, PORTC has register names, IOCPC and IOCNC, for these functions. Setting a value of '1' in the IOCPx register enables interrupts for low-to-high transitions, while setting a value of '1' in the IOCNx register enables interrupts for high-to-low transitions. Setting a value of '1' in both register bits will enable interrupts for either case (e.g., a pulse on the pin will generate two interrupts). In order for any IOC to be detected, the global IOC Interrupt Enable bit (IEC1<3>) must be set, the IOCON bit (PADCON<15>) set and the associated IFSx flag cleared.

When an interrupt request is generated for a pin, the corresponding status flag (IOCFx register bit) will be set, indicating that a Change-of-State occurred on that pin. The IOCFx register bit will remain set until cleared by writing a zero to it. When any IOCFx flag bit in a given port is set, the corresponding IOCPxF bit in the IOCSTAT register will be set. This flag indicates that a change was detected on one of the bits on the given port. The IOCPxF flag will be cleared when all IOCFx<15:0> bits are cleared.

Multiple individual status flags can be cleared by writing a zero to one or more bits using a Read-Modify-Write operation. If another edge is detected on a pin whose status bit is being cleared during the Read-Modify-Write sequence, the associated change flag will still be set at the end of the Read-Modify-Write sequence. The user should use the instruction sequence (or equivalent) shown in Example 11-1 to clear the Interrupt-on-Change Status registers.

At the end of this sequence, the W0 register will contain a zero for each bit for which the port pin had a change detected. In this way, any indication of a pin changing will not be lost.

Due to the asynchronous and real-time nature of the Interrupt-on-Change, the value read on the port pins may not indicate the state of the port when the change was detected, as a second change can occur during the interval between clearing the flag and reading the port. It is up to the user code to handle this case if it is a possibility in their application. To keep this interval to a minimum, it is recommended that any code modifying the IOCFx registers be run either in the interrupt handler or with interrupts disabled.

Each Interrupt-on-Change (IOC) pin has both a weak pull-up and a weak pull-down connected to it. The pullups act as a current source connected to the pin, while the pull-downs act as a current sink connected to the pin. These eliminate the need for external resistors when push button or keypad devices are connected.

The pull-ups and pull-downs are separately enabled using the IOCPUx registers (for pull-ups) and the IOCPDx registers (for pull-downs). Each IOC pin has individual control bits for its pull-up and pull-down. Setting a control bit enables the weak pull-up or pull-down for the corresponding pin.

**Note:** Pull-ups and pull-downs on pins should always be disabled whenever the pin is configured as a digital output.

#### EXAMPLE 11-1: IOC STATUS READ/CLEAR IN ASSEMBLY

| MOV | OxFFFF, WO | ; Initial mask value 0xFFFF -> W0      |

|-----|------------|----------------------------------------|

| XOR | IOCFx, W0  | ; W0 has '1' for each bit set in IOCFx |

| AND | IOCFx      | ; IOCFx & WO ->IOCFx                   |

#### EXAMPLE 11-2: PORT READ/WRITE IN ASSEMBLY

| MOV 0xFF00, W0  | ; Configure PORTB<15:8> as inputs |

|-----------------|-----------------------------------|

| MOV W0, TRISB   | ; and PORTB<7:0> as outputs       |

| NOP             | ; Delay 1 cycle                   |

| BTSS PORTB, #13 | ; Next Instruction                |

#### EXAMPLE 11-3: PORT READ/WRITE IN 'C'

| TRISB = 0xFF00;                    | // Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs |

|------------------------------------|--------------------------------------------------------------|

| Nop();                             | // Delay 1 cycle                                             |

| <pre>If (PORTBbits.RB13){ };</pre> | // Test if RB13 is a `1'                                     |

# PIC24FJ1024GA610/GB610 FAMILY

| U-0                               | U-0 | R/W-1            | R/W-1                              | R/W-1  | R/W-1                | R/W-1  | R/W-1              |  |

|-----------------------------------|-----|------------------|------------------------------------|--------|----------------------|--------|--------------------|--|

| —                                 | —   | T5CKR5           | T5CKR4                             | T5CKR3 | T5CKR2               | T5CKR1 | T5CKR0             |  |

| bit 15                            |     |                  |                                    |        |                      |        | bit 8              |  |

|                                   |     |                  |                                    |        |                      |        |                    |  |

| U-0                               | U-0 | R/W-1            | R/W-1                              | R/W-1  | R/W-1                | R/W-1  | R/W-1              |  |

| —                                 | —   | T4CKR5           | T4CKR4                             | T4CKR3 | T4CKR2               | T4CKR1 | T4CKR0             |  |

| bit 7                             |     |                  |                                    |        |                      |        | bit 0              |  |

|                                   |     |                  |                                    |        |                      |        |                    |  |

| Legend:                           |     |                  |                                    |        |                      |        |                    |  |

| R = Readable bit W = Writable bit |     | bit              | U = Unimplemented bit, read as '0' |        |                      |        |                    |  |

| -n = Value at POR '               |     | '1' = Bit is set | 1' = Bit is set                    |        | '0' = Bit is cleared |        | x = Bit is unknown |  |

|                                   |     |                  |                                    |        |                      |        |                    |  |

#### REGISTER 11-16: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| bit 15-14 | Unimplemented: Read as '0'                                            |

|-----------|-----------------------------------------------------------------------|

| bit 13-8  | T5CKR<5:0>: Assign Timer5 Clock to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                            |

| bit 5-0   | T4CKR<5:0>: Assign Timer4 Clock to Corresponding RPn or RPIn Pin bits |

#### REGISTER 11-17: RPINR5: PERIPHERAL PIN SELECT INPUT REGISTER 5

| U-0    | U-0 | r-1 | r-1 | r-1 | r-1 | r-1 | r-1   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | r-1 | r-1 | r-1 | r-1 | r-1 | r-1   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | —   | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           | r = Reserved bit |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **Reserved**: Maintain as '1'

bit 7-6 Unimplemented: Read as '0'

bit 5-0 Reserved: Maintain as '1'

### REGISTER 11-24: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| U-0     | U-0 | U-0          | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|--------------|-----|-----|-----|-----|-------|

| —       | —   | —            | —   | —   | —   | —   | —     |

| bit 15  |     |              |     |     |     |     | bit 8 |

|         |     |              |     |     |     |     |       |

| U-0     | U-0 | r-1          | r-1 | r-1 | r-1 | r-1 | r-1   |

| —       | —   | —            | —   | —   | _   | —   | _     |

| bit 7   |     |              |     |     |     |     | bit 0 |

|         |     |              |     |     |     |     |       |

| Legend: |     | r = Reserved | bit |     |     |     |       |

| Legenu.           | I – Reserved bit |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **Reserved**: Maintain as '1'

#### REGISTER 11-25: RPINR17: PERIPHERAL PIN SELECT INPUT REGISTER 17

| U-0           | U-0   | R/W-1            | R/W-1  | R/W-1                                   | R/W-1  | R/W-1  | R/W-1  |

|---------------|-------|------------------|--------|-----------------------------------------|--------|--------|--------|

| —             | —     | U3RXR5           | U3RXR4 | U3RXR3                                  | U3RXR2 | U3RXR1 | U3RXR0 |

| bit 15        |       |                  |        |                                         |        |        | bit 8  |

|               |       |                  |        |                                         |        |        |        |

| U-0           | U-0   | U-0              | U-0    | U-0                                     | U-0    | U-0    | U-0    |

|               | —     | —                | —      | —                                       | —      | —      | —      |

| bit 7         |       |                  |        |                                         |        |        | bit 0  |

|               |       |                  |        |                                         |        |        |        |

| Legend:       |       |                  |        |                                         |        |        |        |

| R = Readable  | e bit | W = Writable     | bit    | U = Unimplemented bit, read as '0'      |        |        |        |

| -n = Value at | POR   | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |        |        | nown   |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U3RXR<5:0>: Assign UART3 Receive (U3RX) to Corresponding RPn or RPIn Pin bits

bit 7-0 Unimplemented: Read as '0'

BDs have a fixed relationship to a particular endpoint, depending on the buffering configuration. Table 20-2 provides the mapping of BDs to endpoints. This relationship also means that gaps may occur in the BDT if endpoints are not enabled contiguously. This, theoretically, means that the BDs for disabled endpoints could be used as buffer space. In practice, users should avoid using such spaces in the BDT unless a method of validating BD addresses is implemented.

#### 20.2.1 BUFFER OWNERSHIP

Because the buffers and their BDs are shared between the CPU and the USB module, a simple semaphore mechanism is used to distinguish which is allowed to update the BD and associated buffers in memory. This is done by using the UOWN bit as a semaphore to distinguish which is allowed to update the BD and associated buffers in memory. UOWN is the only bit that is shared between the two configurations of BDnSTAT.

When UOWN is clear, the BD entry is "owned" by the microcontroller core. When the UOWN bit is set, the BD entry and the buffer memory are "owned" by the USB peripheral. The core should not modify the BD or its

corresponding data buffer during this time. Note that the microcontroller core can still read BDnSTAT while the SIE owns the buffer and vice versa.

The Buffer Descriptors have a different meaning based on the source of the register update. Register 20-1 and Register 20-2 show the differences in BDnSTAT depending on its current "ownership".

When UOWN is set, the user can no longer depend on the values that were written to the BDs. From this point, the USB module updates the BDs as necessary, overwriting the original BD values. The BDnSTAT register is updated by the SIE with the token PID and the transfer count is updated.

#### 20.2.2 DMA INTERFACE

The USB OTG module uses a dedicated DMA to access both the BDT and the endpoint data buffers. Since part of the address space of the DMA is dedicated to the Buffer Descriptors, a portion of the memory connected to the DMA must comprise a contiguous address space, properly mapped for the access by the module.

|          |    | BDs Assigned to Endpoint    |              |                                     |                |                                  |                |                                                       |  |

|----------|----|-----------------------------|--------------|-------------------------------------|----------------|----------------------------------|----------------|-------------------------------------------------------|--|

| Endpoint |    | Mode 0<br>(No Ping-Pong) (F |              | Mode 1<br>ng) (Ping-Pong on EP0 RX) |                | Mode 2<br>(Ping-Pong on All EPs) |                | Mode 3<br>(Ping-Pong on All Other<br>EPs, Except EP0) |  |

|          | RX | тх                          | RX           | тх                                  | RX             | тх                               | RX             | тх                                                    |  |

| 0        | 0  | 1                           | 0 (E), 1 (O) | 2                                   | 0 (E), 1 (O)   | 2 (E), 3 (O)                     | 0              | 1                                                     |  |

| 1        | 2  | 3                           | 3            | 4                                   | 4 (E), 5 (O)   | 6 (E), 7 (O)                     | 2 (E), 3 (O)   | 4 (E), 5 (O)                                          |  |

| 2        | 4  | 5                           | 5            | 6                                   | 8 (E), 9 (O)   | 10 (E), 11 (O)                   | 6 (E), 7 (O)   | 8 (E), 9 (O)                                          |  |

| 3        | 6  | 7                           | 7            | 8                                   | 12 (E), 13 (O) | 14 (E), 15 (O)                   | 10 (E), 11 (O) | 12 (E), 13 (O)                                        |  |

| 4        | 8  | 9                           | 9            | 10                                  | 16 (E), 17 (O) | 18 (E), 19 (O)                   | 14 (E), 15 (O) | 16 (E), 17 (O)                                        |  |

| 5        | 10 | 11                          | 11           | 12                                  | 20 (E), 21 (O) | 22 (E), 23 (O)                   | 18 (E), 19 (O) | 20 (E), 21 (O)                                        |  |

| 6        | 12 | 13                          | 13           | 14                                  | 24 (E), 25 (O) | 26 (E), 27 (O)                   | 22 (E), 23 (O) | 24 (E), 25 (O)                                        |  |

| 7        | 14 | 15                          | 15           | 16                                  | 28 (E), 29 (O) | 30 (E), 31 (O)                   | 26 (E), 27 (O) | 28 (E), 29 (O)                                        |  |

| 8        | 16 | 17                          | 17           | 18                                  | 32 (E), 33 (O) | 34 (E), 35 (O)                   | 30 (E), 31 (O) | 32 (E), 33 (O)                                        |  |

| 9        | 18 | 19                          | 19           | 20                                  | 36 (E), 37 (O) | 38 (E), 39 (O)                   | 34 (E), 35 (O) | 36 (E), 37 (O)                                        |  |

| 10       | 20 | 21                          | 21           | 22                                  | 40 (E), 41 (O) | 42 (E), 43 (O)                   | 38 (E), 39 (O) | 40 (E), 41 (O)                                        |  |

| 11       | 22 | 23                          | 23           | 24                                  | 44 (E), 45 (O) | 46 (E), 47 (O)                   | 42 (E), 43 (O) | 44 (E), 45 (O)                                        |  |

| 12       | 24 | 25                          | 25           | 26                                  | 48 (E), 49 (O) | 50 (E), 51 (O)                   | 46 (E), 47 (O) | 48 (E), 49 (O)                                        |  |

| 13       | 26 | 27                          | 27           | 28                                  | 52 (E), 53 (O) | 54 (E), 55 (O)                   | 50 (E), 51 (O) | 52 (E), 53 (O)                                        |  |

| 14       | 28 | 29                          | 29           | 30                                  | 56 (E), 57 (O) | 58 (E), 59 (O)                   | 54 (E), 55 (O) | 56 (E), 57 (O)                                        |  |

| 15       | 30 | 31                          | 31           | 32                                  | 60 (E), 61 (O) | 62 (E), 63 (O)                   | 58 (E), 59 (O) | 60 (E), 61 (O)                                        |  |

## TABLE 20-2: ASSIGNMENT OF BUFFER DESCRIPTORS FOR THE DIFFERENT BUFFERING MODES

**Legend:** (E) = Even transaction buffer, (O) = Odd transaction buffer

## REGISTER 21-8: PMSTAT: EPMP STATUS REGISTER (SLAVE MODE ONLY)

| R-0, HSC        | R/W-0, HS                                                                             | U-0                                                      | U-0                           | R-0, HSC                            | R-0, HSC            | R-0, HSC            | R-0, HSC            |

|-----------------|---------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|-------------------------------------|---------------------|---------------------|---------------------|

| IBF             | IBOV                                                                                  | —                                                        | —                             | IB3F <sup>(1)</sup>                 | IB2F <sup>(1)</sup> | IB1F <sup>(1)</sup> | IB0F <sup>(1)</sup> |

| bit 15          |                                                                                       |                                                          |                               |                                     |                     | •                   | bit 8               |

| <b>D</b> ( 1100 |                                                                                       |                                                          |                               | <u> </u>                            |                     | <b>D</b> ( 1100     |                     |

| R-1, HSC        | R/W-0, HS                                                                             | U-0                                                      | U-0                           | R-1, HSC                            | R-1, HSC            | R-1, HSC            | R-1, HSC            |

| OBE             | OBUF                                                                                  | —                                                        | _                             | OB3E                                | OB2E                | OB1E                | OB0E                |

| bit 7           |                                                                                       |                                                          |                               |                                     |                     |                     | bit                 |

| Legend:         |                                                                                       | HS = Hardware                                            | e Settable bit                | HSC = Hardw                         | are Settable/C      | learable bit        |                     |

| R = Readable    | e bit                                                                                 | W = Writable b                                           | oit                           | U = Unimplem                        | nented bit, read    | l as '0'            |                     |

| -n = Value at   | POR                                                                                   | '1' = Bit is set                                         |                               | '0' = Bit is clea                   | ared                | x = Bit is unkr     | nown                |

| bit 14          | <ul> <li>0 = Some or</li> <li><b>IBOV:</b> Input B</li> <li>1 = A write at</li> </ul> | Buffer Overflow Stempt to a full li                      | le Input Buffer<br>Status bit | registers are er<br>ccurred (must b |                     | oftware)            |                     |

|                 | 0 = No overfl                                                                         |                                                          |                               |                                     |                     |                     |                     |

| bit 13-12       | •                                                                                     | ted: Read as '0                                          |                               |                                     |                     |                     |                     |

| bit 11-8        | 1 = Input buff                                                                        | put Buffer x Sta<br>fer contains unr<br>fer does not cor | ead data (read                | ling the buffer w                   | ill clear this bit  | )                   |                     |

| bit 7           | 1 = All readal                                                                        | Buffer Empty Sible Output Buffer all of the readal       | er registers are              | empty<br>fer registers are          | full                |                     |                     |

| bit 6           | OBUF: Output                                                                          | ıt Buffer Underfl                                        | ow Status bit                 |                                     |                     |                     |                     |

|                 | 1 = A read or<br>0 = No under                                                         |                                                          | empty Output                  | Buffer register                     | (must be cleare     | ed in software)     |                     |

| bit 5-4         | Unimplemen                                                                            | ted: Read as '0                                          | ,                             |                                     |                     |                     |                     |

| h:+ 0 0         | -                                                                                     | Output Buffer >                                          |                               | ' bit                               |                     |                     |                     |

| bit 3-0         |                                                                                       | •                                                        |                               |                                     | clear this bit)     |                     |                     |

**Note 1:** Even though an individual bit represents the byte in the buffer, the bits corresponding to the word (Byte 0 and 1, or Byte 2 and 3) get cleared, even on byte reading.

# PIC24FJ1024GA610/GB610 FAMILY

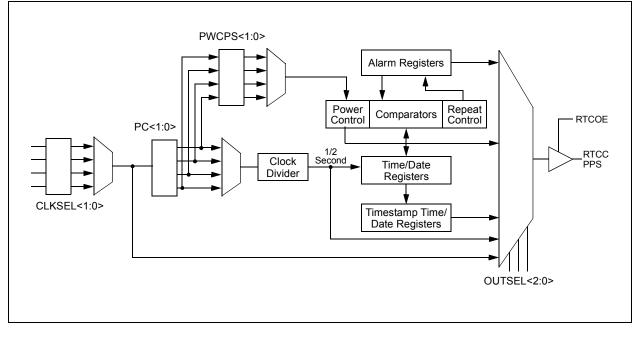

## FIGURE 22-1: RTCC BLOCK DIAGRAM

#### 22.3.3 RTCC VALUE REGISTERS

#### REGISTER 22-7: TIMEL: RTCC TIME REGISTER (LOW)

| U-0    | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

| —      | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 15 |         |         |         |         |         |         | bit 8   |

|        |         |         |         |         |         |         |         |

| U-0    | U-0     | U-0     | U-0     | U-0     | U-0     | U-0     | U-0     |

| —      | —       | —       | —       | —       | _       | —       | —       |

| bit 7  |         |         |         |         |         |         | bit 0   |

## Legend:

**—**

| Legenu.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15    | Unimplemented: Read as '0'                                         |

|-----------|--------------------------------------------------------------------|

| bit 14-12 | SECTEN<2:0>: Binary Coded Decimal Value of Seconds '10' Digit bits |

|           | Contains a value from 0 to 5.                                      |

| bit 11-8  | SECONE<3:0>: Binary Coded Decimal Value of Seconds '1' Digit bits  |

|           | Contains a value from 0 to 9.                                      |

| bit 7-0   | Unimplemented: Read as '0'                                         |

#### REGISTER 22-8: TIMEH: RTCC TIME REGISTER (HIGH)

| U-0    | U-0     | R/W-0   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|---------|---------|---------|---------|---------|---------|---------|

|        | —       | HRTEN1  | HRTEN0  | HRONE3  | HRONE2  | HRONE1  | HRONE0  |

| bit 15 |         |         |         |         |         |         | bit 8   |

|        |         |         |         |         |         |         |         |

| U-0    | R/W-0   | R/W-0   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

| _      | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 7  |         |         |         |         |         |         | bit 0   |

|        |         |         |         |         |         |         |         |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0' bit 13-12 HRTEN<1:0>: Binary Coded Decimal Value of Hours '10' Digit bits Contains a value from 0 to 2. bit 11-8 HRONE<3:0>: Binary Coded Decimal Value of Hours '1' Digit bits Contains a value from 0 to 9. bit 7 Unimplemented: Read as '0' bit 6-4 MINTEN<2:0>: Binary Coded Decimal Value of Minutes '10' Digit bits Contains a value from 0 to 5. bit 3-0 MINONE<3:0>: Binary Coded Decimal Value of Minutes '1' Digit bits Contains a value from 0 to 9.

#### 23.1 User Interface

#### 23.1.1 POLYNOMIAL INTERFACE

The CRC module can be programmed for CRC polynomials of up to the  $32^{nd}$  order, using up to 32 bits.

Polynomial length, which reflects the highest exponent in the equation, is selected by the PLEN<4:0> bits (CRCCON2<4:0>).

The CRCXORL and CRCXORH registers control which exponent terms are included in the equation. Setting a particular bit includes that exponent term in the equation. Functionally, this includes an XOR operation on the corresponding bit in the CRC engine. Clearing the bit disables the XOR.

For example, consider two CRC polynomials, one a 16-bit and the other a 32-bit equation.

#### EQUATION 23-1: 16-BIT, 32-BIT CRC POLYNOMIALS

#### X16 + X12 + X5 + 1

and

$\begin{array}{c} X32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 + \\ X8 + X7 + X5 + X4 + X2 + X + 1 \end{array}$

To program these polynomials into the CRC generator, set the register bits, as shown in Table 23-1.

Note that the appropriate positions are set to '1' to indicate that they are used in the equation (for example, X26 and X23). The '0' bit required by the equation is always XORed; thus, X0 is a don't care. For a polynomial of length 32, it is assumed that the  $32^{nd}$  bit will be used. Therefore, the X<31:1> bits do not have the  $32^{nd}$  bit.

## 23.1.2 DATA INTERFACE

The module incorporates a FIFO that works with a variable data width. Input data width can be configured to any value between 1 and 32 bits using the DWIDTH<4:0> bits (CRCCON2<12:8>). When the data width is greater than 15, the FIFO is 4 words deep. When the DWIDTHx bits are between 15 and 8, the FIFO is 8 words deep. When the DWIDTHx bits are less than 8, the FIFO is 16 words deep.

The data for which the CRC is to be calculated must first be written into the FIFO. Even if the data width is less than 8, the smallest data element that can be written into the FIFO is 1 byte. For example, if the DWIDTHx bits are 5, then the size of the data is DWIDTH<4:0> + 1 or 6. The data is written as a whole byte; the two unused upper bits are ignored by the module.

Once data is written into the MSb of the CRCDAT registers (that is, the MSb as defined by the data width), the value of the VWORD<4:0> bits (CRCCON1<12:8>) increments by one. For example, if the DWIDTHx bits are 24, the VWORDx bits will increment when bit 7 of CRCDATH is written. Therefore, CRCDATL must always be written to before CRCDATH.

The CRC engine starts shifting data when the CRCGO bit (CRCCON1<4>) is set and the value of the VWORDx bits is greater than zero.

Each word is copied out of the FIFO into a buffer register, which decrements the VWORDx bits. The data is then shifted out of the buffer. The CRC engine continues shifting at a rate of two bits per instruction cycle, until the VWORDx bits reach zero. This means that for a given data width, it takes half that number of instructions for each word to complete the calculation. For example, it takes 16 cycles to calculate the CRC for a single word of 32-bit data.

When the VWORDx bits reach the maximum value for the configured value of the DWIDTHx bits (4, 8 or 16), the CRCFUL bit (CRCCON1<7>) becomes set. When the VWORDx bits reach zero, the CRCMPT bit (CRCCON1<6>) becomes set. The FIFO is emptied and the VWORD<4:0> bits are set to '00000' whenever CRCEN is '0'.

At least one instruction cycle must pass after a write to CRCWDAT before a read of the VWORDx bits is done.

#### TABLE 23-1: CRC SETUP EXAMPLES FOR 16 AND 32-BIT POLYNOMIALS

| CRC Control Bits | Bit Values          |                     |  |  |  |

|------------------|---------------------|---------------------|--|--|--|

|                  | 16-Bit Polynomial   | 32-Bit Polynomial   |  |  |  |

| PLEN<4:0>        | 01111               | 11111               |  |  |  |

| X<31:16>         | 0000 0000 0000 0001 | 0000 0100 1100 0001 |  |  |  |

| X<15:1>          | 0001 0000 0010 000  | 0001 1101 1011 011  |  |  |  |

## REGISTER 24-5: CLCxGLSH: CLCx GATE LOGIC INPUT SELECT HIGH REGISTER (CONTINUED)

| bit 3 | G3D2T: Gate 3 Data Source 2 True Enable bit                  |

|-------|--------------------------------------------------------------|

|       | 1 = The Data Source 2 signal is enabled for Gate 3           |

|       | 0 = The Data Source 2 signal is disabled for Gate 3          |

| bit 2 | G3D2N: Gate 3 Data Source 2 Negated Enable bit               |

|       | 1 = The Data Source 2 inverted signal is enabled for Gate 3  |

|       | 0 = The Data Source 2 inverted signal is disabled for Gate 3 |

| bit 1 | G3D1T: Gate 3 Data Source 1 True Enable bit                  |

|       | 1 = The Data Source 1 signal is enabled for Gate 3           |

|       | 0 = The Data Source 1 signal is disabled for Gate 3          |

| bit 0 | G3D1N: Gate 3 Data Source 1 Negated Enable bit               |

|       |                                                              |

|       | 1 = The Data Source 1 inverted signal is enabled for Gate 3  |

#### REGISTER 26-1: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 THROUGH 3)

| R/W-0            | R/W-0                                                                                                                                                                                                                                                                | R/W-0                                                                                                                            | U-0                                                                      | U-0                                    | U-0            | R/W-0, HS     | R-0, HSC     |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------|----------------|---------------|--------------|--|

| CEN              | COE                                                                                                                                                                                                                                                                  | CPOL                                                                                                                             | _                                                                        | —                                      |                | CEVT          | COUT         |  |

| bit 15           |                                                                                                                                                                                                                                                                      |                                                                                                                                  |                                                                          |                                        |                |               | bit 8        |  |

|                  |                                                                                                                                                                                                                                                                      |                                                                                                                                  |                                                                          |                                        |                |               |              |  |

| R/W-0            | R/W-0                                                                                                                                                                                                                                                                | U-0                                                                                                                              | R/W-0                                                                    | U-0                                    | U-0            | R/W-0         | R/W-0        |  |

| EVPOL1           | EVPOL0                                                                                                                                                                                                                                                               | —                                                                                                                                | CREF                                                                     |                                        |                | CCH1          | CCH0         |  |

| bit 7            |                                                                                                                                                                                                                                                                      |                                                                                                                                  |                                                                          |                                        |                |               | bit 0        |  |

|                  |                                                                                                                                                                                                                                                                      |                                                                                                                                  |                                                                          |                                        |                |               |              |  |

| Legend:          |                                                                                                                                                                                                                                                                      | HS = Hardware                                                                                                                    | Settable bit                                                             | HSC = Hardv                            | vare Settable/ | Clearable bit |              |  |

| R = Readable     | e bit                                                                                                                                                                                                                                                                | W = Writable b                                                                                                                   | it                                                                       | U = Unimpler                           | mented bit, re | ad as '0'     |              |  |

| -n = Value at    | POR                                                                                                                                                                                                                                                                  | '1' = Bit is set                                                                                                                 |                                                                          | '0' = Bit is cleared x = Bit is unknow |                |               |              |  |

| bit 15<br>bit 14 | 1 = Compara<br>0 = Compara<br><b>COE:</b> Compa                                                                                                                                                                                                                      | ator Enable bit<br>ator is enabled<br>ator is disabled<br>arator Output Ena<br>ator output is pre                                |                                                                          | OLIT nin                               |                |               |              |  |

| bit 13           | <ul> <li>1 = Comparator output is present on the CxOUT pin</li> <li>0 = Comparator output is internal only</li> <li>CPOL: Comparator Output Polarity Select bit</li> <li>1 = Comparator output is inverted</li> <li>0 = Comparator output is not inverted</li> </ul> |                                                                                                                                  |                                                                          |                                        |                |               |              |  |

| bit 12-10        | Unimplemen                                                                                                                                                                                                                                                           | ted: Read as '0'                                                                                                                 |                                                                          |                                        |                |               |              |  |

| bit 9            | CEVT: Comp                                                                                                                                                                                                                                                           | CEVT: Comparator Event bit                                                                                                       |                                                                          |                                        |                |               |              |  |