Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gb610-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC24FJ1024GA610/GB610 FAMILY PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. Their pinout diagrams appear on the following pages.

|                  | Mem                | ory             | Pi    | ns  | A                  | nalo       | g    |                 |            |           | Dig              | ital |                          |           |     |      |         |

|------------------|--------------------|-----------------|-------|-----|--------------------|------------|------|-----------------|------------|-----------|------------------|------|--------------------------|-----------|-----|------|---------|

| Device           | Program<br>(bytes) | Data<br>(bytes) | Total | 0/1 | 10/12-Bit A/D (ch) | Comparator | CTMU | 16/32-Bit Timer | IC/OC/PWIM | MCCP/SCCP | I <sup>2</sup> C | IdS  | UART w/IrDA <sup>®</sup> | EPMP/EPSP | СГС | RTCC | USB OTG |

| PIC24FJ128GA606  | 128K               | 32K             | 64    | 53  | 16                 | 3          | Y    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Ν       |

| PIC24FJ256GA606  | 256K               | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Ν       |

| PIC24FJ512GA606  | 512K               | 32K             | 64    | 53  | 16                 | 3          | Y    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Ν       |

| PIC24FJ1024GA606 | 1024K              | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Y    | Ν       |

| PIC24FJ128GA610  | 128K               | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Ν       |

| PIC24FJ256GA610  | 256K               | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Υ    | Ν       |

| PIC24FJ512GA610  | 512K               | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Ν       |

| PIC24FJ1024GA610 | 1024K              | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Ν       |

| PIC24FJ128GB606  | 128K               | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Υ       |

| PIC24FJ256GB606  | 256K               | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Υ       |

| PIC24FJ512GB606  | 512K               | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Υ       |

| PIC24FJ1024GB606 | 1024K              | 32K             | 64    | 53  | 16                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Υ       |

| PIC24FJ128GB610  | 128K               | 32K             | 100   | 85  | 24                 | 3          | Y    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Y       |

| PIC24FJ256GB610  | 256K               | 32K             | 100   | 85  | 24                 | 3          | Υ    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Υ    | Υ       |

| PIC24FJ512GB610  | 512K               | 32K             | 100   | 85  | 24                 | 3          | Y    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Y         | 4   | Y    | Y       |

| PIC24FJ1024GB610 | 1024K              | 32K             | 100   | 85  | 24                 | 3          | Y    | 5/2             | 6/6        | 3/4       | 3                | 3    | 6/2                      | Υ         | 4   | Y    | Y       |

## TABLE 1: PIC24FJ1024GA610/GB610 GENERAL PURPOSE FAMILIES

# 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and buses. This architecture also allows direct access of program memory from the Data Space during code execution.

## 4.1 **Program Memory Space**

The program address memory space of the PIC24FJ1024GA610/GB610 family devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or Data Space remapping, as described in **Section 4.3** "Interfacing Program and Data Memory Spaces".

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and customer OTP sections of the configuration memory space.

The PIC24FJ1024GA610/GB610 family of devices supports a Single Partition mode and two Dual Partition modes. The Dual Partition modes allow the device to be programmed with two separate applications to facilitate bootloading or to allow an application to be programmed at run time without stalling the CPU.

Memory maps for the PIC24FJ1024GA610/GB610 family of devices are shown in Figure 4-1.

#### 7.4.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, <u>one or more of the following conditions</u> is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 7.4.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC Oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

| R/W-1        | R-0                                                                                            | R/W-0                                                               | U-0            | U-0              | U-0               | U-0            | R/W-0          |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------|------------------|-------------------|----------------|----------------|--|--|--|--|

| GIE          | DISI                                                                                           | SWTRAP                                                              | —              |                  | _                 |                | AIVTEN         |  |  |  |  |

| bit 15       | <u>ң</u>                                                                                       |                                                                     |                |                  |                   |                | bit 8          |  |  |  |  |

|              |                                                                                                |                                                                     | <b>D</b> 444 0 | <b>D</b> 444 0   | <b>D</b> 444 A    | DAMA           | <b>D</b> 444 0 |  |  |  |  |

| U-0          | U-0                                                                                            | U-0                                                                 | R/W-0          | R/W-0            | R/W-0             | R/W-0          | R/W-0          |  |  |  |  |

|              |                                                                                                | —                                                                   | INT4EP         | INT3EP           | INT2EP            | INT1EP         | INT0EP         |  |  |  |  |

| bit 7        |                                                                                                |                                                                     |                |                  |                   |                | bit (          |  |  |  |  |

| Legend:      |                                                                                                |                                                                     |                |                  |                   |                |                |  |  |  |  |

| R = Readab   | e bit                                                                                          | W = Writable                                                        | bit            | U = Unimplen     | nented bit, read  | l as '0'       |                |  |  |  |  |

| -n = Value a | POR                                                                                            | '1' = Bit is set                                                    |                | '0' = Bit is cle | ared              | x = Bit is unk | nown           |  |  |  |  |

|              |                                                                                                |                                                                     |                |                  |                   |                |                |  |  |  |  |

| bit 15       |                                                                                                | Interrupt Enable                                                    |                |                  |                   |                |                |  |  |  |  |

|              |                                                                                                | ts and associate<br>ts are disabled, I                              | •              |                  | abled             |                |                |  |  |  |  |

| bit 14       | •                                                                                              |                                                                     | •              |                  |                   |                |                |  |  |  |  |

|              |                                                                                                | DISI: DISI Instruction Status bit<br>1 = DISI instruction is active |                |                  |                   |                |                |  |  |  |  |

|              | 0 = DISI in                                                                                    | struction is not a                                                  | ctive          |                  |                   |                |                |  |  |  |  |

| bit 13       | SWTRAP: S                                                                                      | Software Trap St                                                    | atus bit       |                  |                   |                |                |  |  |  |  |

|              |                                                                                                | e trap is enabled<br>e trap is disabled                             |                |                  |                   |                |                |  |  |  |  |

| bit 12-9     |                                                                                                | ented: Read as '                                                    |                |                  |                   |                |                |  |  |  |  |

| bit 8        | AIVTEN: Alternate Interrupt Vector Table Enable bit                                            |                                                                     |                |                  |                   |                |                |  |  |  |  |

|              |                                                                                                | ernate Interrupt \<br>ndard Interrupt \                             |                |                  | onfiguration bits | )              |                |  |  |  |  |

| bit 7-5      | Unimpleme                                                                                      | ented: Read as '                                                    | 0'             |                  |                   |                |                |  |  |  |  |

| bit 4        | INT4EP: Ex                                                                                     | INT4EP: External Interrupt 4 Edge Detect Polarity Select bit        |                |                  |                   |                |                |  |  |  |  |

|              |                                                                                                | t on negative ed<br>t on positive edg                               | •              |                  |                   |                |                |  |  |  |  |

| bit 3        | •                                                                                              |                                                                     |                | Polarity Select  | bit               |                |                |  |  |  |  |

|              | INT3EP: External Interrupt 3 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge |                                                                     |                |                  |                   |                |                |  |  |  |  |

|              |                                                                                                | 0 = Interrupt on positive edge                                      |                |                  |                   |                |                |  |  |  |  |

| bit 2        |                                                                                                | ternal Interrupt 2                                                  |                | Polarity Select  | bit               |                |                |  |  |  |  |

|              |                                                                                                | t on negative edg<br>t on positive edg                              |                |                  |                   |                |                |  |  |  |  |

| bit 1        | INT1EP: Ex                                                                                     | <b>INT1EP:</b> External Interrupt 1 Edge Detect Polarity Select bit |                |                  |                   |                |                |  |  |  |  |

|              |                                                                                                | t on negative ed<br>t on positive edg                               |                |                  |                   |                |                |  |  |  |  |

| bit 0        | -                                                                                              | ternal Interrupt (                                                  |                | Polarity Select  | bit               |                |                |  |  |  |  |

|              |                                                                                                | t on negative ed                                                    | -              |                  |                   |                |                |  |  |  |  |

#### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER 2

# PIC24FJ1024GA610/GB610 FAMILY

| U-0          | U-0                                                                                                                                                                                                                       | U-0                                                       | U-0 | U-0               | U-0              | U-0            | U-0                  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----|-------------------|------------------|----------------|----------------------|

|              | —                                                                                                                                                                                                                         | —                                                         |     | —                 | _                | _              | _                    |

| bit 15       |                                                                                                                                                                                                                           |                                                           |     |                   |                  |                | bit 8                |

|              |                                                                                                                                                                                                                           |                                                           |     |                   |                  |                |                      |

| U-0          | U-0                                                                                                                                                                                                                       | R/W-0                                                     | U-0 | R/W-0             | R/W-0            | R/W-0          | R/W-0                |

| —            | —                                                                                                                                                                                                                         | U4MD                                                      | —   | REFOMD            | CTMUMD           | LVDMD          | USBMD <sup>(1)</sup> |

| bit 7        |                                                                                                                                                                                                                           |                                                           |     |                   |                  |                | bit C                |

| Legend:      |                                                                                                                                                                                                                           |                                                           |     |                   |                  |                |                      |

| R = Readat   | ole bit                                                                                                                                                                                                                   | W = Writable b                                            | oit | U = Unimplem      | nented bit, read | l as '0'       |                      |

| -n = Value a | at POR                                                                                                                                                                                                                    | '1' = Bit is set                                          |     | '0' = Bit is clea | ared             | x = Bit is unk | nown                 |

| bit 4        |                                                                                                                                                                                                                           | is disabled<br>power and clock<br><b>nted:</b> Read as '0 |     | enabled           |                  |                |                      |

| bit 3        | 1 = Module                                                                                                                                                                                                                | Reference Output<br>is disabled<br>power and clock        |     |                   |                  |                |                      |

| bit 2        | 1 = Module                                                                                                                                                                                                                | CTMU Module Di<br>is disabled<br>power and clock          |     | enabled           |                  |                |                      |

| bit 1        | 1 = Module                                                                                                                                                                                                                |                                                           |     |                   |                  |                |                      |

| bit 0        | <ul> <li>0 = Module power and clock sources are enabled</li> <li>USBMD: USB On-The-Go Module Disable bit<sup>(1)</sup></li> <li>1 = Module is disabled</li> <li>0 = Module power and clock sources are enabled</li> </ul> |                                                           |     |                   |                  |                |                      |

### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE REGISTER 4

**Note 1:** USB is not present on PIC24FJXXXXGA6XX devices.

#### **REGISTER 11-9:** IOCPX: INTERRUPT-ON-CHANGE POSITIVE EDGE x REGISTER<sup>(1,2)</sup>

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | U-0   |  |  |

|--------------|-------|------------------|-------|------------------------------------|-------|-------|-------|--|--|

|              |       |                  | IOCP  | x<15:8>                            |       |       |       |  |  |

| bit 15       |       |                  |       |                                    |       |       | bit 8 |  |  |

|              |       |                  |       |                                    |       |       |       |  |  |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|              |       |                  | IOCF  | Px<7:0>                            |       |       |       |  |  |

| bit 7        |       |                  |       |                                    |       |       | bit 0 |  |  |

|              |       |                  |       |                                    |       |       |       |  |  |

| Legend:      |       |                  |       |                                    |       |       |       |  |  |

| R = Readable | e bit | W = Writable bit |       | U = Unimplemented bit, read as '0' |       |       |       |  |  |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **IOCPx<15:0>:** Interrupt-on-Change Positive Edge x Enable bits

- 1 = Interrupt-on-Change is enabled on the IOCx pin for a positive going edge; the associated status bit and interrupt flag will be set upon detecting an edge

- 0 = Interrupt-on-Change is disabled on the IOCx pin for a positive going edge

- **Note 1:** Setting both IOCPx and IOCNx will enable the IOCx pin for both edges, while clearing both registers will disable the functionality.

- 2: Changing the value of this register while the module is enabled (IOCON = 1) may cause a spurious IOC event. The corresponding interrupt must be ignored, cleared (using IOCFx) or masked (within the interrupt controller), or this module must be enabled (IOCON = 0) when changing this register.

## **REGISTER 11-10: IOCNX: INTERRUPT-ON-CHANGE NEGATIVE EDGE x REGISTER**<sup>(1,2)</sup>

| R/W-0  | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | U-0   |  |  |  |

|--------|------------|-------|-------|--------|-------|-------|-------|--|--|--|

|        |            |       | IOCN× | <15:8> |       |       |       |  |  |  |

| bit 15 |            |       |       |        |       |       | bit 8 |  |  |  |

|        |            |       |       |        |       |       |       |  |  |  |

| R/W-0  | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|        | IOCNx<7:0> |       |       |        |       |       |       |  |  |  |

| bit 7  |            |       |       |        |       |       | bit 0 |  |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-0 IOCNx<15:0>: Interrupt-on-Change Negative Edge x Enable bits

- 1 = Interrupt-on-Change is enabled on the IOCx pin for a negative going edge; the associated status bit and interrupt flag will be set upon detecting an edge

- 0 = Interrupt-on-Change is disabled on the IOCx pin for a negative going edge

- **Note 1:** Setting both IOCPx and IOCNx will enable the IOCx pin for both edges, while clearing both registers will disable the functionality.

- 2: Changing the value of this register while the module is enabled (IOCON = 1) may cause a spurious IOC event. The corresponding interrupt must be ignored, cleared (using IOCFx) or masked (within the interrupt controller), or this module must be enabled (IOCON = 0) when changing this register.

# REGISTER 11-11: IOCFx: INTERRUPT-ON-CHANGE FLAG x REGISTER<sup>(1)</sup>

| R/W-0                             | R/W-0                             | R/W-0            | R/W-0 | R/W-0                                | R/W-0 | R/W-0 | U-0   |  |  |

|-----------------------------------|-----------------------------------|------------------|-------|--------------------------------------|-------|-------|-------|--|--|

|                                   |                                   |                  | IOCF  | <sup>-</sup> x<15:8>                 |       |       |       |  |  |

| bit 15                            |                                   |                  |       |                                      |       |       | bit 8 |  |  |

| r                                 |                                   |                  |       |                                      |       |       |       |  |  |

| R/W-0                             | R/W-0                             | R/W-0            | R/W-0 | R/W-0                                | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                   |                                   |                  | IOC   | Fx<7:0>                              |       |       |       |  |  |

| bit 7                             |                                   |                  |       |                                      |       |       | bit 0 |  |  |

|                                   |                                   |                  |       |                                      |       |       |       |  |  |

| Legend:                           |                                   |                  |       |                                      |       |       |       |  |  |

| R = Readable                      | R = Readable bit W = Writable bit |                  | t     | U = Unimplemented bit, read as '0'   |       |       |       |  |  |

| -n = Value at POR '1' = Bit is se |                                   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unkr |       |       | nown  |  |  |

bit 15-0 **IOCFx<15:0>:** Interrupt-on-Change Flag x bits

- 1 = An enabled change was detected on the associated pin; set when IOCPx = 1 and a positive edge was detected on the IOCx pin, or when IOCNx = 1 and a negative edge was detected on the IOCx pin

0 = No change was detected or the user cleared the detected change

- **Note 1:** It is not possible to set the IOCFx register bits with software writes (as this would require the addition of significant logic). To test IOC interrupts, it is recommended to enable the IOC functionality on one or more GPIO pins and then use the corresponding LATx register bit(s) to trigger an IOC interrupt.

| U-0    | U-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|--------|-----|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

|        | —   | RP5R5 <sup>(1)</sup> | RP5R4 <sup>(1)</sup> | RP5R3 <sup>(1)</sup> | RP5R2 <sup>(1)</sup> | RP5R1 <sup>(1)</sup> | RP5R0 <sup>(1)</sup> |

| bit 15 |     |                      |                      |                      |                      |                      | bit 8                |

|        |     |                      |                      |                      |                      |                      |                      |

| U-0    | U-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

| _      | —   | RP4R5                | RP4R4                | RP4R3                | RP4R2                | RP4R1                | RP4R0                |

| bit 7  |     |                      |                      |                      |                      |                      | bit 0                |

#### REGISTER 11-38: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| Legend:           |                  |                                                     |                    |  |  |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP5R<5:0>: RP5 Output Pin Mapping bits <sup>(1)</sup>                                                |

|           | Peripheral Output Number n is assigned to pin, RP5 (see Table 11-4 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | RP4R<5:0>: RP4 Output Pin Mapping bits                                                               |

|           | Peripheral Output Number n is assigned to pin, RP4 (see Table 11-4 for peripheral function numbers). |

**Note 1:** This pin is not available on 64-pin devices.

## REGISTER 11-39: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|-------|-------|-------|

| _      | _   | RP7R5 | RP7R4 | RP7R3 | RP7R2 | RP7R1 | RP7R0 |

| bit 15 |     |       |       |       |       |       | bit 8 |

|        |     |       |       |       |       |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —      | —   | RP6R5 | RP6R4 | RP6R3 | RP6R2 | RP6R1 | RP6R0 |

| bit 7  | •   |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP7R<5:0>: RP7 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP7 (see Table 11-4 for peripheral function numbers).

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP6R<5:0>:** RP6 Output Pin Mapping bits Peripheral Output Number n is assigned to pin, RP6 (see Table 11-4 for peripheral function numbers).

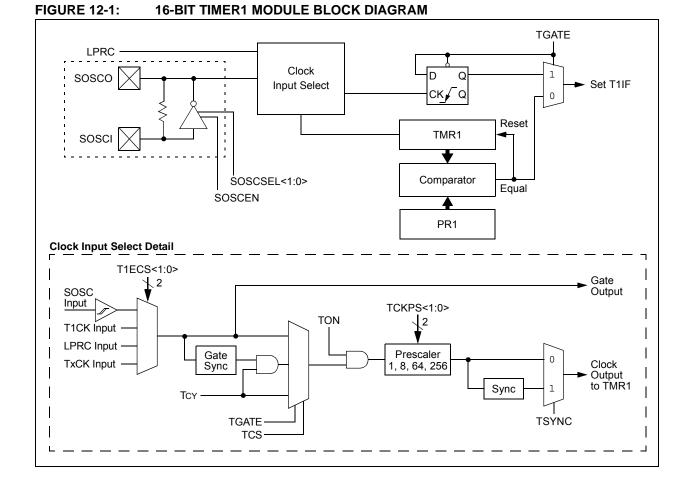

# 12.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, *"Timers"* (DS39704), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the Real-Time Clock (RTC) or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Clear the TON bit (= 0).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS, TECS<1:0> and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

- 7. Set the TON bit (= 1).

© 2015-2016 Microchip Technology Inc.

| R/W-0      | R/W-0                                 | R/W-0                                | R/W-0                                                                                                                                                    | U-0                              | R/W-0               | R/W-0               | R/W-0         |

|------------|---------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------|---------------------|---------------|

| FLTMD      | FLTOUT                                | FLTTRIEN                             | OCINV                                                                                                                                                    | —                                | DCB1 <sup>(3)</sup> | DCB0 <sup>(3)</sup> | OC32          |

| bit 15     |                                       |                                      |                                                                                                                                                          |                                  |                     |                     | bit 8         |

|            |                                       | <b>D</b> 444 0                       | <b>D</b> 444 0                                                                                                                                           | <b>D</b> 444 4                   | <b>D</b> 444 4      | <b>D</b> 444 0      |               |

| R/W-0      | R/W-0, HS                             | R/W-0                                | R/W-0                                                                                                                                                    | R/W-1                            | R/W-1               | R/W-0               | R/W-0         |

| OCTRIG     | TRIGSTAT                              | OCTRIS                               | SYNCSEL4                                                                                                                                                 | SYNCSEL3                         | SYNCSEL2            | SYNCSEL1            | SYNCSEL0      |

| bit 7      |                                       |                                      |                                                                                                                                                          |                                  |                     |                     | bit C         |

| Legend:    |                                       | HS = Hardwa                          | re Settable bit                                                                                                                                          |                                  |                     |                     |               |

| R = Reada  | ble bit                               | W = Writable                         |                                                                                                                                                          | U = Unimplem                     | nented bit, read    | l as '0'            |               |

| -n = Value | at POR                                | '1' = Bit is set                     |                                                                                                                                                          | '0' = Bit is clea                |                     | x = Bit is unkn     | iown          |

|            |                                       |                                      |                                                                                                                                                          |                                  |                     |                     | -             |

| bit 15     | FLTMD: Fault                          | t Mode Select b                      | oit                                                                                                                                                      |                                  |                     |                     |               |

|            |                                       | de is maintaine<br>n software        | ed until the Fau                                                                                                                                         | It source is ren                 | noved and the       | corresponding       | OCFLT0 bit is |

|            |                                       |                                      | d until the Fau                                                                                                                                          | t source is rem                  | oved and a ne       | w PWM period        | starts        |

| bit 14     | FLTOUT: Fau                           | lt Out bit                           |                                                                                                                                                          |                                  |                     |                     |               |

|            |                                       | tput is driven hi                    | •                                                                                                                                                        |                                  |                     |                     |               |

|            | 0 = PWM out                           | tput is driven lo                    | w on a Fault                                                                                                                                             |                                  |                     |                     |               |

| bit 13     |                                       | ault Output Sta                      |                                                                                                                                                          |                                  |                     |                     |               |

|            |                                       |                                      | ut on a Fault co<br>fected by a Fau                                                                                                                      |                                  |                     |                     |               |

| bit 12     | OCINV: OCM                            | P Invert bit                         |                                                                                                                                                          |                                  |                     |                     |               |

|            | 1 = OCx outp 0 = OCx outp             | out is inverted<br>out is not invert | ed                                                                                                                                                       |                                  |                     |                     |               |

| bit 11     | Unimplemen                            | ted: Read as '                       | o'                                                                                                                                                       |                                  |                     |                     |               |

| bit 10-9   | DCB<1:0>: P                           | WM Duty Cycl                         | e Least Signific                                                                                                                                         | ant bits <sup>(3)</sup>          |                     |                     |               |

|            | 10 = Delay O<br>01 = Delay O          | Cx falling edge<br>Cx falling edge   | by <sup>3</sup> ⁄ <sub>4</sub> of the ins<br>by <sup>1</sup> ⁄ <sub>2</sub> of the ins<br>by <sup>1</sup> ⁄ <sub>4</sub> of the ins<br>s at the start of | struction cycle                  | cycle               |                     |               |

| bit 8      | OC32: Casca                           | de Two OC Mo                         | odules Enable b                                                                                                                                          | oit (32-bit opera                | ition)              |                     |               |

|            |                                       | module operat                        |                                                                                                                                                          |                                  |                     |                     |               |

| bit 7      | OCTRIG: OC                            | x Trigger/Sync                       | Select bit                                                                                                                                               |                                  |                     |                     |               |

|            |                                       |                                      |                                                                                                                                                          | ted by the SYN<br>ignated by the |                     | S                   |               |

| bit 6      |                                       | imer Trigger St                      |                                                                                                                                                          |                                  |                     |                     |               |

|            |                                       |                                      | triggered and is<br>en triggered a                                                                                                                       | s running<br>nd is being held    | d clear             |                     |               |

| bit 5      |                                       |                                      | irection Select                                                                                                                                          | •                                |                     |                     |               |

|            | 1 = OCx pin is                        | -                                    |                                                                                                                                                          |                                  |                     |                     |               |

|            |                                       |                                      | ral x is connect                                                                                                                                         | ed to an OCx p                   | pin                 |                     |               |

|            | Never use an Out<br>another equivaler |                                      |                                                                                                                                                          | own Trigger so                   | urce, either by     | selecting this r    | node or       |

|            | Use these inputs                      |                                      | -                                                                                                                                                        | ever as Sync s                   | ources.             |                     |               |

|            | -                                     |                                      | -                                                                                                                                                        | -                                |                     |                     |               |

### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

## REGISTER 17-4: SPIxSTATL: SPIx STATUS REGISTER LOW (CONTINUED)

- bit 2 Unimplemented: Read as '0' bit 1 SPITBF: SPIx Transmit Buffer Full Status bit 1 = SPIxTXB is full 0 = SPIxTXB not full Standard Buffer Mode: Automatically set in hardware when SPIxBUF is written, loading SPIxTXB. Automatically cleared in hardware when SPIx transfers data from SPIxTXB to SPIxTXSR. Enhanced Buffer Mode: Indicates TXELM<5:0> = 6'b111111. bit 0 SPIRBF: SPIx Receive Buffer Full Status bit 1 = SPIxRXB is full 0 = SPIxRXB is not full Standard Buffer Mode: Automatically set in hardware when SPIx transfers data from SPIxRXSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB. Enhanced Buffer Mode: Indicates RXELM<5:0> = 6'b111111.

- **Note 1:** SPITUR is cleared when SPIEN = 0. When IGNTUR = 1, SPITUR provides dynamic status of the Transmit Underrun condition, but does not stop RX/TX operation and does not need to be cleared by software.

# 20.0 UNIVERSAL SERIAL BUS WITH ON-THE-GO SUPPORT (USB OTG)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "USB On-The-Go (OTG)" (DS39721), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

PIC24FJ1024GB610 family devices contain a fullspeed and low-speed compatible, On-The-Go (OTG) USB Serial Interface Engine (SIE). The OTG capability allows the device to act as either a USB peripheral device or as a USB embedded host with limited host capabilities. The OTG capability allows the device to dynamically switch from device to host operation using OTG's Host Negotiation Protocol (HNP).

For more details on OTG operation, refer to the "On-The-Go Supplement" to the "USB 2.0 Specification", published by the USB-IF. For more details on USB operation, refer to the "Universal Serial Bus Specification", v2.0.

The USB OTG module offers these features:

- USB Functionality in Device and Host modes, and OTG Capabilities for Application-Controlled mode Switching

- Software-Selectable module Speeds of Full Speed (12 Mbps) or Low Speed (1.5 Mbps available in Host mode only)

- Support for All Four USB Transfer Types: Control, Interrupt, Bulk and Isochronous

- 16 Bidirectional Endpoints for a Total of 32 Unique Endpoints

- DMA Interface for Data RAM Access

- Queues up to 16 Unique Endpoint Transfers without Servicing

- Integrated, On-Chip USB Transceiver with Support for Off-Chip Transceivers via a Digital Interface

- Integrated VBUS Generation with On-Chip Comparators and Boost Generation, and Support of External VBUS Comparators and Regulators through a Digital Interface

- Configurations for On-Chip Bus Pull-up and Pull-Down Resistors

A simplified block diagram of the USB OTG module is shown in Figure 20-1.

The USB OTG module can function as a USB peripheral device or as a USB host, and may dynamically switch between Device and Host modes under software control. In either mode, the same data paths and Buffer Descriptors (BDs) are used for the transmission and reception of data.

In discussing USB operation, this section will use a controller-centric nomenclature for describing the direction of the data transfer between the microcontroller and the USB. RX (Receive) will be used to describe transfers that move data from the USB to the microcontroller and TX (Transmit) will be used to describe transfers that move data from the microcontroller to the USB. Table 20-1 shows the relationship between data direction in this nomenclature and the USB tokens exchanged.

#### TABLE 20-1: CONTROLLER-CENTRIC DATA DIRECTION FOR USB HOST OR TARGET

| USB Mode | Direction    |              |  |  |  |

|----------|--------------|--------------|--|--|--|

| USB WOUL | RX           | тх           |  |  |  |

| Device   | OUT or SETUP | IN           |  |  |  |

| Host     | IN           | OUT or SETUP |  |  |  |

This chapter presents the most basic operations needed to implement USB OTG functionality in an application. A complete and detailed discussion of the USB protocol and its OTG supplement are beyond the scope of this data sheet. It is assumed that the user already has a basic understanding of USB architecture and the latest version of the protocol.

Not all steps for proper USB operation (such as device enumeration) are presented here. It is recommended that application developers use an appropriate device driver to implement all of the necessary features. Microchip provides a number of application-specific resources, such as USB firmware and driver support. Refer to www.microchip.com/usb for the latest firmware and driver support.

#### 20.1.3 CALCULATING TRANSCEIVER POWER REQUIREMENTS

The USB transceiver consumes a variable amount of current depending on the characteristic impedance of the USB cable, the length of the cable, the VUSB supply voltage and the actual data patterns moving across the USB cable. Longer cables have larger capacitances and consume more total energy when switching output states. The total transceiver current consumption will be application-specific. Equation 20-1 can help estimate how much current actually may be required in full-speed applications.

Refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"USB On-The-Go (OTG)**" (DS39721) for a complete discussion on transceiver power consumption.

## EQUATION 20-1: ESTIMATING USB TRANSCEIVER CURRENT CONSUMPTION

| IXCVR =  | 40 mA • VUSB • PZERO • PIN • LCABLE | + IPULLUP |

|----------|-------------------------------------|-----------|

| IAC VK – | 3.3V • 5m                           | + IPULLUP |

**Legend:** VUSB – Voltage applied to the VUSB3V3 pin in volts (3.0V to 3.6V).

PZERO – Percentage (in decimal) of the IN traffic bits sent by the PIC<sup>®</sup> microcontroller that are a value of '0'.

PIN – Percentage (in decimal) of total bus bandwidth that is used for IN traffic.

LCABLE – Length (in meters) of the USB cable. The "USB 2.0 Specification" requires that full-speed applications use cables no longer than 5m.

IPULLUP – Current which the nominal, 1.5 k $\Omega$  pull-up resistor (when enabled) must supply to the USB cable.

# 22.0 REAL-TIME CLOCK AND CALENDAR WITH TIMESTAMP

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Real-Time Clock and Calendar, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"RTCC with Timestamp"** (DS70005193), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The RTCC provides the user with a Real-Time Clock and Calendar (RTCC) function that can be calibrated.

Key features of the RTCC module are:

- Selectable Clock Source

- Provides Hours, Minutes and Seconds Using 24-Hour Format

- · Visibility of One Half Second Period

- Provides Calendar Weekday, Date, Month and Year

- Alarm-Configurable for Half a Second, 1 Second, 10 Seconds, 1 Minute, 10 Minutes, 1 Hour, 1 Day, 1 Week, 1 Month or 1 Year

- Alarm Repeat with Decrementing Counter

- Alarm with Indefinite Repeat Chime

- Year 2000 to 2099 Leap Year Correction

- BCD Format for Smaller Software Overhead

- Optimized for Long-Term Battery Operation

- User Calibration of the 32.768 kHz Clock Crystal/ 32K INTRC Frequency with Periodic Auto-Adjust

- Fractional Second Synchronization

- Calibration to within ±2.64 Seconds Error per Month

- Calibrates up to 260 ppm of Crystal Error

- Ability to Periodically Wake-up External Devices without CPU Intervention (external power control)

- Power Control Output for External Circuit Control

- Calibration takes Effect Every 15 Seconds

- Timestamp Capture Register for Time and Date

- Programmable Prescaler and Clock Divider Circuit Allows Operation with Any Clock Source up to 32 MHz, Including 32.768 kHz Crystal, 50/60 Hz Powerline Clock, External Real-Time Clock (RTC) or 31.25 kHz LPRC Clock

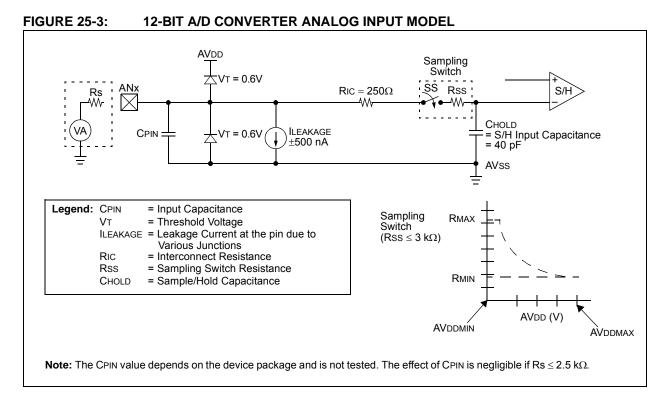

# 22.1 RTCC Source Clock

The RTCC clock divider block converts the incoming oscillator source into accurate 1/2 and 1 second clocks for the RTCC. The clock divider is optimized to work with three different oscillator sources:

- 32.768 kHz Crystal Oscillator

- 31 kHz Low-Power RC Oscillator (LPRC)

- External 50 Hz or 60 Hz Powerline Frequency

An asynchronous prescaler, PS<1:0> (RTCCON2L<5:4>), is provided that allows the RTCC to work with higher speed clock sources, such as the system clock. Divide ratios of 1:16, 1:64 or 1:256 may be selected, allowing sources up to 32 MHz to clock the RTCC.

#### 22.1.1 COARSE FREQUENCY DIVISION

The clock divider block has a 16-bit counter used to divide the input clock frequency. The divide ratio is set by the DIV<15:0> register bits (RTCCON2H<15:0>). The DIV<15:0> bits should be programmed with a value to produce a nominal 1/2 second clock divider count period.

## 22.1.2 FINE FREQUENCY DIVISION

The fine frequency division is set using the FDIV<4:0> (RTCCON2L<15:11>) bits. Increasing the FDIVx value will lengthen the overall clock divider period.

If FDIV<4:0> = 00000, the fine frequency division circuit is effectively disabled. Otherwise, it will optionally remove a clock pulse from the input of the clock divider every 1/2 second. This functionality will allow the user to remove up to 31 pulses over a fixed period of 16 seconds, depending on the value of FDIVx.

The value for DIV<15:0> is calculated as shown in Equation 22-1. The fractional remainder of the DIV<15:0> calculation result can be used to calculate the value for FDIV<4:0>.

#### EQUATION 22-1: RTCC CLOCK DIVIDER OUTPUT FREQUENCY

The DIV<15:0> value is the integer part of this calculation:

$$DIV < 15:0 > = \frac{FIN}{2 \cdot (PS < 1:0 > Prescaler)} - 1$$

The FDIV<4:0> value is the fractional part of the DIV<15:0> calculation multiplied by 32.

#### 22.3.2 RTCVAL REGISTER MAPPINGS

# REGISTER 22-4: RTCCON2H: RTCC CONTROL REGISTER 2 (HIGH)<sup>(1)</sup>

| bit 8 |

|-------|

| bit 8 |

|       |

|       |

| R/W-1 |

|       |

| bit C |

|       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 15-0 DIV<15:0>: Clock Divide bits

Sets the period of the clock divider counter; value should cause a nominal 1/2 second underflow.

**Note 1:** A write to this register is only allowed when WRLOCK = 1.

| U-0                                                                  | U-0     | R/W-0            | R/W-0   | R/W-0                                   | R/W-0   | R/W-0   | R/W-0   |

|----------------------------------------------------------------------|---------|------------------|---------|-----------------------------------------|---------|---------|---------|

| —                                                                    | _       | HRTEN1           | HRTEN0  | HRONE3                                  | HRONE2  | HRONE1  | HRONE0  |

| bit 15                                                               |         |                  |         |                                         |         |         | bit 8   |

|                                                                      |         |                  |         |                                         |         |         |         |

| U-0                                                                  | R/W-0   | R/W-0            | R/W-0   | R/W-0                                   | R/W-0   | R/W-0   | R/W-0   |

| —                                                                    | MINTEN2 | MINTEN1          | MINTEN0 | MINONE3                                 | MINONE2 | MINONE1 | MINONE0 |

| bit 7                                                                |         |                  |         |                                         |         |         | bit 0   |

|                                                                      |         |                  |         |                                         |         |         |         |

| Legend:                                                              |         |                  |         |                                         |         |         |         |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |         |                  |         |                                         |         |         |         |

| -n = Value at F                                                      | POR     | '1' = Bit is set |         | '0' = Bit is cleared x = Bit is unknown |         |         |         |

# REGISTER 22-16: TSATIMEH: RTCC TIMESTAMP A TIME REGISTER (HIGH)<sup>(1)</sup>

| bit 15-14 | Unimplemented: Read as '0'                                         |

|-----------|--------------------------------------------------------------------|

| bit 13-12 | HRTEN<1:0>: Binary Coded Decimal Value of Hours '10' Digit bits    |

|           | Contains a value from 0 to 2.                                      |

| bit 11-8  | HRONE<3:0>: Binary Coded Decimal Value of Hours '1' Digit bits     |

|           | Contains a value from 0 to 9.                                      |

| bit 7     | Unimplemented: Read as '0'                                         |

| bit 6-4   | MINTEN<2:0>: Binary Coded Decimal Value of Minutes '10' Digit bits |

|           | Contains a value from 0 to 5.                                      |

| bit 3-0   | MINONE<3:0>: Binary Coded Decimal Value of Minutes '1' Digit bits  |

|           | Contains a value from 0 to 9.                                      |

**Note 1:** If TSAEN = 0, bits<15:0> can be used for persistence storage throughout a non-Power-on Reset (MCLR, WDT, etc.).

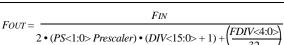

## EQUATION 25-1: A/D CONVERSION CLOCK PERIOD

$$TAD = TCY (ADCS + 1)$$

$$ADCS = \frac{TAD}{TCY} - 1$$

**Note:** Based on TCY = 2/FOSC; Doze mode and PLL are disabled.

# 33.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC24FJ1024GA610/GB610 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24FJ1024GA610/GB610 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

# Absolute Maximum Ratings<sup>(†)</sup>

t

| Ambient temperature under bias<br>Storage temperature                | -65°C to +150°C                                   |

|----------------------------------------------------------------------|---------------------------------------------------|

| Voltage on VDD with respect to Vss                                   |                                                   |

| Voltage on any general purpose digital or analog pin (not 5.5V toler |                                                   |

| Voltage on any general purpose digital or analog pin (5.5V tolerant, | including MCLR) with respect to Vss:              |

| When VDD = 0V:                                                       | -0.3V to +4.0V                                    |

| When $VDD \ge 2.0V$ :                                                | -0.3V to +6.0V                                    |

| Voltage on AVDD with respect to Vss                                  | (VDD – 0.3V) to (lesser of: 4.0V or (VDD + 0.3V)) |

| Voltage on AVss with respect to Vss                                  | -0.3V to +0.3V                                    |

| Maximum current out of Vss pin                                       |                                                   |

| Maximum current into VDD pin (Note 1)                                |                                                   |

| Maximum output current sunk by any I/O pin                           | 25 mA                                             |

| Maximum output current sourced by any I/O pin                        |                                                   |

| Maximum current sunk by all ports                                    |                                                   |

| Maximum current sourced by all ports (Note 1)                        |                                                   |

Note 1: Maximum allowable current is a function of device maximum power dissipation (see Table 33-1).

**NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

|              |        | Standard Operating Condition                                                     |                                  |                    |            | <b>6V (unless otherwise stated)</b><br>A ≤ +85°C for Industrial |                                                      |

|--------------|--------|----------------------------------------------------------------------------------|----------------------------------|--------------------|------------|-----------------------------------------------------------------|------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                                   | Min                              | Typ <sup>(1)</sup> | Max        | Units                                                           | Conditions                                           |

|              | VIL    | Input Low Voltage <sup>(3)</sup>                                                 |                                  |                    |            |                                                                 |                                                      |

| DI10         |        | I/O Pins with ST Buffer                                                          | Vss                              | _                  | 0.2 VDD    | V                                                               |                                                      |

| DI11         |        | I/O Pins with TTL Buffer                                                         | Vss                              | _                  | 0.15 VDD   | V                                                               |                                                      |

| DI15         |        | MCLR                                                                             | Vss                              | —                  | 0.2 VDD    | V                                                               |                                                      |

| DI16         |        | OSCI (XT mode)                                                                   | Vss                              | _                  | 0.2 VDD    | V                                                               |                                                      |

| DI17         |        | OSCI (HS mode)                                                                   | Vss                              | _                  | 0.2 VDD    | V                                                               |                                                      |

| DI18         |        | I/O Pins with I <sup>2</sup> C Buffer                                            | Vss                              | _                  | 0.3 VDD    | V                                                               |                                                      |

| DI19         |        | I/O Pins with SMBus Buffer                                                       | Vss                              | _                  | 0.8        | V                                                               | SMBus is enabled                                     |

|              | VIH    | Input High Voltage <sup>(3)</sup>                                                |                                  |                    |            |                                                                 |                                                      |

| DI20         |        | I/O Pins with ST Buffer:<br>with Analog Functions,<br>Digital Only               | 0.8 Vdd<br>0.8 Vdd               | _                  | VDD<br>5.5 | V<br>V                                                          |                                                      |

| DI21         |        | I/O Pins with TTL Buffer:<br>with Analog Functions,<br>Digital Only              | 0.25 VDD + 0.8<br>0.25 VDD + 0.8 | _                  | VDD<br>5.5 | V<br>V                                                          |                                                      |

| DI25         |        | MCLR                                                                             | 0.8 Vdd                          | _                  | Vdd        | V                                                               |                                                      |

| DI26         |        | OSCI (XT mode)                                                                   | 0.7 Vdd                          | —                  | Vdd        | V                                                               |                                                      |

| DI27         |        | OSCI (HS mode)                                                                   | 0.7 Vdd                          | _                  | Vdd        | V                                                               |                                                      |

| DI28         |        | I/O Pins with I <sup>2</sup> C Buffer:<br>with Analog Functions,<br>Digital Only | 0.7 Vdd<br>0.7 Vdd               | _                  | VDD<br>5.5 | V<br>V                                                          |                                                      |

| DI29         |        | I/O Pins with SMBus Buffer:<br>with Analog Functions,<br>Digital Only            | 2.1<br>2.1                       |                    | Vdd<br>5.5 | V<br>V                                                          | $2.5V \le V\text{PIN} \le V\text{DD}$                |

| DI30         | ICNPU  | CNx Pull-up Current                                                              | 150                              |                    | 450        | μA                                                              | VDD = 3.3V, VPIN = VSS                               |

| DI30A        | ICNPD  | CNx Pull-Down Current                                                            | 230                              |                    | 500        | μA                                                              | VDD = 3.3V, VPIN = VDD                               |

|              | lı∟    | Input Leakage Current <sup>(2)</sup>                                             |                                  |                    |            |                                                                 |                                                      |

| DI50         |        | I/O Ports                                                                        | _                                | —                  | ±1         | μA                                                              | $Vss \le VPIN \le VDD,$ pin at high-impedance        |

| DI51         |        | Analog Input Pins                                                                | —                                | —                  | ±1         | μΑ                                                              | $VSS \le VPIN \le VDD,$ pin at high-impedance        |

| DI55         |        | MCLR                                                                             | _                                | —                  | ±1         | μA                                                              | $VSS \leq VPIN \leq VDD$                             |

| DI56         |        | OSCI/CLKI                                                                        | —                                | —                  | ±1         | μA                                                              | $V_{SS} \le V_{PIN} \le V_{DD},$ EC, XT and HS modes |

## TABLE 33-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** Negative current is defined as current sourced by the pin.

**3:** Refer to Table 1-1 for I/O pin buffer types.

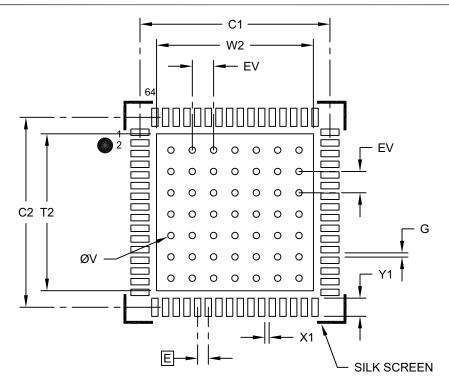

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length and 7.70x7.70mm Exposed Pad