Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj256gb606t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                 |                                                             |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|-------------------------------------------------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer | Description                                                 |

| PMD0            | 60                                  | 60                               | 93                               | 93                               | A4                      | A4                      | I/O | DIG/<br>ST/TTL  | Parallel Master Port Data<br>(Demultiplexed Master mode) or |

| PMD1            | 61                                  | 61                               | 94                               | 94                               | B4                      | B4                      | I/O | DIG/<br>ST/TTL  | Address/Data (Multiplexed<br>Master modes)                  |

| PMD2            | 62                                  | 62                               | 98                               | 98                               | B3                      | B3                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD3            | 63                                  | 63                               | 99                               | 99                               | A2                      | A2                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD4            | 64                                  | 64                               | 100                              | 100                              | A1                      | A1                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD5            | 1                                   | 1                                | 3                                | 3                                | D3                      | D3                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD6            | 2                                   | 2                                | 4                                | 4                                | C1                      | C1                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD7            | 3                                   | 3                                | 5                                | 5                                | D2                      | D2                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD8            | _                                   | _                                | 90                               | 90                               | A5                      | A5                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD9            | —                                   | _                                | 89                               | 89                               | E6                      | E6                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD10           | —                                   | _                                | 88                               | 88                               | A6                      | A6                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD11           | —                                   | —                                | 87                               | 87                               | B6                      | B6                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD12           | —                                   | —                                | 79                               | 79                               | A9                      | A9                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD13           | —                                   | _                                | 80                               | 80                               | D8                      | D8                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD14           | _                                   | _                                | 83                               | 83                               | D7                      | D7                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMD15           | —                                   | —                                | 84                               | 84                               | C7                      | C7                      | I/O | DIG/<br>ST/TTL  |                                                             |

| PMRD/<br>PMWR   | 53                                  | 53                               | 82                               | 82                               | B8                      | B8                      | I/O | DIG/<br>ST/TTL  | Parallel Master Port Read<br>Strobe/Write Strobe            |

| PMWR/<br>PMENB  | 52                                  | 52                               | 81                               | 81                               | C8                      | C8                      | I/O | DIG/<br>ST/TTL  | Parallel Master Port Write<br>Strobe/Enable Strobe          |

| PWRGT           | 21                                  | 21                               | 32                               | 32                               | K4                      | K4                      | 0   | DIG             | Real-Time Clock Power Control<br>Output                     |

| PWRLCLK         | 48                                  | 48                               | 74                               | 74                               | B11                     | B11                     | I   | ST              | Real-Time Clock 50/60 Hz Clock<br>Input                     |

#### **TABLE 1-3:** PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output

ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

|                  |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                  |                                               |

|------------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|------------------|-----------------------------------------------|

| Pin<br>Function  | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer  | Description                                   |

| RPI32            | —                                   | —                                | 40                               | 40                               | K6                      | K6                      | Ι   | DIG/ST           | Remappable Peripherals                        |

| RPI33            | —                                   | —                                | 18                               | 18                               | G1                      | G1                      | I   | DIG/ST           | (input only)                                  |

| RPI34            | —                                   | _                                | 19                               | 19                               | G2                      | G2                      | Т   | DIG/ST           |                                               |

| RPI35            | —                                   | _                                | 67                               | 67                               | E8                      | E8                      | Т   | DIG/ST           |                                               |

| RPI36            | —                                   | _                                | 66                               | 66                               | E11                     | E11                     | I   | DIG/ST           |                                               |

| RPI37            | 48                                  | 48                               | 74                               | 74                               | B11                     | B11                     | I   | DIG/ST           |                                               |

| RPI38            | —                                   | —                                | 6                                | 6                                | D1                      | D1                      | I   | DIG/ST           |                                               |

| RPI39            | _                                   | _                                | 7                                | 7                                | E4                      | E4                      | Ι   | DIG/ST           |                                               |

| RPI40            | _                                   | _                                | 8                                | 8                                | E2                      | E2                      | Ι   | DIG/ST           |                                               |

| RPI41            | _                                   | _                                | 9                                | 9                                | E1                      | E1                      | Ι   | DIG/ST           |                                               |

| RPI42            | _                                   | _                                | 79                               | 79                               | A9                      | A9                      | Ι   | DIG/ST           |                                               |

| RPI43            | _                                   | _                                | 47                               | 47                               | L9                      | L9                      | I   | DIG/ST           |                                               |

| SCL1             | 37                                  | 44                               | 57                               | 66                               | H10                     | E11                     | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock<br>Input/Output |

| SCL2             | 32                                  | 32                               | 58                               | 58                               | H11                     | H11                     | I/O | I <sup>2</sup> C | I2C2 Synchronous Serial Clock<br>Input/Output |

| SCL3             | 2                                   | 2                                | 4                                | 4                                | C1                      | C1                      | I/O | I <sup>2</sup> C | I2C3 Synchronous Serial Clock<br>Input/Output |

| SDA1             | 36                                  | 43                               | 56                               | 67                               | J11                     | E8                      | I/O | I <sup>2</sup> C | I2C1 Data Input/Output                        |

| SDA2             | 31                                  | 31                               | 59                               | 59                               | G10                     | G10                     | I/O | I <sup>2</sup> C | I2C2 Data Input/Output                        |

| SDA3             | 3                                   | 3                                | 5                                | 5                                | D2                      | D2                      | I/O | I <sup>2</sup> C | I2C3 Data Input/Output                        |

| SOSCI            | 47                                  | 47                               | 73                               | 73                               | C10                     | C10                     | I   | ANA/<br>ST       | Secondary Oscillator/Timer1<br>Clock Input    |

| SOSCO            | 48                                  | 48                               | 74                               | 74                               | B11                     | B11                     | 0   | ANA              | Secondary Oscillator/Timer1<br>Clock Output   |

| T1CK             | 22                                  | 22                               | 33                               | 33                               | L4                      | L4                      | Ι   | ST               | Timer1 Clock                                  |

| ТСК              | 27                                  | 27                               | 38                               | 38                               | J6                      | J6                      | I   | ST               | JTAG Test Clock/Programming<br>Clock Input    |

| TDI              | 28                                  | 28                               | 60                               | 60                               | G11                     | G11                     | I   | ST               | JTAG Test Data/Programming<br>Data Input      |

| TDO              | 24                                  | 24                               | 61                               | 61                               | G9                      | G9                      | 0   | DIG              | JTAG Test Data Output                         |

| TMPR             | 22                                  | 22                               | 33                               | 33                               | L4                      | L4                      | I   | ST               | Tamper Detect Input                           |

| TMS              | 23                                  | 23                               | 17                               | 17                               | G3                      | G3                      | I   | ST               | JTAG Test Mode Select Input                   |

| U5CTS            | 58                                  | 58                               | 87                               | 87                               | B6                      | B6                      | I   | ST               | UART5 CTS Output                              |

| U5RTS/<br>U5BCLK | 55                                  | 55                               | 84                               | 84                               | C7                      | C7                      | 0   | DIG              | UART5 RTS Input                               |

| U5RX             | 54                                  | 54                               | 83                               | 83                               | D7                      | D7                      | I   | ST               | UART5 Receive Input                           |

| U5TX             | 49                                  | 49                               | 76                               | 76                               | A11                     | A11                     | 0   | DIG              | UART5 Transmit Output                         |

| U6CTS            | 46                                  | 46                               | 72                               | 72                               | D9                      | D9                      | I   | ST               | UART6 CTS Output                              |

| U6RTS/<br>U6BCLK | 42                                  | 42                               | 68                               | 68                               | E9                      | E9                      | 0   | DIG              | UART6 RTS Input                               |

#### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL =

TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

## 2.4 Voltage Regulator Pin (VCAP)

Note: This section applies only to PIC24FJ devices with an on-chip voltage regulator.

Refer to **Section 30.3** "**On-Chip Voltage Regulator**" for details on connecting and using the on-chip regulator.

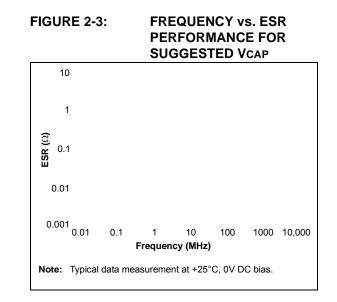

A low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP pin to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

Designers may use Figure 2-3 to evaluate the ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 33.0** "**Electrical Characteristics**" for additional information.

## TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS (0805 CASE SIZE)

| Make   | Part #              | Nominal<br>Capacitance | Base Tolerance | Rated Voltage |

|--------|---------------------|------------------------|----------------|---------------|

| TDK    | C2012X5R1E106K085AC | 10 µF                  | ±10%           | 25V           |

| TDK    | C2012X5R1C106K085AC | 10 µF                  | ±10%           | 16V           |

| Kemet  | C0805C106M4PACTU    | 10 µF                  | ±10%           | 16V           |

| Murata | GRM21BR61E106KA3L   | 10 µF                  | ±10%           | 25V           |

| Murata | GRM21BR61C106KE15   | 10 µF                  | ±10%           | 16V           |

## 2.7 Configuration of Analog and Digital Pins During ICSP Operations

If an ICSP compliant emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins. Depending on the particular device, this is done by setting all bits in the ADxPCFG register(s) or clearing all bits in the ANSx registers.

All PIC24F devices will have either one or more ADxPCFG registers, or several ANSx registers (one for each port); no device will have both. Refer to (Section 11.2 "Configuring Analog Port Pins (ANSx)") for more specific information.

The bits in these registers that correspond to the A/D pins that initialized the emulator must not be changed by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must modify the appropriate bits during initialization of the A/D module, as follows:

- For devices with an ADxPCFG register, clear the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGECx/PGEDx pair, at any time.

- For devices with ANSx registers, set the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGECx/PGEDx pair, at any time.

When a Microchip debugger/emulator is used as a programmer, the user application firmware must correctly configure the ADxPCFG or ANSx registers. Automatic initialization of these registers is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

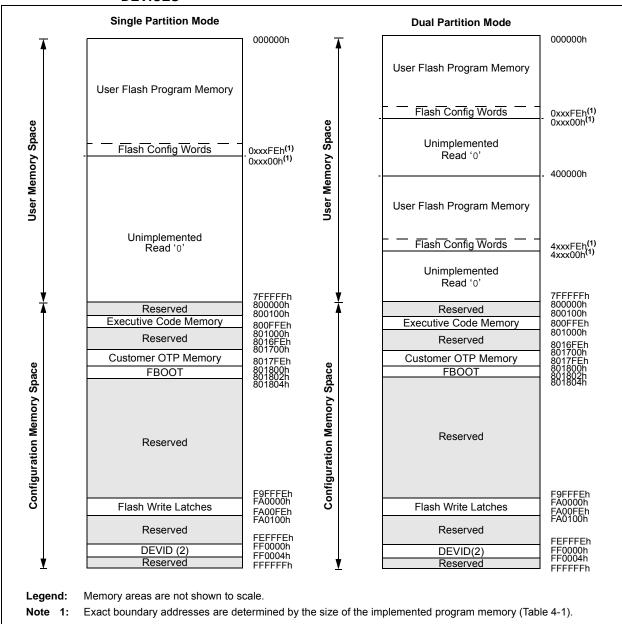

# FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FJ1024GA610/GB610 FAMILY DEVICES

## TABLE 4-1: PROGRAM MEMORY SIZES AND BOUNDARIES<sup>(1)</sup>

|                  | Program Memory   | y Upper Boundary (                  |                |                                |                                |  |

|------------------|------------------|-------------------------------------|----------------|--------------------------------|--------------------------------|--|

| Device           | Single Partition | Dual Part                           | ition Mode     | Write<br>Blocks <sup>(2)</sup> | Erase<br>Blocks <sup>(2)</sup> |  |

|                  | Mode             | Active Partition Inactive Partition |                |                                |                                |  |

| PIC24FJ1024GX6XX | 0ABFFEh (352K)   | 055FFEh (176K)                      | 455FFEh (176K) | 2752                           | 344                            |  |

| PIC24FJ512GX6XX  | 055FFEh (176K)   | 02AFFEh (88k)                       | 42AFFEh (88k)  | 1376                           | 172                            |  |

| PIC24FJ256GX6XX  | 02AFFEh (88K)    | 0157FEh (44k)                       | 4157FEh (44k)  | 688                            | 86                             |  |

| PIC24FJ128GX6XX  | 015FFEh (44K)    | 00AFFEh (22k)                       | 40AFFEh (22k)  | 352                            | 44                             |  |

Note 1: Includes Flash Configuration Words.

2: 1 Write Block = 128 Instruction Words; 1 Erase Block = 1024 Instruction Words.

| File Name | Address | All Resets | File Name        | Address | All Resets |

|-----------|---------|------------|------------------|---------|------------|

| A/D       | ·       |            | PERIPHERAL PIN S |         |            |

| ADC1BUF0  | 0712    | xxxx       | RPINR0           | 0790    | 3F3F       |

| ADC1BUF1  | 0714    | xxxx       | RPINR1           | 0792    | 3F3F       |

| ADC1BUF2  | 0716    | xxxx       | RPINR2           | 0794    | 3F3F       |

| ADC1BUF3  | 0718    | xxxx       | RPINR3           | 0796    | 3F3F       |

| ADC1BUF4  | 071A    | xxxx       | RPINR4           | 0798    | 3F3F       |

| ADC1BUF5  | 071C    | xxxx       | RPINR5           | 079A    | 3F3F       |

| ADC1BUF6  | 071E    | xxxx       | RPINR6           | 079C    | 3F3F       |

| ADC1BUF7  | 0720    | xxxx       | RPINR7           | 079E    | 3F3F       |

| ADC1BUF8  | 0722    | xxxx       | RPINR8           | 07A0    | 003F       |

| ADC1BUF9  | 0724    | xxxx       | RPINR11          | 07A6    | 3F3F       |

| ADC1BUF10 | 0726    | xxxx       | RPINR12          | 07A8    | 3F3F       |

| ADC1BUF11 | 0728    | xxxx       | RPINR14          | 07AC    | 3F3F       |

| ADC1BUF12 | 072A    | xxxx       | RPINR15          | 07AE    | 003F       |

| ADC1BUF13 | 072C    | xxxx       | RPINR17          | 07B2    | 3F00       |

| ADC1BUF14 | 072E    | xxxx       | RPINR18          | 07B4    | 3F3F       |

| ADC1BUF15 | 0730    | xxxx       | RPINR19          | 07B6    | 3F3F       |

| ADC1BUF16 | 0732    | xxxx       | RPINR20          | 07B8    | 3F3F       |

| ADC1BUF17 | 0734    | xxxx       | RPINR21          | 07BA    | 3F3F       |

| ADC1BUF18 | 0736    | xxxx       | RPINR22          | 07BC    | 3F3F       |

| ADC1BUF19 | 0738    | xxxx       | RPINR23          | 07BE    | 3F3F       |

| ADC1BUF20 | 073A    | xxxx       | RPINR25          | 07C2    | 3F3F       |

| ADC1BUF21 | 073C    | xxxx       | RPINR27          | 07C6    | 3F3F       |

| ADC1BUF22 | 073E    | xxxx       | RPINR28          | 07C8    | 3F3F       |

| ADC1BUF23 | 0740    | xxxx       | RPINR29          | 07CA    | 003F       |

| ADC1BUF24 | 0742    | xxxx       | RPOR0            | 07D4    | 0000       |

| ADC1BUF25 | 0744    | xxxx       | RPOR1            | 07D6    | 0000       |

| AD1CON1   | 0746    | 0000       | RPOR2            | 07D8    | 0000       |

| AD1CON2   | 0748    | 0000       | RPOR3            | 07DA    | 0000       |

| AD1CON3   | 074A    | 0000       | RPOR4            | 07DC    | 0000       |

| AD1CHS    | 074C    | 0000       | RPOR5            | 07DE    | 0000       |

| AD1CSSH   | 074E    | 0000       | RPOR6            | 07E0    | 0000       |

| AD1CSSL   | 0750    | 0000       | RPOR7            | 07E2    | 0000       |

| AD1CON4   | 0752    | 0000       | RPOR8            | 07E4    | 0000       |

| AD1CON5   | 0754    | 0000       | RPOR9            | 07E6    | 0000       |

| AD1CHITH  | 0756    | 0000       | RPOR10           | 07E8    | 0000       |

| AD1CHITL  | 0758    | 0000       | RPOR11           | 07EA    | 0000       |

| AD1CTMENH | 075A    | 0000       | RPOR12           | 07EC    | 0000       |

| AD1CTMENL | 075C    | 0000       | RPOR13           | 07EE    | 0000       |

| AD1RESDMA | 075E    | 0000       | RPOR14           | 07F0    | 0000       |

| NVM       |         |            | RPOR15           | 07F2    | 0000       |

| NVMCON    | 0760    | 0000       |                  |         |            |

| NVMADR    | 0762    | xxxx       |                  |         |            |

| NVMADRU   | 0764    | 00xx       |                  |         |            |

| NVMKEY    | 0766    | 0000       |                  |         |            |

TABLE 4-11: SFR MAP: 0700h BLOCK

## 9.1 CPU Clocking Scheme

The system clock source can be provided by one of five sources:

- Primary Oscillator (POSC) on the OSCI and OSCO pins

- Secondary Oscillator (SOSC) on the SOSCI and SOSCO pins

- Digitally Controlled Oscillator (DCO)

- · Fast Internal RC (FRC) Oscillator

- · Low-Power Internal RC (LPRC) Oscillator

The Primary Oscillator and FRC sources have the option of using the internal PLL block, which can generate a 96 MHz USB module PLL clock, or a 4x, 6x or 8x PLL clock. If the 96 MHz PLL is used, the PLL clocks can then be postscaled, if necessary, and used as the system clock. If the 4x, 6x or 8x PLL multipliers are selected, the PLL clock can be used directly as a system clock. Refer to Section 9.6 "PLL Oscillator Modes and USB Operation" for additional information. The internal FRC provides an 8 MHz clock source.

Each clock source (POSC, SOSC, DCO, FRC and LPRC) can be used as an input to an additional divider, which can then be used to produce a divided clock source for use as a system clock (OSCFDIV).

The selected clock source is used to generate the processor and peripheral clock sources. The processor clock source is divided by two to produce the internal instruction cycle clock, FCY. In this document, the instruction cycle clock is also denoted by FOSC/2. The internal instruction cycle clock, FOSC/2, can be provided on the OSCO I/O pin for some Primary Oscillator configurations.

## 9.2 Initial Configuration on POR

The oscillator source (and operating mode) that is used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory (refer to **Section 30.1 "Configuration Bits"** for further details). The Primary Oscillator Configuration bits, POSCMD<1:0> (FOSC<1:0>), and the Initial Oscillator Select Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), select the oscillator source that is used at a Power-on Reset. The OSCFDIV clock source is the default (unprogrammed) selection; the default input source to the OSCFDIV divider is the FRC clock source. Other oscillators may be chosen by programming these bit locations.

The Configuration bits allow users to choose between the various clock modes shown in Table 9-1.

#### 9.2.1 CLOCK SWITCHING MODE CONFIGURATION BITS

The FCKSM<1:0> Configuration bits (FOSC<7:6>) are used to jointly configure device clock switching and the Fail-Safe Clock Monitor (FSCM). Clock switching is enabled only when FCKSM<1> is programmed ('0'). The FSCM is enabled only when FCKSM<1:0> are both programmed ('00'). A recommended code sequence for a clock switch includes the following:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8> in two back-to-back instructions.

- 3. Write the new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0> in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock-sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of the failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

#### EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in WO |

|-------------------------------------------|

| ;OSCCONH (high byte) Unlock Sequence      |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Start oscillator switch operation        |

| BSET OSCCON, #0                           |

|                                           |

## 9.5 FRC Active Clock Tuning

PIC24FJ1024GA610/GB610 family devices include an automatic mechanism to calibrate the FRC during run time. This system uses active clock tuning from a source of known accuracy to maintain the FRC within a very narrow margin of its nominal 8 MHz frequency. This allows for a frequency accuracy that is well within the requirements of the *"USB 2.0 Specification"* regarding full-speed USB devices.

Note: The self-tune feature maintains sufficient accuracy for operation in USB Device mode. For applications that function as a USB host, a high-accuracy clock source (±0.05%) is still required.

The self-tune system is controlled by the bits in the upper half of the OSCTUN register. Setting the STEN bit (OSCTUN<15>) enables the self-tuning feature, allowing the hardware to calibrate to a source selected by the STSRC bit (OSCTUN<12>). When STSRC = 1, the system uses the Start-of-Frame (SOF) packets from an external USB host for its source. When STSRC = 0, the system uses the crystal-controlled SOSC for its calibration source. Regardless of the source, the system uses the TUN<5:0> bits (OSCTUN<5:0>) to change the FRC Oscillator's frequency. Frequency monitoring and adjustment is dynamic, occurring continuously during run time. While the system is active, the TUNx bits cannot be written to by software.

| Note: | To use the USB as a reference clock tuning<br>source (STSRC = 1), the microcontroller<br>must be configured for USB device opera-<br>tion and connected to a non-suspended<br>USB host or hub port. |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | If the SOSC is to be used as the reference clock tuning source (STSRC = 0), the SOSC must also be enabled for clock tuning to occur.                                                                |

The self-tune system can generate a hardware interrupt, FSTIF. The interrupt can result from a drift of the FRC from the reference, by greater than 0.2% in either direction, or whenever the frequency deviation is beyond the ability of the TUN<5:0> bits to correct (i.e., greater than 1.5%). The STLOCK and STOR status bits (OSCTUN<11,9>) are used to indicate these conditions.

The STLPOL and STORPOL bits (OSCTUN<10,8>) configure the FSTIF interrupt to occur in the presence or the absence of the conditions. It is the user's responsibility to monitor both the STLOCK and STOR bits to determine the exact cause of the interrupt.

**Note:** The STLPOL and STORPOL bits should be ignored when the self-tune system is disabled (STEN = 0).

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. In an application that needs to use more than one peripheral multiplexed on a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of any one of many digital peripherals to any one of these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The PPS feature is used with a range of up to 44 pins, depending on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

PIC24FJ1024GA610/GB610 family devices support a larger number of remappable input/output pins than remappable input only pins. In this device family, there are up to 44 remappable input/output pins, depending on the pin count of the particular device selected. These pins are numbered, RP0 through RP31, and RPI32 through RPI43.

See Table 1-1 for a summary of pinout options in each package offering.

## 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals. PPS is not available for these peripherals:

- I<sup>2</sup>C (input and output)

- Input Change Notifications

- EPMP Signals (input and output)

- Analog (inputs and outputs)

- INT0

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 11.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g., output compare, UART transmit) will take priority over general purpose digital functions on a pin, such as EPMP and port I/O. Specialized digital outputs will take priority over PPS outputs on the same pin. The pin diagrams list peripheral outputs in the order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pinselectable peripheral inputs will never take ownership of a pin. The pin's output buffer will be controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in Digital mode, then the PPS input will operate correctly. If an analog function is enabled on the pin, the PPS input will be disabled.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

## 11.4.3.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral; that is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-12 through Register 11-35). Each register contains one or two sets of 6-bit fields, with each set associated with one of the pin-selectable peripherals. Programming a given peripheral's bit field with an appropriate 6-bit value maps the RPn/RPIn pin with that value to that peripheral. For any given device, the valid range of values for any of the bit fields corresponds to the maximum number of Peripheral Pin Selections supported by the device.

| TABLE TT-3. SELECTABLE INFOT SOUNCES (WAFS INFOT TO TONCTION). | <b>TABLE 11-3</b> : | SELECTABLE INPUT SOURCES | (MAPS INPUT TO FUNCTION) <sup>(1)</sup> |

|----------------------------------------------------------------|---------------------|--------------------------|-----------------------------------------|

|----------------------------------------------------------------|---------------------|--------------------------|-----------------------------------------|

| Input Name                   | Function Name | Register      | Function Mapping<br>Bits |  |

|------------------------------|---------------|---------------|--------------------------|--|

| Output Compare Trigger 1     | OCTRIG1       | RPINR0<5:0>   | OCTRIG1R<5:0>            |  |

| External Interrupt 1         | INT1          | RPINR0<13:8>  | INT1R<5:0>               |  |

| External Interrupt 2         | INT2          | RPINR1<5:0>   | INT2R<5:0>               |  |

| External Interrupt 3         | INT3          | RPINR1<13:8>  | INT3R<5:0>               |  |

| External Interrupt 4         | INT4          | RPINR2<5:0>   | INT4R<5:0>               |  |

| Output Compare Trigger 2     | OCTRIG2       | RPINR2<13:8>  | OCTRIG2R<5:0>            |  |

| Timer2 External Clock        | T2CK          | RPINR3<5:0>   | T2CKR<5:0>               |  |

| Timer3 External Clock        | T3CK          | RPINR3<13:8>  | T3CKR<5:0>               |  |

| Timer4 External Clock        | T4CK          | RPINR4<5:0>   | T4CKR<5:0>               |  |

| Timer5 External Clock        | T5CK          | RPINR4<13:8>  | T5CKR<5:0>               |  |

| Input Capture 1              | IC1           | RPINR7<5:0>   | IC1R<5:0>                |  |

| Input Capture 2              | IC2           | RPINR7<13:8>  | IC2R<5:0>                |  |

| Input Capture 3              | IC3           | RPINR8<5:0>   | IC3R<5:0>                |  |

| Output Compare Fault A       | OCFA          | RPINR11<5:0>  | OCFAR<5:0>               |  |

| Output Compare Fault B       | OCFB          | RPINR11<13:8> | OCFBR<5:0>               |  |

| CCP Clock Input A            | TCKIA         | RPINR12<5:0>  | TCKIAR<5:0>              |  |

| CCP Clock Input B            | TCKIB         | RPINR12<13:8> | TCKIBR<5:0>              |  |

| UART3 Receive                | U3RX          | RPINR17<13:8> | U3RXR<5:0>               |  |

| UART1 Receive                | U1RX          | RPINR18<5:0>  | U1RXR<5:0>               |  |

| UART1 Clear-to-Send          | U1CTS         | RPINR18<13:8> | U1CTSR<5:0>              |  |

| UART2 Receive                | U2RX          | RPINR19<5:0>  | U2RXR<5:0>               |  |

| UART2 Clear-to-Send          | U2CTS         | RPINR19<13:8> | U2CTSR<5:0>              |  |

| SPI1 Data Input              | SDI1          | RPINR20<5:0>  | SDI1R<5:0>               |  |

| SPI1 Clock Input             | SCK1IN        | RPINR20<13:8> | SCK1R<5:0>               |  |

| SPI1 Slave Select Input      | SS1IN         | RPINR21<5:0>  | SS1R<5:0>                |  |

| UART3 Clear-to-Send          | U3CTS         | RPINR21<13:8> | U3CTSR<5:0>              |  |

| SPI2 Data Input              | SDI2          | RPINR22<5:0>  | SDI2R<5:0>               |  |

| SPI2 Clock Input             | SCK2IN        | RPINR22<13:8> | SCK2R<5:0>               |  |

| SPI2 Slave Select Input      | SS2IN         | RPINR23<5:0>  | SS2R<5:0>                |  |

| Generic Timer External Clock | TxCK          | RPINR23<13:8> | TXCKR<5:0>               |  |

| CLC Input A                  | CLCINA        | RPINR25<5:0>  | CLCINAR<5:0>             |  |

| CLC Input B                  | CLCINB        | RPINR25<13:8> | CLCINBR<5:0>             |  |

| UART4 Receive                | U4RX          | RPINR27<5:0>  | U4RXR<5:0>               |  |

| UART4 Clear-to-Send          | U4CTS         | RPINR27<13:8> | U4CTSR<5:0>              |  |

| SPI3 Data Input              | SDI3          | RPINR28<5:0>  | SDI3R<5:0>               |  |

| SPI3 Clock Input             | SCK3IN        | RPINR28<13:8> | SCK3R<5:0>               |  |

| SPI3 Slave Select Input      | SS3IN         | RPINR29<5:0>  | SS3R<5:0>                |  |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger (ST) input buffers.

#### 11.4.6 PERIPHERAL PIN SELECT REGISTERS

The PIC24FJ1024GA610/GB610 family of devices implements a total of 40 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (24)

- Output Remappable Peripheral Registers (16)

Note: Input and Output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 11.4.4.1 "Control Register Lock" for a specific command sequence.

#### REGISTER 11-12: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | INT1R5 | INT1R4 | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1     | R/W-1     | R/W-1     | R/W-1     | R/W-1     | R/W-1     |

|-------|-----|-----------|-----------|-----------|-----------|-----------|-----------|

| —     | —   | OCTRIG1R5 | OCTRIG1R4 | OCTRIG1R3 | OCTRIG1R2 | OCTRIG1R1 | OCTRIG1R0 |

| bit 7 |     |           |           |           |           |           | bit 0     |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 **Unimplemented:** Read as '0'

bit 7-6 Unimplemented: Read as '0'

bit 5-0 OCTRIG1R<5:0>: Assign Output Compare Trigger 1 to Corresponding RPn or RPIn Pin bits

#### REGISTER 11-13: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0                                                                        | U-0        | R/W-1            | R/W-1  | R/W-1        | R/W-1            | R/W-1    | R/W-1  |  |  |

|----------------------------------------------------------------------------|------------|------------------|--------|--------------|------------------|----------|--------|--|--|

| _                                                                          | —          | INT3R5           | INT3R4 | INT3R3       | INT3R2           | INT3R1   | INT3R0 |  |  |

| bit 15                                                                     |            |                  |        |              |                  |          | bit 8  |  |  |

| U-0                                                                        | U-0        | R/W-1            | R/W-1  | R/W-1        | R/W-1            | R/W-1    | R/W-1  |  |  |

| _                                                                          | _          | INT2R5           | INT2R4 | INT2R3       | INT2R2           | INT2R1   | INT2R0 |  |  |

| bit 7                                                                      |            |                  |        |              |                  |          | bit 0  |  |  |

| Legend:                                                                    |            |                  |        |              |                  |          |        |  |  |

| R = Readable                                                               | e bit      | W = Writable     | bit    | U = Unimplem | nented bit, read | 1 as '0' |        |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |            |                  |        |              |                  |          |        |  |  |

| bit 15-14                                                                  | Unimplemer | ited: Read as 'o | )'     |              |                  |          |        |  |  |

| bit 13-8                                                                   |            |                  |        |              |                  |          |        |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 INT2R<5:0>: Assign External Interrupt 2 (INT2) to Corresponding RPn or RPIn Pin bits

#### REGISTER 17-6: SPIxBUFL: SPIx BUFFER REGISTER LOW

| R/W-0                              | R/W-0  | R/W-0            | R/W-0                                   | R/W-0         | R/W-0           | R/W-0  | R/W-0 |

|------------------------------------|--------|------------------|-----------------------------------------|---------------|-----------------|--------|-------|

|                                    |        |                  | DAT                                     | A<15:8>       |                 |        |       |

| bit 15                             |        |                  |                                         |               |                 |        | bit 8 |

|                                    |        |                  |                                         |               |                 |        |       |

| R/W-0                              | R/W-0  | R/W-0            | R/W-0                                   | R/W-0         | R/W-0           | R/W-0  | R/W-0 |

|                                    |        |                  | DA                                      | TA<7:0>       |                 |        |       |

| bit 7                              |        |                  |                                         |               |                 |        | bit 0 |

|                                    |        |                  |                                         |               |                 |        |       |

| Legend:                            |        |                  |                                         |               |                 |        |       |

| R = Readab                         | le bit | W = Writable bit |                                         | U = Unimpleme | ented bit, read | as '0' |       |

| -n = Value at POR '1' = Bit is set |        |                  | '0' = Bit is cleared x = Bit is unknown |               |                 |        | nown  |

#### bit 15-0 DATA<15:0>: SPIx FIFO Data bits

When the MODE<32,16> or WLENGTH<4:0> bits select 16 to 9-bit data, the SPIx only uses DATA<15:0>. When the MODE<32,16> or WLENGTH<4:0> bits select 8 to 2-bit data, the SPIx only uses DATA<7:0>.

#### REGISTER 17-7: SPIxBUFH: SPIx BUFFER REGISTER HIGH

| R/W-0                              | R/W-0  | R/W-0                           | R/W-0 | R/W-0         | R/W-0           | R/W-0  | R/W-0 |

|------------------------------------|--------|---------------------------------|-------|---------------|-----------------|--------|-------|

|                                    |        |                                 | DAT   | ΓA<31:24>     |                 |        |       |

| bit 15                             |        |                                 |       |               |                 |        | bit 8 |

|                                    |        |                                 |       |               |                 |        |       |

| R/W-0                              | R/W-0  | R/W-0                           | R/W-0 | R/W-0         | R/W-0           | R/W-0  | R/W-0 |

|                                    |        |                                 | DAT   | ГA<23:16>     |                 |        |       |

| bit 7                              |        |                                 |       |               |                 |        | bit 0 |

|                                    |        |                                 |       |               |                 |        |       |

| Legend:                            |        |                                 |       |               |                 |        |       |

| R = Readab                         | le bit | W = Writable bit                |       | U = Unimpleme | ented bit, read | as '0' |       |

| -n = Value at POR '1' = Bit is set |        | '0' = Bit is cleared x = Bit is |       |               | x = Bit is unkr | nown   |       |

#### bit 15-0 DATA<31:16>: SPIx FIFO Data bits

When the MODE<32,16> or WLENGTH<4:0> bits select 32 to 25-bit data, the SPIx uses DATA<31:16>. When the MODE<32,16> or WLENGTH<4:0> bits select 24 to 17-bit data, the SPIx only uses DATA<23:16>.

## REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits                                                                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Interrupt is set on an RSR transfer, making the receive buffer full (i.e., has 4 data characters)</li> <li>10 = Interrupt is set on an RSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)</li> <li>0x = Interrupt is set when any character is received and transferred from the RSR to the receive buffer; receive buffer has one or more characters</li> </ul> |

| bit 5   | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Address Detect mode is enabled (if 9-bit mode is not selected, this does not take effect)</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                                                                             |

| bit 4   | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                                                                                                                                                                                                       |

|         | 1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                                                                                                                                                                             |

| bit 3   | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Parity error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                            |

| bit 2   | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Framing error has been detected for the current character (the character at the top of the receive FIFO)</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                          |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed (clearing a previously set OERR bit, 1 → 0 transition); will reset the receive buffer and the RSR to the empty state</li> </ul>                                                                                                                                                                                  |

| bit 0   | URXDA: UARTx Receive Buffer Data Available bit (read-only)                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                                                                                                                                                                              |

| Note 1: | The value of this bit only affects the transmit properties of the module when the $IrDA^{\otimes}$ encoder is enabled (IREN = 1).                                                                                                                                                                                                                                                                          |

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

#### 20.6.2 HOST NEGOTIATION PROTOCOL (HNP)

In USB OTG applications, a Dual Role Device (DRD) is a device that is capable of being either a host or a peripheral. Any OTG DRD must support Host Negotiation Protocol (HNP).

HNP allows an OTG B-device to temporarily become the USB host. The A-device must first enable the B-device to follow HNP. Refer to the *"On-The-Go Supplement"* to the *"USB 2.0 Specification"* for more information regarding HNP. HNP may only be initiated at full speed.

After being enabled for HNP by the A-device, the B-device requests being the host any time that the USB link is in the suspend state, by simply indicating a disconnect. This can be done in software by clearing DPPULUP and DMPULUP. When the A-device detects the disconnect condition (via the URSTIF (U1IR<0>) interrupt), the A-device may allow the B-device to take over as host. The A-device does this by signaling connect as a full-speed function. Software may accomplish this by setting DPPULUP.

If the A-device responds instead with resume signaling, the A-device remains as host. When the B-device detects the connect condition (via ATTACHIF, U1IR<6>), the B-device becomes host. The B-device drives Reset signaling prior to using the bus.

When the B-device has finished in its role as host, it stops all bus activity and turns on its D+ pull-up resistor by setting DPPULUP. When the A-device detects a suspend condition (Idle for 3 ms), the A-device turns off its D+ pull-up. The A-device may also power down the VBUS supply to end the session. When the A-device detects the connect condition (via ATTACHIF), the A-device resumes host operation and drives Reset signaling.

## 20.7 USB OTG Module Registers

There are a total of 37 memory-mapped registers associated with the USB OTG module. They can be divided into four general categories:

- USB OTG Module Control (12)

- USB Interrupt (7)

- USB Endpoint Management (16)

- USB VBUS Power Control (2)

This total does not include the (up to) 128 BD registers in the BDT. Their prototypes, described in Register 20-1 and Register 20-2, are shown separately in **Section 20.2 "USB Buffer Descriptors and the BDT"**.

All USB OTG registers are implemented in the Least Significant Byte (LSB) of the register. Bits in the upper byte are unimplemented and have no function. Note that some registers are instantiated only in Host mode, while other registers have different bit instantiations and functions in Device and Host modes.

The registers described in the following sections are those that have bits with specific control and configuration features. The following registers are used for data or address values only:

- U1BDTP1, U1BDTP2 and U1BDTP3: Specifies the 256-word page in data RAM used for the BDT; 8-bit value with bit 0 fixed as '0' for boundary alignment.

- U1FRML and U1FRMH: Contains the 11-bit byte counter for the current data frame.

## REGISTER 20-6: U1STAT: USB STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R-0, HSC            | U-0 | U-0   |

|----------|----------|----------|----------|----------|---------------------|-----|-------|

| ENDPT3   | ENDPT2   | ENDPT1   | ENDPT0   | DIR      | PPBI <sup>(1)</sup> | —   | —     |

| bit 7    |          |          |          |          |                     |     | bit 0 |

| Legend:           | U = Unimplemented bit, read as '0' |                                       |                    |  |  |

|-------------------|------------------------------------|---------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/Clearable bit |                    |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                  | x = Bit is unknown |  |  |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

| bit 7-4 | <b>ENDPT&lt;3:0&gt;:</b> Number of the Last Endpoint Activity bits (Represents the number of the BDT updated by the last USB transfer.)<br>1111 = Endpoint 15<br>1110 = Endpoint 14 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                                                                   |

|         | •                                                                                                                                                                                   |

|         | 0001 = Endpoint 1                                                                                                                                                                   |

|         | 0000 = Endpoint 0                                                                                                                                                                   |

| bit 3   | DIR: Last BD Direction Indicator bit                                                                                                                                                |

|         | 1 = The last transaction was a transmit transfer (TX)                                                                                                                               |

|         | 0 = The last transaction was a receive transfer (RX)                                                                                                                                |

| bit 2   | PPBI: Ping-Pong BD Pointer Indicator bit <sup>(1)</sup>                                                                                                                             |

|         | 1 = The last transaction was to the odd BD bank                                                                                                                                     |

|         | 0 = The last transaction was to the even BD bank                                                                                                                                    |

| bit 1-0 | Unimplemented: Read as '0'                                                                                                                                                          |

**Note 1:** This bit is only valid for endpoints with available even and odd BD registers.

## PIC24FJ1024GA610/GB610 FAMILY

## REGISTER 20-7: U1CON: USB CONTROL REGISTER (DEVICE MODE)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R-x, HSC | R/W-0  | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 |

|-------|----------|--------|-----|--------|--------|--------|-------|

|       | SE0      | PKTDIS | _   | HOSTEN | RESUME | PPBRST | USBEN |

| bit 7 |          |        |     |        |        |        | bit 0 |

| Legend:           | gend: U = Unimplemented bit, read as '0' |                           |                    |  |  |  |

|-------------------|------------------------------------------|---------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                         | HSC = Hardware Settable/C | learable bit       |  |  |  |

| -n = Value at POR | '1' = Bit is set                         | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

| Unimplemented: Read as '0'                                                                                                                                                                                     |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SE0: Live Single-Ended Zero Flag bit                                                                                                                                                                           |  |  |  |  |  |  |

| <ul> <li>1 = Single-ended zero is active on the USB bus</li> <li>0 = No single-ended zero is detected</li> </ul>                                                                                               |  |  |  |  |  |  |

| PKTDIS: Packet Transfer Disable bit                                                                                                                                                                            |  |  |  |  |  |  |

| <ul> <li>1 = SIE token and packet processing are disabled; automatically set when a SETUP token is received</li> <li>0 = SIE token and packet processing are enabled</li> </ul>                                |  |  |  |  |  |  |

| Unimplemented: Read as '0'                                                                                                                                                                                     |  |  |  |  |  |  |

| HOSTEN: Host Mode Enable bit                                                                                                                                                                                   |  |  |  |  |  |  |

| <ul> <li>1 = USB host capability is enabled; pull-downs on D+ and D- are activated in hardware</li> <li>0 = USB host capability is disabled</li> </ul>                                                         |  |  |  |  |  |  |

| RESUME: Resume Signaling Enable bit                                                                                                                                                                            |  |  |  |  |  |  |

| 1 = Resume signaling is activated                                                                                                                                                                              |  |  |  |  |  |  |

| 0 = Resume signaling is disabled                                                                                                                                                                               |  |  |  |  |  |  |

| PPBRST: Ping-Pong Buffers Reset bit                                                                                                                                                                            |  |  |  |  |  |  |

| <ul> <li>1 = Resets all Ping-Pong Buffer Pointers to the even BD banks</li> <li>0 = Ping-Pong Buffer Pointers are not reset</li> </ul>                                                                         |  |  |  |  |  |  |

| USBEN: USB Module Enable bit                                                                                                                                                                                   |  |  |  |  |  |  |

| <ul> <li>1 = USB module and supporting circuitry are enabled (device attached); D+ pull-up is activated in hardware</li> <li>0 = USB module and supporting circuitry are disabled (device detached)</li> </ul> |  |  |  |  |  |  |

|                                                                                                                                                                                                                |  |  |  |  |  |  |

## 25.2 Extended DMA Operations

In addition to the standard features available on all 12-bit A/D Converters, PIC24FJ1024GA610/GB610 family devices implement a limited extension of DMA functionality. This extension adds features that work with the device's DMA Controller to expand the A/D module's data storage abilities beyond the module's built-in buffer.

The Extended DMA functionality is controlled by the DMAEN bit (AD1CON1<11>); setting this bit enables the functionality. The DMABM bit (AD1CON1<12>) configures how the DMA feature operates.

## 25.2.1 EXTENDED BUFFER MODE

Extended Buffer mode (DMABM = 1) maps the A/D Data Buffer registers and data from all channels above 26 into a user-specified area of data RAM. This allows users to read the conversion results of channels above 26, which do not have their own memory-mapped A/D buffer locations, from data memory.

To accomplish this, the DMA must be configured in Peripheral Indirect Addressing mode and the DMA destination address must point to the beginning of the buffer. The DMA count must be set to generate an interrupt after the desired number of conversions.

In Extended Buffer mode, the A/D control bits will function similarly to non-DMA modes. The BUFREGEN bit will still select between FIFO mode and Channel-Aligned mode, but the number of words in the destination FIFO will be determined by the SMPI<4:0> bits in DMA mode. In FIFO mode, the BUFM bit will still split the output FIFO into two sets of 13 results (the SMPIx bits should be set accordingly), and the BUFS bit will still indicate which set of results is being written to and which can be read.

## 25.2.2 PIA MODE

When DMABM = 0, the A/D module is configured to function with the DMA Controller for Peripheral Indirect Addressing (PIA) mode operations. In this mode, the A/D module generates an 11-bit Indirect Address (IA). This is ORed with the destination address in the DMA Controller to define where the A/D conversion data will be stored.

In PIA mode, the buffer space is created as a series of contiguous smaller buffers, one per analog channel. The size of the channel buffer determines how many analog channels can be accommodated. The size of the buffer is selected by the DMABL<2:0> bits (AD1CON4<2:0>). The size options range from a single word per buffer to 128 words. Each channel is allocated a buffer of this size, regardless of whether or not the channel will actually have conversion data.

The IA is created by combining the base address within a channel buffer with three to five bits (depending on the buffer size) to identify the channel. The base address ranges from zero to seven bits wide, depending on the buffer size. The address is right-padded with a '0' in order to maintain address alignment in the Data Space. The concatenated channel and base address bits are then left-padded with zeros, as necessary, to complete the 11-bit IA.

The IA is configured to auto-increment which channel is written in each analog input's sub-buffer during write operations by using the SMPIx bits (AD1CON2<6:2>).

As with PIA operations for any DMA-enabled module, the base destination address in the DMADSTn register must be masked properly to accommodate the IA. Table 25-1 shows how complete addresses are formed. Note that the address masking varies for each buffer size option. Because of masking requirements, some address ranges may not be available for certain buffer sizes. Users should verify that the DMA base address is compatible with the buffer size selected.