Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0 0              |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

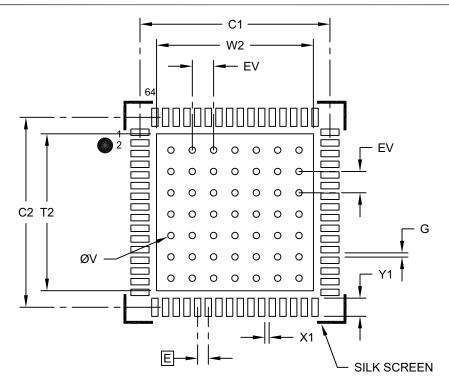

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj512ga606-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCUs and improve Data Space memory usage efficiency, the PIC24F instruction set supports both word and byte operations. As a consequence of byte accessibility, all EA calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode, [Ws++], will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word, which contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The Most Significant Byte (MSB) is not modified.

A Sign-Extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions operate only on words.

#### 4.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. The remainder of the Data Space is addressable indirectly. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing with a 16-bit address field.

#### 4.2.4 SPECIAL FUNCTION REGISTER (SFR) SPACE

The first 2 Kbytes of the Near Data Space, from 0000h to 07FFh, are primarily occupied with Special Function Registers (SFRs). These are used by the PIC24F core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A diagram of the SFR space, showing where the SFRs are actually implemented, is shown in Table 4-3. Each implemented area indicates a 32-byte region where at least one address is implemented as an SFR. A complete list of implemented SFRs, including their addresses, is shown in Tables 4-3 through 4-11.

|      | SFR Space Address |                      |      |      |      |        |      |      |      |      |        |                |      |      |      |      |

|------|-------------------|----------------------|------|------|------|--------|------|------|------|------|--------|----------------|------|------|------|------|

|      | xx00              | xx10                 | xx20 | xx30 | xx40 | xx50   | xx60 | xx70 | xx80 | xx90 | xxA0   | xxB0           | xxC0 | xxD0 | xxE0 | xxF0 |

| 000h | 000h Core         |                      |      |      |      |        |      |      |      |      |        |                |      |      |      |      |

| 100h | OSC               | Reset <sup>(1)</sup> |      | EPMP |      | CRC    | REFO | PN   | ИD   |      | Timers |                | CTM  |      | RTCC |      |

| 200h | Capture Compare   |                      |      |      |      | MCCP C |      |      |      |      | Comp   | ANCFG          |      |      |      |      |

| 300h |                   |                      |      |      | SCCP |        |      | UART |      |      |        | SPI            |      |      |      |      |

| 400h |                   |                      | SPI  |      |      | —      |      | CLC  |      |      | I      | <sup>2</sup> C |      |      | DMA  |      |

| 500h | D                 | MA                   |      | _    |      |        |      | US   | SB   |      |        |                |      | _    | _    | _    |

| 600h | _                 | _                    |      | _    |      |        | I/O  |      |      |      | _      |                |      |      |      |      |

| 700h | _                 |                      |      | A/D  |      |        | _    | _    | _    |      |        |                | PPS  |      |      |      |

#### TABLE 4-3: IMPLEMENTED REGIONS OF SFR DATA SPACE

Legend: - = No implemented SFRs in this block

Note 1: Includes HLVD control.

| File Name       | Address | All Resets | File Name       | Address         | All Resets |  |  |  |

|-----------------|---------|------------|-----------------|-----------------|------------|--|--|--|

| DMA (CONTINUED) |         |            | DMA (CONTINUED) | DMA (CONTINUED) |            |  |  |  |

| DMASRC0         | 04D0    | 0000       | DMACNT2         | 04E8            | 0001       |  |  |  |

| DMADST0         | 04D2    | 0000       | DMACH3          | 04EA            | 0000       |  |  |  |

| DMACNT0         | 04D4    | 0001       | DMAINT3         | 04EC            | 0000       |  |  |  |

| DMACH1          | 04D6    | 0000       | DMASRC3         | 04EE            | 0000       |  |  |  |

| DMAINT1         | 04D8    | 0000       | DMADST3         | 04F0            | 0000       |  |  |  |

| DMASRC1         | 04DA    | 0000       | DMACNT3         | 04F2            | 0001       |  |  |  |

| DMADST1         | 04DC    | 0000       | DMACH4          | 04F4            | 0000       |  |  |  |

| DMACNT1         | 04DE    | 0001       | DMAINT4         | 04F6            | 0000       |  |  |  |

| DMACH2          | 04E0    | 0000       | DMASRC4         | 04F8            | 0000       |  |  |  |

| DMAINT2         | 04E2    | 0000       | DMADST4         | 04FA            | 0000       |  |  |  |

| DMASRC2         | 04E4    | 0000       | DMACNT4         | 04FC            | 0001       |  |  |  |

| DMADST2         | 04E6    | 0000       | DMACH5          | 04FE            | 0000       |  |  |  |

### TABLE 4-8: SFR MAP: 0400h BLOCK (CONTINUED)

Legend: — = unimplemented, read as '0'; x = undefined. Reset values are shown in hexadecimal.

#### 4.2.5.2 Data Write into EDS

In order to write data to EDS, such as in EDS reads, an Address Pointer is set up by loading the required EDS page number into the DSWPAG register and assigning the offset address to one of the W registers. Once the above assignment is done, then the EDS window is enabled by setting bit 15 of the Working register, assigned with the offset address and the accessed location can be written.

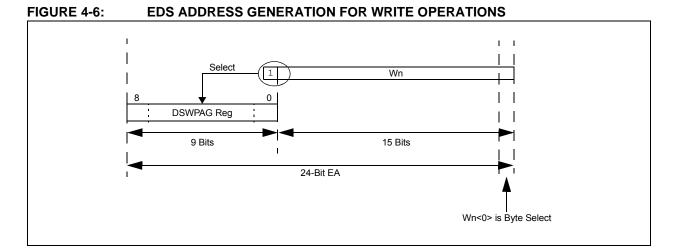

Figure 4-2 illustrates how the EDS address is generated for write operations.

When the MSbs of EA are '1', the lower 9 bits of DSWPAG are concatenated to the lower 15 bits of EA to form a 24-bit EDS address for write operations. Example 4-2 shows how to write a byte, word and double word to EDS.

The Data Space Page registers (DSRPAG/DSWPAG) do not update automatically while crossing a page boundary when the rollover happens from 0xFFFF to 0x8000. While developing code in assembly, care must be taken to update the Data Space Page registers when an Address Pointer crosses the page boundary. The 'C' compiler keeps track of the addressing, and increments or decrements the Page registers accordingly, while accessing contiguous data memory locations.

- **Note 1:** All write operations to EDS are executed in a single cycle.

- 2: Use of Read/Modify/Write operation on any EDS location under a REPEAT instruction is not supported. For example, BCLR, BSW, BTG, RLC f, RLNC f, RRC f, RRNC f, ADD f, SUB f, SUBR f, AND f, IOR f, XOR f, ASR f, ASL f.

- 3: Use the DSRPAG register while performing Read/Modify/Write operations.

#### EXAMPLE 4-2: EDS WRITE CODE IN ASSEMBLY

```

; Set the EDS page where the data to be written

#0x0002, w0

mov

w0, DSWPAG

;page 2 is selected for write

mov

#0x0800, w1

;select the location (0x800) to be written

mov

w1, #15

;set the MSB of the base address, enable EDS mode

bset

;Write a byte to the selected location

mov #0x00A5, w2

mov

#0x003C, w3

mov.b w2, [w1++]

;write Low byte

mov.b w3, [w1++]

;write High byte

;Write a word to the selected location

#0x1234, w2

mov

;

w2, [w1]

mov

;

;Write a Double - word to the selected location

#0x1122, w2

mov

mov

#0x4455, w3

mov.d w2, [w1]

;2 EDS writes

```

| REGISTER 5-1: | DMACON: DMA ENGINE CONTROL REGISTER |

|---------------|-------------------------------------|

|               |                                     |

| R/W-0                              | U-0         | U-0           | U-0                             | U-0                                | U-0 | U-0  | U-0    |  |

|------------------------------------|-------------|---------------|---------------------------------|------------------------------------|-----|------|--------|--|

| DMAEN                              | —           | —             | _                               | —                                  | —   | —    | —      |  |

| bit 15                             |             |               |                                 | -<br>-                             |     | •    | bit 8  |  |

|                                    |             |               |                                 |                                    |     |      |        |  |

| U-0                                | U-0         | U-0           | U-0                             | U-0                                | U-0 | U-0  | R/W-0  |  |

| —                                  | —           | —             | —                               | —                                  | —   | —    | PRSSEL |  |

| bit 7                              |             |               |                                 |                                    |     |      | bit 0  |  |

|                                    |             |               |                                 |                                    |     |      |        |  |

| Legend:                            |             |               |                                 |                                    |     |      |        |  |

| R = Readable                       | e bit       | W = Writable  | bit                             | U = Unimplemented bit, read as '0' |     |      |        |  |

| -n = Value at POR '1' = Bit is set |             |               | '0' = Bit is cleared x = Bit is |                                    |     | iown |        |  |

|                                    |             |               |                                 |                                    |     |      |        |  |

| bit 15                             | DMAEN: DM   | A Module Enab | le bit                          |                                    |     |      |        |  |

|                                    | 1 - Enchlos | modulo        |                                 |                                    |     |      |        |  |

1 = Enables module

0 = Disables module and terminates all active DMA operation(s)

bit 14-1 Unimplemented: Read as '0'

bit 0 PRSSEL: Channel Priority Scheme Selection bit

1 = Round-robin scheme

0 = Fixed priority scheme

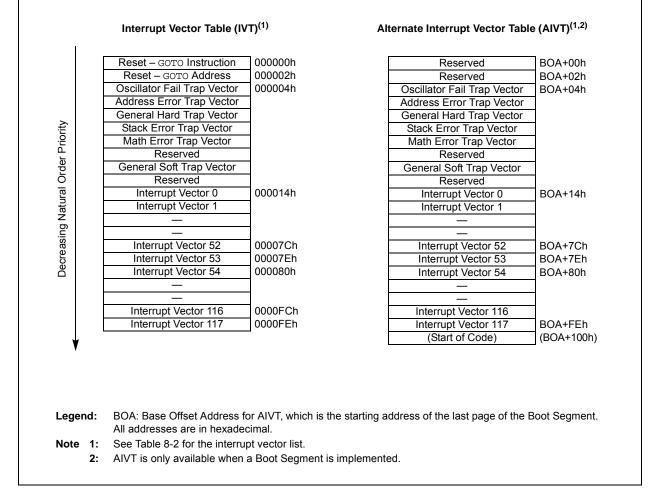

#### FIGURE 8-1: PIC24FJ1024GA610/GB610 FAMILY INTERRUPT VECTOR TABLES

#### TABLE 8-1: TRAP VECTOR DETAILS

| Vector Number | IVT Address | AIVT Address | Trap Source            |

|---------------|-------------|--------------|------------------------|

| 0             | 000004h     | BOA+04h      | Oscillator Failure     |

| 1             | 000006h     | BOA+06h      | Address Error          |

| 2             | 000008h     | BOA+08h      | General Hardware Error |

| 3             | 00000Ah     | BOA+0Ah      | Stack Error            |

| 4             | 00000Ch     | BOA+0Ch      | Math Error             |

| 5             | 00000Eh     | BOA+0Eh      | Reserved               |

| 6             | 000010h     | BOA+10h      | General Software Error |

| 7             | 000012h     | BOA+12h      | Reserved               |

**Legend:** BOA = Base Offset Address for the AIVT segment, which is the starting address of the last page of the Boot Segment.

The BOA depends on the size of the Boot Segment defined by  $\overline{BSLIM<12:0>}:$  [( $\overline{BSLIM<12:0>} - 1$ ) x 0x800]

|                     | U-0                                                                                                       | R/W-0                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                     | R-0              | R-0              | R-0             | R-0            |  |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|----------------|--|--|--|--|--|--|

| CPUIRQ              |                                                                                                           | VHOLD                                                                                                                                                                                                                                          | _                                                                                                                                                                                       | ILR3             | ILR2             | ILR1            | ILR0           |  |  |  |  |  |  |

| bit 15              |                                                                                                           | •                                                                                                                                                                                                                                              |                                                                                                                                                                                         |                  |                  |                 | bit 8          |  |  |  |  |  |  |

| R-0                 | R-0                                                                                                       | R-0                                                                                                                                                                                                                                            | R-0                                                                                                                                                                                     | R-0              | R-0              | R-0             | R-0            |  |  |  |  |  |  |

| VECNUM7             |                                                                                                           | VECNUM5                                                                                                                                                                                                                                        | VECNUM4                                                                                                                                                                                 | VECNUM3          | VECNUM2          | VECNUM1         | VECNUM0        |  |  |  |  |  |  |

| bit 7               |                                                                                                           |                                                                                                                                                                                                                                                |                                                                                                                                                                                         |                  |                  |                 | bit 0          |  |  |  |  |  |  |

| Legend:             |                                                                                                           |                                                                                                                                                                                                                                                |                                                                                                                                                                                         |                  |                  |                 |                |  |  |  |  |  |  |

| R = Readable        | e bit                                                                                                     | W = Writable                                                                                                                                                                                                                                   | bit                                                                                                                                                                                     | U = Unimpler     | nented bit, read | 1 as '0'        |                |  |  |  |  |  |  |

| -n = Value at       | POR                                                                                                       | '1' = Bit is set                                                                                                                                                                                                                               |                                                                                                                                                                                         | '0' = Bit is cle |                  | x = Bit is unkr | nown           |  |  |  |  |  |  |

|                     |                                                                                                           |                                                                                                                                                                                                                                                |                                                                                                                                                                                         |                  |                  |                 |                |  |  |  |  |  |  |

| bit 15              |                                                                                                           | errupt Request                                                                                                                                                                                                                                 | -                                                                                                                                                                                       |                  |                  |                 |                |  |  |  |  |  |  |

|                     |                                                                                                           |                                                                                                                                                                                                                                                |                                                                                                                                                                                         |                  | en Acknowledg    | ed by the CPU   | ; this happens |  |  |  |  |  |  |

|                     |                                                                                                           | CPU priority is                                                                                                                                                                                                                                |                                                                                                                                                                                         |                  | iority           |                 |                |  |  |  |  |  |  |

| L:1 4 4             |                                                                                                           | upt request is u                                                                                                                                                                                                                               | •                                                                                                                                                                                       | ea               |                  |                 |                |  |  |  |  |  |  |

| bit 14              | •                                                                                                         | ted: Read as '                                                                                                                                                                                                                                 |                                                                                                                                                                                         |                  |                  |                 |                |  |  |  |  |  |  |

| bit 13              |                                                                                                           | or Number Ca                                                                                                                                                                                                                                   | Ũ                                                                                                                                                                                       |                  | ,                |                 |                |  |  |  |  |  |  |

|                     |                                                                                                           | 1 = The VECNUMx bits contain the value of the highest priority pending interrupt                                                                                                                                                               |                                                                                                                                                                                         |                  |                  |                 |                |  |  |  |  |  |  |

|                     |                                                                                                           | 0 = The VECNUMx bits contain the value of the last Acknowledged interrupt (i.e., the last interrupt that has occurred with higher priority than the CPU, even if other interrupts are pending)                                                 |                                                                                                                                                                                         |                  |                  |                 |                |  |  |  |  |  |  |

| bit 12              |                                                                                                           |                                                                                                                                                                                                                                                |                                                                                                                                                                                         |                  |                  |                 |                |  |  |  |  |  |  |

| 510 12              | Unimplemented: Read as '0'                                                                                |                                                                                                                                                                                                                                                |                                                                                                                                                                                         |                  |                  |                 |                |  |  |  |  |  |  |

| hit 11_8            | IL R-3.0- Ne                                                                                              | w CPI I Interru                                                                                                                                                                                                                                |                                                                                                                                                                                         | al hits          |                  |                 |                |  |  |  |  |  |  |

| bit 11-8            |                                                                                                           | w CPU Interru                                                                                                                                                                                                                                  | pt Priority Lev                                                                                                                                                                         | el bits          |                  |                 |                |  |  |  |  |  |  |

| bit 11-8            |                                                                                                           | w CPU Interru<br>Interrupt Priorit                                                                                                                                                                                                             | pt Priority Lev                                                                                                                                                                         | el bits          |                  |                 |                |  |  |  |  |  |  |

| bit 11-8            |                                                                                                           |                                                                                                                                                                                                                                                | pt Priority Lev                                                                                                                                                                         | el bits          |                  |                 |                |  |  |  |  |  |  |

| bit 11-8            | 1111 = CPU<br>•<br>•                                                                                      | Interrupt Priorit                                                                                                                                                                                                                              | pt Priority Leve<br>y Level is 15                                                                                                                                                       | el bits          |                  |                 |                |  |  |  |  |  |  |

| bit 11-8            | 1111 = CPU<br>•<br>•<br>•<br>0001 = CPU                                                                   | Interrupt Priorit                                                                                                                                                                                                                              | pt Priority Leve<br>y Level is 15<br>y Level is 1                                                                                                                                       | el bits          |                  |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit                                                                                                                                                                                    | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0                                                                                                                       |                  |                  |                 |                |  |  |  |  |  |  |

| bit 11-8<br>bit 7-0 | 1111 = CPU<br>•<br>•<br>0001 = CPU<br>0000 = CPU<br>VECNUM<7:(                                            | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br><b>0&gt;:</b> Vector Nun                                                                                                                                                        | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0<br>ber of Pendin                                                                                                      |                  | 3                |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU<br>•<br>•<br>0001 = CPU<br>0000 = CPU<br>VECNUM<7:(                                            | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit                                                                                                                                                                                    | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0<br>ber of Pendin                                                                                                      |                  | 3                |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU<br>•<br>•<br>0001 = CPU<br>0000 = CPU<br>VECNUM<7:(                                            | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br><b>0&gt;:</b> Vector Nun                                                                                                                                                        | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0<br>ber of Pendin                                                                                                      |                  | 5                |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU<br>0001 = CPU<br>0000 = CPU<br>VECNUM<7:0<br>11111111 = 2                                      | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br><b>0&gt;:</b> Vector Nun<br>255, Reserved                                                                                                                                       | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0<br>ber of Pendin<br>; do not use                                                                                      |                  | 3                |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU                                                                                                | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br><b>0&gt;:</b> Vector Nun<br>255, Reserved<br>9, IC1 – Input (                                                                                                                   | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0<br>ber of Pendin<br>; do not use                                                                                      | g Interrupt bits | 3                |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU                                                                                                | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br><b>0&gt;:</b> Vector Nun<br>255, Reserved<br>9, IC1 – Input (<br>8, INT0 – Exter                                                                                                | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0<br>ber of Pendin<br>; do not use<br>Capture 1<br>rnal Interrupt 0                                                     | g Interrupt bits | 5                |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU                                                                                                | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br><b>0&gt;:</b> Vector Nun<br>255, Reserved<br>9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d                                                                              | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0<br>ber of Pendin<br>; do not use<br>Capture 1<br>rnal Interrupt (<br>o not use                                        | g Interrupt bits | 3                |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU                                                                                                | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br><b>0&gt;:</b> Vector Nun<br>255, Reserved<br>9, IC1 – Input (<br>8, INT0 – Exter                                                                                                | pt Priority Leve<br>y Level is 1<br>y Level is 1<br>y Level is 0<br>ber of Pendin<br>; do not use<br>Capture 1<br>rnal Interrupt 0<br>o not use<br>error trap                           | g Interrupt bits | 3                |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU                                                                                                | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br><b>D&gt;:</b> Vector Nun<br>255, Reserved<br>9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d<br>6, Generic soft<br>5, Reserved; d<br>4, Math error tr                     | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0<br>her of Pendin<br>do not use<br>Capture 1<br>rnal Interrupt 0<br>o not use<br>error trap<br>o not use<br>ap         | g Interrupt bits | 5                |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU                                                                                                | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br><b>D&gt;:</b> Vector Nun<br>255, Reserved<br>9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d<br>6, Generic soft<br>5, Reserved; d<br>4, Math error tr<br>3, Stack error t | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0<br>aber of Pendin<br>do not use<br>capture 1<br>rnal Interrupt 0<br>o not use<br>error trap<br>o not use<br>ap<br>rap | g Interrupt bits | 5                |                 |                |  |  |  |  |  |  |

|                     | 1111 = CPU                                                                                                | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit<br><b>D&gt;:</b> Vector Nun<br>255, Reserved<br>9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d<br>6, Generic soft<br>5, Reserved; d<br>4, Math error tr                     | pt Priority Leve<br>y Level is 15<br>y Level is 1<br>y Level is 0<br>aber of Pendin<br>do not use<br>error trap<br>o not use<br>ap<br>rap<br>d trap                                     | g Interrupt bits | 3                |                 |                |  |  |  |  |  |  |

#### REGISTER 8-6: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0           | R-x <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                  | R-x <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                      | R-x <sup>(1)</sup>                                    | U-0                                  | R/W-x <sup>(1)</sup>          | R/W-x <sup>(1)</sup> | R/W-x <sup>(1)</sup> |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------|-------------------------------|----------------------|----------------------|--|

| _             | COSC2                                                                                                                                                                                                                                                                                                                                                                                                                               | COSC1                                                                                                                                                                                                                                                                                                                                                                                   | COSC0                                                 | —                                    | NOSC2                         | NOSC1                | NOSC0                |  |

| oit 15        | ·                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |                                      |                               |                      | bit                  |  |

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                               | R-0 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                   | R/CO-0                               | R/W-0                         | R/W-0                | R/W-0                |  |

| CLKLOCK       |                                                                                                                                                                                                                                                                                                                                                                                                                                     | LOCK                                                                                                                                                                                                                                                                                                                                                                                    |                                                       | CF                                   | POSCEN                        | SOSCEN               | OSWEN                |  |

| bit 7         | IOLOGIA                                                                                                                                                                                                                                                                                                                                                                                                                             | LOOK                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |                                      | TOODEIN                       | OCCCLI               | bit                  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                     | CO = Clearal                                                                                                                                                                                                                                                                                                                                                                            | ole Only bit                                          |                                      |                               |                      |                      |  |

| R = Readabl   | le hit                                                                                                                                                                                                                                                                                                                                                                                                                              | W = Writable                                                                                                                                                                                                                                                                                                                                                                            |                                                       | II = I Inimpler                      | mented bit, read              | 1 as '0'             |                      |  |

| -n = Value at |                                                                                                                                                                                                                                                                                                                                                                                                                                     | '1' = Bit is se                                                                                                                                                                                                                                                                                                                                                                         |                                                       | '0' = Bit is cle                     |                               | x = Bit is unkn      | own                  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |                                      |                               |                      | lowin                |  |

| oit 15        | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                          | ted: Read as                                                                                                                                                                                                                                                                                                                                                                            | 0'                                                    |                                      |                               |                      |                      |  |

| oit 14-12     | COSC<2:0>:                                                                                                                                                                                                                                                                                                                                                                                                                          | Current Oscill                                                                                                                                                                                                                                                                                                                                                                          | ator Selection b                                      | oits <sup>(1)</sup>                  |                               |                      |                      |  |

|               | 110 = Digital<br>101 = Low-Po<br>100 = Second<br>011 = Primar<br>010 = Primar<br>001 = Fast R                                                                                                                                                                                                                                                                                                                                       | y Controlled O<br>ower RC Oscil<br>dary Oscillator<br>y Oscillator wit<br>y Oscillator (X                                                                                                                                                                                                                                                                                               | (SOSC)<br>h PLL module<br>ſ, HS, EC)<br>th PLL module | (XTPLL, ECPL                         | L)                            |                      |                      |  |

| bit 11        | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                          | ted: Read as '                                                                                                                                                                                                                                                                                                                                                                          | 0'                                                    |                                      |                               |                      |                      |  |

| bit 10-8      | NOSC<2:0>: New Oscillator Selection bits <sup>(1)</sup><br>111 = Oscillator with Frequency Divider (OSCFDIV)<br>110 = Digitally Controlled Oscillator (DCO)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Secondary Oscillator (SOSC)<br>011 = Primary Oscillator with PLL module (XTPLL, ECPLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |                                      |                               |                      |                      |  |

| bit 7         | CLKLOCK: C                                                                                                                                                                                                                                                                                                                                                                                                                          | lock Selection                                                                                                                                                                                                                                                                                                                                                                          | Lock Enable b                                         | bit                                  |                               |                      |                      |  |

|               | 1 = Clock and<br>0 = Clock and<br>If FSCM is Dis                                                                                                                                                                                                                                                                                                                                                                                    | CLKLOCK: Clock Selection Lock Enable bit<br><u>If FSCM is Enabled (FCKSM&lt;1:0&gt; = 00):</u><br>1 = Clock and PLL selections are locked<br>0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit<br><u>If FSCM is Disabled (FCKSM&lt;1:0&gt; = 1x):</u><br>Clock and PLL selections are never locked and may be modified by setting the OSWEN bit. |                                                       |                                      |                               |                      |                      |  |

| oit 6         |                                                                                                                                                                                                                                                                                                                                                                                                                                     | Lock Enable b                                                                                                                                                                                                                                                                                                                                                                           |                                                       | and may be fi                        |                               | S TO COVEN           | <b>VII.</b>          |  |

|               | 1 = I/O lock is                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |                                      |                               |                      |                      |  |

|               | 0 = I/O lock is                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |                                      |                               |                      |                      |  |

| oit 5         | LOCK: PLL L                                                                                                                                                                                                                                                                                                                                                                                                                         | ock Status bit <sup>(</sup>                                                                                                                                                                                                                                                                                                                                                             | 3)                                                    |                                      |                               |                      |                      |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                         |                                                       | start-up timer is<br>timer is runnii | satisfied<br>ng or PLL is dis | abled                |                      |  |

| oit 4         | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                          | ted: Read as                                                                                                                                                                                                                                                                                                                                                                            | 0'                                                    |                                      |                               |                      |                      |  |

| Note 1: R     | eset values for t                                                                                                                                                                                                                                                                                                                                                                                                                   | hese bits are                                                                                                                                                                                                                                                                                                                                                                           | determined by                                         | the FNOSCx C                         | onfiguration bits             | S.                   |                      |  |

| <b>2:</b> T   | he state of the IO                                                                                                                                                                                                                                                                                                                                                                                                                  | OLOCK bit car                                                                                                                                                                                                                                                                                                                                                                           | only be chang                                         | ged once an un                       | locking sequen                | ce has been ex       |                      |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                         |                                                       |                                      |                               |                      |                      |  |

#### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER

3: This bit also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

|                  | 5444.0        | 5444.0                               | 5444.0         | <b>B</b> 444 A    | 544/ 0        | 5444  | <b>B</b> 844 A                                                  |  |  |  |  |  |  |  |  |  |

|------------------|---------------|--------------------------------------|----------------|-------------------|---------------|-------|-----------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| U-0              | R/W-0         | R/W-0                                | R/W-0          | R/W-0             | R/W-0         | R/W-0 | R/W-0                                                           |  |  |  |  |  |  |  |  |  |

|                  |               |                                      |                | DIV<14:8>         |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

| bit 15           |               |                                      |                |                   |               |       | bit 8                                                           |  |  |  |  |  |  |  |  |  |

|                  |               |                                      |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

| R/W-0            | R/W-0         | R/W-0                                | R/W-0          | R/W-0             | R/W-0         | R/W-0 | R/W-1                                                           |  |  |  |  |  |  |  |  |  |

|                  |               |                                      | DIV            | /<7:0>            |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

| bit 7            |               |                                      |                |                   |               |       | bit C                                                           |  |  |  |  |  |  |  |  |  |

|                  |               |                                      |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

| Legend:          |               |                                      |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

| R = Readable bit |               | W = Writable b                       | bit            | U = Unimplen      |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

| -n = Value       | at POR        | '1' = Bit is set                     |                | '0' = Bit is clea | nown          |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  |               |                                      |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

| bit 15           | Unimpleme     | nted: Read as '0                     | ,              |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

| bit 14-0         | DIV<14:0>:    | Reference Clock                      | Divider bits   |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  | Specifies the | e 1/2 period of the                  | e reference cl | ock in the sourc  | e clocks      |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  |               | of ref_clk_output =                  |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  |               | 111111 = Oscilla                     |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  | 111111111     | 111110 <b>= Oscilla</b>              | ator frequency | y divided by 65,  | 532 (32,766 * | 2)    |                                                                 |  |  |  |  |  |  |  |  |  |

|                  | •             |                                      |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  | •             |                                      |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  | •             |                                      | tor froquene   | divided by 6 (2   | ) * O)        |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  |               | 000011 = Oscilla<br>000010 = Oscilla |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  |               | 000001 = Oscilla                     |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  |               |                                      |                |                   |               |       |                                                                 |  |  |  |  |  |  |  |  |  |

|                  | 300000000     | 00000 <b>000</b>                     |                | , is anonanged    |               |       | 00000000000000 = Oscillator frequency is unchanged (no divider) |  |  |  |  |  |  |  |  |  |

#### REGISTER 9-6: OSCDIV: OSCILLATOR DIVISOR REGISTER

#### 9.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the five clock sources (POSC, SOSC, FRC, DCO and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

Note: The Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

#### 9.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM<1> Configuration bit in FOSC must be programmed to '0'. (Refer to **Section 30.1 "Configuration Bits"** for further details.) If the FCKSM<1> Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled; this is the default setting.

The NOSC<2:0> control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC<2:0> bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSC<2:0> Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 9.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC<2:0> bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC<2:0> bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- The clock switching hardware compares the COSC<2:0> bits with the new value of the NOSC<2:0> bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC<2:0> bits values are transferred to the COSC<2:0> bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM is enabled) or SOSC (if SOSCEN remains set).

- Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.