Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

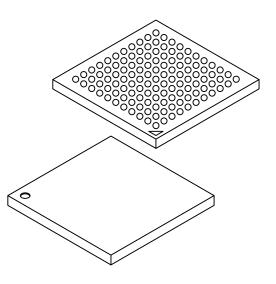

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj512ga610-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin | Function                                    | Pin | Function                          |

|-----|---------------------------------------------|-----|-----------------------------------|

| 1   | IC4/CTED4/PMD5/RE5                          | 33  | RP16/USBID/RF3                    |

| 2   | SCL3/IC5/PMD6/RE6                           | 34  | VBUS/RF7                          |

| 3   | SDA3/IC6/PMD7/RE7                           | 35  | VUSB3V3                           |

| 4   | C1IND/RP21/ICM1/OCM1A/PMA5/RG6              | 36  | D-/RG3                            |

| 5   | C1INC/RP26/OCM1B/PMA4/RG7                   | 37  | D+/RG2                            |

| 6   | C2IND/RP19/ICM2/OCM2A/PMA3/RG8              | 38  | VDD                               |

| 7   | MCLR                                        | 39  | OSCI/CLKI/RC12                    |

| 8   | C1INC/C2INC/C3INC/RP27/OCM2B/PMA2/PMALU/RG9 | 40  | OSCO/CLKO/RC15                    |

| 9   | Vss                                         | 41  | Vss                               |

| 10  | Vdd                                         | 42  | CLC4OUT/RP2/U6RTS/U6BCLK/ICM5/RD8 |

| 11  | PGEC3/AN5/C1INA/RP18/ICM3/OCM3A/RB5         | 43  | RP4/SDA1/PMACK2/RD9               |

| 12  | PGED3/AN4/C1INB/RP28/USBOEN/OCM3B/RB4       | 44  | RP3/SCL1/PMA15/PMCS2/RD10         |

| 13  | AN3/C2INA/RB3                               | 45  | RP12/PMA14/PMCS1/RD11             |

| 14  | AN2/CTCMP/C2INB/RP13/CTED13/RB2             | 46  | CLC3OUT/RP11/U6CTS/ICM6/INT0/RD0  |

| 15  | PGEC1/ALTCVREF-/ALTVREF-/AN1/RP1/CTED12/RB1 | 47  | SOSCI/C3IND/RC13                  |

| 16  | PGED1/ALTCVREF+/ALTVREF+/AN0/RP0/PMA6/RB0   | 48  | SOSCO/C3INC/RPI37/PWRLCLK/RC14    |

| 17  | PGEC2/AN6/ <b>RP6</b> /RB6                  | 49  | RP24/U5TX/ICM4/RD1                |

| 18  | PGED2/AN7/ <b>RP7</b> /U6TX/RB7             | 50  | RP23/PMACK1/RD2                   |

| 19  | AVdd                                        | 51  | RP22/ICM7/PMBE0/RD3               |

| 20  | AVss                                        | 52  | RP25/PMWR/PMENB/RD4               |

| 21  | AN8/ <b>RP8</b> /PWRGT/RB8                  | 53  | RP20/PMRD/PMWR/RD5                |

| 22  | AN9/TMPR/RP9/T1CK/PMA7/RB9                  | 54  | C3INB/U5RX/OC4/RD6                |

| 23  | TMS/CVREF/AN10/PMA13/RB10                   | 55  | C3INA/U5RTS/U5BCLK/OC5/RD7        |

| 24  | TDO/AN11/REFI/PMA12/RB11                    | 56  | VCAP                              |

| 25  | Vss                                         | 57  | N/C                               |

| 26  | Vdd                                         | 58  | U5CTS/OC6/RF0                     |

| 27  | TCK/AN12/U6RX/CTED2/PMA11/RB12              | 59  | RF1                               |

| 28  | TDI/AN13/CTED1/PMA10/RB13                   | 60  | PMD0/RE0                          |

| 29  | AN14/RP14/CTED5/CTPLS/PMA1/PMALH/RB14       | 61  | PMD1/RE1                          |

| 30  | AN15/RP29/CTED6/PMA0/PMALL/RB15             | 62  | PMD2/RE2                          |

| 31  | RP10/SDA2/PMA9/RF4                          | 63  | CTED9/PMD3/RE3                    |

| 32  | RP17/SCL2/PMA8/RF5                          | 64  | HLVDIN/CTED8/PMD4/RE4             |

# TABLE 3: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJXXXGB606)

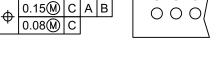

Legend: RPn and RPIn represent remappable pins for Peripheral Pin Select (PPS) functions.

**Note:** Pinouts are subject to change.

# 1.2 DMA Controller

PIC24FJ1024GA610/GB610 family devices have a Direct Memory Access (DMA) Controller. This module acts in concert with the CPU, allowing data to move between data memory and peripherals without the intervention of the CPU, increasing data throughput and decreasing execution time overhead. Eight independently programmable channels make it possible to service multiple peripherals at virtually the same time, with each channel peripheral performing a different operation. Many types of data transfer operations are supported.

## 1.3 Other Special Features

- Peripheral Pin Select: The Peripheral Pin Select (PPS) feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

- **Configurable Logic Cell:** The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins.

- **Timing Modules:** The PIC24FJ1024GA610/GB610 family provides five independent, general purpose, 16-bit timers (four of which can be combined into two 32-bit timers). The devices also include 3 multiple output and 4 single output advanced Capture/Compare/PWM/Timer peripherals, and 6 independent legacy Input Capture and 6 independent legacy Output Compare modules.

- Communications: The PIC24FJ1024GA610/ GB610 family incorporates a range of serial communication peripherals to handle a range of application requirements. There are 3 independent I<sup>2</sup>C modules that support both Master and Slave modes of operation. Devices also have, through the PPS feature, 6 independent UARTs with built-in IrDA<sup>®</sup> encoders/decoders and 3 SPI modules.

- Analog Features: All members of the PIC24FJ1024GA610/GB610 family include the new 12-bit A/D Converter (A/D) module and a triple comparator module. The A/D module incorporates a range of new features that allow the converter to assess and make decisions on incoming data, reducing CPU overhead for routine A/D conversions. The comparator module includes three analog comparators that are configurable for a wide range of operations.

- **CTMU Interface:** In addition to their other analog features, members of the PIC24FJ1024GA610/ GB610 family include the CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- Enhanced Parallel Master/Parallel Slave Port: This module allows rapid and transparent access to the microcontroller data bus, and enables the CPU to directly address external data memory. The parallel port can function in Master or Slave mode, accommodating data widths of 4, 8 or 16 bits and address widths of up to 23 bits in Master modes.

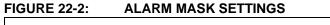

- Real-Time Clock and Calendar (RTCC): This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

# 1.4 Details on Individual Family Members

Devices in the PIC24FJ1024GA610/GB610 family are available in 64-pin, 100-pin and 121-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in six ways:

- Flash program memory (128 Kbytes for PIC24FJ128GX6XX devices, 256 Kbytes for PIC24FJ256GX6XX devices, 512 Kbytes for PIC24FJ512GX6XX devices and 1024 Kbytes for PIC24FJ1024GX6XX devices).

- Available I/O pins and ports (53 pins on 6 ports for 64-pin devices and 85 pins on 7 ports for 100-pin and 121-pin devices).

- Available Interrupt-on-Change Notification (IOC) inputs (53 on 64-pin devices and 85 on 100-pin and 121-pin devices).

- 4. Available remappable pins (29 pins on 64-pin devices, 44 pins on 100-pin and 121-pin devices).

- Available USB peripheral (available on PIC24FJXXXGB6XX devices; not available on PIC24FJXXXGA6XX devices).

- 6. Analog input channels (16 channels for 64-pin devices and 24 channels for 100-pin and 121-pin devices).

All other features for devices in this family are identical. These are summarized in Table 1-1, Table 1-2 and Table 1-3.

A list of the pin features available on the PIC24FJ1024GA610/GB610 family devices, sorted by function, is shown in Table 1-3. Note that this table shows the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

| R/S-0, HC <sup>(</sup>   | <sup>(1)</sup> R/W-0 <sup>(1)</sup>                                         | R-0, HSC <sup>(1)</sup>                                                                    | r-0         | R-0, HSC <sup>(1,3)</sup>                  | R-0 <sup>(1)</sup>    | U-0                   | U-0                   |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------|--------------------------------------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

| WR                       | WREN                                                                        | WRERR                                                                                      |             | SFTSWP                                     | P2ACTIV               | _                     |                       |  |  |  |  |

| bit 15                   |                                                                             | <u> </u>                                                                                   |             |                                            |                       | _                     | bit                   |  |  |  |  |

|                          |                                                                             |                                                                                            |             |                                            |                       |                       |                       |  |  |  |  |

| U-0                      | U-0                                                                         | U-0                                                                                        | U-0         | R/W-0 <sup>(1)</sup>                       | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  | R/W-0 <sup>(1)</sup>  |  |  |  |  |

|                          | —                                                                           | —                                                                                          |             | NVMOP3 <sup>(2)</sup>                      | NVMOP2 <sup>(2)</sup> | NVMOP1 <sup>(2)</sup> | NVMOP0 <sup>(2)</sup> |  |  |  |  |

| bit 7                    |                                                                             |                                                                                            |             |                                            |                       |                       | bit                   |  |  |  |  |

|                          |                                                                             |                                                                                            |             |                                            |                       |                       |                       |  |  |  |  |

| Legend:                  |                                                                             | S = Settable b                                                                             | bit         | HC = Hardware                              | Clearable bit         | r = Reserved I        | oit                   |  |  |  |  |

| R = Reada                | able bit                                                                    | W = Writable                                                                               | bit         | '0' = Bit is cleare                        | ed                    | x = Bit is unkn       | own                   |  |  |  |  |

| -n = Value               | at POR                                                                      | '1' = Bit is set                                                                           |             | U = Unimpleme                              | nted bit, read as     | s '0'                 |                       |  |  |  |  |

| HSC = Hai                | rdware Settable                                                             | /Clearable bit                                                                             |             |                                            |                       |                       |                       |  |  |  |  |

|                          |                                                                             |                                                                                            |             |                                            |                       |                       |                       |  |  |  |  |

| oit 15                   | WR: Write C                                                                 | Control bit <sup>(1,4)</sup>                                                               |             |                                            |                       |                       |                       |  |  |  |  |

|                          |                                                                             |                                                                                            |             | m or erase operat                          |                       | on is self-timed      | and the bit           |  |  |  |  |

|                          |                                                                             |                                                                                            |             | eration is complete<br>mplete and inactive |                       |                       |                       |  |  |  |  |

| oit 14                   |                                                                             |                                                                                            |             |                                            | •                     |                       |                       |  |  |  |  |

| <i>л</i> (1 <del>4</del> |                                                                             | WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations        |             |                                            |                       |                       |                       |  |  |  |  |

|                          |                                                                             | Flash program/                                                                             |             |                                            |                       |                       |                       |  |  |  |  |

| oit 13                   | WRERR: W                                                                    | WRERR: Write Sequence Error Flag bit <sup>(1)</sup>                                        |             |                                            |                       |                       |                       |  |  |  |  |

|                          |                                                                             | 1 = An improper program or erase sequence attempt, or termination has occurred (bit is set |             |                                            |                       |                       |                       |  |  |  |  |

|                          |                                                                             | tically on any se                                                                          |             |                                            |                       |                       |                       |  |  |  |  |

| -: 10                    | -                                                                           | -                                                                                          | operation c | completed normally                         | ,                     |                       |                       |  |  |  |  |

| oit 12                   |                                                                             | Maintain as '0'<br>oft Swap Status                                                         |             |                                            |                       |                       |                       |  |  |  |  |

| oit 11                   |                                                                             |                                                                                            | S DIT(1,0)  |                                            |                       |                       |                       |  |  |  |  |

|                          | Read as '0'.                                                                | rtition Mode:                                                                              |             |                                            |                       |                       |                       |  |  |  |  |

|                          | In Dual Part                                                                |                                                                                            |             |                                            |                       |                       |                       |  |  |  |  |

|                          |                                                                             |                                                                                            |             | swapped using the                          |                       | ruction               |                       |  |  |  |  |

|                          |                                                                             | - ·                                                                                        |             | sing the BOOTSWP                           | instruction           |                       |                       |  |  |  |  |

| oit 10                   | -                                                                           | ual Partition Ac                                                                           | tive Status | bit <sup>(1)</sup>                         |                       |                       |                       |  |  |  |  |

|                          | In Single Pa<br>Read as '0'.                                                | rtition Mode:                                                                              |             |                                            |                       |                       |                       |  |  |  |  |

|                          |                                                                             |                                                                                            |             |                                            |                       |                       |                       |  |  |  |  |

|                          | In Dual Partition Mode:<br>1 = Partition 2 is mapped into the active region |                                                                                            |             |                                            |                       |                       |                       |  |  |  |  |

|                          |                                                                             | 1 is mapped in                                                                             |             |                                            |                       |                       |                       |  |  |  |  |

| oit 9-4                  | Unimpleme                                                                   | nted: Read as                                                                              | '0'         |                                            |                       |                       |                       |  |  |  |  |

|                          | These bits can                                                              | only be reset or                                                                           | n a Power-  | on Reset.                                  |                       |                       |                       |  |  |  |  |

| Note 1:                  |                                                                             | -                                                                                          |             |                                            |                       |                       |                       |  |  |  |  |

|                          | All other combi                                                             | 114110115 01 11 11                                                                         | UPS3.02 a   | are unimplemented                          |                       |                       |                       |  |  |  |  |

| 2:                       |                                                                             |                                                                                            |             | are unimplemented<br>any Reset.            | •                     |                       |                       |  |  |  |  |

| 2:<br>3:                 | This bit may be                                                             | cleared by soft                                                                            | ware or by  | •                                          |                       | h memory progr        | am or erase           |  |  |  |  |

#### 6.6.2 PROGRAMMING A DOUBLE WORD OF FLASH PROGRAM MEMORY

If a Flash location has been erased, it can be programmed using Table Write instructions to write two instruction words (2 x 24-bit) into the write latch. The TBLPAG register is loaded with the address of the write latches and the NVMADRU/NVMADR registers are loaded with the address of the first of the two instruction words to be programmed. The TBLWTL and TBLWTH instructions write the desired data into the write latches. To configure the NVMCON register for a two-word write, set the NVMOPx bits (NVMCON<3:0>) to '0001'. The write is performed by executing the unlock sequence and setting the WR bit. An equivalent procedure in 'C', using the MPLAB<sup>®</sup> XC16 compiler and built-in hardware functions, is shown in Example 6-3.

| TABLE 6-2: | PROGRAMMING A DOUBLE WORD OF FLASH PROGRAM MEMORY |

|------------|---------------------------------------------------|

|            |                                                   |

| Step 1: Init | ialize the TBLPAG register for writing to the latches.                                    |

|--------------|-------------------------------------------------------------------------------------------|

| MOV          | #0xFA, W12                                                                                |

| MOV          | W12, TBLPAG                                                                               |

| Step 2: Loa  | ad W0:W2 with the next two packed instruction words to program.                           |

| MOV          | # <lsw0>, W0</lsw0>                                                                       |

| MOV          | # <msb1:msb0>, W1</msb1:msb0>                                                             |

| MOV          | # <lsw1>, W2</lsw1>                                                                       |

| Step 3: Set  | t the Read Pointer (W6) and Write Pointer (W7), and load the (next set of) write latches. |

| CLR          | W6                                                                                        |

| CLR          | W7                                                                                        |

| TBLWTL       | [W6++], [W7]                                                                              |

|              | [W6++], [W7++]                                                                            |

| TBLWTH.B     | [W6++], [++W7]                                                                            |

| TBLWTL.W     | [W6++], [W7++]                                                                            |

| Step 4: Set  | t the NVMADRU/NVMADR register pair to point to the correct address.                       |

| MOV          | <pre>#DestinationAddress&lt;15:0&gt;, W3</pre>                                            |

| MOV          | #DestinationAddress<23:16>, W4                                                            |

| MOV          | W3, NVMADR                                                                                |

| MOV          | W4, NVMADRU                                                                               |

| Step 5: Set  | t the NVMCON register to program two instruction words.                                   |

| MOV          | #0x4001, W10                                                                              |

| MOV          | W10, NVMCON                                                                               |

| NOP          |                                                                                           |

| Step 6: Init | iate the write cycle.                                                                     |

| MOV          | #0x55, W1                                                                                 |

| MOV          | W1, NVMKEY                                                                                |

| MOV          | #OxAA, W1                                                                                 |

| MOV          | W1, NVMKEY                                                                                |

| BSET         | NVMCON, #WR                                                                               |

| NOP          |                                                                                           |

| NOP          |                                                                                           |

| NOP          |                                                                                           |

# 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Reset" (DS39712), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

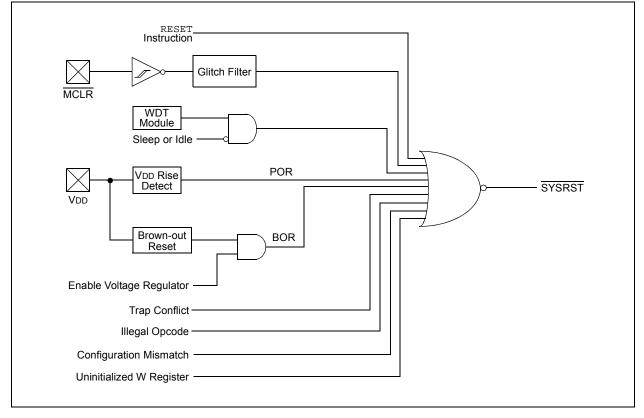

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Note: Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A POR will clear all bits, except for the BOR and POR (RCON<1:0>) bits, which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register values after a device Reset will be meaningful.

#### FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

© 2015-2016 Microchip Technology Inc.

#### REGISTER 7-1: RCON: RESET CONTROL REGISTER (CONTINUED)

| bit 5   | SWDTEN: Software Enable/Disable of WDT bit <sup>(4)</sup>                                                      |

|---------|----------------------------------------------------------------------------------------------------------------|

|         | 1 = WDT is enabled                                                                                             |

|         | 0 = WDT is disabled                                                                                            |

| bit 4   | WDTO: Watchdog Timer Time-out Flag bit <sup>(1)</sup>                                                          |

|         | 1 = WDT time-out has occurred                                                                                  |

|         | 0 = WDT time-out has not occurred                                                                              |

| bit 3   | SLEEP: Wake from Sleep Flag bit <sup>(1)</sup>                                                                 |

|         | 1 = Device has been in Sleep mode                                                                              |

|         | 0 = Device has not been in Sleep mode                                                                          |

| bit 2   | IDLE: Wake-up from Idle Flag bit <sup>(1)</sup>                                                                |

|         | 1 = Device has been in Idle mode                                                                               |

|         | 0 = Device has not been in Idle mode                                                                           |

| bit 1   | BOR: Brown-out Reset Flag bit <sup>(1)</sup>                                                                   |

|         | 1 = A Brown-out Reset has occurred (also set after a Power-on Reset)                                           |

|         | 0 = A Brown-out Reset has not occurred                                                                         |

| bit 0   | POR: Power-on Reset Flag bit <sup>(1)</sup>                                                                    |

|         | 1 = A Power-on Reset has occurred                                                                              |

|         | 0 = A Power-on Reset has not occurred                                                                          |

| Note 1: | All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not |

cause a device Reset.

- 2: If the LPCFG Configuration bit is '1' (unprogrammed), the retention regulator is disabled and the RETEN bit has no effect. Retention mode preserves the SRAM contents during Sleep.

- **3:** Re-enabling the regulator after it enters Standby mode will add a delay, TVREG, when waking up from Sleep. Applications that do not use the voltage regulator should set this bit to prevent this delay from occurring.

- 4: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Flag Bit          | Setting Event                                     | Clearing Event                  |

|-------------------|---------------------------------------------------|---------------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                             |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                             |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                             |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                             |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                             |

| WDTO (RCON<4>)    | WDT Time-out                                      | CLRWDT, PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #0 Instruction                             | POR                             |

| IDLE (RCON<2>)    | PWRSAV #1 Instruction                             | POR                             |

| BOR (RCON<1>)     | POR, BOR                                          |                                 |

| POR (RCON<0>)     | POR                                               |                                 |

#### TABLE 7-1: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits may be set or cleared by the user software.

# PIC24FJ1024GA610/GB610 FAMILY

| U-0          | U-0                                                                                                                           | U-0                                                                                                                                     | U-0 | U-0               | U-0              | U-0            | U-0                  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|------------------|----------------|----------------------|--|--|

|              | —                                                                                                                             | —                                                                                                                                       |     | —                 | _                | _              | _                    |  |  |

| bit 15       |                                                                                                                               |                                                                                                                                         |     |                   |                  |                | bit 8                |  |  |

|              |                                                                                                                               |                                                                                                                                         |     |                   |                  |                |                      |  |  |

| U-0          | U-0                                                                                                                           | R/W-0                                                                                                                                   | U-0 | R/W-0             | R/W-0            | R/W-0          | R/W-0                |  |  |

| —            | —                                                                                                                             | U4MD                                                                                                                                    | —   | REFOMD            | CTMUMD           | LVDMD          | USBMD <sup>(1)</sup> |  |  |

| bit 7        |                                                                                                                               |                                                                                                                                         |     |                   |                  |                | bit C                |  |  |

| Legend:      |                                                                                                                               |                                                                                                                                         |     |                   |                  |                |                      |  |  |

| R = Readat   | ole bit                                                                                                                       | W = Writable b                                                                                                                          | oit | U = Unimplem      | nented bit, read | l as '0'       |                      |  |  |

| -n = Value a | at POR                                                                                                                        | '1' = Bit is set                                                                                                                        |     | '0' = Bit is clea | ared             | x = Bit is unk | nown                 |  |  |

| bit 4        |                                                                                                                               | is disabled<br>power and clock<br><b>nted:</b> Read as '0                                                                               |     | enabled           |                  |                |                      |  |  |

| bit 3        | 1 = Module                                                                                                                    | <b>REFOMD:</b> Reference Output Clock Disable bit         1 = Module is disabled         0 = Module power and clock sources are enabled |     |                   |                  |                |                      |  |  |

| bit 2        | <b>CTMUMD:</b> CTMU Module Disable bit<br>1 = Module is disabled<br>0 = Module power and clock sources are enabled            |                                                                                                                                         |     |                   |                  |                |                      |  |  |

| bit 1        | LVDMD: High/Low-Voltage Detect Module Disable bit<br>1 = Module is disabled<br>0 = Module power and clock sources are enabled |                                                                                                                                         |     |                   |                  |                |                      |  |  |

| bit 0        | USBMD: US<br>1 = Module<br>0 = Module                                                                                         |                                                                                                                                         |     |                   |                  |                |                      |  |  |

#### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE REGISTER 4

**Note 1:** USB is not present on PIC24FJXXXXGA6XX devices.

# 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. In an application that needs to use more than one peripheral multiplexed on a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of any one of many digital peripherals to any one of these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The PPS feature is used with a range of up to 44 pins, depending on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

PIC24FJ1024GA610/GB610 family devices support a larger number of remappable input/output pins than remappable input only pins. In this device family, there are up to 44 remappable input/output pins, depending on the pin count of the particular device selected. These pins are numbered, RP0 through RP31, and RPI32 through RPI43.

See Table 1-1 for a summary of pinout options in each package offering.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals. PPS is not available for these peripherals:

- I<sup>2</sup>C (input and output)

- Input Change Notifications

- EPMP Signals (input and output)

- Analog (inputs and outputs)

- INT0

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 11.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g., output compare, UART transmit) will take priority over general purpose digital functions on a pin, such as EPMP and port I/O. Specialized digital outputs will take priority over PPS outputs on the same pin. The pin diagrams list peripheral outputs in the order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pinselectable peripheral inputs will never take ownership of a pin. The pin's output buffer will be controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in Digital mode, then the PPS input will operate correctly. If an analog function is enabled on the pin, the PPS input will be disabled.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | SCK2R5 | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|        |     |        |        |        |        |        |        |

#### REGISTER 11-30: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK2R<5:0>: Assign SPI2 Clock Input (SCK2IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI2R<5:0>: Assign SPI2 Data Input (SDI2) to Corresponding RPn or RPIn Pin bits    |

#### REGISTER 11-31: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | TXCKR5 | TXCKR4 | TXCKR3 | TXCKR2 | TXCKR1 | TXCKR0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS2R5 | SS2R4 | SS2R3 | SS2R2 | SS2R1 | SS2R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **TXCKR<5:0>:** Assign General Timer External Input (TxCK) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SS2R<5:0>: Assign SPI2 Slave Select Input (SS2IN) to Corresponding RPn or RPIn Pin bits

| R/W-0                 | U-0            | R/W-0                                   | R/W-0               | R/W-0             | U-0              | R/W-0            | R/W-0           |

|-----------------------|----------------|-----------------------------------------|---------------------|-------------------|------------------|------------------|-----------------|

| UARTEN <sup>(1)</sup> | —              | USIDL                                   | IREN <sup>(2)</sup> | RTSMD             | —                | UEN1             | UEN0            |

| bit 15                |                |                                         |                     |                   |                  |                  | bit 8           |

|                       | <b>D</b> /// 0 |                                         |                     | DAMA              | DAMA             | DAALO            | <b>D</b> /// 0  |

| R/W-0, HC             | R/W-0          | R/W-0, HC                               | R/W-0               | R/W-0             | R/W-0            | R/W-0            | R/W-0           |

| WAKE                  | LPBACK         | ABAUD                                   | URXINV              | BRGH              | PDSEL1           | PDSEL0           | STSEL           |

| bit 7                 |                |                                         |                     |                   |                  |                  | bit             |

| Legend:               |                | HC = Hardwar                            | e Clearable bi      | t                 |                  |                  |                 |

| R = Readabl           | le bit         | W = Writable b                          | bit                 | U = Unimplen      | nented bit, read | 1 as '0'         |                 |

| -n = Value at         | t POR          | '1' = Bit is set                        |                     | '0' = Bit is clea |                  | x = Bit is unkn  | own             |

|                       |                |                                         |                     |                   |                  |                  | -               |

| bit 15                | UARTEN: UA     | ARTx Enable bit                         | (1)                 |                   |                  |                  |                 |

|                       |                | s enabled; all UA                       |                     | controlled by L   | JARTx as define  | ed by UEN<1:0    | >               |

|                       |                | disabled; all UA                        |                     |                   |                  |                  |                 |

| bit 14                | Unimplemen     | ted: Read as '0                         | 3                   |                   |                  |                  |                 |

| bit 13                | USIDL: UAR     | Tx Stop in Idle M                       | lode bit            |                   |                  |                  |                 |

|                       |                | ues module ope                          |                     |                   | e mode           |                  |                 |

|                       |                | s module operat                         |                     |                   |                  |                  |                 |

| bit 12                |                | Encoder and De                          |                     |                   |                  |                  |                 |

|                       |                | oder and decode                         |                     |                   |                  |                  |                 |

|                       |                | oder and decode                         |                     |                   |                  |                  |                 |

| bit 11                |                | de Selection for                        |                     |                   |                  |                  |                 |

|                       |                | in is in Simplex i<br>in is in Flow Cor |                     |                   |                  |                  |                 |

| bit 10                | Unimplemen     | ted: Read as '0                         | ,                   |                   |                  |                  |                 |

| bit 9-8               | UEN<1:0>: し    | JARTx Enable b                          | its                 |                   |                  |                  |                 |

|                       |                | JxRX and BCLK                           |                     |                   |                  | controlled by po | rt latches      |

|                       |                | JxRX, UxCTS a                           |                     |                   |                  |                  | wt latabaa      |

|                       |                | JxRX and UxRT<br>nd UxRX pins ar        |                     |                   |                  |                  |                 |

|                       | latches        |                                         |                     |                   |                  |                  | itiolica by po  |

| bit 7                 | WAKE: Wake     | e-up on Start Bit                       | Detect During       | Sleep Mode E      | nable bit        |                  |                 |

|                       | 1 = UARTx o    | continues to sam                        | ple the UxRX        | pin; interrupt is | generated on     | the falling edge | , bit is cleare |

|                       |                | are on the follow                       | /ing rising edg     | e                 |                  |                  |                 |

|                       | 0 = No wake    | -up is enabled                          |                     |                   |                  |                  |                 |

| bit 6                 |                | ARTx Loopback                           | Mode Select b       | bit               |                  |                  |                 |

|                       |                | Loopback mode<br>c mode is disable      | ed                  |                   |                  |                  |                 |

| bit 5                 | •              | o-Baud Enable b                         |                     |                   |                  |                  |                 |

|                       |                | baud rate meas                          |                     | e next charact    | er – requires re | eception of a Sy | nc field (55h   |

|                       | cleared i      | n hardware upo<br>e measurement         | n completion        |                   | ·                | , ,              | Υ.              |

| bit 4                 |                | RTx Receive Po                          |                     | •                 |                  |                  |                 |

| ~                     | 1 = UxRX Idle  |                                         |                     |                   |                  |                  |                 |

|                       | 0 = UxRX Idle  |                                         |                     |                   |                  |                  |                 |

| Note 1: If            |                | the peripheral ir                       | nute and oute       | ute muet he co    | nfigured to an c | availahle DDn/D  | Pla nin For     |

|                       |                | n, see Section 1                        |                     |                   | -                |                  | ι πιρπ. Ευ      |

|                       |                |                                         |                     |                   | ····             |                  |                 |

#### REGISTER 19-1: UXMODE: UARTX MODE REGISTER

2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### 20.5.3 SEND A FULL-SPEED BULK DATA TRANSFER TO A TARGET DEVICE

- Follow the procedure described in Section 20.5.1 "Enable Host Mode and Discover a Connected Device" and Section 20.5.2 "Complete a Control Transaction to a Connected Device" to discover and configure a device.

- To enable transmit and receive transfers with handshaking enabled, write 1Dh to U1EP0. If the target device is a low-speed device, also set the LSPD (U1EP0<7>) bit. If you want the hardware to automatically retry indefinitely if the target device asserts a NAK on the transfer, clear the Retry Disable bit, RETRYDIS (U1EP0<6>).

- 3. Set up the BD for the current (even or odd) TX EP0 to transfer up to 64 bytes.

- 4. Set the USB device address of the target device in the address register (U1ADDR<6:0>).

- 5. Write an OUT token to the desired endpoint to U1TOK. This triggers the module's transmit state machines to begin transmitting the token and the data.

- 6. Wait for the Token Complete Interrupt Flag, TRNIF. This indicates that the BD has been released back to the microprocessor and the transfer has completed. If the Retry Disable bit (RETRYDIS) is set, the handshake (ACK, NAK, STALL or ERROR (0Fh)) is returned in the BD PID field. If a STALL interrupt occurs, the pending packet must be dequeued and the error condition in the target device cleared. If a detach interrupt occurs (SE0 for more than 2.5 µs), then the target has detached (U1IR<0> is set).

- 7. Once the Token Complete Interrupt Flag occurs (TRNIF is set), the BD can be examined and the next data packet queued by returning to Step 2.

- **Note:** USB speed, transceiver and pull-ups should only be configured during the module setup phase. It is not recommended to change these settings while the module is enabled.

#### 20.6 OTG Operation

#### 20.6.1 SESSION REQUEST PROTOCOL (SRP)

An OTG A-device may decide to power down the VBUS supply when it is not using the USB link through the Session Request Protocol (SRP). SRP can only be initiated at full speed. Software may do this by configuring a GPIO pin to disable an external power transistor, or voltage regulator enable signal, which controls the VBUS supply. When the VBUS supply is powered down, the A-device is said to have ended a USB session.

An OTG A-device or embedded host may repower the VBUS supply at any time (initiate a new session). An OTG B-device may also request that the OTG A-device repower the VBUS supply (initiate a new session). This is accomplished via Session Request Protocol (SRP).

Prior to requesting a new session, the B-device must first check that the previous session has definitely ended. To do this, the B-device must check for two conditions:

- 1. VBUS supply is below the session valid voltage.

- 2. Both D+ and D- have been low for at least 2 ms.

The B-device will be notified of Condition 1 by the SESENDIF (U1OTGIR<2>) interrupt. Software will have to manually check for Condition 2.

| Note: | When the A-device powers down the            |

|-------|----------------------------------------------|

|       | VBUS supply, the B-device must discon-       |

|       | nect its pull-up resistor from power. If the |

|       | device is self-powered, it can do this by    |

|       | clearing DPPULUP (U1OTGCON<7>) and           |

|       | DMPULUP (U1OTGCON<6>).                       |

The B-device may aid in achieving Condition 1 by discharging the VBUS supply through a resistor. Software may do this by setting VBUSDIS (U1OTGCON<0>).

After these initial conditions are met, the B-device may begin requesting the new session. The B-device begins by pulsing the D+ data line. Software should do this by setting DPPULUP (U10TGCON<7>). The data line should be held high for 5 to 10 ms.

The B-device then proceeds by pulsing the VBUS supply. Software should do this by setting PUVBUS (U1CNFG2<4>). When an A-device detects SRP signaling (either via the ATTACHIF (U1IR<6>) interrupt or via the SESVDIF (U1OTGIR<3>) interrupt), the A-device must restore the VBUS supply by properly configuring the general purpose I/O port pin controlling the external power source.

The B-device should not monitor the state of the VBUS supply while performing VBUS supply pulsing. When the B-device does detect that the VBUS supply has been restored (via the SESVDIF (U10TGIR<3>) interrupt), the B-device must reconnect to the USB link by pulling up D+ or D- (via the DPPULUP or DMPULUP bit).

The A-device must complete the SRP by driving USB Reset signaling.

#### 20.6.2 HOST NEGOTIATION PROTOCOL (HNP)

In USB OTG applications, a Dual Role Device (DRD) is a device that is capable of being either a host or a peripheral. Any OTG DRD must support Host Negotiation Protocol (HNP).

HNP allows an OTG B-device to temporarily become the USB host. The A-device must first enable the B-device to follow HNP. Refer to the *"On-The-Go Supplement"* to the *"USB 2.0 Specification"* for more information regarding HNP. HNP may only be initiated at full speed.

After being enabled for HNP by the A-device, the B-device requests being the host any time that the USB link is in the suspend state, by simply indicating a disconnect. This can be done in software by clearing DPPULUP and DMPULUP. When the A-device detects the disconnect condition (via the URSTIF (U1IR<0>) interrupt), the A-device may allow the B-device to take over as host. The A-device does this by signaling connect as a full-speed function. Software may accomplish this by setting DPPULUP.

If the A-device responds instead with resume signaling, the A-device remains as host. When the B-device detects the connect condition (via ATTACHIF, U1IR<6>), the B-device becomes host. The B-device drives Reset signaling prior to using the bus.

When the B-device has finished in its role as host, it stops all bus activity and turns on its D+ pull-up resistor by setting DPPULUP. When the A-device detects a suspend condition (Idle for 3 ms), the A-device turns off its D+ pull-up. The A-device may also power down the VBUS supply to end the session. When the A-device detects the connect condition (via ATTACHIF), the A-device resumes host operation and drives Reset signaling.

# 20.7 USB OTG Module Registers

There are a total of 37 memory-mapped registers associated with the USB OTG module. They can be divided into four general categories:

- USB OTG Module Control (12)

- USB Interrupt (7)

- USB Endpoint Management (16)

- USB VBUS Power Control (2)

This total does not include the (up to) 128 BD registers in the BDT. Their prototypes, described in Register 20-1 and Register 20-2, are shown separately in **Section 20.2 "USB Buffer Descriptors and the BDT"**.

All USB OTG registers are implemented in the Least Significant Byte (LSB) of the register. Bits in the upper byte are unimplemented and have no function. Note that some registers are instantiated only in Host mode, while other registers have different bit instantiations and functions in Device and Host modes.

The registers described in the following sections are those that have bits with specific control and configuration features. The following registers are used for data or address values only:

- U1BDTP1, U1BDTP2 and U1BDTP3: Specifies the 256-word page in data RAM used for the BDT; 8-bit value with bit 0 fixed as '0' for boundary alignment.

- U1FRML and U1FRMH: Contains the 11-bit byte counter for the current data frame.

| R-0, HSC               | U-0                    | R/C-0, HS                           | R/C-0, HS              | U-0                                     | U-0                       | U-0                    | U-0                    |

|------------------------|------------------------|-------------------------------------|------------------------|-----------------------------------------|---------------------------|------------------------|------------------------|

| BUSY                   | —                      | ERROR                               | TIMEOUT                | —                                       | —                         | —                      | —                      |

| bit 15                 |                        |                                     |                        |                                         |                           |                        | bit 8                  |

|                        |                        |                                     |                        |                                         |                           |                        |                        |

| R/W-0                  | R/W-0                  | R/W-0                               | R/W-0                  | R/W-0                                   | R/W-0                     | R/W-0                  | R/W-0                  |

| RADDR23 <sup>(1)</sup> | RADDR22 <sup>(1)</sup> | RADDR21 <sup>(1)</sup>              | RADDR20 <sup>(1)</sup> | RADDR19 <sup>(1)</sup>                  | RADDR18 <sup>(1)</sup>    | RADDR17 <sup>(1)</sup> | RADDR16 <sup>(1)</sup> |

| bit 7                  |                        |                                     |                        |                                         |                           |                        | bit C                  |

|                        |                        |                                     |                        |                                         |                           |                        |                        |

| Legend:                | 1.11                   |                                     |                        |                                         |                           | 0                      |                        |

| R = Readable           |                        | W = Writable I                      | DIT                    |                                         | ented, read as '          |                        |                        |

| -n = Value at POR      |                        | '1' = Bit is set                    |                        | '0' = Bit is cleared x = Bit is unknown |                           |                        |                        |

| C = Clearable          | bit                    | HS = Hardward                       | e Settable bit         | HSC = Hardw                             | are Settable/Cl           | earable bit            |                        |

| bit 15                 | BUSY: Busy b           | oit (Master mod                     | e only)                |                                         |                           |                        |                        |

|                        | 1 = Port is bu         | sy                                  |                        |                                         |                           |                        |                        |

|                        | 0 = Port is no         | t busy                              |                        |                                         |                           |                        |                        |

| bit 14                 | Unimplement            | ted: Read as 'o                     | )'                     |                                         |                           |                        |                        |

| bit 13                 | ERROR: Error           | r bit                               |                        |                                         |                           |                        |                        |

|                        |                        | on error (illegal<br>on completed s |                        | as requested)                           |                           |                        |                        |

| bit 12                 | TIMEOUT: Tin           | ne-out bit                          | -                      |                                         |                           |                        |                        |

|                        | 1 = Transactio         | on timed out                        |                        |                                         |                           |                        |                        |

|                        | 0 = Transactio         | on completed s                      | successfully           |                                         |                           |                        |                        |

| bit 11-8               | Unimplement            | ted: Read as 'o                     | )'                     |                                         |                           |                        |                        |

| bit 7-0                | RADDR<23:1             | 6>: Parallel Ma                     | aster Port Rese        | erved Address S                         | Space bits <sup>(1)</sup> |                        |                        |

| Note 1: If R           |                        |                                     |                        | DS address for                          |                           | will be FFFFF          | <sup>-</sup> h.        |

#### REGISTER 21-2: PMCON2: EPMP CONTROL REGISTER 2

|                           | R/W-0                                                                                                                                                                              | R/W-0                                                                                                                                                                                              | R/W-0                                                                                                                                          | U-0                              | R/W-0            | R/W-0           | R/W-0 |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|-----------------|-------|--|

| CSDIS                     | CSP                                                                                                                                                                                | CSPTEN                                                                                                                                                                                             | BEP                                                                                                                                            |                                  | WRSP             | RDSP            | SM    |  |

| bit 15                    |                                                                                                                                                                                    |                                                                                                                                                                                                    |                                                                                                                                                |                                  |                  |                 | bit   |  |

| R/W-0                     | R/W-0                                                                                                                                                                              | R/W-0                                                                                                                                                                                              | U-0                                                                                                                                            | U-0                              | U-0              | U-0             | U-0   |  |

| ACKP                      | PTSZ1                                                                                                                                                                              | PTSZ0                                                                                                                                                                                              |                                                                                                                                                |                                  | _                | _               |       |  |

| bit 7                     |                                                                                                                                                                                    |                                                                                                                                                                                                    |                                                                                                                                                |                                  |                  |                 | bit   |  |

| Legend:                   |                                                                                                                                                                                    |                                                                                                                                                                                                    |                                                                                                                                                |                                  |                  |                 |       |  |

| R = Readabl               | e bit                                                                                                                                                                              | W = Writable I                                                                                                                                                                                     | oit                                                                                                                                            | U = Unimpler                     | nented bit, read | 1 as '0'        |       |  |