Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Active                                                                          |

| Core Processor            | PIC                                                                             |

| Core Size                 | 16-Bit                                                                          |

| Speed                     | 32MHz                                                                           |

| onnectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| eripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| lumber of I/O             | 85                                                                              |

| rogram Memory Size        | 512KB (170K x 24)                                                               |

| rogram Memory Type        | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| AM Size                   | 32K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| ata Converters            | A/D 24x10/12b                                                                   |

| scillator Type            | Internal                                                                        |

| perating Temperature      | -40°C ~ 85°C (TA)                                                               |

| lounting Type             | Surface Mount                                                                   |

| ackage / Case             | 100-TQFP                                                                        |

| upplier Device Package    | 100-TQFP (12x12)                                                                |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj512ga610t-i-pt |

TABLE 5: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJXXXGB610 TQFP)

| Pin | Function                                         | Pin | Function                          |

|-----|--------------------------------------------------|-----|-----------------------------------|

|     |                                                  | ļ   |                                   |

| 1   | OCM1C/CTED3/RG15                                 | 51  | RP16/USBID/RF3                    |

| 2   | VDD                                              | 52  | RP30/RF2                          |

| 3   | IC4/CTED4/PMD5/RE5                               | 53  | RP15/RF8                          |

| 4   | SCL3/IC5/PMD6/RE6                                | 54  | VBUS/RF7                          |

| 5   | SDA3/IC6/PMD7/RE7                                | 55  | Vusbaya                           |

| 6   | RPI38/OCM1D/RC1                                  | 56  | D-/RG3                            |

| 7   | RPI39/OCM2C/RC2                                  | 57  | D+/RG2                            |

| 8   | RPI40/OCM2D/RC3                                  | 58  | PMPCS1/SCL2/RA2                   |

| 9   | AN16/RPI41/OCM3C/PMCS2/RC4                       | 59  | SDA2/PMA20/RA3                    |

| 10  | AN17/C1IND/RP21/ICM1/OCM1A/PMA5/RG6              | 60  | TDI/PMA21/RA4                     |

| 11  | AN18/C1INC/RP26/OCM1B/PMA4/RG7                   | 61  | TDO/RA5                           |

| 12  | AN19/C2IND/ <b>RP19</b> /ICM2/OCM2A/PMA3/RG8     | 62  | VDD                               |

| 13  | MCLR                                             | 63  | OSCI/CLKI/RC12                    |

| 14  | AN20/C1INC/C2INC/C3INC/RP27/OCM2B/PMA2/PMALU/RG9 | 64  | OSCO/CLKO/RC15                    |

| 15  | Vss                                              | 65  | Vss                               |

| 16  | VDD                                              | 66  | RPI36/SCL1/PMA22/RA14             |

| 17  | TMS/OCM3D/RA0                                    | 67  | RPI35/SDA1/PMBE1/RA15             |

| 18  | RPI33/PMCS1/RE8                                  | 68  | CLC4OUT/RP2/U6RTS/U6BCLK/ICM5/RD8 |

| 19  | AN21/ <b>RPI34</b> /PMA19/RE9                    | 69  | RP4/PMACK2/RD9                    |

| 20  | PGEC3/AN5/C1INA/RP18/ICM3/OCM3A/RB5              | 70  | RP3/PMA15/PMCS2/RD10              |

| 21  | PGED3/AN4/C1INB/RP28/USBOEN/OCM3B/RB4            | 71  | RP12/PMA14/PMCS1/RD11             |

| 22  | AN3/C2INA/RB3                                    | 72  | CLC3OUT/RP11/U6CTS/ICM6/INT0/RD0  |

| 23  | AN2/CTCMP/C2INB/RP13/CTED13/RB2                  | 73  | SOSCI/C3IND/RC13                  |

| 24  | PGEC1/ALTCVREF-/ALTVREF-/AN1/RP1/CTED12/RB1      | 74  | SOSCO/C3INC/RPI37/PWRLCLK/RC14    |

| 25  | PGED1/ALTCVREF+/ALTVREF+/AN0/RP0/RB0             | 75  | Vss                               |

| 26  | PGEC2/AN6/ <b>RP6</b> /RB6                       | 76  | RP24/U5TX/ICM4/RD1                |

| 27  | PGED2/AN7/ <b>RP7</b> /U6TX/RB7                  | 77  | RP23/PMACK1/RD2                   |

| 28  | CVREF-/VREF-/PMA7/RA9                            | 78  | RP22/ICM7/PMBE0/RD3               |

| 29  | CVREF+/VREF+/PMA6/RA10                           | 79  | RPI42/OCM3E/PMD12/RD12            |

| 30  | AVDD                                             | 80  | OCM3F/PMD13/RD13                  |

| 31  | AVss                                             | 81  | RP25/PMWR/PMENB/RD4               |

| 32  | AN8/RP8/PWRGT/RB8                                | 82  | RP20/PMRD/PMWR/RD5                |

| 33  | AN9/TMPR/RP9/T1CK/RB9                            | 83  | C3INB/U5RX/OC4/PMD14/RD6          |

| 34  | CVREF/AN10/PMA13/RB10                            | 84  | C3INA/U5RTS/U5BCLK/OC5/PMD15/RD7  |

| 35  | AN11/REFI/PMA12/RB11                             | 85  | VCAP                              |

| 36  | Vss                                              | 86  | N/C                               |

| 37  | VDD                                              | 87  | U5CTS/OC6/PMD11/RF0               |

| 38  | TCK/RA1                                          | 88  | PMD10/RF1                         |

| 39  | <b>RP31</b> /RF13                                | 89  | PMD9/RG1                          |

| 40  | RPI32/CTED7/PMA18/RF12                           | 90  | PMD8/RG0                          |

| 41  | AN12/U6RX/CTED2/PMA11/RB12                       | 91  | AN23/OCM1E/RA6                    |

| 42  | AN13/CTED1/PMA10/RB13                            | 92  | AN22/OCM1F/PMA17/RA7              |

| 43  | AN14/RP14/CTED5/CTPLS/PMA1/PMALH/RB14            | 93  | PMD0/RE0                          |

| 44  | AN15/RP29/CTED6/PMA0/PMALL/RB15                  | 94  | PMD1/RE1                          |

| 45  | Vss                                              | 95  | CTED11/PMA16/RG14                 |

| 46  | VDD                                              | 96  | OCM2E/RG12                        |

| 47  | RPI43/RD14                                       | 96  | OCM2E/RG12 OCM2F/CTED10/RG13      |

| 48  | RP5/RD15                                         |     | PMD2/RE2                          |

|     |                                                  | 98  |                                   |

| 49  | RP10/PMA9/RF4  PP17/PMA9/PF6                     | 99  | CTED9/PMD3/RE3                    |

| 50  | RP17/PMA8/RF5                                    | 100 | HLVDIN/CTED8/PMD4/RE4             |

**Legend:** RPn and RPln represent remappable pins for Peripheral Pin Select (PPS) functions.

Note: Pinouts are subject to change.

TABLE 7: COMPLETE PIN FUNCTION DESCRIPTIONS (PIC24FJXXXGB610 BGA) (CONTINUED)

| Pin | Full Pin Name                                 | Pin | Full Pin Name                         |

|-----|-----------------------------------------------|-----|---------------------------------------|

| J1  | AN3/C2INA/RB3                                 | K7  | AN14/RP14/CTED5/CTPLS/PMA1/PMALH/RB14 |

| J2  | AN2/CTCMP/C2INB/RP13/CTED13/RB2               | K8  | VDD                                   |

| J3  | PGED2/AN7/ <b>RP7</b> /U6TX/RB7               | K9  | <b>RP5</b> /RD15                      |

| J4  | AVDD                                          | K10 | RP16/USBID/RF3                        |

| J5  | AN11/REFI/PMA12/RB11                          | K11 | RP30/RF2                              |

| J6  | TCK/RA1                                       | L1  | PGEC2/AN6/ <b>RP6</b> /RB6            |

| J7  | AN12/U6RX/CTED2/PMA11/RB12                    | L2  | CVREF-/VREF-/PMA7/RA9                 |

| J8  | N/C                                           | L3  | AVss                                  |

| J9  | N/C                                           | L4  | AN9/TMPR/RP9/T1CK/RB9                 |

| J10 | <b>RP15</b> /RF8                              | L5  | CVREF/AN10/PMA13/RB10                 |

| J11 | D-/RG3                                        | L6  | <b>RP31</b> /RF13                     |

| K1  | PGEC1/ALTCVREF-/ALTVREF-/AN1/RP1/CTED12/RB1   | L7  | AN13/CTED1/PMA10/RB13                 |

| K2  | PGED1/ALTCVREF+/ALTVREF+/AN0/ <b>RP0</b> /RB0 | L8  | AN15/RP29/CTED6/PMA0/PMALL/RB15       |

| K3  | CVREF+/VREF+/PMA6/RA10                        | L9  | RPI43/RD14                            |

| K4  | AN8/ <b>RP8</b> /PWRGT/RB8                    | L10 | RP10/PMA9/RF4                         |

| K5  | N/C                                           | L11 | RP17/PMA8/RF5                         |

| K6  | RPI32/CTED7/PMA18/RF12                        |     |                                       |

**Legend:** RPn and RPln represent remappable pins for Peripheral Pin Select (PPS) functions.

Note: Pinouts are subject to change.I

### 1.2 DMA Controller

PIC24FJ1024GA610/GB610 family devices have a Direct Memory Access (DMA) Controller. This module acts in concert with the CPU, allowing data to move between data memory and peripherals without the intervention of the CPU, increasing data throughput and decreasing execution time overhead. Eight independently programmable channels make it possible to service multiple peripherals at virtually the same time, with each channel peripheral performing a different operation. Many types of data transfer operations are supported.

## 1.3 Other Special Features

- Peripheral Pin Select: The Peripheral Pin Select (PPS) feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

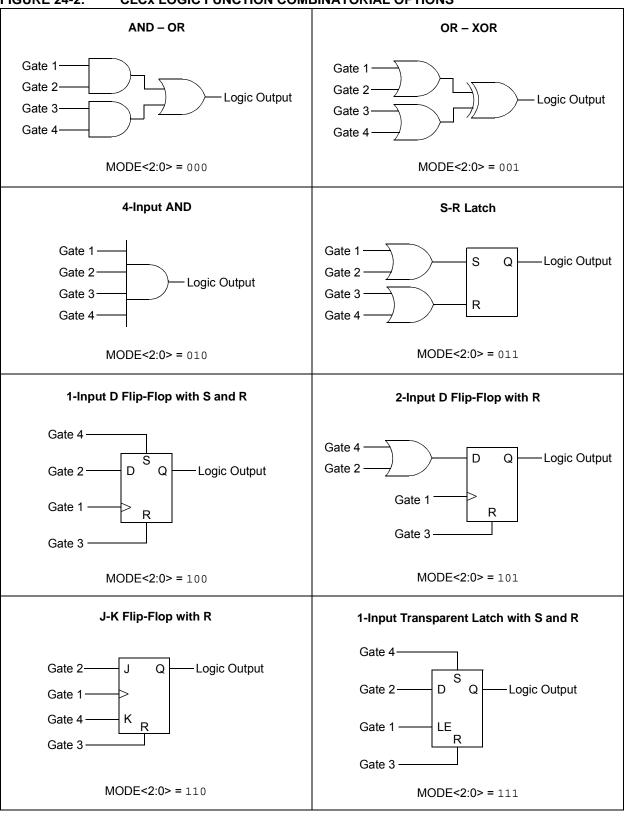

- Configurable Logic Cell: The Configurable Logic Cell (CLC) module allows the user to specify combinations of signals as inputs to a logic function and to use the logic output to control other peripherals or I/O pins.

- Timing Modules: The PIC24FJ1024GA610/GB610 family provides five independent, general purpose, 16-bit timers (four of which can be combined into two 32-bit timers). The devices also include 3 multiple output and 4 single output advanced Capture/Compare/PWM/Timer peripherals, and 6 independent legacy Input Capture and 6 independent legacy Output Compare modules.

- Communications: The PIC24FJ1024GA610/ GB610 family incorporates a range of serial communication peripherals to handle a range of application requirements. There are 3 independent I<sup>2</sup>C modules that support both Master and Slave modes of operation. Devices also have, through the PPS feature, 6 independent UARTs with built-in IrDA<sup>®</sup> encoders/decoders and 3 SPI modules.

- Analog Features: All members of the PIC24FJ1024GA610/GB610 family include the new 12-bit A/D Converter (A/D) module and a triple comparator module. The A/D module incorporates a range of new features that allow the converter to assess and make decisions on incoming data, reducing CPU overhead for routine A/D conversions. The comparator module includes three analog comparators that are configurable for a wide range of operations.

- CTMU Interface: In addition to their other analog features, members of the PIC24FJ1024GA610/ GB610 family include the CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- Enhanced Parallel Master/Parallel Slave Port:

This module allows rapid and transparent access to the microcontroller data bus, and enables the CPU to directly address external data memory. The parallel port can function in Master or Slave mode, accommodating data widths of 4, 8 or 16 bits and address widths of up to 23 bits in Master modes.

- Real-Time Clock and Calendar (RTCC): This

module implements a full-featured clock and

calendar with alarm functions in hardware, freeing

up timer resources and program memory space

for use of the core application.

# 1.4 Details on Individual Family Members

Devices in the PIC24FJ1024GA610/GB610 family are available in 64-pin, 100-pin and 121-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in six ways:

- Flash program memory (128 Kbytes for PIC24FJ128GX6XX devices, 256 Kbytes for PIC24FJ256GX6XX devices, 512 Kbytes for PIC24FJ512GX6XX devices and 1024 Kbytes for PIC24FJ1024GX6XX devices).

- Available I/O pins and ports (53 pins on 6 ports for 64-pin devices and 85 pins on 7 ports for 100-pin and 121-pin devices).

- Available Interrupt-on-Change Notification (IOC) inputs (53 on 64-pin devices and 85 on 100-pin and 121-pin devices).

- Available remappable pins (29 pins on 64-pin devices, 44 pins on 100-pin and 121-pin devices).

- 5. Available USB peripheral (available on PIC24FJXXXGB6XX devices; not available on PIC24FJXXXGA6XX devices).

- Analog input channels (16 channels for 64-pin devices and 24 channels for 100-pin and 121-pin devices).

All other features for devices in this family are identical. These are summarized in Table 1-1, Table 1-2 and Table 1-3.

A list of the pin features available on the PIC24FJ1024GA610/GB610 family devices, sorted by function, is shown in Table 1-3. Note that this table shows the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of this data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

# 4.3.3 READING DATA FROM PROGRAM MEMORY USING EDS

The upper 32 Kbytes of Data Space may optionally be mapped into any 16K word page of the program space. This provides transparent access of stored constant data from the Data Space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the Data Space occurs when the MSb of EA is '1' and the DSRPAG<9> is also '1'. The lower 8 bits of DSRPAG are concatenated to the Wn<14:0> bits to form a 23-bit EA to access program memory. The DSRPAG<8> decides which word should be addressed; when the bit is '0', the lower word, and when '1', the upper word of the program memory is accessed.

The entire program memory is divided into 512 EDS pages, from 200h to 3FFh, each consisting of 16K words of data. Pages, 200h to 2FFh, correspond to the lower words of the program memory, while 300h to 3FFh correspond to the upper words of the program memory.

Using this EDS technique, the entire program memory can be accessed. Previously, the access to the upper word of the program memory was not supported.

Table 4-15 provides the corresponding 23-bit EDS address for program memory with EDS page and source addresses.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

| TARIF 1-15.  | EDS DROCRAM | ADDRESS WITH DIFFERENT PAGES AND ADDRESSES |

|--------------|-------------|--------------------------------------------|

| IADLE 4" 10. |             | AUDRESS WITH DIFFERENT FAGES AND AUDRESSES |

| DSRPAG<br>(Data Space Read Register) |                |                    | Comment                           |

|--------------------------------------|----------------|--------------------|-----------------------------------|

| 200h                                 |                | 000000h to 007FFEh | Lower words of 4M program         |

| •                                    |                | •                  | instructions; (8 Mbytes) for      |

| •                                    |                | •                  | read operations only.             |

| •                                    |                | •                  |                                   |

| 2FFh                                 |                | 7F8000h to 7FFFFEh |                                   |

| 300h                                 | 8000h to FFFFh | 000001h to 007FFFh | Upper words of 4M program         |

| •                                    |                | •                  | instructions (4 Mbytes remaining; |

| •                                    |                | •                  | 4 Mbytes are phantom bytes) for   |

| •                                    |                | •                  | read operations only.             |

| 3FFh                                 |                | 7F8001h to 7FFFFFh |                                   |

| 000h                                 |                | Invalid Address    | Address error trap.(1)            |

**Note 1:** When the source/destination address is above 8000h and DSRPAG/DSWPAG is '0', an address error trap will occur.

### **EXAMPLE 4-3:** EDS READ CODE FROM PROGRAM MEMORY IN ASSEMBLY

```

; Set the EDS page from where the data to be read

#0x0202, w0

mov

mov

w0, DSRPAG

;page 0x202, consisting lower words, is selected for read

mov

#0x000A, w1

; select the location (0x0A) to be read

w1, #15

;set the MSB of the base address, enable EDS mode

bset.

;Read a byte from the selected location

mov.b [w1++], w2

;read Low byte

mov.b [w1++], w3

read High byte;

;Read a word from the selected location

[w1], w2

;Read Double - word from the selected location

mov.d [w1], w2

; two word read, stored in w2 and w3

```

## 8.0 INTERRUPT CONTROLLER

Note 1: This data sheet summarizes the features of the PIC24FJ1024GA610/GB610 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24FJ1024GA610/GB610 family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24FJ1024GA610/GB610 family CPU.

The interrupt controller has the following features:

- Up to Eight Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for Each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- · Fixed Interrupt Entry and Return Latencies

## 8.1 Interrupt Vector Table

The PIC24FJ1024GA610/GB610 family Interrupt Vector Table (IVT), shown in Figure 8-1, resides in program memory starting at location, 000004h. The IVT contains 6 non-maskable trap vectors and up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

# 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. The AIVTEN (INTCON2<8>) control bit provides access to the AIVT. If the AIVTEN bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT is available only if the Boot Segment has been defined and the AIVT has been enabled. To enable the AIVT, both the Configuration bit, AIVTDIS (FSEC<15>), and the AIVTEN bit (INTCON2<8> in the SFR), have to be set. When the AIVT is enabled, all interrupts and exception processes use the alternate vectors instead of the default vectors. The AIVT begins at the start of the last page of the Boot Segment (BS) defined by the BSLIM<12:0> bits. The AIVT address is:  $(BSLIM<12:0>-1) \times 0\times800$ .

## 8.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24FJ1024GA610/GB610 family devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

Note: Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | U-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0                |

|-------|-----|-------|-----|--------|--------|-------|----------------------|

| _     | _   | U4MD  | _   | REFOMD | CTMUMD | LVDMD | USBMD <sup>(1)</sup> |

| bit 7 |     |       |     |        |        |       | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5 **U4MD:** UART4 Module Disable bit 1 = Module is disabled

0 = Module power and clock sources are enabled

bit 4 **Unimplemented:** Read as '0'

bit 3 REFOMD: Reference Output Clock Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 2 CTMUMD: CTMU Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 1 LVDMD: High/Low-Voltage Detect Module Disable bit

1 = Module is disabled

0 = Module power and clock sources are enabled

bit 0 USBMD: USB On-The-Go Module Disable bit<sup>(1)</sup>

1 = Module is disabled

0 = Module power and clock sources are enabled

Note 1: USB is not present on PIC24FJXXXXGA6XX devices.

### REGISTER 11-5: ANSE: PORTE ANALOG FUNCTION SELECTION REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-1                | U-0   |

|--------|-----|-----|-----|-----|-----|----------------------|-------|

| _      | _   | _   | _   | _   | _   | ANSE9 <sup>(1)</sup> | _     |

| bit 15 |     |     |     |     |     |                      | bit 8 |

| U-0   | U-0 | U-0 | R/W-1 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-------|-----|-----|-----|-------|

| _     | _   | _   | ANSE4 | _   | _   | _   | _     |

| bit 7 |     |     |       |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9 ANSE9: PORTE Analog Function Selection bit<sup>(1)</sup>

1 = Pin is configured in Analog mode; I/O port read is disabled0 = Pin is configured in Digital mode; I/O port read is enabled

bit 8-5 **Unimplemented:** Read as '0'

bit 4 ANSE4: PORTE Analog Function Selection bit

1 = Pin is configured in Analog mode; I/O port read is disabled 0 = Pin is configured in Digital mode; I/O port read is enabled

bit 3-0 **Unimplemented:** Read as '0'

Note 1: ANSE9 is not available on 64-pin devices.

## REGISTER 11-6: ANSG: PORTG ANALOG FUNCTION SELECTION REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-1     | R/W-1 |

|--------|-----|-----|-----|-----|-----|-----------|-------|

| _      | _   | _   | _   | _   | _   | ANSG<9:8> |       |

| bit 15 |     |     |     |     |     |           | bit 8 |

| R/W-1 | R/W-1  | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|--------|-----|-----|-----|-----|-----|-------|

| ANSO  | G<7:6> | _   | _   | _   | _   | _   | _     |

| bit 7 |        |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9-6 ANSG<9:6>: PORTG Analog Function Selection bits

1 = Pin is configured in Analog mode; I/O port read is disabled 0 = Pin is configured in Digital mode; I/O port read is enabled

bit 5-0 **Unimplemented:** Read as '0'

## REGISTER 11-48: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP25R5 | RP25R4 | RP25R3 | RP25R2 | RP25R1 | RP25R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP24R5 | RP24R4 | RP24R3 | RP24R2 | RP24R1 | RP24R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP25R<5:0>: RP25 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP25 (see Table 11-4 for peripheral function numbers).

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP24R<5:0>: RP24 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP24 (see Table 11-4 for peripheral function numbers).

#### REGISTER 11-49: RPOR13: PERIPHERAL PIN SELECT OUTPUT REGISTER 13

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP27R5 | RP27R4 | RP27R3 | RP27R2 | RP27R1 | RP27R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP26R5 | RP26R4 | RP26R3 | RP26R2 | RP26R1 | RP26R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP27R<5:0>: RP27 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP27 (see Table 11-4 for peripheral function numbers).

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP26R<5:0>: RP26 Output Pin Mapping bits

Peripheral Output Number n is assigned to pin, RP26 (see Table 11-4 for peripheral function numbers).

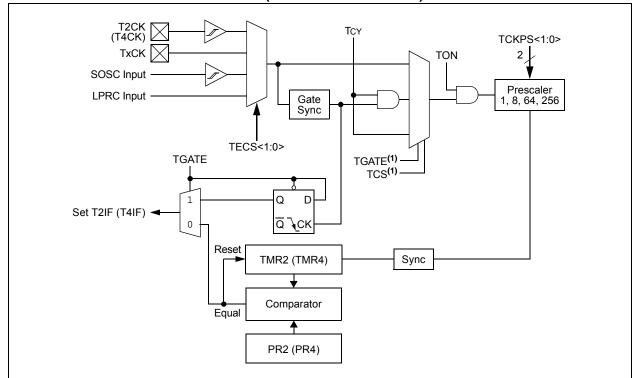

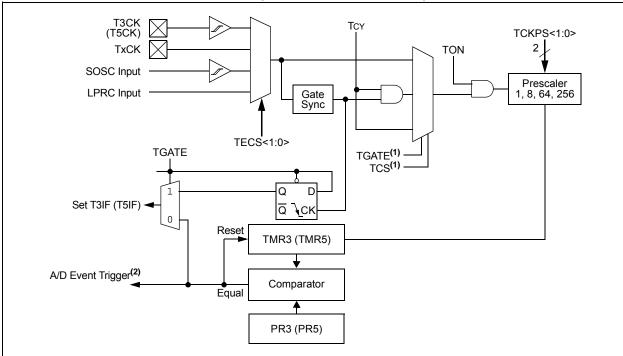

## 13.0 TIMER2/3 AND TIMER4/5

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Timers" (DS39704), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent, 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 can each operate in three modes:

- Two Independent 16-Bit Timers with All 16-Bit Operating modes (except Asynchronous Counter mode)

- · Single 32-Bit Timer

- · Single 32-Bit Synchronous Counter

They also support these features:

- · Timer Gate Operation

- Selectable Prescaler Settings

- · Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- A/D Event Trigger (only on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the A/D Event Trigger. This Trigger is implemented only on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1; T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word; Timer3 and Timer5 are the most significant word of the 32-bit timers.

Note:

For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 or Timer5 interrupt flags.

To configure Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 or T45 bit (T2CON<3> or T4CON<3> = 1).

- Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to an external clock, RPINRx (TyCK) must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

- Load the timer period value. PR3 (or PR5) will contain the most significant word (msw) of the value, while PR2 (or PR4) contains the least significant word (lsw).

- 5. If interrupts are required, set the interrupt enable bit, T3IE or T5IE. Use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. Note that while Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair, TMR<3:2> (or TMR<5:4>). TMR3 (TMR5) always contains the most significant word of the count, while TMR2 (TMR4) contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- Clear the T32 bit corresponding to that timer (T2CON<3> for Timer2 and Timer3 or T4CON<3> for Timer4 and Timer5).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See **Section 11.4 "Peripheral Pin Select (PPS)"** for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON (TxCON<15> = 1) bit.

## FIGURE 13-2: TIMER2 AND TIMER4 (16-BIT SYNCHRONOUS) BLOCK DIAGRAM

Note 1: The timer clock input must be assigned to an available RPn/RPIn pin before use. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

## FIGURE 13-3: TIMER3 AND TIMER5 (16-BIT ASYNCHRONOUS) BLOCK DIAGRAM

- Note 1: The timer clock input must be assigned to an available RPn/RPIn pin before use. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

- 2: The A/D Event Trigger is available only on Timer3.

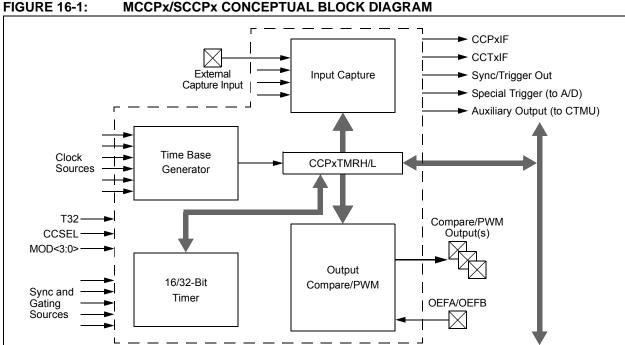

## 16.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the MCCP/SCCP modules, refer to the "dsPIC33/PIC24 Family Reference Manual", "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS33035A), which is available from the Microchip web site (www.microchip.com). The information in sheet supersedes the data information in the FRM.

PIC24FJ1024GA610/GB610 family devices include several Capture/Compare/PWM/Timer base modules, which provide the functionality of three different peripherals of earlier PIC24F devices. The module can operate in one of three major modes:

- · General Purpose Timer

- Input Capture

- Output Compare/PWM

The module is provided in two different forms, distinguished by the number of PWM outputs that the module can generate. Single Capture/Compare/PWM (SCCPs) output modules provide only one PWM output. Multiple Capture/Compare/PWM (MCCPs) output modules can provide up to six outputs and an extended range of power control features, depending on the pin count of the particular device. All other features of the modules are identical.

The SCCPx and MCCPx modules can be operated only in one of the three major modes at any time. The other modes are not available unless the module is reconfigured for the new mode.

A conceptual block diagram for the module is shown in Figure 16-1. All three modules share a time base generator and a common Timer register pair (CCPxTMRH/L); other shared hardware components are added as a particular mode requires.

Each module has a total of 8 control and status registers:

- CCPxCON1L (Register 16-1)

- CCPxCON1H (Register 16-2)

- CCPxCON2L (Register 16-3)

- CCPxCON2H (Register 16-4)

- CCPxCON3L (Register 16-5)

- CCPxCON3H (Register 16-6)

- CCPxSTATL (Register 16-7)

- CCPxSTATH (Register 16-8)

Each module also includes 8 buffer/counter registers that serve as Timer Value registers or data holding buffers:

- · CCPxTMRH/CCPxTMRL (Timer High/Low Counters)

- CCPxPRH/CCPxPRL (Timer Period High/Low)

- CCPxRA (Primary Output Compare Data Buffer)

- · CCPxRB (Secondary Output Compare Data Buffer)

- CCPxBUFH/CCPxBUFL (Input Capture High/Low Buffers)

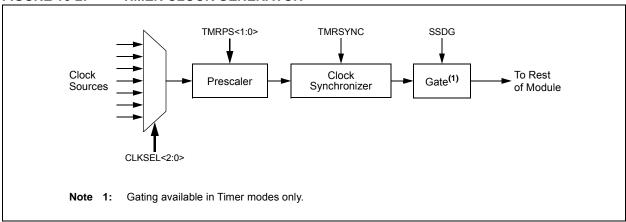

## 16.1 Time Base Generator

The Timer Clock Generator (TCG) generates a clock for the module's internal time base using one of the clock signals already available on the microcontroller. This is used as the time reference for the module in its three major modes. The internal time base is shown in Figure 16-2.

There are eight inputs available to the clock generator, which are selected using the CLKSEL<2:0> bits (CCPxCON1L<10:8>). Available sources include the FRC and LPRC, the Secondary Oscillator and the TCLKI external clock inputs. The system clock is the default source (CLKSEL<2:0> = 000).

## FIGURE 16-2: TIMER CLOCK GENERATOR

#### REGISTER 17-9: SPIXIMSKL: SPIX INTERRUPT MASK REGISTER LOW

| U-0    | U-0 | U-0 | R/W-0    | R/W-0  | U-0 | U-0 | R/W-0    |

|--------|-----|-----|----------|--------|-----|-----|----------|

| _      | _   | _   | FRMERREN | BUSYEN | _   | _   | SPITUREN |

| bit 15 |     |     |          |        |     |     | bit 8    |

| R/W-0  | R/W-0    | R/W-0   | U-0 | R/W-0   | U-0 | R/W-0    | R/W-0    |

|--------|----------|---------|-----|---------|-----|----------|----------|

| SRMTEN | SPIROVEN | SPIRBEN | _   | SPITBEN | _   | SPITBFEN | SPIRBFEN |

| bit 7  |          |         |     |         |     |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 Unimplemented: Read as '0'

bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit

1 = Frame error generates an interrupt event

0 = Frame error does not generate an interrupt event

bit 11 BUSYEN: Enable Interrupt Events via SPIBUSY bit

1 = SPIBUSY generates an interrupt event

0 = SPIBUSY does not generate an interrupt event

bit 10-9 Unimplemented: Read as '0'

bit 8 SPITUREN: Enable Interrupt Events via SPITUR bit

1 = Transmit Underrun (TUR) generates an interrupt event0 = Transmit Underrun does not generate an interrupt event

bit 7 SRMTEN: Enable Interrupt Events via SRMT bit

1 = Shift Register Empty (SRMT) generates interrupt events0 = Shift Register Empty does not generate interrupt events

bit 6 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = SPIx Receive Overflow generates an interrupt event

0 = SPIx Receive Overflow does not generate an interrupt event

bit 5 SPIRBEN: Enable Interrupt Events via SPIRBE bit

1 = SPIx RX Buffer Empty generates an interrupt event

0 = SPIx RX Buffer Empty does not generate an interrupt event

bit 4 Unimplemented: Read as '0'

bit 3 SPITBEN: Enable Interrupt Events via SPITBE bit

1 = SPIx Transmit Buffer Empty generates an interrupt event

0 = SPIx Transmit Buffer Empty does not generate an interrupt event

bit 2 **Unimplemented:** Read as '0'

bit 1 SPITBFEN: Enable Interrupt Events via SPITBF bit

1 = SPIx Transmit Buffer Full generates an interrupt event

0 = SPIx Transmit Buffer Full does not generate an interrupt event

bit 0 SPIRBFEN: Enable Interrupt Events via SPIRBF bit

1 = SPIx Receive Buffer Full generates an interrupt event

0 = SPIx Receive Buffer Full does not generate an interrupt event

# 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note:

This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70000195), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Inter-Integrated Circuit (I<sup>2</sup>C) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, display drivers, A/D Converters, etc.

The I<sup>2</sup>C module supports these features:

- · Independent Master and Slave Logic

- · 7-Bit and 10-Bit Device Addresses

- General Call Address as Defined in the I<sup>2</sup>C Protocol

- Clock Stretching to Provide Delays for the Processor to Respond to a Slave Data Request

- · Both 100 kHz and 400 kHz Bus Specifications

- Configurable Address Masking

- Multi-Master modes to Prevent Loss of Messages in Arbitration

- Bus Repeater mode, Allowing the Acceptance of All Messages as a Slave, Regardless of the Address

- Automatic SCL

A block diagram of the module is shown in Figure 18-1.

# 18.1 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communications protocol for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDAx and SCLx.

- Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the

- Send the serial memory address low byte to the slave

- Repeat Steps 4 and 5 until all data bytes are sent

- Assert a Repeated Start condition on SDAx and SCLx.

- Send the device address byte to the slave with a read indication.

- Wait for and verify an Acknowledge from the slave.

- Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDAx and SCLx.

### REGISTER 20-20: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0  | R/W-0 |

|-------|-----|-------|-------|--------|---------|--------|-------|

| BTSEE | _   | DMAEE | BTOEE | DFN8EE | CRC16EE | CRC5EE | PIDEE |

|       |     |       |       |        |         | EOFEE  |       |

| bit 7 |     |       |       |        |         |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7 BTSEE: Bit Stuff Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 6 Unimplemented: Read as '0'

bit 5 **DMAEE:** DMA Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 1 For Device mode:

CRC5EE: CRC5 Host Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

For Host mode:

EOFEE: End-of-Frame (EOF) Error interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 0 PIDEE: PID Check Failure Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

FIGURE 24-2: CLCx LOGIC FUNCTION COMBINATORIAL OPTIONS

TABLE 30-1: CONFIGURATION WORD ADDRESSES

| Configuration         | Single Partition Mode                                          |                 |                         |                 |  |  |  |  |

|-----------------------|----------------------------------------------------------------|-----------------|-------------------------|-----------------|--|--|--|--|

| Registers             | PIC24FJ1024GX6XX                                               | PIC24FJ512GX6XX | PIC24FJ256GX6XX         | PIC24FJ128GX6XX |  |  |  |  |

| FSEC                  | 0ABF00h                                                        | 055F00h         | 02AF00h                 | 015F00h         |  |  |  |  |

| FBSLIM                | 0ABF10h                                                        | 055F10h         | 02AF10h                 | 015F10h         |  |  |  |  |

| FSIGN                 | 0ABF14h                                                        | 055F14h         | 02AF14h                 | 015F14h         |  |  |  |  |

| FOSCSEL               | 0ABF18h                                                        | 055F18h         | 02AF18h                 | 015F18h         |  |  |  |  |

| FOSC                  | 0ABF1Ch                                                        | 055F1Ch         | 02AF1Ch                 | 015F1Ch         |  |  |  |  |

| FWDT                  | 0ABF20h                                                        | 055F20h         | 02AF20h                 | 015F20h         |  |  |  |  |

| FPOR                  | 0ABF24h                                                        | 055F24h         | 02AF24h                 | 015F24h         |  |  |  |  |

| FICD                  | 0ABF28h                                                        | 055F28h         | 02AF28h                 | 015F28h         |  |  |  |  |

| FDEVOPT1              | 0ABF2Ch                                                        | 055F2Ch         | 02AF2Ch                 | 015F2Ch         |  |  |  |  |

| FBOOT                 | 801800h                                                        |                 |                         |                 |  |  |  |  |

|                       |                                                                | Dual Partiti    | on Modes <sup>(1)</sup> |                 |  |  |  |  |

| FSEC <sup>(2)</sup>   | 055F00h/455F00h                                                | 02AF00h/42AF00h | 015700h/415700h         | 00AF00h/40AF00h |  |  |  |  |

| FBSLIM <sup>(2)</sup> | 055F10h/455F10h                                                | 02AF10h/42AF10h | 015710h/415710h         | 00AF10h/40AF10h |  |  |  |  |

| FSIGN <sup>(2)</sup>  | 055F14h/455F14h                                                | 02AF14h/42AF14h | 015714h/ 415714h        | 00AF14h/40AF14h |  |  |  |  |

| FOSCSEL               | 055F18h/455F18h                                                | 02AF18h/42AF18h | 015718h/415718h         | 00AF18h/40AF18h |  |  |  |  |

| FOSC                  | 055F1Ch/455F1Ch                                                | 02AF1Ch/42AF1Ch | 01571Ch/41571Ch         | 00AF1Ch/40AF1Ch |  |  |  |  |

| FWDT                  | 055F20h/455F20h                                                | 02AF20h/42AF20h | 015720h/415720h         | 00AF20h/40AF20h |  |  |  |  |

| FPOR                  | 055F24h/ 455F24h                                               | 02AF24h/42AF24h | 015724h/415724h         | 00AF24h/40AF24h |  |  |  |  |

| FICD                  | 055F28h/455F28h                                                | 02AF28h/42AF28h | 015728h/415728h         | 00AF28h/40AF28h |  |  |  |  |

| FDEVOPT1              | 055F2Ch/455F2Ch                                                | 02AF2Ch/42AF2Ch | 01572Ch/41572Ch         | 00AF2Ch/40AF2Ch |  |  |  |  |

| FBTSEQ <sup>(3)</sup> | 055FFCh/455FFCh 02AFFCh/42AFFCh 0157FCh/4157FCh 00AFFCh/40AFFC |                 |                         |                 |  |  |  |  |

| FBOOT                 | 801800h                                                        |                 |                         |                 |  |  |  |  |

Note 1: Addresses shown for Dual Partition modes are for the Active/Inactive Partitions, respectively.

**<sup>2:</sup>** Changes to these Inactive Partition Configuration Words affect how the Active Partition accesses the Inactive Partition.

<sup>3:</sup> FBTSEQ is a 24-bit Configuration Word, using all three bytes of the program memory width.

TABLE 32-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                       |

|-----------------|-----------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                   |

| (text)          | Means "content of text"                                                           |

| [text]          | Means "the location addressed by text"                                            |

| { }             | Optional field or operation                                                       |

| <n:m></n:m>     | Register bit field                                                                |

| .b              | Byte mode selection                                                               |

| .d              | Double-Word mode selection                                                        |

| .S              | Shadow register select                                                            |

| .W              | Word mode selection (default)                                                     |

| bit4            | 4-bit Bit Selection field (used in word addressed instructions) ∈ {015}           |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero              |

| Expr            | Absolute address, label or expression (resolved by the linker)                    |

| f               | File register address ∈ {0000h1FFFh}                                              |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                    |

| lit4            | 4-bit unsigned literal ∈ {015}                                                    |

| lit5            | 5-bit unsigned literal ∈ {031}                                                    |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                   |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode            |

| lit14           | 14-bit unsigned literal ∈ {016383}                                                |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                |

| lit23           | 23-bit unsigned literal ∈ {08388607}; LSB must be '0'                             |

| None            | Field does not require an entry, may be blank                                     |

| PC              | Program Counter                                                                   |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                 |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                             |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                    |

| Wb              | Base W register ∈ {W0W15}                                                         |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                 |

| Wdo             | Destination W register ∈ { Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm,Wn           | Dividend, Divisor Working register pair (direct addressing)                       |

| Wn              | One of 16 Working registers ∈ {W0W15}                                             |

| Wnd             | One of 16 destination Working registers ∈ {W0W15}                                 |

| Wns             | One of 16 source Working registers ∈ {W0W15}                                      |

| WREG            | W0 (Working register used in file register instructions)                          |

| Ws              | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                      |

| Wso             | Source W register ∈ { Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }      |

| UxTXREG (UARTx Transmit,              |             |

|---------------------------------------|-------------|

| Normally Write-Only)                  | 263         |

| Resets                                |             |

| BOR (Brown-out Reset)                 | 97          |

| Brown-out Reset (BOR)                 |             |

| Clock Source Selection                |             |

| CM (Configuration Mismatch Reset)     |             |

| Delay Times                           |             |

| Device Times                          |             |

| IOPUWR (Illegal Opcode Reset)         |             |

|                                       |             |

| MCLR (Master Clear Pin Reset)         |             |

| POR (Power-on Reset)                  |             |

| RCON Flags, Operation                 |             |

| SFR States                            |             |

| SWR (RESET Instruction)               |             |

| TRAPR (Trap Conflict Reset)           |             |

| UWR (Uninitialized W Register Reset)  | 97          |

| WDT (Watchdog Timer Reset)            | 97          |

| Revision History                      |             |

| RTCC                                  |             |

| Alarm Configuration                   | 328         |

| Alarm Mask Settings (figure)          |             |

| Alarm Value Registers                 |             |

| Calibration                           |             |

|                                       |             |

| Clock Source Selection                |             |

| Control Registers                     |             |

| Event Timestamping                    |             |

| Power Control                         |             |

| Register Mapping                      |             |

| RTCVAL Register Mappings              |             |

| Source Clock                          | 311         |

| Timestamp Registers                   | 324         |

| Value Registers                       | 320         |

| Write Lock                            |             |

| _                                     |             |

| S                                     |             |

| Secondary Oscillator Operation        | 132         |

| Serial Peripheral Interface (SPI)     |             |

| Serial Peripheral Interface. See SPI. |             |

| Software Simulator (MPLAB SIM)        | <i>4</i> ∩0 |

| Software Stack                        |             |

| Special Features                      |             |

| •                                     |             |

| Special Features of the CPU           | 389         |

| SPI                                   | 202         |

| Audio Mode Operation                  |             |

| Control Registers                     |             |

| Master Mode Operation                 |             |

| Slave Mode Operation                  | 228         |

| т                                     |             |

| •                                     |             |

| Timer1                                |             |

| Timer2/3 and Timer4/5                 | 187         |

| Timing Diagrams                       |             |

| CLKO and I/O Characteristics          | 434         |

| DNL vs. Code (10-Bit Mode)            |             |

| DNL vs. Code (12-Bit Mode)            |             |

| External Clock                        |             |

| INL vs. Code (10-Bit Mode)            |             |

| INL vs. Code (12-Bit Mode)            |             |

|                                       |             |

| Triple Comparator Module              |             |

| Triple Comparator Module              | 309         |

| U                                                    |     |

|------------------------------------------------------|-----|

| UART                                                 |     |

| Baud Rate Generator (BRG)                            | 257 |

| Infrared Support                                     | 258 |

| Operation of UxCTS and UxRTS Pins                    | 258 |

| Receiving                                            |     |

| 8-Bit or 9-Bit Data Mode                             | 258 |

| Transmitting                                         |     |

| 8-Bit Data Mode                                      | 258 |

| 9-Bit Data Mode                                      | 258 |

| Break and Sync Sequence                              |     |

| Unique Device Identifier (UDID)                      |     |

| Addresses                                            | 402 |

| Universal Asynchronous Receiver Transmitter. See UAF |     |

| Universal Serial Bus. See USB OTG.                   |     |

| USB OTG                                              | 265 |

| Buffer Descriptors                                   |     |

| Assignment in Different Buffering Modes              | 271 |

| Buffer Descriptors and BDT                           | 270 |

| Control Registers                                    | 279 |

| Device Mode Operation                                | 275 |

| DMA Interface                                        | 271 |

| Hardware                                             |     |

| Calculating                                          |     |

| Transceiver Power Requirements                       | 269 |

| Hardware Configuration                               | 267 |

| Device Mode                                          | 267 |

| Host and OTG Modes                                   | 268 |

| Host Mode Operation                                  |     |

| Interrupts                                           |     |

| Interrupts and USB Transactions                      |     |

| Operation                                            |     |

| HNP                                                  | 279 |

| SRP                                                  | 278 |

| W                                                    |     |

| Watchdog Timer (WDT)                                 | 404 |

| Control Register                                     |     |

| Windowed Operation                                   |     |

| WWW Address                                          |     |

| WWW, On-Line Support                                 |     |

## Worldwide Sales and Service

#### **AMERICAS**

Corporate Office

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7277 Technical Support: http://www.microchip.com/

support

Web Address: www.microchip.com

Atlanta

Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY

Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115

Fax: 86-571-8792-8116

China - Hong Kong SAR

Tel: 852-2943-5100

Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300

Fax: 86-27-5980-5118 China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040

Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160

Fax: 81-6-6152-9310 **Japan - Tokyo** Tel: 81-3-6880- 3770

Fax: 81-3-6880-3771 **Korea - Daegu**

Tel: 82-53-744-4301 Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857

Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

**Philippines - Manila** Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366

Fax: 886-3-5770-955 **Taiwan - Kaohsiung**

Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

## **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828

Fax: 45-4485-2829 Finland - Espoo

Tel: 358-9-4520-820 France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

France - Saint Cloud Tel: 33-1-30-60-70-00

**Germany - Garching** Tel: 49-8931-9700 **Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn

Tel: 49-7131-67-3636 **Germany - Karlsruhe**

Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

**Israel - Ra'anana** Tel: 972-9-744-7705

ltaly - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820