Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj512gb606-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

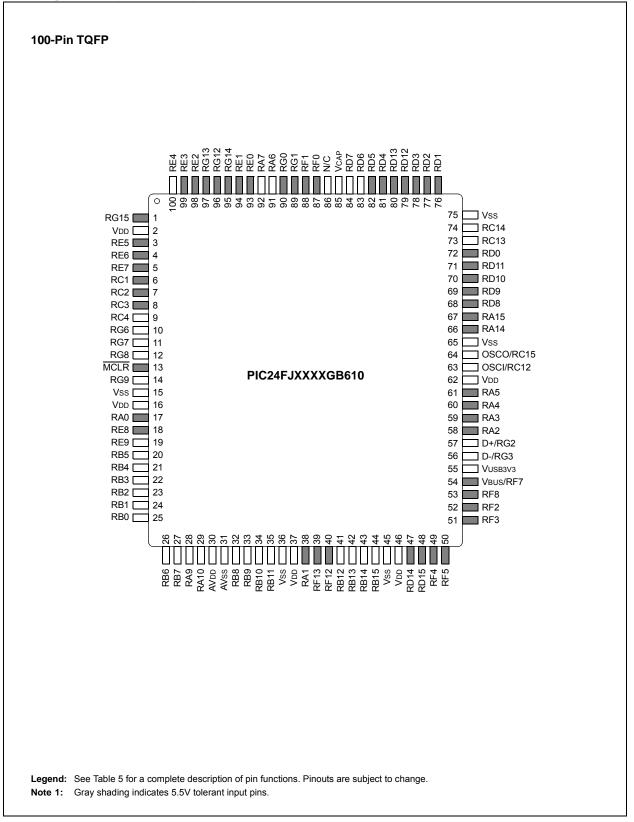

### Pin Diagrams<sup>(1)</sup> (Continued)

|                 |                                     | Pin N                            | Number/Grid Locator              |                                  |                         |                         |     |                 |                    |  |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|--------------------|--|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA |     | Input<br>Buffer | Description        |  |

| RF0             | 58                                  | 58                               | 87                               | 87                               | B6                      | B6                      | I/O | DIG/ST          | PORTF Digital I/Os |  |

| RF1             | 59                                  | 59                               | 88                               | 88                               | A6                      | A6                      | I/O | DIG/ST          |                    |  |

| RF2             | 34                                  | _                                | 52                               | 52                               | K11                     | K11                     | I/O | DIG/ST          |                    |  |

| RF3             | 33                                  | 33                               | 51                               | 51                               | K10                     | K10                     | I/O | DIG/ST          |                    |  |

| RF4             | 31                                  | 31                               | 49                               | 49                               | L10                     | L10                     | I/O | DIG/ST          |                    |  |

| RF5             | 32                                  | 32                               | 50                               | 50                               | L11                     | L11                     | I/O | DIG/ST          |                    |  |

| RF6             | 35                                  | _                                | 55                               | _                                | H9                      |                         | I/O | DIG/ST          |                    |  |

| RF7             | —                                   | 34                               | 54                               | 54                               | H8                      | H8                      | I/O | DIG/ST          |                    |  |

| RF8             | _                                   | _                                | 53                               | 53                               | J10                     | J10                     | I/O | DIG/ST          |                    |  |

| RF12            | _                                   | _                                | 40                               | 40                               | K6                      | K6                      | I/O | DIG/ST          |                    |  |

| RF13            | _                                   | —                                | 39                               | 39                               | L6                      | L6                      | I/O | DIG/ST          |                    |  |

| RG0             | _                                   | _                                | 90                               | 90                               | A5                      | A5                      | I/O | DIG/ST          | PORTG Digital I/Os |  |

| RG1             | _                                   | _                                | 89                               | 89                               | E6                      | E6                      | I/O | DIG/ST          |                    |  |

| RG2             | 37                                  | 37                               | 57                               | 57                               | H10                     | H10                     | I/O | DIG/ST          |                    |  |

| RG3             | 36                                  | 36                               | 56                               | 56                               | J11                     | J11                     | I/O | DIG/ST          |                    |  |

| RG6             | 4                                   | 4                                | 10                               | 10                               | E3                      | E3                      | I/O | DIG/ST          |                    |  |

| RG7             | 5                                   | 5                                | 11                               | 11                               | F4                      | F4                      | I/O | DIG/ST          |                    |  |

| RG8             | 6                                   | 6                                | 12                               | 12                               | F2                      | F2                      | I/O | DIG/ST          |                    |  |

| RG9             | 8                                   | 8                                | 14                               | 14                               | F3                      | F3                      | I/O | DIG/ST          |                    |  |

| RG12            | —                                   | _                                | 96                               | 96                               | C3                      | C3                      | I/O | DIG/ST          |                    |  |

| RG13            | —                                   | _                                | 97                               | 97                               | A3                      | A3                      | I/O | DIG/ST          |                    |  |

| RG14            | —                                   | —                                | 95                               | 95                               | C4                      | C4                      | I/O | DIG/ST          |                    |  |

| RG15            | —                                   | _                                | 1                                | 1                                | B2                      | B2                      | I/O | DIG/ST          |                    |  |

TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

**Legend:** TTL = TTL input buffer

ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

|                  |                                     | Pin N                            | umber/Gri                        |                                  |                         |                         |     |                  |                                               |  |

|------------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|------------------|-----------------------------------------------|--|

| Pin<br>Function  | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer  | Description                                   |  |

| RPI32            | —                                   | —                                | 40                               | 40                               | K6                      | K6                      | Ι   | DIG/ST           | Remappable Peripherals                        |  |

| RPI33            | —                                   | —                                | 18                               | 18                               | G1                      | G1                      | I   | DIG/ST           | (input only)                                  |  |

| RPI34            | —                                   | _                                | 19                               | 19                               | G2                      | G2                      | Т   | DIG/ST           |                                               |  |

| RPI35            | —                                   | _                                | 67                               | 67                               | E8                      | E8                      | Т   | DIG/ST           |                                               |  |

| RPI36            | —                                   | _                                | 66                               | 66                               | E11                     | E11                     | Ι   | DIG/ST           |                                               |  |

| RPI37            | 48                                  | 48                               | 74                               | 74                               | B11                     | B11                     | I   | DIG/ST           |                                               |  |

| RPI38            | —                                   | —                                | 6                                | 6                                | D1                      | D1                      | I   | DIG/ST           |                                               |  |

| RPI39            | _                                   | _                                | 7                                | 7                                | E4                      | E4                      | Ι   | DIG/ST           |                                               |  |

| RPI40            | _                                   | —                                | 8                                | 8                                | E2                      | E2                      | Ι   | DIG/ST           |                                               |  |

| RPI41            | _                                   | —                                | 9                                | 9                                | E1                      | E1                      | Ι   | DIG/ST           |                                               |  |

| RPI42            | _                                   | _                                | 79                               | 79                               | A9                      | A9                      | Ι   | DIG/ST           |                                               |  |

| RPI43            | _                                   | _                                | 47                               | 47                               | L9                      | L9                      | I   | DIG/ST           |                                               |  |

| SCL1             | 37                                  | 44                               | 57                               | 66                               | H10                     | E11                     | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock<br>Input/Output |  |

| SCL2             | 32                                  | 32                               | 58                               | 58                               | H11                     | H11                     | I/O | I <sup>2</sup> C | I2C2 Synchronous Serial Clock<br>Input/Output |  |

| SCL3             | 2                                   | 2                                | 4                                | 4                                | C1                      | C1                      | I/O | I <sup>2</sup> C | I2C3 Synchronous Serial Clock<br>Input/Output |  |

| SDA1             | 36                                  | 43                               | 56                               | 67                               | J11                     | E8                      | I/O | I <sup>2</sup> C | I2C1 Data Input/Output                        |  |

| SDA2             | 31                                  | 31                               | 59                               | 59                               | G10                     | G10                     | I/O | I <sup>2</sup> C | I2C2 Data Input/Output                        |  |

| SDA3             | 3                                   | 3                                | 5                                | 5                                | D2                      | D2                      | I/O | I <sup>2</sup> C | I2C3 Data Input/Output                        |  |

| SOSCI            | 47                                  | 47                               | 73                               | 73                               | C10                     | C10                     | I   | ANA/<br>ST       | Secondary Oscillator/Timer1<br>Clock Input    |  |

| SOSCO            | 48                                  | 48                               | 74                               | 74                               | B11                     | B11                     | 0   | ANA              | Secondary Oscillator/Timer1<br>Clock Output   |  |

| T1CK             | 22                                  | 22                               | 33                               | 33                               | L4                      | L4                      | Ι   | ST               | Timer1 Clock                                  |  |

| ТСК              | 27                                  | 27                               | 38                               | 38                               | J6                      | J6                      | I   | ST               | JTAG Test Clock/Programming<br>Clock Input    |  |

| TDI              | 28                                  | 28                               | 60                               | 60                               | G11                     | G11                     | I   | ST               | JTAG Test Data/Programming<br>Data Input      |  |

| TDO              | 24                                  | 24                               | 61                               | 61                               | G9                      | G9                      | 0   | DIG              | JTAG Test Data Output                         |  |

| TMPR             | 22                                  | 22                               | 33                               | 33                               | L4                      | L4                      | I   | ST               | Tamper Detect Input                           |  |

| TMS              | 23                                  | 23                               | 17                               | 17                               | G3                      | G3                      | I   | ST               | JTAG Test Mode Select Input                   |  |

| U5CTS            | 58                                  | 58                               | 87                               | 87                               | B6                      | B6                      | I   | ST               | UART5 CTS Output                              |  |

| U5RTS/<br>U5BCLK | 55                                  | 55                               | 84                               | 84                               | C7                      | C7                      | 0   | DIG              | UART5 RTS Input                               |  |

| U5RX             | 54                                  | 54                               | 83                               | 83                               | D7                      | D7                      | I   | ST               | UART5 Receive Input                           |  |

| U5TX             | 49                                  | 49                               | 76                               | 76                               | A11                     | A11                     | 0   | DIG              | UART5 Transmit Output                         |  |

| U6CTS            | 46                                  | 46                               | 72                               | 72                               | D9                      | D9                      | I   | ST               | UART6 CTS Output                              |  |

| U6RTS/<br>U6BCLK | 42                                  | 42                               | 68                               | 68                               | E9                      | E9                      | 0   | DIG              | UART6 RTS Input                               |  |

#### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL =

TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

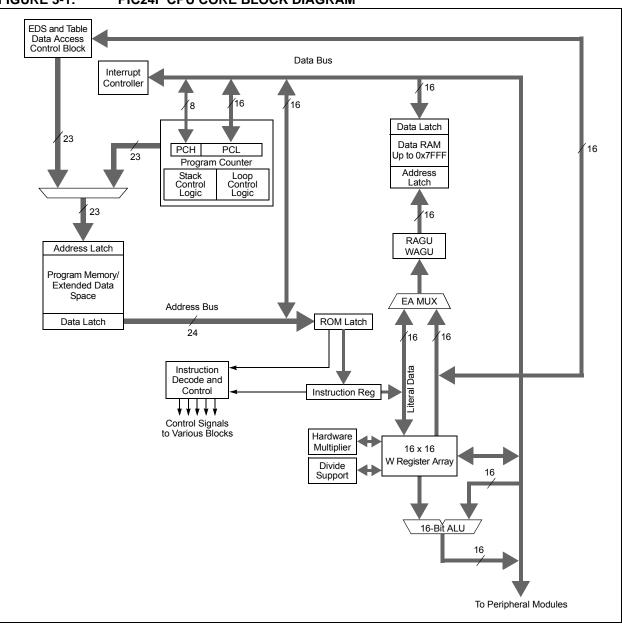

#### FIGURE 3-1: PIC24F CPU CORE BLOCK DIAGRAM

| TABLE 3-1: CI | PU CORE REGISTERS |

|---------------|-------------------|

|---------------|-------------------|

| Register(s) Name | Description                        |  |

|------------------|------------------------------------|--|

| W0 through W15   | Working Register Array             |  |

| PC               | 23-Bit Program Counter             |  |

| SR               | ALU STATUS Register                |  |

| SPLIM            | Stack Pointer Limit Value Register |  |

| TBLPAG           | Table Memory Page Address Register |  |

| RCOUNT           | REPEAT Loop Counter Register       |  |

| CORCON           | CPU Control Register               |  |

| DISICNT          | Disable Interrupt Count Register   |  |

| DSRPAG           | Data Space Read Page Register      |  |

| DSWPAG           | Data Space Write Page Register     |  |

## PIC24FJ1024GA610/GB610 FAMILY

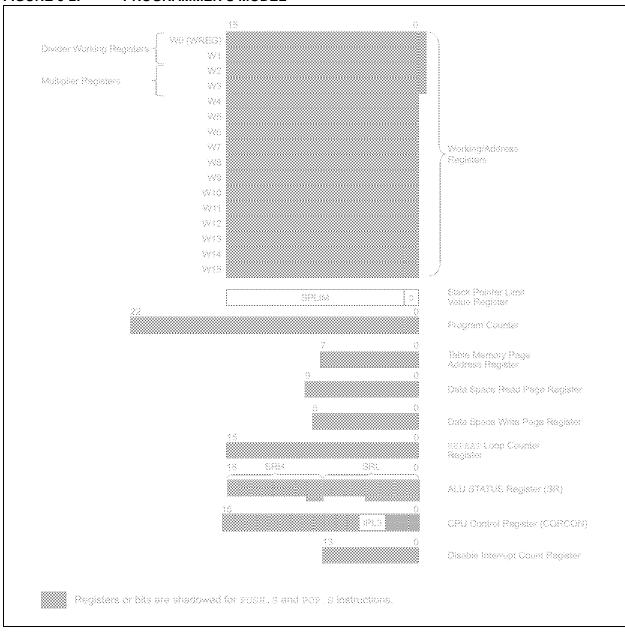

#### FIGURE 3-2: PROGRAMMER'S MODEL

| File Name      | Address          | All Resets | File Name                                 | Address | All Resets |  |  |  |

|----------------|------------------|------------|-------------------------------------------|---------|------------|--|--|--|

| SPI (CONTINUED | ))               |            | CONFIGURABLE LOGIC CELL (CLC) (CONTINUED) |         |            |  |  |  |

| SPI1BUFL       | 0400             | 0000       | CLC3CONL                                  | 047C    | 0000       |  |  |  |

| SPI1BUFH       | 0402             | 0000       | CLC3CONH                                  | 047E    | 0000       |  |  |  |

| SPI1BRGL       | 0404             | xxxx       | CLC3SELL                                  | 0480    | 0000       |  |  |  |

| SPI1IMSK1      | 0408             | 0000       | CLC3GLSL                                  | 0484    | 0000       |  |  |  |

| SPI1IMSK2      | 040A             | 0000       | CLC3GLSH                                  | 0486    | 0000       |  |  |  |

| SPI1URDTL      | 040C             | 0000       | CLC4CONL                                  | 0488    | 0000       |  |  |  |

| SPI1URDTH      | 040E             | 0000       | CLC4CONH                                  | 048A    | 0000       |  |  |  |

| SPI2CON1       | 0410             | 0x00       | CLC4SELL                                  | 048C    | 0000       |  |  |  |

| SPI2CON2       | 0412             | 0000       | CLC4GLSL                                  | 0490    | 0000       |  |  |  |

| SPI2CON3       | 0414             | 0000       | CLC4GLSH                                  | 0492    | 0000       |  |  |  |

| SPI2STATL      | 0418             | 0028       | l <sup>2</sup> C                          |         |            |  |  |  |

| SPI2STATH      | 041A             | 0000       | I2C1RCV                                   | 0494    | 0000       |  |  |  |

| SPI2BUFL       | 041C             | 0000       | I2C1TRN                                   | 0496    | 00FF       |  |  |  |

| SPI2BUFH       | 041E             | 0000       | I2C1BRG                                   | 0498    | 0000       |  |  |  |

| SPI2BRGL       | 0420             | xxxx       | I2C1CON1                                  | 049A    | 1000       |  |  |  |

| SPI2IMSK1      | 0424             | 0000       | I2C1CON2                                  | 049C    | 0000       |  |  |  |

| SPI2IMSK2      | 0426             | 0000       | I2C1STAT                                  | 049E    | 0000       |  |  |  |

| SPI2URDTL      | 0428             | 0000       | I2C1ADD                                   | 04A0    | 0000       |  |  |  |

| SPI2URDTH      | 042A             | 0000       | I2C1MSK                                   | 04A2    | 0000       |  |  |  |

| SPI3CON1       | 042C             | 0x00       | I2C2RCV                                   | 04A4    | 0000       |  |  |  |

| SPI3CON2       | 042E             | 0000       | I2C2TRN                                   | 04A6    | 00FF       |  |  |  |

| SPI3CON3       | 0430             | 0000       | I2C2BRG                                   | 04A8    | 0000       |  |  |  |

| SPI3STATL      | 0434             | 0028       | I2C2CON1                                  | 04AA    | 1000       |  |  |  |

| SPI3STATH      | 0436             | 0000       | I2C2CON2                                  | 04AC    | 0000       |  |  |  |

| SPI3BUFL       | 0438             | 0000       | I2C2STAT                                  | 04AE    | 0000       |  |  |  |

| SPI3BUFH       | 043A             | 0000       | I2C2ADD                                   | 04B0    | 0000       |  |  |  |

| SPI3BRGL       | 043C             | xxxx       | I2C2MSK                                   | 04B2    | 0000       |  |  |  |

| SPI3IMSK1      | 0440             | 0000       | I2C3RCV                                   | 04B4    | 0000       |  |  |  |

| SPI3IMSK2      | 0442             | 0000       | I2C3TRN                                   | 04B6    | 00FF       |  |  |  |

| SPI3URDTL      | 0444             | 0000       | I2C3BRG                                   | 04B8    | 0000       |  |  |  |

| SPI3URDTH      | 0446             | 0000       | I2C3CON1                                  | 04BA    | 1000       |  |  |  |

| CONFIGURABLE   | LOGIC CELL (CLC) |            | I2C3CON2                                  | 04BC    | 0000       |  |  |  |

| CLC1CONL       | 0464             | 0000       | I2C3STAT                                  | 04BE    | 0000       |  |  |  |

| CLC1CONH       | 0466             | 0000       | I2C3ADD                                   | 04C0    | 0000       |  |  |  |

| CLC1SELL       | 0468             | 0000       | I2C3MSK                                   | 04C2    | 0000       |  |  |  |

| CLC1GLSL       | 046C             | 0000       | DMA                                       |         |            |  |  |  |

| CLC1GLSH       | 046E             | 0000       | DMACON                                    | 04C4    | 0000       |  |  |  |

| CLC2CONL       | 0470             | 0000       | DMABUF                                    | 04C6    | 0000       |  |  |  |

| CLC2CONH       | 0472             | 0000       | DMAL                                      | 04C8    | 0000       |  |  |  |

| CLC2SELL       | 0474             | 0000       | DMAH                                      | 04CA    | 0000       |  |  |  |

| CLC2GLSL       | 0478             | 0000       | DMACH0                                    | 04CC    | 0000       |  |  |  |

| CLC2GLSH       | 047A             | 0000       | DMAINT0                                   | 04CE    | 0000       |  |  |  |

#### TABLE 4-8: SFR MAP: 0400h BLOCK

**Legend:** — = unimplemented, read as '0'; x = undefined. Reset values are shown in hexadecimal.

#### 5.1.6 CHANNEL PRIORITY

Each DMA channel functions independently of the others, but also competes with the others for access to the data and DMA buses. When access collisions occur, the DMA Controller arbitrates between the channels using a user-selectable priority scheme. Two schemes are available:

- Round-Robin: When two or more channels collide, the lower numbered channel receives priority on the first collision. On subsequent collisions, the higher numbered channels each receive priority, based on their channel number.

- Fixed: When two or more channels collide, the lowest numbered channel always receives priority, regardless of past history; however, any channel being actively processed is not available for an immediate retrigger. If a higher priority channel is continually requesting service, it will be scheduled for service after the next lower priority channel with a pending request.

#### 5.2 Typical Setup

To set up a DMA channel for a basic data transfer:

- Enable the DMA Controller (DMAEN = 1) and select an appropriate channel priority scheme by setting or clearing PRSSEL.

- 2. Program DMAH and DMAL with the appropriate upper and lower address boundaries for data RAM operations.

- 3. Select the DMA channel to be used and disable its operation (CHEN = 0).

- Program the appropriate source and destination addresses for the transaction into the channel's DMASRCn and DMADSTn registers. For PIA mode addressing, use the base address value.

- 5. Program the DMACNTn register for the number of Triggers per transfer (One-Shot or Continuous modes) or the number of words (bytes) to be transferred (Repeated modes).

- 6. Set or clear the SIZE bit to select the data size.

- 7. Program the TRMODE<1:0> bits to select the Data Transfer mode.

- 8. Program the SAMODE<1:0> and DAMODE<1:0> bits to select the addressing mode.

- 9. Enable the DMA channel by setting CHEN.

- 10. Enable the Trigger source interrupt.

#### 5.3 Peripheral Module Disable

Unlike other peripheral modules, the channels of the DMA Controller cannot be individually powered down using the Peripheral Module Disable (PMD) registers. Instead, the channels are controlled as two groups. The DMA0MD bit (PMD7<4>) selectively controls DMACH0 through DMACH3. The DMA1MD bit (PMD7<5>) controls DMACH4 through DMACH7. Setting both bits effectively disables the DMA Controller.

#### 5.4 Registers

The DMA Controller uses a number of registers to control its operation. The number of registers depends on the number of channels implemented for a particular device.

There are always four module-level registers (one control and three buffer/address):

- DMACON: DMA Engine Control Register (Register 5-1)

- DMAH and DMAL: DMA High and Low Address Limit Registers

- DMABUF: DMA Data Buffer

Each of the DMA channels implements five registers (two control and three buffer/address):

- DMACHn: DMA Channel n Control Register (Register 5-2)

- DMAINTn: DMA Channel n Interrupt Register (Register 5-3)

- DMASRCn: DMA Data Source Address Pointer for Channel n

- DMADSTn: DMA Data Destination Source for Channel n

- DMACNTn: DMA Transaction Counter for Channel n

For PIC24FJ1024GA610/GB610 family devices, there are a total of 44 registers.

#### 6.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 128 instructions or 384 bytes. RTSP allows the user to erase blocks of eight rows (1024 instructions) at a time and to program one row at a time. It is also possible to program two instruction word blocks.

The 8-row erase blocks and single row write blocks are edge-aligned, from the beginning of program memory, on boundaries of 3072 bytes and 384 bytes, respectively.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using Table Writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 128 TBLWT instructions are required to write the full row of memory.

To ensure that no data is corrupted during a write, any unused address should be programmed with FFFFFFh. This is because the holding latches reset to an unknown state, so if the addresses are left in the Reset state, they may overwrite the locations on rows which were not rewritten.

The basic sequence for RTSP programming is to set the Table Pointer to point to the programming latches, do a series of TBLWT instructions to load the buffers and set the NVMADRU/NVMADR registers to point to the destination. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing is *not* recommended.

All of the Table Write operations are single-word writes (2 instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

#### 6.3 JTAG Operation

The PIC24F family supports JTAG boundary scan. Boundary scan can improve the manufacturing process by verifying pin to PCB connectivity.

#### 6.4 Enhanced In-Circuit Serial Programming

Enhanced In-Circuit Serial Programming uses an onboard bootloader, known as the Program Executive (PE), to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

#### 6.5 Control Registers

There are four SFRs used to read and write the program Flash memory: NVMCON, NVMADRU, NVMADR and NVMKEY.

The NVMCON register (Register 6-1) controls which blocks are to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 6.6 "Programming Operations"** for further details.

The NVMADRU/NVMADR registers contain the upper byte and lower word of the destination of the NVM write or erase operation. Some operations (chip erase, Inactive Partition erase) operate on fixed locations and do not require an address value.

#### 6.6 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

In Dual Partition mode, programming or erasing the Inactive Partition will not stall the processor; the code in the Active Partition will still execute during the programming operation.

It is important to mask interrupts for a minimum of 5 instruction cycles during Flash programming. This can be done in Assembly using the DISI instruction (see Example 6-1).

#### 7.1 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSC<2:0> bits in the FOSCSEL Flash Configuration Word (see Table 7-2). The NVMCON register is only affected by a POR.

#### 7.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 7-3. Note that the Master Reset Signal, SYSRST, is released after the POR delay time expires.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The Fail-Safe Clock Monitor (FSCM) delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

#### 7.3 Brown-out Reset (BOR)

PIC24FJ1024GA610/GB610 family devices implement a BOR circuit that provides the user with several configuration and power-saving options. The BOR is controlled by the BOREN<1:0> (FPOR<1:0>) Configuration bits.

When BOR is enabled, any drop of VDD below the BOR threshold results in a device BOR. Threshold levels are described in **Section 33.1 "DC Characteristics"**.

#### 7.4 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 7-2. If clock switching is disabled, the system clock source is always selected according to the Oscillator Configuration bits. For more information, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Oscillator**" (DS39700).

# TABLE 7-2:OSCILLATOR SELECTION vs.TYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant                  |  |  |  |  |

|------------|-------------------------------------------|--|--|--|--|

| POR        | FNOSC<2:0> Configuration bits             |  |  |  |  |

| BOR        | (FOSCSEL<2:0>)                            |  |  |  |  |

| MCLR       |                                           |  |  |  |  |

| WDTO       | COSC<2:0> Control bits<br>(OSCCON<14:12>) |  |  |  |  |

| SWR        | (030001(14.122))                          |  |  |  |  |

#### REGISTER 9-5: DCOCON: DIGITALLY CONTROLLED OSCILLATOR ENABLE REGISTER

| U-0                                | U-0                                                                                                                                                                                               | R/W-0                       | U-0             | R/W-0             | R/W-1            | R/W-1           | R/W-1    |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|-------------------|------------------|-----------------|----------|

|                                    |                                                                                                                                                                                                   | DCOEN                       |                 | DCOFSEL3          | DCOFSEL2         | DCOFSEL1        | DCOFSEL0 |

| bit 15                             |                                                                                                                                                                                                   |                             |                 |                   |                  |                 | bit 8    |

|                                    |                                                                                                                                                                                                   |                             |                 |                   |                  |                 |          |

| U-0                                | U-0                                                                                                                                                                                               | U-0                         | U-0             | U-0               | U-0              | U-0             | U-0      |

| —                                  | —                                                                                                                                                                                                 | —                           | —               | —                 | —                | —               | —        |

| bit 7                              |                                                                                                                                                                                                   |                             |                 |                   |                  |                 | bit C    |

| Legend:                            |                                                                                                                                                                                                   |                             |                 |                   |                  |                 |          |

| R = Readab                         | le bit                                                                                                                                                                                            | W = Writable b              | it              | U = Unimplem      | nented bit, read | l as '0'        |          |

| -n = Value at POR '1' = Bit is set |                                                                                                                                                                                                   |                             |                 | '0' = Bit is clea | ared             | x = Bit is unkn | own      |

| bit 12<br>bit 11-8                 | DCOFSEL<3<br>0000 = 1 MH<br>0001 = 2 MH<br>0010 = 3 MH<br>0011 = 4 MH<br>0100 = 5 MH<br>0101 = 6 MH<br>0110 = 7 MH<br>0111 = 8 MH<br>1000 = Reset<br>1001 = Reset<br>1010 = Reset<br>1011 = Reset | z<br>z<br>z<br>z            | e oscillator se |                   |                  |                 |          |

|                                    | 1101 = Rese<br>1110 = 15 M<br>1111 = 30 M                                                                                                                                                         | ∿ed; do not use<br>Hz<br>Hz |                 |                   |                  |                 |          |

| bit 7-0                            | Unimplemen                                                                                                                                                                                        | ted: Read as '0             | ,               |                   |                  |                 |          |

|                                    |                                                                                                                                                                                                   |                             |                 |                   |                  |                 |          |

NOTES:

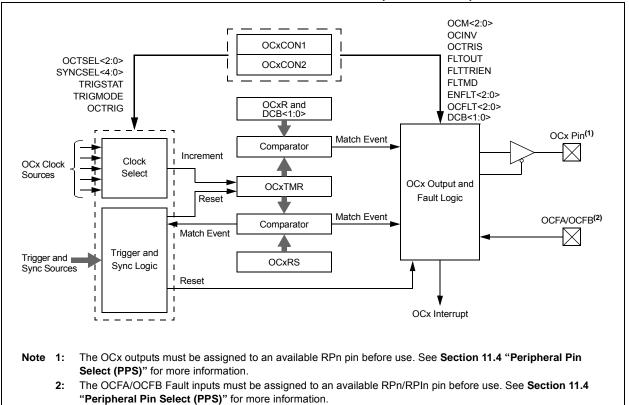

#### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

15.2 Compare Operations

In Compare mode (Figure 15-1), the output compare module can be configured for Single-Shot or Continuous mode pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins if available on the OCx module you are using. Otherwise, configure the dedicated OCx output pins.

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate the time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse based on the desired pulse width and the time to the rising edge of the pulse.

- 3. Write the rising edge value to OCxR and the falling edge value to OCxRS.

- 4. Set the Timer Period register, PRy, to a value equal to or greater than the value in OCxRS.

- 5. Set the OCM<2:0> bits for the appropriate compare operation (= 0xx).

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure Trigger operation and TRIGSTAT to select a hardware or software Trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the Trigger or Sync source. If free-running timer operation is required, set the SYNCSELx bits to '00000' (no Sync/Trigger source).

- Select the time base source with the OCTSEL<2:0> bits. If necessary, set the TON bit for the selected timer, which enables the compare time base to count. Synchronous mode operation starts as soon as the time base is enabled; Trigger mode operation starts after a Trigger source event occurs.

| R/W-0         | U-0                                                                                      | R/W-0, HC                             | R/W-1                             | R/W-0                              | R/W-0             | R/W-0            | R/W-0           |

|---------------|------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------|------------------------------------|-------------------|------------------|-----------------|

| I2CEN         |                                                                                          | I2CSIDL                               | SCLREL <sup>(1)</sup>             | STRICT                             | A10M              | DISSLW           | SMEN            |

| bit 15        |                                                                                          |                                       |                                   |                                    |                   |                  | bit 8           |

|               |                                                                                          | DAMA                                  |                                   |                                    |                   |                  |                 |

| R/W-0         |                                                                                          | R/W-0                                 | R/W-0, HC                         | R/W-0, HC                          | R/W-0, HC         | R/W-0, HC        | R/W-0, HC       |

| GCEN<br>bit 7 | STREN                                                                                    | ACKDT                                 | ACKEN                             | RCEN                               | PEN               | RSEN             | SEN             |

|               |                                                                                          |                                       |                                   |                                    |                   |                  | bit 0           |

| Legend:       |                                                                                          | HC = Hardwa                           | re Clearable bi                   | t                                  |                   |                  |                 |

| R = Read      | able bit                                                                                 | W = Writable                          | bit                               | U = Unimplen                       | nented bit, read  | l as '0'         |                 |

| -n = Value    | e at POR                                                                                 | '1' = Bit is set                      |                                   | '0' = Bit is clea                  | ared              | x = Bit is unkn  | own             |

|               |                                                                                          |                                       |                                   |                                    |                   |                  |                 |

| bit 15        | 12CEN: 12Cx                                                                              | Enable bit (writ                      | able from softw                   | are only)                          |                   |                  |                 |

|               |                                                                                          | he I2Cx module                        |                                   |                                    |                   |                  | S               |

| L:L 4 4       |                                                                                          | the I2Cx modul                        | •                                 | are controlled b                   | by port functions | 6                |                 |

| bit 14        | -                                                                                        | ited: Read as '                       |                                   |                                    |                   |                  |                 |

| bit 13        |                                                                                          | x Stop in Idle M                      |                                   | ovico ontore Id                    | lo modo           |                  |                 |

|               |                                                                                          | s module opera                        |                                   |                                    | ie mode           |                  |                 |

| bit 12        |                                                                                          | Lx Release Co                         |                                   |                                    | )(1)              |                  |                 |

|               | Module reset                                                                             | s and (I2CEN =                        | 0) sets SCLRI                     | EL = 1.                            | ,                 |                  |                 |

|               | If STREN = 0                                                                             | _                                     |                                   |                                    |                   |                  |                 |

|               | 1 = Releases                                                                             |                                       | stratab)                          |                                    |                   |                  |                 |

|               | If STREN = 1                                                                             | ock low (clock s                      | sireich)                          |                                    |                   |                  |                 |

|               | 1 = Releases                                                                             |                                       |                                   |                                    |                   |                  |                 |

|               | 0 = Holds clo                                                                            | ck low (clock st                      | retch); user ma                   | y program this                     | bit to '0', clock | stretch at next  | SCLx low        |

| bit 11        |                                                                                          | x Strict Reserve                      |                                   |                                    |                   |                  |                 |

|               |                                                                                          | erved addressi<br>Mode: The dev       |                                   |                                    |                   |                  | esos fallina ir |

|               |                                                                                          | gory are NACK                         |                                   |                                    | veu audress sp    |                  | sses iailing ii |

|               | In Maste                                                                                 | r Mode: The de                        | vice is allowed                   |                                    | dresses with re   | eserved addres   | s space.        |

|               |                                                                                          | d addressing w                        |                                   |                                    | falling in the re |                  | anaaa Whan      |

|               |                                                                                          | Mode: The devi<br>a match with an     |                                   |                                    |                   |                  |                 |

|               |                                                                                          | r Mode: Reserv                        | -                                 | ,                                  | ·                 |                  |                 |

| bit 10        | A10M: 10-Bit                                                                             | Slave Address                         | Flag bit                          |                                    |                   |                  |                 |

|               |                                                                                          | is a 10-bit slav                      |                                   |                                    |                   |                  |                 |

| hit O         |                                                                                          | is a 7-bit slave                      |                                   |                                    |                   |                  |                 |

| bit 9         |                                                                                          | w Rate Control<br>control is disat    |                                   | rd Sneed mode                      | a (100 kHz also   | disabled for 1   | MHz mode)       |

|               |                                                                                          | control is enab                       |                                   |                                    |                   |                  |                 |

| bit 8         | SMEN: SMB                                                                                | us Input Levels                       | Enable bit                        |                                    | -                 |                  |                 |

|               |                                                                                          | nput logic so th<br>SMBus-specific    |                                   | ompliant with th                   | ne SMBus spec     | fication         |                 |

| Note 1:       | Automatically cle<br>of slave reception<br>setting the SCLR<br>as specified in <b>Se</b> | n. The user soft<br>EL bit. This dela | ware must prov<br>ay must be grea | vide a delay be<br>ater than the m | tween writing to  | o the transmit b | ouffer and      |

#### REGISTER 18-1: I2CxCONL: I2Cx CONTROL REGISTER LOW

**2:** Automatically cleared to '0' at the beginning of slave transmission.

NOTES:

| R/W-0         | U-0                               | R/W-0                                | U-0            | R/W-0             | r-1             | r-1            | R-0, HS, HC           |

|---------------|-----------------------------------|--------------------------------------|----------------|-------------------|-----------------|----------------|-----------------------|

| HLVDEN        | _                                 | LSIDL                                | _              | VDIR              | BGVST           | IRVST          | LVDEVT <sup>(2)</sup> |

| bit 15        |                                   |                                      |                |                   |                 |                | bit                   |

| U-0           | U-0                               | U-0                                  | U-0            | R/W-0             | R/W-0           | R/W-0          | R/W-0                 |

| _             | _                                 |                                      | _              | HLVDL3            | HLVDL2          | HLVDL1         | HLVDL0                |

| bit 7         |                                   |                                      |                |                   |                 |                | bit                   |

|               |                                   |                                      |                |                   |                 |                |                       |

| Legend:       |                                   | HS = Hardware                        |                |                   | e Clearable bit |                |                       |

| R = Readable  |                                   | W = Writable t                       | bit            | '0' = Bit is clea |                 | x = Bit is unk | nown                  |

| -n = Value at | POR                               | '1' = Bit is set                     |                | U = Unimplem      | ented bit, read | as '0'         |                       |

| bit 15        | HLVDEN: H                         | High/Low-Voltage                     | Detect Powe    | r Enable bit      |                 |                |                       |

|               | 1 = HLVD i                        | is enabled                           |                |                   |                 |                |                       |

|               | 0 = HLVD i                        |                                      |                |                   |                 |                |                       |

| bit 14        | Unimplem                          | ented: Read as 'o                    | )'             |                   |                 |                |                       |

| bit 13        | LSIDL: HLVD Stop in Idle Mode bit |                                      |                |                   |                 |                |                       |

|               |                                   | tinues module op<br>ues module opera |                |                   | dle mode        |                |                       |

| bit 12        |                                   | ented: Read as 'o                    |                |                   |                 |                |                       |

| bit 11        | VDIR: Volta                       | age Change Direc                     | tion Select bi | t                 |                 |                |                       |

|               |                                   | occurs when volta                    |                |                   |                 |                |                       |

| bit 10        |                                   | eserved bit (value                   |                |                   | ,               | ,              |                       |

| bit 9         |                                   | served bit (value i                  | • •            |                   |                 |                |                       |

| bit 8         |                                   | ow-Voltage Event                     | •              |                   |                 |                |                       |

|               |                                   | ent is true during                   |                |                   |                 |                |                       |

|               |                                   | ent is not true dur                  | -              | struction cycle   |                 |                |                       |

| bit 7-4       | •                                 | ented: Read as 'o                    |                |                   |                 |                |                       |

| bit 3-0       |                                   | <b>D&gt;:</b> High/Low-Volt          | •              |                   |                 |                |                       |

|               | 1111 = Ext<br>1110 = Trip         | ernal analog inpu                    | t is used (inp | ut comes from th  | ne HLVDIN pin)  | )              |                       |

|               | 1101 = Trip                       |                                      |                |                   |                 |                |                       |

|               | 1100 = Trip                       | Point 3 <sup>(1)</sup>               |                |                   |                 |                |                       |

|               | •                                 |                                      |                |                   |                 |                |                       |

|               | •                                 |                                      |                |                   |                 |                |                       |

|               | •<br>0100 = Trir                  | o Point 11 <sup>(1)</sup>            |                |                   |                 |                |                       |

|               | 0100 = Inp<br>00xx = Unp          |                                      |                |                   |                 |                |                       |

#### REGISTER 29-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

2: The LVDIF flag cannot be cleared by software unless LVDEVT = 0. The voltage must be monitored so that the HLVD condition (as set by VDIR and HLVDL<3:0>) is not asserted.

#### REGISTER 30-8: FWDT CONFIGURATION REGISTER (CONTINUED)

- bit 3-0 WDTPS<3:0>: Watchdog Timer Postscale Select bits 1111 = 1:32,768 1110 = 1:16,384 1101 = 1:8,192 1100 = 1:4,096 1011 = 1:2,048 1010 = 1:1,024 1001 = 1:512 1000 = 1:256 0111 = 1:128 0110 = 1:64 0101 = 1:32 0100 = 1:16 0011 = 1:8

- 0010 **= 1:4**

- 0001 = 1:2 0000 = 1:1

#### 30.4 Watchdog Timer (WDT)

For PIC24FJ1024GA610/GB610 family devices, the WDT is driven by the LPRC Oscillator, the Secondary Oscillator (SOSC) or the system timer. When the device is in Sleep mode, the LPRC Oscillator will be used. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 31 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 31 kHz input, the prescaler yields a nominal WDT Time-out (TWDT) period of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPS<3:0> Configuration bits (FWDT<3:0>), which allows the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler time-out periods, ranges from 1 ms to 131 seconds, can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE (RCON<3:2>) bits will need to be cleared in software after the device wakes up. The WDT Flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

| Note: | The CLRWDT and PWRSAV instructions        |

|-------|-------------------------------------------|

|       | clear the prescaler and postscaler counts |

|       | when executed.                            |

#### 30.4.1 WINDOWED OPERATION

The Watchdog Timer has an optional Fixed Window mode of operation. In this Windowed mode, CLRWDT instructions can only reset the WDT during the last 1/4 of the programmed WDT period. A CLRWDT instruction executed before that window causes a WDT Reset, similar to a WDT time-out.

Windowed WDT mode is enabled by programming the WINDIS Configuration bit (FWDT<7>) to '0'.

#### 30.4.2 CONTROL REGISTER

The WDT is enabled or disabled by the FWDTEN<1:0> Configuration bits (FWDT<6:5>). When the Configuration bits, FWDTEN<1:0> = 11, the WDT is always enabled.

The WDT can be optionally controlled in software when the Configuration bits, FWDTEN<1:0> = 10. When FWDTEN<1:0> = 00, the Watchdog Timer is always disabled. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical code segments for maximum power savings.

| TABLE 32-1: | SYMBOLS USED IN OPCODE DESCRIPTIONS |

|-------------|-------------------------------------|

|-------------|-------------------------------------|

| Field           | Description                                                                          |

|-----------------|--------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                      |

| (text)          | Means "content of text"                                                              |

| [text]          | Means "the location addressed by text"                                               |

| { }             | Optional field or operation                                                          |

| <n:m></n:m>     | Register bit field                                                                   |

| .b              | Byte mode selection                                                                  |

| .d              | Double-Word mode selection                                                           |

| .S              | Shadow register select                                                               |

| .W              | Word mode selection (default)                                                        |

| bit4            | 4-bit Bit Selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |

| f               | File register address ∈ {0000h1FFFh}                                                 |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4            | 4-bit unsigned literal $\in \{015\}$                                                 |

| lit5            | 5-bit unsigned literal ∈ {031}                                                       |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                      |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |

| lit14           | 14-bit unsigned literal ∈ {016383}                                                   |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                   |

| lit23           | 23-bit unsigned literal ∈ {08388607}; LSB must be '0'                                |

| None            | Field does not require an entry, may be blank                                        |

| PC              | Program Counter                                                                      |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                       |

| Wb              | Base W register ∈ {W0W15}                                                            |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm,Wn           | Dividend, Divisor Working register pair (direct addressing)                          |

| Wn              | One of 16 Working registers ∈ {W0W15}                                                |

| Wnd             | One of 16 destination Working registers ∈ {W0W15}                                    |

| Wns             | One of 16 source Working registers ∈ {W0W15}                                         |

| WREG            | W0 (Working register used in file register instructions)                             |

| Ws              | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                         |

| Wso             | Source W register ∈ { Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }         |

| Normally Write-Only)263Resets97BOR (Brown-out Reset)97Brown-out Reset (BOR)100Clock Source Selection100Clock Source Selection100CM (Configuration Mismatch Reset)97Delay Times101Device Times100IOPUWR (Illegal Opcode Reset)97MCLR (Master Clear Pin Reset)97POR (Power-on Reset)97RCON Flags, Operation99SFR States100SWR (RESET Instruction)97TRAPR (Trap Conflict Reset)97WDT (Watchdog Timer Reset)97WDT (Watchdog Timer Reset)97RtCCAlarm Configuration328Alarm Mask Settings (figure)329Alarm Value Registers322Calibration328Clock Source Selection313Control Registers314Event Timestamping330Power Control329Register Mapping313RTCVAL Register Mappings317Source Clock311Timestamp Registers324Value Registers324Value Registers320Write Lock313 | UxTXREG (UARTx Transmit,            |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|

| BOR (Brown-out Reset)97Brown-out Reset (BOR)100Clock Source Selection100CM (Configuration Mismatch Reset)97Delay Times101Device Times100IOPUWR (Illegal Opcode Reset)97MCLR (Master Clear Pin Reset)97POR (Power-on Reset)97RCON Flags, Operation99SFR States100SWR (RESET Instruction)97TRAPR (Trap Conflict Reset)97WDT (Watchdog Timer Reset)97Revision History455RTCCAlarm Configuration328Alarm Value Registers322Calibration328Clock Source Selection313Control Registers314Event Timestamping330Power Control329Register Mapping313RTCVAL Register Mapping313RTCVAL Register Mapping314Timestamp Registers324Value Registers324Value Registers324Value Registers324                                                                                  | Normally Write-Only)263             |  |

| Brown-out Reset (BOR)100Clock Source Selection100CM (Configuration Mismatch Reset)97Delay Times101Device Times100IOPUWR (Illegal Opcode Reset)97MCLR (Master Clear Pin Reset)97POR (Power-on Reset)97RCON Flags, Operation99SFR States100SWR (RESET Instruction)97TRAPR (Trap Conflict Reset)97WDT (Watchdog Timer Reset)97RCCC41srAlarm Configuration328Alarm Mask Settings (figure)329Alarm Value Registers322Calibration328Clock Source Selection313Control Registers314Event Timestamping330Power Control329Register Mapping313RTCVAL Register Mapping313RTCVAL Register Mapping314Livent Registers324Value Registers324Value Registers324Value Registers324                                                                                            | Resets                              |  |

| Clock Source Selection100CM (Configuration Mismatch Reset)97Delay Times101Device Times100IOPUWR (Illegal Opcode Reset)97MCLR (Master Clear Pin Reset)97POR (Power-on Reset)97POR (Power-on Reset)97RCON Flags, Operation99SFR States100SWR (RESET Instruction)97TRAPR (Trap Conflict Reset)97UWR (Uninitialized W Register Reset)97WDT (Watchdog Timer Reset)97Revision History455RTCCAlarm Configuration328Alarm Value Registers322Calibration328Clock Source Selection313Control Registers314Event Timestamping330Power Control329Register Mapping313RTCVAL Register Mappings317Source Clock311Timestamp Registers324Value Registers324Value Registers324                                                                                                 |                                     |  |

| CM (Configuration Mismatch Reset)97Delay Times101Device Times100IOPUWR (Illegal Opcode Reset)97MCLR (Master Clear Pin Reset)97POR (Power-on Reset)97RCON Flags, Operation99SFR States100SWR (RESET Instruction)97TRAPR (Trap Conflict Reset)97UWR (Uninitialized W Register Reset)97WDT (Watchdog Timer Reset)97Revision History455RTCCAlarm Configuration328Alarm Value Registers322Calibration328Clock Source Selection313Control Registers314Event Timestamping330Power Control329Register Mapping313RTCVAL Register Mappings317Source Clock311Timestamp Registers324Value Registers324Value Registers324                                                                                                                                                | Brown-out Reset (BOR)100            |  |

| Delay Times101Device Times100IOPUWR (Illegal Opcode Reset)97MCLR (Master Clear Pin Reset)97POR (Power-on Reset)97RCON Flags, Operation99SFR States100SWR (RESET Instruction)97TRAPR (Trap Conflict Reset)97UWR (Uninitialized W Register Reset)97WDT (Watchdog Timer Reset)97Revision History455RTCC41arm Configuration328Alarm Configuration328Alarm Value Registers322Calibration328Clock Source Selection313Control Registers314Event Timestamping330Power Control329Register Mapping313RTCVAL Register Mappings317Source Clock311Timestamp Registers324Value Registers324Value Registers324                                                                                                                                                             | Clock Source Selection 100          |  |

| Device Times100IOPUWR (Illegal Opcode Reset)97MCLR (Master Clear Pin Reset)97POR (Power-on Reset)97RCON Flags, Operation99SFR States100SWR (RESET Instruction)97TRAPR (Trap Conflict Reset)97UWR (Uninitialized W Register Reset)97WDT (Watchdog Timer Reset)97Revision History455RTCC455Alarm Configuration328Alarm Value Registers322Calibration328Clock Source Selection313Control Registers314Event Timestamping330Power Control329Register Mapping313RTCVAL Register Mapping317Source Clock311Timestamp Registers324Value Registers320                                                                                                                                                                                                                 | CM (Configuration Mismatch Reset)97 |  |

| IOPUWR (Illegal Opcode Reset)97MCLR (Master Clear Pin Reset)97POR (Power-on Reset)97RCON Flags, Operation99SFR States100SWR (RESET Instruction)97TRAPR (Trap Conflict Reset)97UWR (Uninitialized W Register Reset)97WDT (Watchdog Timer Reset)97Revision History455RTCC328Alarm Configuration328Alarm Value Registers322Calibration328Clock Source Selection313Control Registers314Event Timestamping330Power Control329Register Mapping313RTCVAL Register Mappings317Source Clock311Timestamp Registers324Value Registers324Value Registers320                                                                                                                                                                                                             | Delay Times 101                     |  |