Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj512gb606t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Pin Diagrams<sup>(1)</sup> (Continued)

PIC24FJXXXGA610 121-Pin BGA

|   | 1        | 2        | 3         | 4        | 5         | 6        | 7         | 8         | 9         | 10        | 11        |  |

|---|----------|----------|-----------|----------|-----------|----------|-----------|-----------|-----------|-----------|-----------|--|

| A | O<br>RE4 | RE3      | RG13      | RE0      | RG0       | RF1      | O<br>N/C  | O<br>N/C  | RD12      | RD2       | RD1       |  |

| В | O<br>N/C | RG15     | RE2       | RE1      | O<br>RA7  | RF0      | O<br>VCAP | RD5       | RD3       | O<br>Vss  | O<br>RC14 |  |

| С | RE6      |          | RG12      | RG14     | O<br>RA6  | ⊖<br>N/C | O<br>RD7  | RD4       | ⊖<br>N/C  | O<br>RC13 | RD11      |  |

| D | RC1      | RE7      | RE5       | ∩<br>N/C | ⊖<br>N/C  | ⊖<br>N/C | O<br>RD6  | RD13      | RD0       | ∩<br>N/C  | RD10      |  |

| E | O<br>RC4 | RC3      | O<br>RG6  | RC2      | ⊖<br>N/C  | RG1      | ⊖<br>N/C  | RA15      | RD8       | RD9       | RA14      |  |

| F |          | O<br>RG8 | O<br>RG9  | O<br>RG7 | O<br>Vss  | O<br>N/C | ∩<br>N/C  |           | O<br>RC12 | O<br>Vss  | O<br>RC15 |  |

| G | RE8      | O<br>RE9 | RA0       | ⊖<br>N/C |           | O<br>Vss | O<br>Vss  | ⊖<br>N/C  | RA5       | RA3       | RA4       |  |

| н | O<br>RB5 | O<br>RB4 | ∩<br>N/C  | ⊖<br>N/C | ⊖<br>N/C  |          | ∩<br>N/C  | RF7       | RF6       | RG2       | RA2       |  |

| J | O<br>RB3 | O<br>RB2 | O<br>RB7  |          | O<br>RB11 | RA1      | O<br>RB12 | ⊖<br>N/C  | ⊖<br>N/C  | RF8       | RG3       |  |

| к | O<br>RB1 | O<br>RB0 | O<br>RA10 | O<br>RB8 | ⊖<br>N/C  | RF12     | O<br>RB14 |           | RD15      | RF3       | RF2       |  |

| L | O<br>RB6 | O<br>RA9 | O<br>AVss | O<br>RB9 | O<br>RB10 | RF13     | O<br>RB13 | O<br>RB15 | RD14      | RF4       | RF5       |  |

Legend: See Table 6 for a complete description of pin functions. Pinouts are subject to change. Note 1: Gray shading indicates 5.5V tolerant input pins.

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                          |                          |     |                 |                                                                  |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|--------------------------|--------------------------|-----|-----------------|------------------------------------------------------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA  | GB612<br>121-Pin<br>BGA  | I/O | Input<br>Buffer | Description                                                      |

| U6RX            | 27                                  | 27                               | 41                               | 41                               | J7                       | J7                       | I   | ST              | UART6 Receive Input                                              |

| U6TX            | 18                                  | 18                               | 27                               | 27                               | J3                       | J3                       | 0   | DIG             | UART6 Transmit Output                                            |

| USBID           | —                                   | 33                               | —                                | 51                               | _                        | K10                      | Ι   | ST              | USB OTG ID Input                                                 |

| USBOEN          | —                                   | 12                               | _                                | 21                               | _                        | H2                       | 0   | DIG             | USB Output Enable (active-low)                                   |

| VBUS            | _                                   | 34                               | _                                | 54                               | _                        | H8                       | I   |                 | VBUS Supply Detect                                               |

| VCAP            | 56                                  | 56                               | 85                               | 85                               | B7                       | B7                       | Ρ   | —               | External Filter Capacitor<br>Connection (regulator enabled)      |

| Vdd             | 10,26,38                            | 10,26,38                         | 2,16,37,<br>46,62                | 2,16,37,<br>46,62                | C2,F8,<br>G5,H6,<br>K8   | C2,F8,<br>G5,H6,<br>K8   | Ρ   | —               | Positive Supply for Peripheral<br>Digital Logic and I/O Pins     |

| VREF+           | 16                                  | 16                               | 25,29                            | 25,29                            | K2,K3                    | K2,K3                    | I   | ANA             | Comparator and A/D Reference<br>Voltage (high) Input             |

| VREF-           | 15                                  | 15                               | 24,28                            | 24,28                            | K1,L2                    | K1,L2                    | I   | ANA             | Comparator and A/D Reference<br>Voltage (low) Input              |

| Vss             | 9,25,41                             | 9,25,41                          | 15,36,45,<br>65,75               | 15,36,45,<br>65,75               | B10,F5,<br>F10,G6,<br>G7 | B10,F5,<br>F10,G6,<br>G7 | Ρ   | —               | Ground Reference for<br>Peripheral Digital Logic and I/O<br>Pins |

| VUSB3V3         | _                                   | 35                               | _                                | 55                               | _                        | H9                       | Р   | _               | 3.3V VUSB                                                        |

#### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL =

TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMB$ us input buffer

XCVR = Dedicated Transceiver

DS30010074D-page 40

| DSRPAG<br>(Data Space Read<br>Register) | DSWPAG<br>(Data Space Write<br>Register) | Source/Destination<br>Address while<br>Indirect<br>Addressing | 24-Bit EA<br>Pointing to EDS | Comment                           |

|-----------------------------------------|------------------------------------------|---------------------------------------------------------------|------------------------------|-----------------------------------|

| X <sup>(1)</sup>                        | х <sup>(1)</sup>                         | 0000h to 1FFFh                                                | 000000h to<br>001FFFh        | Near Data Space <sup>(2)</sup>    |

|                                         |                                          | 2000h to 7FFFh                                                | 002000h to<br>007FFFh        |                                   |

| 001h                                    | 001h                                     |                                                               | 008000h to<br>00FFFEh        |                                   |

| 002h                                    | 002h                                     |                                                               | 010000h to<br>017FFEh        |                                   |

| 003h                                    | 003h                                     |                                                               | 018000h to                   |                                   |

| •                                       | •                                        |                                                               | 0187FEh                      | EPMP Memory Space                 |

| •                                       | •                                        | 8000h to FFFFh                                                | •                            | EPIVIP MEMORY Space               |

| •                                       | •                                        |                                                               | •                            |                                   |

| •                                       | •                                        |                                                               | •                            |                                   |

| •                                       | •                                        |                                                               | •                            |                                   |

| 1FFh                                    | 1FFh                                     |                                                               | FF8000h to<br>FFFFFEh        |                                   |

| 000h                                    | 000h                                     |                                                               | Invalid Address              | Address Error Trap <sup>(3)</sup> |

#### TABLE 4-13: EDS MEMORY ADDRESS WITH DIFFERENT PAGES AND ADDRESSES

**Note 1:** If the source/destination address is below 8000h, the DSRPAG and DSWPAG registers are not considered.

- 2: This Data Space can also be accessed by Direct Addressing.

- **3:** When the source/destination address is above 8000h and DSRPAG/DSWPAG are '0', an address error trap will occur.

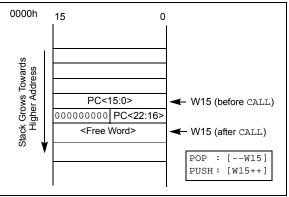

#### 4.2.6 SOFTWARE STACK

Apart from its use as a Working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer (SSP). The pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-7. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value register (SPLIM), associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be wordaligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 2000h in RAM, initialize the SPLIM with the value, 1FFEh.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the SFR space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 4-7: CALL STACK FRAME

#### 5.1 Summary of DMA Operations

The DMA Controller is capable of moving data between addresses according to a number of different parameters. Each of these parameters can be independently configured for any transaction; in addition, any or all of the DMA channels can independently perform a different transaction at the same time. Transactions are classified by these parameters:

- Source and destination (SFRs and data RAM)

- · Data size (byte or word)

- Trigger source

- Transfer mode (One-Shot, Repeated or Continuous)

- Addressing modes (fixed address or address blocks, with or without address increment/ decrement)

In addition, the DMA Controller provides channel priority arbitration for all channels.

#### 5.1.1 SOURCE AND DESTINATION

Using the DMA Controller, data may be moved between any two addresses in the Data Space. The SFR space (0000h to 07FFh), or the data RAM space (0800h to FFFFh), can serve as either the source or the destination. Data can be moved between these areas in either direction or between addresses in either area. The four different combinations are shown in Figure 5-2.

If it is necessary to protect areas of data RAM, the DMA Controller allows the user to set upper and lower address boundaries for operations in the Data Space above the SFR space. The boundaries are set by the DMAH and DMAL Limit registers. If a DMA channel attempts an operation outside of the address boundaries, the transaction is terminated and an interrupt is generated.

#### 5.1.2 DATA SIZE

The DMA Controller can handle both 8-bit and 16-bit transactions. Size is user-selectable using the SIZE bit (DMACHn<1>). By default, each channel is configured for word-sized transactions. When byte-sized transactions are chosen, the LSb of the source and/or destination address determines if the data represents the upper or lower byte of the data RAM location.

#### 5.1.3 TRIGGER SOURCE

The DMA Controller can use any one of the device's interrupt sources to initiate a transaction. The DMA Trigger sources are listed in reverse order of their natural interrupt priority and are shown in Table 5-1.

Since the source and destination addresses for any transaction can be programmed independently of the Trigger source, the DMA Controller can use any Trigger to perform an operation on any peripheral. This also allows DMA channels to be cascaded to perform more complex transfer operations.

#### 5.1.4 TRANSFER MODE

The DMA Controller supports four types of data transfers, based on the volume of data to be moved for each Trigger.

- One-Shot: A single transaction occurs for each Trigger.

- Continuous: A series of back-to-back transactions occur for each Trigger; the number of transactions is determined by the DMACNTn transaction counter.

- Repeated One-Shot: A single transaction is performed repeatedly, once per Trigger, until the DMA channel is disabled.

- Repeated Continuous: A series of transactions are performed repeatedly, one cycle per Trigger, until the DMA channel is disabled.

All transfer modes allow the option to have the source and destination addresses, and counter value automatically reloaded after the completion of a transaction. Repeated mode transfers do this automatically.

#### 5.1.5 ADDRESSING MODES

The DMA Controller also supports transfers between single addresses or address ranges. The four basic options are:

- · Fixed-to-Fixed: Between two constant addresses

- Fixed-to-Block: From a constant source address to a range of destination addresses

- Block-to-Fixed: From a range of source addresses to a single, constant destination address

- Block-to-Block: From a range to source addresses to a range of destination addresses

The option to select auto-increment or auto-decrement of source and/or destination addresses is available for Block Addressing modes.

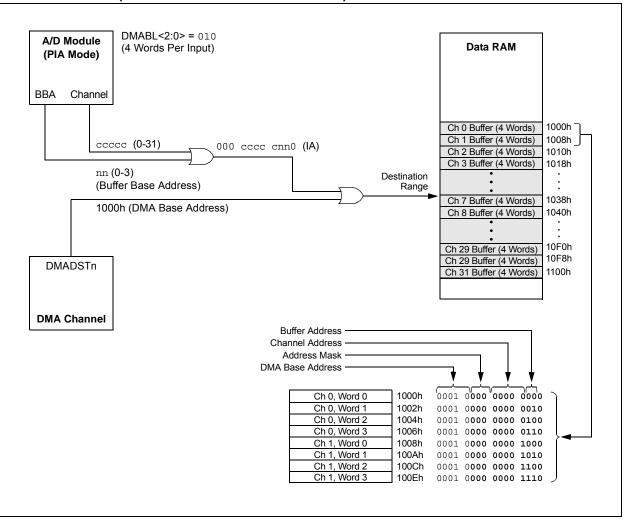

In addition to the four basic modes, the DMA Controller also supports Peripheral Indirect Addressing (PIA) mode, where the source or destination address is generated jointly by the DMA Controller and a PIA capable peripheral. When enabled, the DMA channel provides a base source and/or destination address, while the peripheral provides a fixed range offset address.

For PIC24FJ1024GA610/GB610 family devices, the 12-bit A/D Converter module is the only PIA capable peripheral. Details for its use in PIA mode are provided in **Section 25.0 "12-Bit A/D Converter with Threshold Detect"**.

| TABLE 0-2. INTERRUPT VECTOR DETAILS (CONTINUED) | <b>TABLE 8-2:</b> | INTERRUPT VECTOR DETAILS (CO | NTINUED) |

|-------------------------------------------------|-------------------|------------------------------|----------|

|-------------------------------------------------|-------------------|------------------------------|----------|

| Interrunt Source                   | IRQ |             | Int      | errupt Bit Lo | ocation         |

|------------------------------------|-----|-------------|----------|---------------|-----------------|

| Interrupt Source                   | #   | IVT Address | Flag     | Enable        | Priority        |

| I2C1BC – I2C1 Bus Collision        | 84  | 0000BCh     | IFS5<4>  | IEC5<4>       | I2C1BCInterrupt |

| I2C2BC – I2C2 Bus Collision        | 85  | 0000BEh     | IFS5<5>  | IEC5<5>       | I2C2BCInterrupt |

| USB1 – USB1 Interrupt              | 86  | 0000C0h     | IFS5<6>  | IEC5<6>       | USB1Interrupt   |

| U4E – UART4 Error                  | 87  | 0000C2h     | IFS5<7>  | IEC5<7>       | U4ErrInterrupt  |

| U4RX – UART4 Receiver              | 88  | 0000C4h     | IFS5<8>  | IEC5<8>       | U4RXInterrupt   |

| U4TX – UART4 Transmitter           | 89  | 0000C6h     | IFS5<9>  | IEC5<9>       | U4TXInterrupt   |

| SPI3 – SPI3 General                | 90  | 0000C8h     | IFS5<10> | IEC5<10>      | SPI3Interrupt   |

| SPI3TX – SPI3 Transfer Done        | 91  | 0000CAh     | IFS5<11> | IEC5<11>      | SPI3TXInterrupt |

| —                                  | 92  | 92          | _        | _             | —               |

| —                                  | 93  | 93          | _        | _             | —               |

| CCP3 – Capture/Compare 3           | 94  | 0000D0h     | IFS5<14> | IEC5<14>      | CCP3Interrupt   |

| CCP4 – Capture/Compare 4           | 95  | 0000D2h     | IFS5<15> | IEC5<15>      | CCP4Interrupt   |

| CLC1 – Configurable Logic Cell 1   | 96  | 0000D4h     | IFS6<0>  | IEC6<0>       | CLC1Interrupt   |

| CLC2 – Configurable Logic Cell 2   | 97  | 0000D6h     | IFS6<1>  | IEC6<1>       | CLC2Interrupt   |

| CLC3 – Configurable Logic Cell 3   | 98  | 0000D8h     | IFS6<2>  | IEC6<2>       | CLC3Interrupt   |

| CLC4 – Configurable Logic Cell 4   | 99  | 0000DAh     | IFS6<3>  | IEC6<3>       | CLC4Interrupt   |

| —                                  | 100 | —           | —        | —             | —               |

| CCT1 – Capture/Compare Timer1      | 101 | 0000DEh     | IFS6<5>  | IEC6<5>       | CCT1Interrupt   |

| CCT2 – Capture/Compare Timer2      | 102 | 0000E0h     | IFS6<6>  | IEC6<6>       | CCT2Interrupt   |

| —                                  | 103 | —           | —        | —             | —               |

| —                                  | 104 | —           | —        | _             | —               |

|                                    | 105 | —           | —        | _             | —               |

| FST – FRC Self-Tuning Interrupt    | 106 | 0000E8h     | IFS6<10> | IEC6<10>      | FSTInterrupt    |

|                                    | 107 | —           | —        | —             | —               |

|                                    | 108 | —           | —        | _             | —               |

| I2C3BC – I2C3 Bus Collision        | 109 | 0000EEh     | IFS6<13> | IEC6<13>      | I2C3BCInterrupt |

| RTCCTS – Real-Time Clock Timestamp | 110 | 0000F0h     | IFS6<14> | IEC6<14>      | RTCCTSInterrupt |

| U5RX – UART5 Receiver              | 111 | 0000F2h     | IFS6<15> | IEC6<15>      | U5RXInterrupt   |

| U5TX – UART5 Transmitter           | 112 | 0000F4h     | IFS7<0>  | IEC7<0>       | U5TXInterrupt   |

| U5E – UART5 Error                  | 113 | 0000F6h     | IFS7<1>  | IEC7<1>       | U5ErrInterrupt  |

| U6RX – UART6 Receiver              | 114 | 0000F8h     | IFS7<2>  | IEC7<2>       | U6RXInterrupt   |

| U6TX – UART6 Transmitter           | 115 | 0000FAh     | IFS7<3>  | IEC7<3>       | U6TXInterrupt   |

| U6E – UART6 Error                  | 116 | 0000FCh     | IFS7<4>  | IEC7<4>       | U6ErrInterrupt  |

| JTAG – JTAG                        | 117 | 0000FEh     | IFS7<5>  | IEC7<5>       | JTAGInterrupt   |

### 9.8 Secondary Oscillator

#### 9.8.1 BASIC SOSC OPERATION

PIC24FJ1024GA610/GB610 family devices do not have to set the SOSCEN bit to use the Secondary Oscillator. Any module requiring the SOSC (such as RTCC or Timer1) will automatically turn on the SOSC when the clock signal is needed. The SOSC, however, has a long start-up time (as long as 1 second). To avoid delays for peripheral start-up, the SOSC can be manually started using the SOSCEN bit.

To use the Secondary Oscillator, the SOSCSEL bit (FOSC<3>) must be set to '1'. Programming the SOSCSEL bit to '0' configures the SOSC pins for Digital mode, enabling digital I/O functionality on the pins.

#### 9.8.2 CRYSTAL SELECTION

The 32.768 kHz crystal used for the SOSC must have the following specifications in order to properly start up and run at the correct frequency when in High-Power mode:

- 12.5 pF loading capacitance

- 1.0 pF shunt capacitance

- A typical ESR of 35K; 50K maximum

In addition, the two external crystal loading capacitors should be in the range of 18-22 pF, which will be based on the PC board layout. The capacitors should be COG, 5% tolerance and rated 25V or greater.

The accuracy and duty cycle of the SOSC can be measured on the REFO pin, and is recommended to be in the range of 40-60% and accurate to  $\pm 0.65$  Hz.

#### 9.8.3 LOW-POWER SOSC OPERATION

The Secondary Oscillator can operate in two distinct levels of power consumption based on device configuration. In Low-Power mode, the oscillator operates in a low drive strength, low-power state. By default, the oscillator uses a higher drive strength, and therefore, requires more power. Low-Power mode is selected by Configuration bit, SOSCHP (FDEVOPT1<3>). The lower drive strength of this mode makes the SOSC more sensitive to noise and requires a longer start-up time. This mode can be used with lower load capacitance crystals (6 pF-9 pF) having higher ESR ratings (50K-80K) to reduce Sleep current in the RTCC. When Low-Power mode is used, care must be taken in the design and layout of the SOSC circuit to ensure that the oscillator starts up and oscillates properly. PC board layout issues, stray capacitance and other factors will need to be carefully controlled in order for the crystal to operate.

For 32-bit cascaded operation, these steps are also necessary:

- 1. Set the OC32 bits for both registers (OCyCON2<8> and OCxCON2<8>). Enable the even numbered module first to ensure the modules will start functioning in unison.

- Clear the OCTRIG bit of the even module (OCyCON2<7>), so the module will run in Synchronous mode.

- 3. Configure the desired output and Fault settings for OCy.

- 4. Force the output pin for OCx to the output state by clearing the OCTRIS bit.

- If Trigger mode operation is required, configure the Trigger options in OCx by using the OCTRIG (OCxCON2<7>), TRIGMODE (OCxCON1<3>) and SYNCSEL<4:0> (OCxCON2<4:0>) bits.

- Configure the desired Compare or PWM mode of operation (OCM<2:0>) for OCy first, then for OCx.

Depending on the output mode selected, the module holds the OCx pin in its default state and forces a transition to the opposite state when OCxR matches the timer. In Double Compare modes, OCx is forced back to its default state when a match with OCxRS occurs. The OCxIF interrupt flag is set after an OCxR match in Single Compare modes and after each OCxRS match in Double Compare modes.

Single-Shot pulse events only occur once, but may be repeated by simply rewriting the value of the OCxCON1 register. Continuous pulse events continue indefinitely until terminated.

#### 15.3 Pulse-Width Modulation (PWM) Mode

In PWM mode, the output compare module can be configured for edge-aligned or center-aligned pulse waveform generation. All PWM operations are doublebuffered (buffer registers are internal to the module and are not mapped into SFR space).

To configure the output compare module for PWM operation:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins if available on the OC module you are using. Otherwise, configure the dedicated OCx output pins.

- 2. Calculate the desired duty cycles and load them into the OCxR register.

- 3. Calculate the desired period and load it into the OCxRS register.

- Select the current OCx as the synchronization source by writing 0x1F to the SYNCSEL<4:0> bits (OCxCON2<4:0>) and '0' to the OCTRIG bit (OCxCON2<7>).

- 5. Select a clock source by writing to the OCTSEL<2:0> bits (OCxCON1<12:10>).

- 6. Enable interrupts, if required, for the timer and output compare modules. The output compare interrupt is required for PWM Fault pin utilization.

- Select the desired PWM mode in the OCM<2:0> bits (OCxCON1<2:0>).

- Appropriate Fault inputs may be enabled by using the ENFLT<2:0> bits as described in Register 15-1.

- 9. If a timer is selected as a clock source, set the selected timer prescale value. The selected timer's prescaler output is used as the clock input for the OCx timer, and not the selected timer output.

Note: This peripheral contains input and output functions that may need to be configured by the Peripheral Pin Select. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

| U-0        | U-0                                    | R/W-0                             | R/W-0                   | R/W-0             | R/W-0               | R/W-0                       | R/W-0                 |

|------------|----------------------------------------|-----------------------------------|-------------------------|-------------------|---------------------|-----------------------------|-----------------------|

| <u> </u>   | <u> </u>                               | OCSIDL                            | OCTSEL2                 | OCTSEL1           | OCTSEL0             | ENFLT2 <sup>(2)</sup>       | ENFLT1 <sup>(2)</sup> |

| bit 15     |                                        | OCCIDE                            | OUTOLLE                 | OUTOLLT           | OUTOLLU             |                             | bit 8                 |

|            |                                        |                                   |                         |                   |                     |                             |                       |

| R/W-0      | R/W-0, HSC                             | R/W-0, HSC                        | R/W-0, HSC              | R/W-0             | R/W-0               | R/W-0                       | R/W-0                 |

| ENFLT0     | (2) OCFLT2 <sup>(2,3)</sup>            | OCFLT1 <sup>(2,4)</sup>           | OCFLT0 <sup>(2,4)</sup> | TRIGMODE          | OCM2 <sup>(1)</sup> | OCM1 <sup>(1)</sup>         | OCM0 <sup>(1)</sup>   |

| bit 7      | 1                                      |                                   | L                       | l                 |                     | •                           | bit 0                 |

|            |                                        |                                   |                         |                   |                     |                             |                       |

| Legend:    |                                        | HSC = Hardw                       | are Settable/C          | learable bit      |                     |                             |                       |

| R = Read   | able bit                               | W = Writable                      | bit                     | U = Unimplem      | nented bit, read    | l as '0'                    |                       |

| -n = Value | e at POR                               | '1' = Bit is set                  |                         | '0' = Bit is clea | ared                | x = Bit is unkr             | nown                  |

|            |                                        |                                   |                         |                   |                     |                             |                       |

| bit 15-14  | Unimplemen                             | ted: Read as '                    | )'                      |                   |                     |                             |                       |

| bit 13     | OCSIDL: Out                            | put Compare x                     | Stop in Idle Mo         | ode Control bit   |                     |                             |                       |

|            |                                        | ompare x halts                    |                         |                   |                     |                             |                       |

|            |                                        |                                   |                         | e in CPU Idle m   | node                |                             |                       |

| bit 12-10  |                                        | >: Output Com                     |                         | elect bits        |                     |                             |                       |

|            | 111 = Periphe<br>110 = Reserv          | eral clock (Fcy)                  |                         |                   |                     |                             |                       |

|            | 101 = Reserv                           |                                   |                         |                   |                     |                             |                       |

|            |                                        |                                   | hchronous cloc          | k is supported)   |                     |                             |                       |

|            | 011 = Timer5                           |                                   |                         |                   |                     |                             |                       |

|            | 010 = Timer4<br>001 = Timer3           |                                   |                         |                   |                     |                             |                       |

|            | 001 = Timer3<br>000 = Timer2           |                                   |                         |                   |                     |                             |                       |

| bit 9      |                                        | It Input 2 Enab                   | e bit <b>(2)</b>        |                   |                     |                             |                       |

|            |                                        | Comparator 1/2                    |                         | ed <sup>(3)</sup> |                     |                             |                       |

|            | 0 = Fault 2 is                         |                                   | ,                       |                   |                     |                             |                       |

| bit 8      |                                        | lt Input 1 Enab                   |                         |                   |                     |                             |                       |

|            | 1 = Fault 1 (0<br>0 = Fault 1 is       | DCFB pin) is er                   | abled <sup>(4)</sup>    |                   |                     |                             |                       |

| bit 7      |                                        | It Input 0 Enab                   | e hit(2)                |                   |                     |                             |                       |

|            |                                        | DCFA pin) is er                   |                         |                   |                     |                             |                       |

|            | 0 = Fault 0 is                         |                                   |                         |                   |                     |                             |                       |

| bit 6      | OCFLT2: Out                            | put Compare x                     | PWM Fault 2 (           | (Comparator 1/2   | 2/3) Condition      | Status bit <sup>(2,3)</sup> |                       |

|            | 1 = PWM Fa                             | ult 2 has occur                   | ed                      |                   |                     |                             |                       |

|            |                                        | Fault 2 has oc                    |                         |                   |                     |                             |                       |

| bit 5      |                                        |                                   |                         | (OCFB pin) Cor    | ndition Status b    | bit <sup>(2,4)</sup>        |                       |

|            |                                        | ult 1 has occur<br>Fault 1 has oc |                         |                   |                     |                             |                       |

|            |                                        | 1 4411 1 1143 00                  | curred                  |                   |                     |                             |                       |

| Note 1:    | The OCx output n<br>"Peripheral Pin \$ | Select (PPS)".                    | •                       |                   |                     |                             | Section 11.4          |

| 2:         | The Fault input er                     |                                   |                         |                   |                     |                             |                       |

| 3:         | The Comparator channels, Compa         |                                   |                         |                   |                     | put controls the            | e OC4-OC6             |

| 4:         | The OCFA/OCFB                          | Fault inputs mu                   | ust also be conf        | figured to an av  | ailable RPn/RF      | In pin. For mor             | e information,        |

#### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

4: The OCFA/OCFB Fault inputs must also be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

#### FIGURE 16-4: 32-BIT TIMER MODE

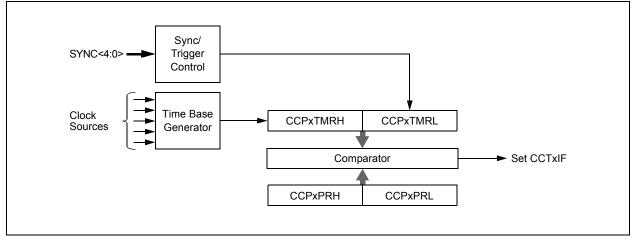

#### 16.3 Output Compare Mode

Output Compare mode compares the Timer register value with the value of one or two Compare registers, depending on its mode of operation. The Output Compare x module, on compare match events, has the ability to generate a single output transition or a train of output pulses. Like most PIC<sup>®</sup> MCU peripherals, the Output Compare x module can also generate interrupts on a compare match event.

Table 16-2 shows the various modes available in Output Compare modes.

| TABLE 16-2: 001              | PUT COMPARE/P         | WM MODES                               |                  |  |  |  |  |

|------------------------------|-----------------------|----------------------------------------|------------------|--|--|--|--|

| MOD<3:0><br>(CCPxCON1L<3:0>) | T32<br>(CCPxCON1L<5>) | Operating Mode                         |                  |  |  |  |  |

| 0001                         | 0                     | Output High on Compare (16-bit)        |                  |  |  |  |  |

| 0001                         | 1                     | Output High on Compare (32-bit)        |                  |  |  |  |  |

| 0010                         | 0                     | Output Low on Compare (16-bit)         | Single Edge Mede |  |  |  |  |

| 0010                         | 1                     | Output Low on Compare (32-bit)         | Single Edge Mode |  |  |  |  |

| 0011                         | 0                     | Output Toggle on Compare (16-bit)      |                  |  |  |  |  |

| 0011                         | 1                     | Output Toggle on Compare (32-bit)      |                  |  |  |  |  |

| 0100                         | 0                     | Dual Edge Compare (16-bit)             | Dual Edge Mode   |  |  |  |  |

| 0101                         | 0                     | Dual Edge Compare (16-bit buffered)    | PWM Mode         |  |  |  |  |

| 0110                         | 0                     | Center-Aligned Pulse (16-bit buffered) | Center PWM Mode  |  |  |  |  |

| 0111                         | 0                     | Variable Frequency Pulse (16-bit)      |                  |  |  |  |  |

| 1111                         | 0                     | External Input Source Mode (16-bit)    |                  |  |  |  |  |

|                              |                       |                                        |                  |  |  |  |  |

#### TABLE 16-2: OUTPUT COMPARE/PWM MODES

NOTES:

| R/W-0              | U-0                    | R/W-0                                  | R/W-0                           | R/W-0                                 | R/W-0                   | R/W-0                 | R/W-0                 |

|--------------------|------------------------|----------------------------------------|---------------------------------|---------------------------------------|-------------------------|-----------------------|-----------------------|

| RXWIEN             | —                      | RXMSK5 <sup>(1)</sup>                  | RXMSK4 <sup>(1,4)</sup>         | RXMSK3 <sup>(1,3)</sup>               | RXMSK2 <sup>(1,2)</sup> | RXMSK1 <sup>(1)</sup> | RXMSK0 <sup>(1)</sup> |

| bit 15             |                        | ·                                      |                                 |                                       | •                       |                       | bit 8                 |

|                    |                        |                                        |                                 |                                       |                         |                       |                       |

| R/W-0              | U-0                    | R/W-0                                  | R/W-0                           | R/W-0                                 | R/W-0                   | R/W-0                 | R/W-0                 |

| TXWIEN             | —                      | TXMSK5 <sup>(1)</sup>                  | TXMSK4 <sup>(1,4)</sup>         | TXMSK3 <sup>(1,3)</sup>               | TXMSK2 <sup>(1,2)</sup> | TXMSK1 <sup>(1)</sup> | TXMSK0 <sup>(1)</sup> |

| bit 7              |                        |                                        |                                 |                                       |                         |                       | bit (                 |

| Legend:            |                        |                                        |                                 |                                       |                         |                       |                       |

| R = Reada          | able bit               | W = Writable                           | bit                             | U = Unimpleme                         | nted bit, read as       | ʻ0'                   |                       |

| -n = Value         | at POR                 | '1' = Bit is set                       | :                               | '0' = Bit is cleare                   | ed                      | x = Bit is unkn       | own                   |

| bit 14<br>bit 13-8 | RXMSK<5                | ented: Read as<br>:0>: RX Buffer       | Mask bits <sup>(1,2,3,4</sup>   |                                       |                         |                       |                       |

|                    |                        | oits; used in con                      | -                               |                                       |                         |                       |                       |

| bit 7              |                        | Transmit Waterr                        |                                 |                                       |                         |                       | _                     |

|                    |                        | rs transmit buffe<br>es transmit buffe |                                 | rmark interrupt w<br>ermark interrupt | /hen TXMSK<5:(          | )> = TXELM<5:         | 0>                    |

| bit 6              | Unimplem               | ented: Read as                         | <b>s</b> 'O'                    |                                       |                         |                       |                       |

| bit 5-0            | TXMSK<5                | :0>: TX Buffer M                       | /lask bits <sup>(1,2,3,4)</sup> |                                       |                         |                       |                       |

|                    | TX mask b              | its; used in conj                      | junction with the               | e TXWIEN bit.                         |                         |                       |                       |

| Note 1:            | Mask values this case. | s higher than Fl                       | FODEPTH are                     | not valid. The m                      | odule will not tri      | gger a match fo       | or any value in       |

| 2:                 | RXMSK2 ar              | nd TXMSK2 bits                         | are only prese                  | nt when FIFODE                        | PTH = 8 or high         | er.                   |                       |

| 3:                 | RXMSK3 ar              | nd TXMSK3 bits                         | are only prese                  | nt when FIFODE                        | PTH = 16 or hig         | her.                  |                       |

|                    |                        |                                        |                                 |                                       |                         |                       |                       |

#### REGISTER 17-10: SPIxIMSKH: SPIx INTERRUPT MASK REGISTER HIGH

**4:** RXMSK4 and TXMSK4 bits are only present when FIFODEPTH = 32.

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "UART" (DS39708), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins. The UART module includes an IrDA<sup>®</sup> encoder/decoder unit.

The PIC24FJ1024GA610/GB610 family devices are equipped with six UART modules, referred to as UART1, UART2, UART3, UART4, UART5 and UART6.

The primary features of the UARTx modules are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with the UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Range from up to 1 Mbps and Down to 15 Hz at 16 MIPS in 16x mode

- Baud Rates Range from up to 4 Mbps and Down to 61 Hz at 16 MIPS in 4x mode

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect  $(9^{th} bit = 1)$

- · Separate Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- Polarity Control for Transmit and Receive Lines

- · Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- Includes DMA Support

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 19-1. The UARTx module consists of these key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

**Note:** Throughout this section, references to register and bit names that may be associated with a specific UART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the Status register for either UART1, UART2, UART3, UART4, UART5 or UART6.

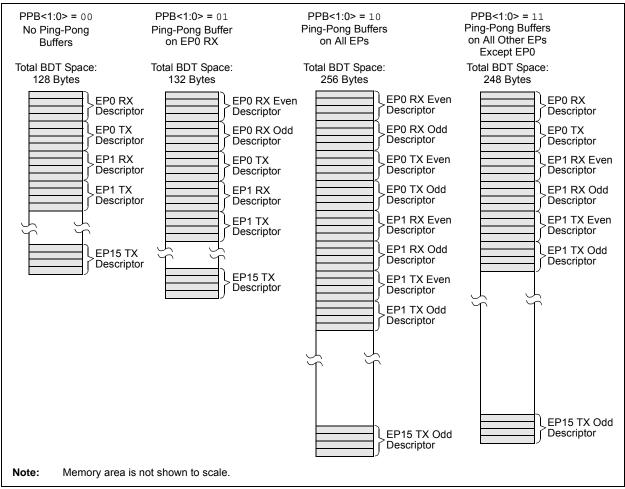

#### 20.2 USB Buffer Descriptors and the BDT

Endpoint buffer control is handled through a structure called the Buffer Descriptor Table (BDT). This provides a flexible method for users to construct and control endpoint buffers of various lengths and configurations.

The BDT can be located in any available 512-byte, aligned block of data RAM. The BDT Pointer (U1BDTP1) contains the upper address byte of the BDT and sets the location of the BDT in RAM. The user must set this pointer to indicate the table's location.

The BDT is composed of Buffer Descriptors (BDs) which are used to define and control the actual buffers in the USB RAM space. Each BD consists of two 16-bit, "soft" (non-fixed-address) registers, BDnSTAT and BDnADR, where n represents one of the 64 possible BDs (range of 0 to 63). BDnSTAT is the status register for BDn, while BDnADR specifies the starting address for the buffer associated with BDn.

Note: Since BDnADR is a 16-bit register, only the first 64 Kbytes of RAM can be accessed by the USB module.

Depending on the endpoint buffering configuration used, there are up to 64 sets of Buffer Descriptors, for a total of 256 bytes. At a minimum, the BDT must be at least 8 bytes long. This is because the *"USB 2.0 Specification"* mandates that every device must have Endpoint 0 with both input and output for initial setup.

Endpoint mapping in the BDT is dependent on three variables:

- Endpoint number (0 to 15)

- Endpoint direction (RX or TX)

- Ping-pong settings (U1CNFG1<1:0>)

Figure 20-7 illustrates how these variables are used to map endpoints in the BDT.

In Host mode, only Endpoint 0 Buffer Descriptors are used. All transfers utilize the Endpoint 0 Buffer Descriptor and Endpoint Control register (U1EP0). For received packets, the attached device's source endpoint is indicated by the value of ENDPT<3:0> in the USB Status register (U1STAT<7:4>). For transmitted packets, the attached device's destination endpoint is indicated by the value written to the USB Token register (U1TOK).

#### FIGURE 20-7: BDT MAPPING FOR ENDPOINT BUFFERING MODES

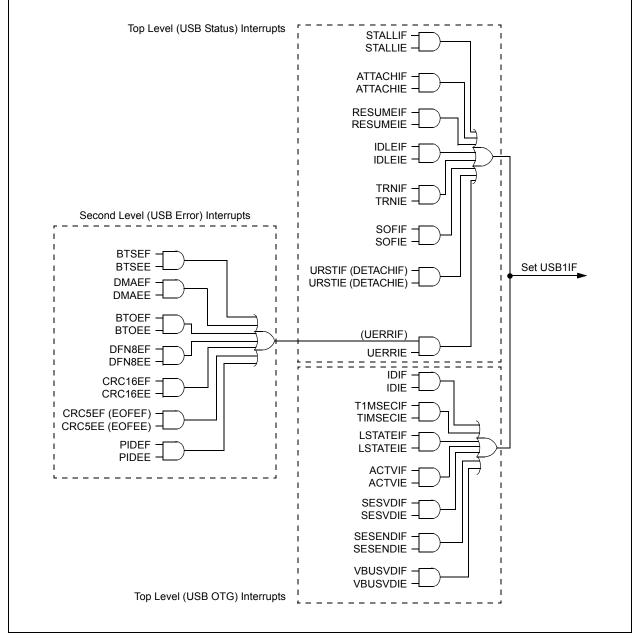

#### 20.3 USB Interrupts

The USB OTG module has many conditions that can be configured to cause an interrupt. All interrupt sources use the same interrupt vector.

Figure 20-8 shows the interrupt logic for the USB module. There are two layers of interrupt registers in the USB module. The top level consists of overall USB status interrupts; these are enabled and flagged in the U1IE and U1IR registers, respectively. The second level consists of USB error conditions, which are enabled and flagged in the U1EIR and U1EIE registers.

An interrupt condition in any of these triggers a USB Error Interrupt Flag (UERRIF) in the top level. Unlike the device-level interrupt flags in the IFSx registers, USB interrupt flags in the U1IR registers can only be cleared by writing a '1' to the bit position.

Interrupts may be used to trap routine events in a USB transaction. Figure 20-9 provides some common events within a USB frame and their corresponding interrupts.

# FIGURE 20-8: USB OTG INTERRUPT FUNNEL

# REGISTER 20-16: U1IR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0           | U-0         | U-0                                        | U-0              | U-0               | U-0                 | U-0                | U-0                |

|---------------|-------------|--------------------------------------------|------------------|-------------------|---------------------|--------------------|--------------------|

| _             | —           |                                            | —                |                   |                     |                    | —                  |

| bit 15        |             |                                            |                  |                   |                     |                    | bit 8              |

|               |             |                                            |                  |                   |                     |                    |                    |

| R/K-0, HS     | U-0         | R/K-0, HS                                  | R/K-0, HS        | R/K-0, HS         | R/K-0, HS           | R/K-0, HS          | R/K-0, HS          |

| STALLIF       |             | RESUMEIF                                   | IDLEIF           | TRNIF             | SOFIF               | UERRIF             | URSTIF             |

| bit 7         |             |                                            |                  |                   |                     |                    | bit 0              |

|               |             |                                            |                  |                   |                     |                    |                    |

| Legend:       |             | U = Unimplem                               | ented bit, read  | d as '0'          |                     |                    |                    |

| R = Readabl   |             | K = Write '1' to                           | o Clear bit      | HS = Hardwa       | re Settable bit     |                    |                    |

| -n = Value at | POR         | '1' = Bit is set                           |                  | '0' = Bit is clea | ared                | x = Bit is unkr    | nown               |

|               |             |                                            |                  |                   |                     |                    |                    |

| bit 15-8      | Unimplem    | ented: Read as '0                          | )'               |                   |                     |                    |                    |

| bit 7         | STALLIF: S  | STALL Handshake                            | e Interrupt bit  |                   |                     |                    |                    |

|               |             | LL handshake wa                            | s sent by the p  | peripheral durin  | g the handshal      | ke phase of the    | transaction in     |

|               |             | e mode<br>LL handshake has                 | s not been sen   | ht.               |                     |                    |                    |

| bit 6         |             | ented: Read as '0                          |                  | it.               |                     |                    |                    |

| bit 5         | -           | -: Resume Interru                          |                  |                   |                     |                    |                    |

| Sit 0         |             | ate is observed on                         |                  | oin for 2.5 us (d | lifferential '1' fo | r low speed, dit   | fferential '0' for |

|               | full spe    |                                            |                  |                   |                     |                    |                    |

|               | 0 = No K-s  | state is observed                          |                  |                   |                     |                    |                    |

| bit 4         | IDLEIF: Idl | e Detect Interrupt                         | bit              |                   |                     |                    |                    |

|               |             | ndition is detected<br>e condition is dete | •                | e state of 3 ms   | or more)            |                    |                    |

| bit 3         |             | e condition is dete                        |                  | unt hit           |                     |                    |                    |

| DIL 3         |             | ssing of the curren                        | -                | -                 | LI1STAT regist      | er for endpoint    | information        |

|               |             | ssing of the curren                        |                  |                   |                     |                    |                    |

|               |             | TAT (clearing this                         |                  |                   |                     | -                  |                    |

| bit 2         |             | rt-of-Frame Toker                          | •                |                   |                     |                    |                    |

|               |             | -of-Frame token is                         | s received by t  | he peripheral c   | or the Start-of-F   | rame threshold     | l is reached by    |

|               | the hos     | st<br>ırt-of-Frame token                   | is received or   | threshold read    | bed                 |                    |                    |

| bit 1         |             | ISB Error Conditio                         |                  |                   | neu                 |                    |                    |

| bit 1         |             | masked error cond                          |                  |                   | states enabled      | in the U1EIE r     | egister can set    |

|               | this bit    |                                            |                  | field, only error |                     |                    | egiotor our cor    |

|               | 0 = No unr  | masked error cond                          | dition has occu  | ırred             |                     |                    |                    |

| bit 0         | URSTIF: U   | SB Reset Interrup                          | ot bit           |                   |                     |                    |                    |

|               |             | JSB Reset has oc                           | curred for at le | east 2.5 μs; Re   | set state must      | be cleared before  | ore this bit can   |

|               |             | sserted<br>B Reset has occu                | urred: individua | al hite can only  | be cleared by       | writing a '1' to t | the hit position   |

|               |             | t of a word write of                       |                  | -                 | -                   | -                  |                    |

|               |             | to write to a single                       |                  |                   |                     |                    |                    |

|               | cleared     | d                                          |                  |                   |                     |                    |                    |

|               |             |                                            |                  |                   |                     |                    |                    |

|               |             | can only be cleare                         |                  |                   |                     |                    |                    |

|               | -           | Using Boolean in                           |                  |                   |                     |                    | uon wiii Cause     |

| R/W-0                              | R/W-0                                                                                                                       | R/W-0                                                                                                                  | R/W-0                                                                                           | R/W-0                                            | R/W-0           | R/W-0    | R/W-0    |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|----------|----------|

| PWCSAMP7                           | PWCSAMP6                                                                                                                    | PWCSAMP5                                                                                                               | PWCSAMP4                                                                                        | PWCSAMP3                                         | PWCSAMP2        | PWCSAMP1 | PWCSAMP0 |

| bit 15                             |                                                                                                                             |                                                                                                                        |                                                                                                 |                                                  |                 |          | bit 8    |

|                                    |                                                                                                                             |                                                                                                                        |                                                                                                 |                                                  |                 |          |          |

| R/W-0                              | R/W-0                                                                                                                       | R/W-0                                                                                                                  | R/W-0                                                                                           | R/W-0                                            | R/W-0           | R/W-0    | R/W-0    |

| PWCSTAB7                           | PWCSTAB6                                                                                                                    | PWCSTAB5                                                                                                               | PWCSTAB4                                                                                        | PWCSTAB3                                         | PWCSTAB2        | PWCSTAB1 | PWCSTAB0 |

| bit 7                              |                                                                                                                             |                                                                                                                        |                                                                                                 |                                                  |                 |          | bit 0    |

|                                    |                                                                                                                             |                                                                                                                        |                                                                                                 |                                                  |                 |          |          |

| Legend:                            |                                                                                                                             |                                                                                                                        |                                                                                                 |                                                  |                 |          |          |

| R = Readable bit W = Writable bit  |                                                                                                                             |                                                                                                                        |                                                                                                 | U = Unimplem                                     | ented bit, read | as '0'   |          |

| -n = Value at POR '1' = Bit is set |                                                                                                                             |                                                                                                                        |                                                                                                 | '0' = Bit is clea                                | nown            |          |          |

| bit 15-8<br>bit 7-0                | 11111111 = S<br>11111110 = S<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ample window is<br>ample window is<br>ample window is<br>o sample windo<br><b>0&gt;:</b> Power Con<br>itability window | s always enable<br>s 254 TPWCCLK<br>s 1 TPWCCLK clo<br>w<br>trol Stability Wi<br>is 255 TPWCCLI | ock period<br>ndow Timer bits<br>< clock periods | WCEN = 0        |          |          |

#### REGISTER 22-5: RTCCON3L: RTCC CONTROL REGISTER 3 (LOW)

Note 1: The sample window always starts when the stability window timer expires, except when its initial value is 00h.

# FIGURE 25-2: EXAMPLE OF BUFFER ADDRESS GENERATION IN PIA MODE (4-WORD BUFFERS PER CHANNEL)

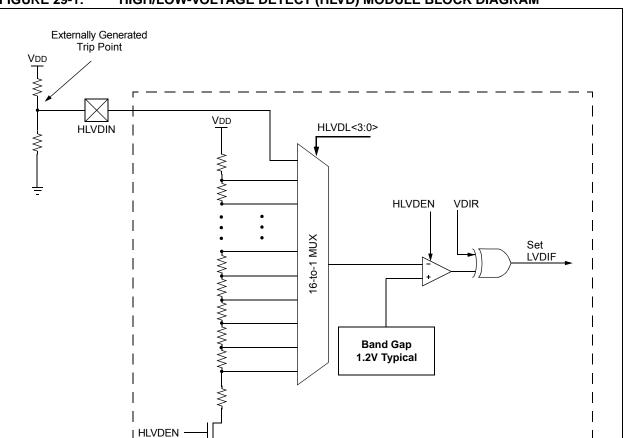

# 29.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the High/Low-Voltage Detect, refer to the "dsPIC33/PIC24 Family Reference Manual", "High-Level Integration with Programmable High/Low-Voltage Detect (HLVD)" (DS39725), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The High/Low-Voltage Detect (HLVD) module is a programmable circuit that allows the user to specify both the device voltage trip point and the direction of change.

An interrupt flag is set if the device experiences an excursion past the trip point in the direction of change. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt. The LVDIF flag may be set during a POR or BOR event. The firmware should clear the flag before the application uses it for the first time, even if the interrupt was disabled.

The HLVD Control register (see Register 29-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device. The HLVDEN bit (HLVDCON<15>) should be cleared when writing data to the HLVDCON register. Once the register is configured, the module is enabled from power-down by setting HLVDEN. The application must wait a minimum of 5  $\mu$ S before clearing the HLVDIF flag and using the module after HLVDEN has been set.

#### FIGURE 29-1: HIGH/LOW-VOLTAGE DETECT (HLVD) MODULE BLOCK DIAGRAM

|  | REGISTER 30-6: | FOSCSEL | CONFIGURATION REGISTER |

|--|----------------|---------|------------------------|

|--|----------------|---------|------------------------|

| U-1      | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 |

|----------|-----|-----|-----|-----|-----|-----|-----|

| —        | —   | —   | —   | —   | —   | —   | —   |

| bit 23 b |     |     |     |     |     |     |     |

| U-1        | U-1 | U-1 | U-1 | U-1 | U-1 | r-0 | r-0 |

|------------|-----|-----|-----|-----|-----|-----|-----|

| —          | —   | —   | —   | —   | —   | —   | —   |

| bit 15 bit |     |     |     |     |     |     |     |

| R/PO-1 | R/PO-1   | R/PO-1   | R/PO-1   | R/PO-1   | R/PO-1 | R/PO-1 | R/PO-1 |

|--------|----------|----------|----------|----------|--------|--------|--------|

| IESO   | PLLMODE3 | PLLMODE2 | PLLMODE1 | PLLMODE0 | FNOSC2 | FNOSC1 | FNOSC0 |

| bit 7  |          |          |          |          |        |        | bit 0  |

| Legend: PO = Program Once bit     |                  | r = Reserved bit                   |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '1' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 23-10 | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9-8   | Reserved: Maintain as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 7     | <ul> <li>IESO: Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Starts up the device with FRC, then automatically switches to the user-selected oscillator when ready</li> <li>0 = Starts up the device with the user-selected oscillator source</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 6-3   | PLLMODE<3:0>: Frequency Multiplier Select bits<br>1111 = No PLL is used (PLLEN bit is unavailable)<br>1110 = 8x PLL is selected<br>1101 = 6x PLL is selected<br>1100 = 4x PLL is selected<br>0111 = 96 MHz USB PLL is selected (Input Frequency = 48 MHz)<br>0110 = 96 MHz USB PLL is selected (Input Frequency = 32 MHz)<br>0101 = 96 MHz USB PLL is selected (Input Frequency = 24 MHz)<br>0100 = 96 MHz USB PLL is selected (Input Frequency = 20 MHz)<br>0011 = 96 MHz USB PLL is selected (Input Frequency = 16 MHz)<br>0010 = 96 MHz USB PLL is selected (Input Frequency = 12 MHz)<br>0010 = 96 MHz USB PLL is selected (Input Frequency = 8 MHz)<br>0001 = 96 MHz USB PLL is selected (Input Frequency = 4 MHz) |

| bit 2-0   | FNOSC<2:0>: Oscillator Selection bits<br>111 = Oscillator with Frequency Divider (OSCFDIV)<br>110 = Digitally Controlled Oscillator (DCO)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Secondary Oscillator (SOSC)<br>011 = Primary Oscillator with PLL (XTPLL, HSPLL, ECPLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with PLL (FRCPLL)<br>000 = Fast RC Oscillator (FRC)                                                                                                                                                                                                                                                                                                              |

$\ensuremath{\textcircled{}^{\odot}}$  2015-2016 Microchip Technology Inc.

#### REGISTER 30-10: FICD CONFIGURATION REGISTER

| U-1                     | U-1                                                                  | U-1              | U-1        | U-1                                                                           | U-1  | U-1    | U-1    |  |  |  |

|-------------------------|----------------------------------------------------------------------|------------------|------------|-------------------------------------------------------------------------------|------|--------|--------|--|--|--|

| _                       |                                                                      | _                | _          | _                                                                             | _    | _      | _      |  |  |  |

| bit 23 bit 23           |                                                                      |                  |            |                                                                               |      |        |        |  |  |  |

|                         |                                                                      |                  |            |                                                                               |      |        | ,      |  |  |  |

| R/PO-1                  | U-1                                                                  | U-1              | U-1        | U-1                                                                           | U-1  | U-1    | U-1    |  |  |  |

| BTSWP                   | —                                                                    | —                | —          | —                                                                             | —    | —      |        |  |  |  |

| bit 15                  | bit 15 bit 8                                                         |                  |            |                                                                               |      |        |        |  |  |  |

|                         |                                                                      |                  |            |                                                                               |      |        |        |  |  |  |

| r-1                     | U-1                                                                  | R/PO-1           | U-1        | U-1                                                                           | U-1  | R/PO-1 | R/PO-1 |  |  |  |

|                         |                                                                      | JTAGEN           | —          |                                                                               |      | ICS1   | ICS0   |  |  |  |

| bit 7                   |                                                                      |                  |            |                                                                               |      |        | bit 0  |  |  |  |

| Logondu                 |                                                                      | PO = Progran     | o Onco hit | r = Reserved                                                                  | hit  |        | ]      |  |  |  |

| Legend:<br>R = Readable | , hit                                                                | W = Writable     |            |                                                                               |      |        |        |  |  |  |

| -n = Value at           |                                                                      | '1' = Bit is set |            | U = Unimplemented bit, read as '1'<br>'0' = Bit is cleared x = Bit is unknown |      |        |        |  |  |  |