Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj512gb610-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                 |                    |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|--------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer | Description        |

| RA0             | _                                   | —                                | 17                               | 17                               | G3                      | G3                      | I/O | DIG/ST          | PORTA Digital I/Os |

| RA1             | _                                   | _                                | 38                               | 38                               | J6                      | J6                      | I/O | DIG/ST          |                    |

| RA2             | _                                   | _                                | 58                               | 58                               | H11                     | H11                     | I/O | DIG/ST          |                    |

| RA3             | _                                   | _                                | 59                               | 59                               | G10                     | G10                     | I/O | DIG/ST          |                    |

| RA4             | _                                   | _                                | 60                               | 60                               | G11                     | G11                     | I/O | DIG/ST          |                    |

| RA5             | _                                   | _                                | 61                               | 61                               | G9                      | G9                      | I/O | DIG/ST          |                    |

| RA6             | _                                   | —                                | 91                               | 91                               | C5                      | C5                      | I/O | DIG/ST          |                    |

| RA7             | _                                   | _                                | 92                               | 92                               | B5                      | B5                      | I/O | DIG/ST          |                    |

| RA9             | _                                   | —                                | 28                               | 28                               | L2                      | L2                      | I/O | DIG/ST          |                    |

| RA10            | _                                   | _                                | 29                               | 29                               | K3                      | K3                      | I/O | DIG/ST          |                    |

| RA14            | _                                   | _                                | 66                               | 66                               | E11                     | E11                     | I/O | DIG/ST          |                    |

| RA15            | _                                   | —                                | 67                               | 67                               | E8                      | E8                      | I/O | DIG/ST          |                    |

| RB0             | 16                                  | 16                               | 25                               | 25                               | K2                      | K2                      | I/O | DIG/ST          | PORTB Digital I/Os |

| RB1             | 15                                  | 15                               | 24                               | 24                               | K1                      | K1                      | I/O | DIG/ST          |                    |

| RB2             | 14                                  | 14                               | 23                               | 23                               | J2                      | J2                      | I/O | DIG/ST          |                    |

| RB3             | 13                                  | 13                               | 22                               | 22                               | J1                      | J1                      | I/O | DIG/ST          |                    |

| RB4             | 12                                  | 12                               | 21                               | 21                               | H2                      | H2                      | I/O | DIG/ST          |                    |

| RB5             | 11                                  | 11                               | 20                               | 20                               | H1                      | H1                      | I/O | DIG/ST          |                    |

| RB6             | 17                                  | 17                               | 26                               | 26                               | L1                      | L1                      | I/O | DIG/ST          |                    |

| RB7             | 18                                  | 18                               | 27                               | 27                               | J3                      | J3                      | I/O | DIG/ST          |                    |

| RB8             | 21                                  | 21                               | 32                               | 32                               | K4                      | K4                      | I/O | DIG/ST          |                    |

| RB9             | 22                                  | 22                               | 33                               | 33                               | L4                      | L4                      | I/O | DIG/ST          |                    |

| RB10            | 23                                  | 23                               | 34                               | 34                               | L5                      | L5                      | I/O | DIG/ST          |                    |

| RB11            | 24                                  | 24                               | 35                               | 35                               | J5                      | J5                      | I/O | DIG/ST          |                    |

| RB12            | 27                                  | 27                               | 41                               | 41                               | J7                      | J7                      | I/O | DIG/ST          |                    |

| RB13            | 28                                  | 28                               | 42                               | 42                               | L7                      | L7                      | I/O | DIG/ST          |                    |

| RB14            | 29                                  | 29                               | 43                               | 43                               | K7                      | K7                      | I/O | DIG/ST          |                    |

| RB15            | 30                                  | 30                               | 44                               | 44                               | L8                      | L8                      | I/O | DIG/ST          |                    |

| RC1             | _                                   | _                                | 6                                | 6                                | D1                      | D1                      | I/O | DIG/ST          | PORTC Digital I/Os |

| RC2             | _                                   | _                                | 7                                | 7                                | E4                      | E4                      | I/O | DIG/ST          |                    |

| RC3             | —                                   | _                                | 8                                | 8                                | E2                      | E2                      | I/O | DIG/ST          |                    |

| RC4             | -                                   | _                                | 9                                | 9                                | E1                      | E1                      | I/O | DIG/ST          |                    |

| RC12            | 39                                  | 39                               | 63                               | 63                               | F9                      | F9                      | I/O | DIG/ST          |                    |

| RC13            | 47                                  | 47                               | 73                               | 73                               | C10                     | C10                     | I/O | DIG/ST          |                    |

| RC14            | 48                                  | 48                               | 74                               | 74                               | B11                     | B11                     | I/O | DIG/ST          |                    |

| RC15            | 40                                  | 40                               | 64                               | 64                               | F11                     | F11                     | I/O | DIG/ST          |                    |

### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated Transceiver

## 4.2 Data Memory Space

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Data Memory with Extended Data Space (EDS)**" (DS39733). The information in this data sheet supersedes the information in the FRM.

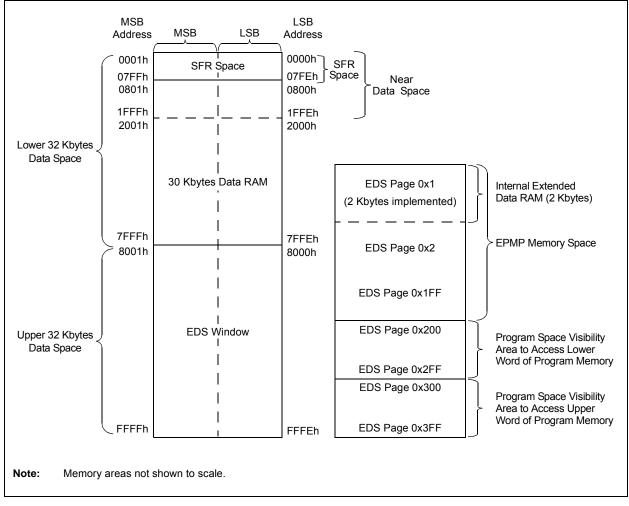

The PIC24F core has a 16-bit wide data memory space, addressable as a single linear range. The Data Space is accessed using two Address Generation Units (AGUs), one each for read and write operations. The Data Space memory map is shown in Figure 4-3.

The 16-bit wide data addresses in the data memory space point to bytes within the Data Space (DS). This gives a DS address range of 32 Kbytes or 16K words. The lower half (0000h to 7FFFh) is used for implemented (on-chip) memory addresses.

The upper half of data memory address space (8000h to FFFFh) is used as a window into the Extended Data Space (EDS). This allows the microcontroller to directly access a greater range of data beyond the standard 16-bit address range. EDS is discussed in detail in **Section 4.2.5 "Extended Data Space (EDS)**".

The lower half of DS is compatible with previous PIC24F microcontrollers without EDS. All PIC24FJ1024GA610/ GB610 family devices implement 30 Kbytes of data RAM in the lower half of DS, from 0800h to 7FFF.

# 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

| File Name       | Address | All Resets | File Name       | Address | All Resets |  |

|-----------------|---------|------------|-----------------|---------|------------|--|

| DMA (CONTINUED) |         |            | DMA (CONTINUED) |         |            |  |

| DMASRC0         | 04D0    | 0000       | DMACNT2         | 04E8    | 0001       |  |

| DMADST0         | 04D2    | 0000       | DMACH3          | 04EA    | 0000       |  |

| DMACNT0         | 04D4    | 0001       | DMAINT3         | 04EC    | 0000       |  |

| DMACH1          | 04D6    | 0000       | DMASRC3         | 04EE    | 0000       |  |

| DMAINT1         | 04D8    | 0000       | DMADST3         | 04F0    | 0000       |  |

| DMASRC1         | 04DA    | 0000       | DMACNT3         | 04F2    | 0001       |  |

| DMADST1         | 04DC    | 0000       | DMACH4          | 04F4    | 0000       |  |

| DMACNT1         | 04DE    | 0001       | DMAINT4         | 04F6    | 0000       |  |

| DMACH2          | 04E0    | 0000       | DMASRC4         | 04F8    | 0000       |  |

| DMAINT2         | 04E2    | 0000       | DMADST4         | 04FA    | 0000       |  |

| DMASRC2         | 04E4    | 0000       | DMACNT4         | 04FC    | 0001       |  |

| DMADST2         | 04E6    | 0000       | DMACH5          | 04FE    | 0000       |  |

# TABLE 4-8: SFR MAP: 0400h BLOCK (CONTINUED)

Legend: — = unimplemented, read as '0'; x = undefined. Reset values are shown in hexadecimal.

| File Name       | Address | All Resets | File Name           | Address | All Resets |  |

|-----------------|---------|------------|---------------------|---------|------------|--|

| DMA (CONTINUED) |         |            | USB OTG (CONTINUED) |         |            |  |

| DMAINT5         | 0500    | 0000       | U1ADDR              | 056E    | 00xx       |  |

| DMASRC5         | 0502    | 0000       | U1BDTP1             | 0570    | 0000       |  |

| DMADST5         | 0504    | 0000       | U1FRML              | 0572    | 0000       |  |

| DMACNT5         | 0506    | 0001       | U1FRMH              | 0574    | 0000       |  |

| DMACH6          | 0508    | 0000       | U1TOK               | 0576    | 0000       |  |

| DMAINT6         | 050A    | 0000       | U1SOF               | 0578    | 0000       |  |

| DMASRC6         | 050C    | 0000       | U1BDTP2             | 057A    | 0000       |  |

| DMADST6         | 050E    | 0000       | U1BDTP3             | 057C    | 0000       |  |

| DMACNT6         | 0510    | 0001       | U1CNFG1             | 057E    | 0000       |  |

| DMACH7          | 0512    | 0000       | U1CNFG2             | 0580    | 0000       |  |

| DMAINT7         | 0514    | 0000       | U1EP0               | 0582    | 0000       |  |

| DMASRC7         | 0516    | 0000       | U1EP1               | 0584    | 0000       |  |

| DMADST7         | 0518    | 0000       | U1EP2               | 0586    | 0000       |  |

| DMACNT7         | 051A    | 0001       | U1EP3               | 0588    | 0000       |  |

| USB OTG         |         |            | U1EP4               | 058A    | 0000       |  |

| U10TGIR         | 0558    | 0000       | U1EP5               | 058C    | 0000       |  |

| U1OTGIE         | 055A    | 0000       | U1EP6               | 058E    | 0000       |  |

| U1OTGSTAT       | 055C    | 0000       | U1EP7               | 0590    | 0000       |  |

| U10TGCON        | 055E    | 0000       | U1EP8               | 0592    | 0000       |  |

| U1PWRC          | 0560    | 00x0       | U1EP9               | 0594    | 0000       |  |

| U1IR            | 0562    | 0000       | U1EP10              | 0596    | 0000       |  |

| U1IE            | 0564    | 0000       | U1EP11              | 0598    | 0000       |  |

| U1EIR           | 0566    | 0000       | U1EP12              | 059A    | 0000       |  |

| U1EIE           | 0568    | 0000       | U1EP13              | 059C    | 0000       |  |

| U1STAT          | 056A    | 0000       | U1EP14              | 059E    | 0000       |  |

| U1CON           | 056C    | 00x0       | U1EP15              | 05A0    | 0000       |  |

### TABLE 4-9:SFR MAP: 0500h BLOCK

**Legend:** — = unimplemented, read as '0'; x = undefined. Reset values are shown in hexadecimal.

| R/W-1        | R-0         | R/W-0                                   | U-0            | U-0              | U-0               | U-0            | R/W-0          |

|--------------|-------------|-----------------------------------------|----------------|------------------|-------------------|----------------|----------------|

| GIE          | DISI        | SWTRAP                                  | —              |                  | _                 |                | AIVTEN         |

| bit 15       | <u>ң</u>    |                                         |                |                  |                   |                | bit 8          |

|              |             |                                         | <b>D</b> 444 0 | <b>D</b> 444 0   | <b>D</b> 444 A    | DAMA           | <b>D</b> 444 0 |

| U-0          | U-0         | U-0                                     | R/W-0          | R/W-0            | R/W-0             | R/W-0          | R/W-0          |

|              |             | —                                       | INT4EP         | INT3EP           | INT2EP            | INT1EP         | INT0EP         |

| bit 7        |             |                                         |                |                  |                   |                | bit (          |

| Legend:      |             |                                         |                |                  |                   |                |                |

| R = Readab   | e bit       | W = Writable                            | bit            | U = Unimplen     | nented bit, read  | l as '0'       |                |

| -n = Value a | POR         | '1' = Bit is set                        |                | '0' = Bit is cle | ared              | x = Bit is unk | nown           |

|              |             |                                         |                |                  |                   |                |                |

| bit 15       |             | Interrupt Enable                        |                |                  |                   |                |                |

|              |             | ts and associate<br>ts are disabled, I  | •              |                  | abled             |                |                |

| bit 14       | •           | Instruction Statu                       | •              |                  |                   |                |                |

|              |             | struction is active                     |                |                  |                   |                |                |

|              | 0 = DISI in | struction is not a                      | ctive          |                  |                   |                |                |

| bit 13       | SWTRAP: S   | Software Trap St                        | atus bit       |                  |                   |                |                |

|              |             | e trap is enabled<br>e trap is disabled |                |                  |                   |                |                |

| bit 12-9     |             | ented: Read as '                        |                |                  |                   |                |                |

| bit 8        | -           | ternate Interrupt                       |                | Enable bit       |                   |                |                |

|              |             | ernate Interrupt \<br>ndard Interrupt \ |                |                  | onfiguration bits | )              |                |

| bit 7-5      | Unimpleme   | ented: Read as '                        | 0'             |                  |                   |                |                |

| bit 4        | INT4EP: Ex  | ternal Interrupt 4                      | Edge Detect    | Polarity Select  | bit               |                |                |

|              |             | t on negative ed<br>t on positive edg   | •              |                  |                   |                |                |

| bit 3        | •           | ternal Interrupt 3                      |                | Polarity Select  | bit               |                |                |

|              |             | t on negative ed                        | -              | ,,               |                   |                |                |

|              |             | t on positive edg                       |                |                  |                   |                |                |

| bit 2        |             | ternal Interrupt 2                      |                | Polarity Select  | bit               |                |                |

|              |             | t on negative edg<br>t on positive edg  |                |                  |                   |                |                |

| bit 1        | INT1EP: Ex  | ternal Interrupt 1                      | Edge Detect    | Polarity Select  | bit               |                |                |

|              |             | t on negative ed<br>t on positive edg   |                |                  |                   |                |                |

| bit 0        | -           | ternal Interrupt (                      |                | Polarity Select  | bit               |                |                |

|              |             | t on negative ed                        | -              |                  | · · · ·           |                |                |

#### REGISTER 8-4: INTCON2: INTERRUPT CONTROL REGISTER 2

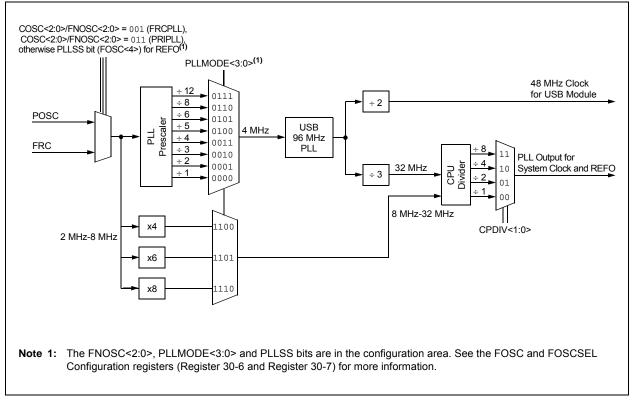

# FIGURE 9-2: PLL BLOCK

# 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. In an application that needs to use more than one peripheral multiplexed on a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of any one of many digital peripherals to any one of these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 11.4.1 AVAILABLE PINS

The PPS feature is used with a range of up to 44 pins, depending on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

PIC24FJ1024GA610/GB610 family devices support a larger number of remappable input/output pins than remappable input only pins. In this device family, there are up to 44 remappable input/output pins, depending on the pin count of the particular device selected. These pins are numbered, RP0 through RP31, and RPI32 through RPI43.

See Table 1-1 for a summary of pinout options in each package offering.

# 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals. PPS is not available for these peripherals:

- I<sup>2</sup>C (input and output)

- Input Change Notifications

- EPMP Signals (input and output)

- Analog (inputs and outputs)

- INT0

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 11.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g., output compare, UART transmit) will take priority over general purpose digital functions on a pin, such as EPMP and port I/O. Specialized digital outputs will take priority over PPS outputs on the same pin. The pin diagrams list peripheral outputs in the order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pinselectable peripheral inputs will never take ownership of a pin. The pin's output buffer will be controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in Digital mode, then the PPS input will operate correctly. If an analog function is enabled on the pin, the PPS input will be disabled.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

# 11.4.3.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral; that is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-12 through Register 11-35). Each register contains one or two sets of 6-bit fields, with each set associated with one of the pin-selectable peripherals. Programming a given peripheral's bit field with an appropriate 6-bit value maps the RPn/RPIn pin with that value to that peripheral. For any given device, the valid range of values for any of the bit fields corresponds to the maximum number of Peripheral Pin Selections supported by the device.

| TABLE TT-3. SELECTABLE INFOT SOUNCES (WAFS INFOT TO TONCTION). | <b>TABLE 11-3</b> : | SELECTABLE INPUT SOURCES | (MAPS INPUT TO FUNCTION) <sup>(1)</sup> |

|----------------------------------------------------------------|---------------------|--------------------------|-----------------------------------------|

|----------------------------------------------------------------|---------------------|--------------------------|-----------------------------------------|

| Input Name                   | Function Name | Register      | Function Mapping<br>Bits |

|------------------------------|---------------|---------------|--------------------------|

| Output Compare Trigger 1     | OCTRIG1       | RPINR0<5:0>   | OCTRIG1R<5:0>            |

| External Interrupt 1         | INT1          | RPINR0<13:8>  | INT1R<5:0>               |

| External Interrupt 2         | INT2          | RPINR1<5:0>   | INT2R<5:0>               |

| External Interrupt 3         | INT3          | RPINR1<13:8>  | INT3R<5:0>               |

| External Interrupt 4         | INT4          | RPINR2<5:0>   | INT4R<5:0>               |

| Output Compare Trigger 2     | OCTRIG2       | RPINR2<13:8>  | OCTRIG2R<5:0>            |

| Timer2 External Clock        | T2CK          | RPINR3<5:0>   | T2CKR<5:0>               |

| Timer3 External Clock        | T3CK          | RPINR3<13:8>  | T3CKR<5:0>               |

| Timer4 External Clock        | T4CK          | RPINR4<5:0>   | T4CKR<5:0>               |

| Timer5 External Clock        | T5CK          | RPINR4<13:8>  | T5CKR<5:0>               |

| Input Capture 1              | IC1           | RPINR7<5:0>   | IC1R<5:0>                |

| Input Capture 2              | IC2           | RPINR7<13:8>  | IC2R<5:0>                |

| Input Capture 3              | IC3           | RPINR8<5:0>   | IC3R<5:0>                |

| Output Compare Fault A       | OCFA          | RPINR11<5:0>  | OCFAR<5:0>               |

| Output Compare Fault B       | OCFB          | RPINR11<13:8> | OCFBR<5:0>               |

| CCP Clock Input A            | TCKIA         | RPINR12<5:0>  | TCKIAR<5:0>              |

| CCP Clock Input B            | TCKIB         | RPINR12<13:8> | TCKIBR<5:0>              |

| UART3 Receive                | U3RX          | RPINR17<13:8> | U3RXR<5:0>               |

| UART1 Receive                | U1RX          | RPINR18<5:0>  | U1RXR<5:0>               |

| UART1 Clear-to-Send          | U1CTS         | RPINR18<13:8> | U1CTSR<5:0>              |

| UART2 Receive                | U2RX          | RPINR19<5:0>  | U2RXR<5:0>               |

| UART2 Clear-to-Send          | U2CTS         | RPINR19<13:8> | U2CTSR<5:0>              |

| SPI1 Data Input              | SDI1          | RPINR20<5:0>  | SDI1R<5:0>               |

| SPI1 Clock Input             | SCK1IN        | RPINR20<13:8> | SCK1R<5:0>               |

| SPI1 Slave Select Input      | SS1IN         | RPINR21<5:0>  | SS1R<5:0>                |

| UART3 Clear-to-Send          | U3CTS         | RPINR21<13:8> | U3CTSR<5:0>              |

| SPI2 Data Input              | SDI2          | RPINR22<5:0>  | SDI2R<5:0>               |

| SPI2 Clock Input             | SCK2IN        | RPINR22<13:8> | SCK2R<5:0>               |

| SPI2 Slave Select Input      | SS2IN         | RPINR23<5:0>  | SS2R<5:0>                |

| Generic Timer External Clock | TxCK          | RPINR23<13:8> | TXCKR<5:0>               |

| CLC Input A                  | CLCINA        | RPINR25<5:0>  | CLCINAR<5:0>             |

| CLC Input B                  | CLCINB        | RPINR25<13:8> | CLCINBR<5:0>             |

| UART4 Receive                | U4RX          | RPINR27<5:0>  | U4RXR<5:0>               |

| UART4 Clear-to-Send          | U4CTS         | RPINR27<13:8> | U4CTSR<5:0>              |

| SPI3 Data Input              | SDI3          | RPINR28<5:0>  | SDI3R<5:0>               |

| SPI3 Clock Input             | SCK3IN        | RPINR28<13:8> | SCK3R<5:0>               |

| SPI3 Slave Select Input      | SS3IN         | RPINR29<5:0>  | SS3R<5:0>                |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger (ST) input buffers.

| R/W-0              | U-0                                  | R/W-0                                        | U-0                   | U-0                        | U-0             | R/W-0                     | R/W-0                  |

|--------------------|--------------------------------------|----------------------------------------------|-----------------------|----------------------------|-----------------|---------------------------|------------------------|

| TON <sup>(2)</sup> | —                                    | TSIDL <sup>(2)</sup>                         |                       | _                          | _               | TECS1 <sup>(2,3)</sup>    | TECS0 <sup>(2,3)</sup> |

| bit 15             |                                      |                                              |                       |                            | <b>I</b>        |                           | bit                    |

|                    |                                      |                                              |                       |                            |                 |                           |                        |

| U-0                | R/W-0                                | R/W-0                                        | R/W-0                 | U-0                        | U-0             | R/W-0                     | U-0                    |

|                    | TGATE <sup>(2)</sup>                 | TCKPS1 <sup>(2)</sup>                        | TCKPS0 <sup>(2)</sup> | —                          | _               | TCS <sup>(2,3)</sup>      | _                      |

| bit 7              |                                      |                                              |                       |                            |                 |                           | bit                    |

| Legend:            |                                      |                                              |                       |                            |                 |                           |                        |

| R = Reada          | able bit                             | W = Writable                                 | bit                   | U = Unimpler               | nented bit, rea | ad as '0'                 |                        |

| -n = Value         | at POR                               | '1' = Bit is set                             |                       | '0' = Bit is cle           | ared            | x = Bit is unkn           | own                    |

|                    |                                      |                                              |                       |                            |                 |                           |                        |

| bit 15             | TON: Timery                          |                                              |                       |                            |                 |                           |                        |

|                    | 1 = Starts 16<br>0 = Stops 16        |                                              |                       |                            |                 |                           |                        |

| bit 14             | •                                    | nted: Read as '                              | o'                    |                            |                 |                           |                        |

| bit 13             | -                                    | ry Stop in Idle N                            |                       |                            |                 |                           |                        |

|                    |                                      | nues module op                               |                       | evice enters Id            | lle mode        |                           |                        |

|                    |                                      | es module opera                              |                       | de                         |                 |                           |                        |

| bit 12-10          | -                                    | nted: Read as '                              |                       |                            |                 | (2.2)                     |                        |

| bit 9-8            |                                      | Timery Extende                               |                       | e Select bits (s           | selected when   | TCS = 1) <sup>(2,3)</sup> |                        |

|                    | 11 = Generic<br>10 = LPRC (          | c timer (TxCK) e                             | external input        |                            |                 |                           |                        |

|                    |                                      | xternal clock inp                            | but                   |                            |                 |                           |                        |

|                    | 00 = SOSC                            |                                              |                       |                            |                 |                           |                        |

| bit 7              | Unimplemer                           | nted: Read as '                              | כ'                    |                            |                 |                           |                        |

| bit 6              | TGATE: Time                          | ery Gated Time                               | Accumulation          | Enable bit <sup>(2)</sup>  |                 |                           |                        |

|                    | When TCS =                           |                                              |                       |                            |                 |                           |                        |

|                    | This bit is ign<br>When TCS =        |                                              |                       |                            |                 |                           |                        |

|                    |                                      | <u>·                                    </u> | n is enabled          |                            |                 |                           |                        |

|                    | 0 = Gated ti                         | me accumulatio                               | n is disabled         |                            |                 |                           |                        |

| bit 5-4            | TCKPS<1:0>                           | Timery Input                                 | Clock Prescale        | Select bits <sup>(2)</sup> |                 |                           |                        |

|                    | 11 = 1:256                           |                                              |                       |                            |                 |                           |                        |

|                    | 10 = 1:64<br>01 = 1:8                |                                              |                       |                            |                 |                           |                        |

|                    | 00 = 1:1                             |                                              |                       |                            |                 |                           |                        |

| bit 3-2            | Unimplemer                           | nted: Read as '                              | כ'                    |                            |                 |                           |                        |

| bit 1              | -                                    | Clock Source S                               |                       |                            |                 |                           |                        |

|                    |                                      | clock from pin,                              | TyCK (on the ri       | ising edge)                |                 |                           |                        |

|                    |                                      | clock (Fosc/2)                               |                       |                            |                 |                           |                        |

| bit 0              | Unimplemer                           | nted: Read as '                              | Ο'                    |                            |                 |                           |                        |

| Note 1:            | Changing the val reset and is not re | •                                            | nile the timer is     | running (TON               | = 1) causes th  | e timer prescale          | counter to             |

|                    | When 32-bit ope operation; all time  | er functions are                             | set through T2        | 2CON and T4C               | ON.             |                           | -                      |

| 3:                 | If TCS = 1 and T<br>available RPn/RF |                                              |                       |                            |                 |                           |                        |

# REGISTER 13-2: TyCON: TIMER3 AND TIMER5 CONTROL REGISTER<sup>(1)</sup>

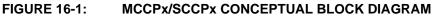

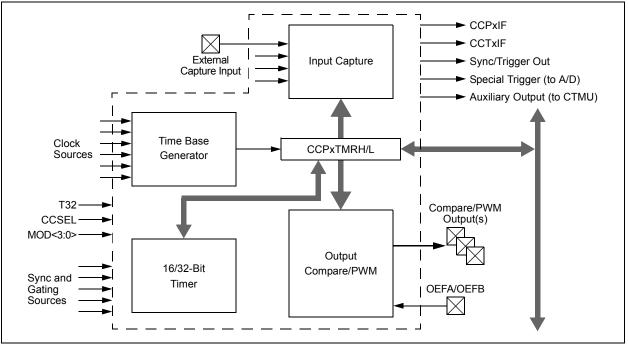

# 16.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the MCCP/SCCP modules, refer to the "dsPIC33/PIC24 Family Reference Manual", "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS33035A), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

PIC24FJ1024GA610/GB610 family devices include several Capture/Compare/PWM/Timer base modules, which provide the functionality of three different peripherals of earlier PIC24F devices. The module can operate in one of three major modes:

- · General Purpose Timer

- Input Capture

- Output Compare/PWM

The module is provided in two different forms, distinguished by the number of PWM outputs that the module can generate. Single Capture/Compare/PWM (SCCPs) output modules provide only one PWM output. Multiple Capture/Compare/PWM (MCCPs) output modules can provide up to six outputs and an extended range of power control features, depending on the pin count of the particular device. All other features of the modules are identical. The SCCPx and MCCPx modules can be operated only in one of the three major modes at any time. The other modes are not available unless the module is reconfigured for the new mode.

A conceptual block diagram for the module is shown in Figure 16-1. All three modules share a time base generator and a common Timer register pair (CCPxTMRH/L); other shared hardware components are added as a particular mode requires.

Each module has a total of 8 control and status registers:

- CCPxCON1L (Register 16-1)

- CCPxCON1H (Register 16-2)

- CCPxCON2L (Register 16-3)

- CCPxCON2H (Register 16-4)

- CCPxCON3L (Register 16-5)

- CCPxCON3H (Register 16-6)

- CCPxSTATL (Register 16-7)

- CCPxSTATH (Register 16-8)

Each module also includes 8 buffer/counter registers that serve as Timer Value registers or data holding buffers:

- CCPxTMRH/CCPxTMRL (Timer High/Low Counters)

- CCPxPRH/CCPxPRL (Timer Period High/Low)

- CCPxRA (Primary Output Compare Data Buffer)

- CCPxRB (Secondary Output Compare Data Buffer)

- CCPxBUFH/CCPxBUFL (Input Capture High/Low Buffers)

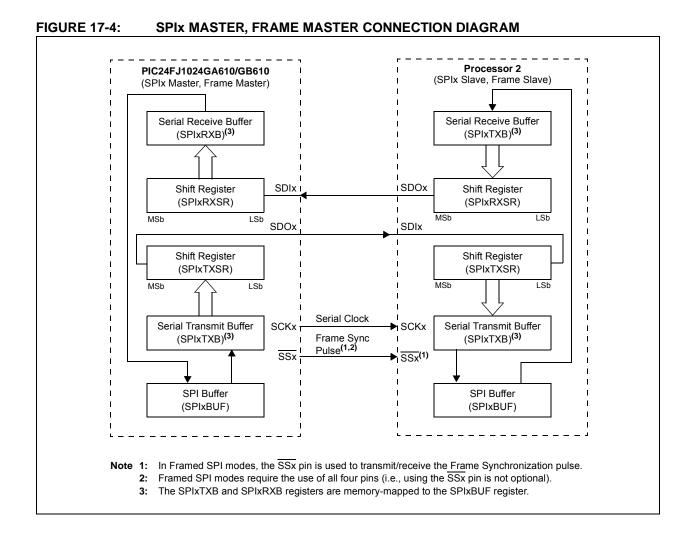

# 17.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC24FJ1024GA610/GB610 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Serial Peripheral Interface (SPI) with Audio Codec Support" (DS70005136), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces. All devices in the PIC24FJ1024GA610/GB610 family include three SPI modules.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through a FIFO buffer. The FIFO level depends on the configured mode.

Variable length data can be transmitted and received from 2 to 32 bits.

| Note: | Do not perform Read-Modify-Write opera-      |

|-------|----------------------------------------------|

|       | tions (such as bit-oriented instructions) on |

|       | the SPIxBUF register in either Standard or   |

|       | Enhanced Buffer mode.                        |

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The module also supports Audio modes. Four different Audio modes are available.

- I<sup>2</sup>S mode

- Left Justified

- Right Justified

- PCM/DSP

In each of these modes, the serial clock is free-running and audio data is always transferred.

If an audio protocol data transfer takes place between two devices, then usually one device is the master and the other is the slave. However, audio data can be transferred between two slaves. Because the audio protocols require free-running clocks, the master can be a third party controller. In either case, the master generates two free-running clocks: SCKx and LRC (Left, Right Channel Clock/SSx/FSYNC). The SPI serial interface consists of four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

The SPI module has the ability to generate three interrupts reflecting the events that occur during the data communication. The following types of interrupts can be generated:

- 1. Receive interrupts are signalled by SPIxRXIF. This event occurs when:

- RX watermark interrupt

- SPIROV = 1

- SPIRBF = 1

- SPIRBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 2. Transmit interrupts are signalled by SPIxTXIF. This event occurs when:

- TX watermark interrupt

- SPITUR = 1

- SPITBF = 1

- SPITBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 3. General interrupts are signalled by SPIxIF. This event occurs when

- FRMERR = 1

- SPIBUSY = 1

- SRMT = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

A block diagram of the module in Enhanced Buffer mode is shown in Figure 17-1.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1, SPI2 or SPI3. Special Function Registers will follow a similar notation. For example, SPIxCON1 and SPIxCON2 refer to the control registers for any of the three SPI modules.

| R/W-0    | R/W-0                 | R/W-0    | R/W-0    | R/W-0, HC | R/W-0                | R-0, HSC  | R-1, HSC |

|----------|-----------------------|----------|----------|-----------|----------------------|-----------|----------|

| UTXISEL1 | UTXINV <sup>(1)</sup> | UTXISEL0 | URXEN    | UTXBRK    | UTXEN <sup>(2)</sup> | UTXBF     | TRMT     |

| bit 15   |                       |          |          |           |                      |           | bit 8    |

|          |                       |          |          |           |                      |           |          |

|          |                       |          |          |           |                      |           |          |

| R/W-0    | R/W-0                 | R/W-0    | R-1, HSC | R-0, HSC  | R-0, HSC             | R/C-0, HS | R-0, HSC |

#### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| Legend:                    | C = Clearable bit         | HSC = Hardware Settable   | /Clearable bit     |

|----------------------------|---------------------------|---------------------------|--------------------|

| R = Readable bit           | W = Writable bit          | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR          | '1' = Bit is set          | '0' = Bit is cleared      | x = Bit is unknown |

| HS = Hardware Settable bit | HC = Hardware Clearable b | it                        |                    |

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

11 = Reserved; do not use

bit 7

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx IrDA<sup>®</sup> Encoder Transmit Polarity Inversion bit<sup>(1)</sup>

|         | IREN = 0:                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = UxTX Idle state is '0'                                                                                                                       |

|         | 0 = UxTX Idle state is '1'                                                                                                                       |

|         | IREN = 1:                                                                                                                                        |

|         | 1 = UxTX Idle state is '1'                                                                                                                       |

|         | 0 = UxTX Idle state is '0'                                                                                                                       |

| bit 12  | URXEN: UARTx Receive Enable bit                                                                                                                  |

|         | 1 = Receive is enabled, UxRX pin is controlled by UARTx                                                                                          |

|         | 0 = Receive is disabled, UxRX pin is controlled by the port                                                                                      |

| bit 11  | UTXBRK: UARTx Transmit Break bit                                                                                                                 |

|         | 1 = Sends Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit;<br>cleared by hardware upon completion |

|         | 0 = Sync Break transmission is disabled or completed                                                                                             |

| bit 10  | UTXEN: UARTx Transmit Enable bit <sup>(2)</sup>                                                                                                  |

|         | 1 = Transmit is enabled, UxTX pin is controlled by UARTx                                                                                         |

|         | 0 = Transmit is disabled, any pending transmission is aborted and the buffer is reset; UxTX pin is<br>controlled by the port                     |

| bit 9   | UTXBF: UARTx Transmit Buffer Full Status bit (read-only)                                                                                         |

|         | 1 = Transmit buffer is full                                                                                                                      |

|         | 0 = Transmit buffer is not full, at least one more character can be written                                                                      |

| bit 8   | TRMT: Transmit Shift Register Empty bit (read-only)                                                                                              |

|         | 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)                                          |

|         | 0 = Transmit Shift Register is not empty, a transmission is in progress or queued                                                                |

| Note 1: | The value of this bit only affects the transmit properties of the module when the $IrDA^{\textcircled{B}}$ encoder is enabled (IREN = 1).        |

2: If UARTEN = 1, the peripheral inputs and outputs must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

© 2015-2016 Microchip Technology Inc.

bit 0

### 20.5.3 SEND A FULL-SPEED BULK DATA TRANSFER TO A TARGET DEVICE

- Follow the procedure described in Section 20.5.1 "Enable Host Mode and Discover a Connected Device" and Section 20.5.2 "Complete a Control Transaction to a Connected Device" to discover and configure a device.

- To enable transmit and receive transfers with handshaking enabled, write 1Dh to U1EP0. If the target device is a low-speed device, also set the LSPD (U1EP0<7>) bit. If you want the hardware to automatically retry indefinitely if the target device asserts a NAK on the transfer, clear the Retry Disable bit, RETRYDIS (U1EP0<6>).

- 3. Set up the BD for the current (even or odd) TX EP0 to transfer up to 64 bytes.

- 4. Set the USB device address of the target device in the address register (U1ADDR<6:0>).

- 5. Write an OUT token to the desired endpoint to U1TOK. This triggers the module's transmit state machines to begin transmitting the token and the data.

- 6. Wait for the Token Complete Interrupt Flag, TRNIF. This indicates that the BD has been released back to the microprocessor and the transfer has completed. If the Retry Disable bit (RETRYDIS) is set, the handshake (ACK, NAK, STALL or ERROR (0Fh)) is returned in the BD PID field. If a STALL interrupt occurs, the pending packet must be dequeued and the error condition in the target device cleared. If a detach interrupt occurs (SE0 for more than 2.5 µs), then the target has detached (U1IR<0> is set).

- 7. Once the Token Complete Interrupt Flag occurs (TRNIF is set), the BD can be examined and the next data packet queued by returning to Step 2.

- **Note:** USB speed, transceiver and pull-ups should only be configured during the module setup phase. It is not recommended to change these settings while the module is enabled.

# 20.6 OTG Operation

#### 20.6.1 SESSION REQUEST PROTOCOL (SRP)

An OTG A-device may decide to power down the VBUS supply when it is not using the USB link through the Session Request Protocol (SRP). SRP can only be initiated at full speed. Software may do this by configuring a GPIO pin to disable an external power transistor, or voltage regulator enable signal, which controls the VBUS supply. When the VBUS supply is powered down, the A-device is said to have ended a USB session.

An OTG A-device or embedded host may repower the VBUS supply at any time (initiate a new session). An OTG B-device may also request that the OTG A-device repower the VBUS supply (initiate a new session). This is accomplished via Session Request Protocol (SRP).

Prior to requesting a new session, the B-device must first check that the previous session has definitely ended. To do this, the B-device must check for two conditions:

- 1. VBUS supply is below the session valid voltage.

- 2. Both D+ and D- have been low for at least 2 ms.

The B-device will be notified of Condition 1 by the SESENDIF (U1OTGIR<2>) interrupt. Software will have to manually check for Condition 2.

| Note: | When the A-device powers down the            |

|-------|----------------------------------------------|

|       | VBUS supply, the B-device must discon-       |

|       | nect its pull-up resistor from power. If the |

|       | device is self-powered, it can do this by    |

|       | clearing DPPULUP (U1OTGCON<7>) and           |

|       | DMPULUP (U1OTGCON<6>).                       |

The B-device may aid in achieving Condition 1 by discharging the VBUS supply through a resistor. Software may do this by setting VBUSDIS (U1OTGCON<0>).

After these initial conditions are met, the B-device may begin requesting the new session. The B-device begins by pulsing the D+ data line. Software should do this by setting DPPULUP (U10TGCON<7>). The data line should be held high for 5 to 10 ms.

The B-device then proceeds by pulsing the VBUS supply. Software should do this by setting PUVBUS (U1CNFG2<4>). When an A-device detects SRP signaling (either via the ATTACHIF (U1IR<6>) interrupt or via the SESVDIF (U1OTGIR<3>) interrupt), the A-device must restore the VBUS supply by properly configuring the general purpose I/O port pin controlling the external power source.

The B-device should not monitor the state of the VBUS supply while performing VBUS supply pulsing. When the B-device does detect that the VBUS supply has been restored (via the SESVDIF (U1OTGIR<3>) interrupt), the B-device must reconnect to the USB link by pulling up D+ or D- (via the DPPULUP or DMPULUP bit).

The A-device must complete the SRP by driving USB Reset signaling.

# REGISTER 20-16: U1IR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0           | U-0                    | U-0                                                                                                                                                          | U-0              | U-0               | U-0               | U-0               | U-0              |  |  |  |

|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-------------------|-------------------|------------------|--|--|--|

| —             | —                      |                                                                                                                                                              | —                |                   | —                 |                   |                  |  |  |  |

| bit 15        |                        |                                                                                                                                                              |                  |                   |                   |                   | bit 8            |  |  |  |

|               |                        |                                                                                                                                                              |                  |                   |                   |                   |                  |  |  |  |

| R/K-0, HS     | U-0                    | R/K-0, HS                                                                                                                                                    | R/K-0, HS        | R/K-0, HS         | R/K-0, HS         | R/K-0, HS         | R/K-0, HS        |  |  |  |

| STALLIF       | —                      | RESUMEIF                                                                                                                                                     | IDLEIF           | TRNIF             | SOFIF             | UERRIF            | URSTIF           |  |  |  |

| bit 7         |                        |                                                                                                                                                              |                  |                   |                   |                   | bit 0            |  |  |  |

|               |                        |                                                                                                                                                              |                  |                   |                   |                   |                  |  |  |  |

| Legend:       |                        | U = Unimplem                                                                                                                                                 | ented bit, read  | d as '0'          |                   |                   |                  |  |  |  |

| R = Readable  |                        | K = Write '1' to                                                                                                                                             | Clear bit        | HS = Hardwa       | re Settable bit   |                   |                  |  |  |  |

| -n = Value at | POR                    | '1' = Bit is set                                                                                                                                             |                  | '0' = Bit is clea | ared              | x = Bit is unkr   | nown             |  |  |  |

|               |                        |                                                                                                                                                              |                  |                   |                   |                   |                  |  |  |  |

| bit 15-8      | Unimplem               | ented: Read as '0                                                                                                                                            | ,                |                   |                   |                   |                  |  |  |  |

| bit 7         | STALLIF: S             | STALL Handshake                                                                                                                                              | e Interrupt bit  |                   |                   |                   |                  |  |  |  |

|               |                        | LL handshake wa                                                                                                                                              | s sent by the p  | peripheral durin  | g the handshal    | ke phase of the   | transaction in   |  |  |  |

|               |                        | e mode<br>LL handshake has                                                                                                                                   | s not been sen   | .t                |                   |                   |                  |  |  |  |

| bit 6         |                        | ented: Read as '0                                                                                                                                            |                  | it i              |                   |                   |                  |  |  |  |

| bit 5         | -                      |                                                                                                                                                              |                  |                   |                   |                   |                  |  |  |  |

| bit o         |                        | <b>RESUMEIF:</b> Resume Interrupt bit<br>1 = A K-state is observed on the D+ or D- pin for 2.5 $\mu$ s (differential '1' for low speed, differential '0' for |                  |                   |                   |                   |                  |  |  |  |

|               | full spe               |                                                                                                                                                              |                  | μο (α             |                   | now opeca, an     |                  |  |  |  |

|               | 0 = No K-s             | state is observed                                                                                                                                            |                  |                   |                   |                   |                  |  |  |  |

| bit 4         | IDLEIF: Idl            | DLEIF: Idle Detect Interrupt bit                                                                                                                             |                  |                   |                   |                   |                  |  |  |  |

|               |                        | ndition is detected<br>e condition is dete                                                                                                                   | •                | e state of 3 ms   | or more)          |                   |                  |  |  |  |

| bit 3         |                        | ken Processing Co                                                                                                                                            |                  | upt bit           |                   |                   |                  |  |  |  |

| Sito          |                        | ssing of the curren                                                                                                                                          | -                | -                 | U1STAT regist     | er for endpoint   | information      |  |  |  |

|               | 0 = Proces             | ssing of the curren                                                                                                                                          | t token is not   | complete; clear   | the U1STAT r      |                   |                  |  |  |  |

| bit 2         | SOFIF: Sta             | irt-of-Frame Toker                                                                                                                                           | Interrupt bit    |                   | -                 |                   |                  |  |  |  |

|               | 1 = A Start            | t-of-Frame token is                                                                                                                                          | s received by t  | he peripheral o   | or the Start-of-F | rame threshold    | l is reached by  |  |  |  |

|               | the ho                 |                                                                                                                                                              |                  |                   |                   |                   |                  |  |  |  |

|               |                        | irt-of-Frame token                                                                                                                                           |                  |                   | hed               |                   |                  |  |  |  |

| bit 1         |                        | SB Error Conditio                                                                                                                                            | -                |                   |                   |                   |                  |  |  |  |

|               | 1 = An unr<br>this bit | masked error cond                                                                                                                                            | ition has occu   | rred; only error  | states enabled    | in the U1EIE r    | egister can set  |  |  |  |

|               | 0 = No unr             | masked error cond                                                                                                                                            | lition has occu  | irred             |                   |                   |                  |  |  |  |

| bit 0         | URSTIF: U              | SB Reset Interrup                                                                                                                                            | ot bit           |                   |                   |                   |                  |  |  |  |

|               | 1 = Valid U            | JSB Reset has oc                                                                                                                                             | curred for at le | east 2.5 μs; Re   | set state must l  | be cleared before | ore this bit can |  |  |  |

|               |                        | sserted                                                                                                                                                      |                  |                   |                   |                   |                  |  |  |  |

|               | as par                 | B Reset has occu<br>t of a word write of<br>to write to a single<br>d                                                                                        | peration on the  | e entire register | . Using Boolea    | n instructions o  | r bitwise oper-  |  |  |  |

|               |                        |                                                                                                                                                              |                  |                   |                   |                   |                  |  |  |  |

| Note: In      | dividual bits o        | can only be cleare                                                                                                                                           | d by writing a ' | 1' to the bit pos | ition as part of  | a word write op   | eration on the   |  |  |  |

| er            | ntire register.        | Using Boolean in:                                                                                                                                            | structions or b  | itwise operation  |                   |                   |                  |  |  |  |

| U-0               | U-0                                                                               | U-0                                                                             | U-0             | U-0               | U-0              | U-0             | U-0   |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|

| _                 | —                                                                                 | _                                                                               | _               | _                 | —                | —               | _     |  |  |  |  |  |

| bit 15            |                                                                                   | ·                                                                               |                 |                   |                  |                 | bit   |  |  |  |  |  |

|                   |                                                                                   |                                                                                 |                 |                   |                  |                 |       |  |  |  |  |  |

| R/W-0             | U-0                                                                               | R/W-0                                                                           | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |

| BTSEE             | —                                                                                 | DMAEE                                                                           | BTOEE           | DFN8EE            | CRC16EE          | CRC5EE          | PIDEE |  |  |  |  |  |

|                   |                                                                                   |                                                                                 |                 |                   |                  | EOFEE           |       |  |  |  |  |  |

| bit 7             |                                                                                   |                                                                                 |                 |                   |                  |                 | bit   |  |  |  |  |  |

|                   |                                                                                   |                                                                                 |                 |                   |                  |                 |       |  |  |  |  |  |

| Legend:           |                                                                                   |                                                                                 |                 |                   |                  |                 |       |  |  |  |  |  |

| R = Readat        |                                                                                   | W = Writable                                                                    |                 | •                 | nented bit, read |                 |       |  |  |  |  |  |

| -n = Value a      | at POR                                                                            | '1' = Bit is set                                                                |                 | '0' = Bit is clea | ared             | x = Bit is unkn | own   |  |  |  |  |  |