Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj512gb610t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                 |                           |  |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|---------------------------|--|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer | Description               |  |

| IOCD0           | 46                                  | 46                               | 72                               | 72                               | D9                      | D9                      | Ι   | ST              | PORTD Interrupt-on-Change |  |

| IOCD1           | 49                                  | 49                               | 76                               | 76                               | A11                     | A11                     | Ι   | ST              |                           |  |

| IOCD2           | 50                                  | 50                               | 77                               | 77                               | A10                     | A10                     | Ι   | ST              |                           |  |

| IOCD3           | 51                                  | 51                               | 78                               | 78                               | B9                      | B9                      | Ι   | ST              |                           |  |

| IOCD4           | 52                                  | 52                               | 81                               | 81                               | C8                      | C8                      | Ι   | ST              |                           |  |

| IOCD5           | 53                                  | 53                               | 82                               | 82                               | B8                      | B8                      | Ι   | ST              |                           |  |

| IOCD6           | 54                                  | 54                               | 83                               | 83                               | D7                      | D7                      | Ι   | ST              |                           |  |

| IOCD7           | 55                                  | 55                               | 84                               | 84                               | C7                      | C7                      | Ι   | ST              |                           |  |

| IOCD8           | 42                                  | 42                               | 68                               | 68                               | E9                      | E9                      | Ι   | ST              |                           |  |

| IOCD9           | 43                                  | 43                               | 69                               | 69                               | E10                     | E10                     | Ι   | ST              |                           |  |

| IOCD10          | 44                                  | 44                               | 70                               | 70                               | D11                     | D11                     | Ι   | ST              |                           |  |

| IOCD11          | 45                                  | 45                               | 71                               | 71                               | C11                     | C11                     | Ι   | ST              |                           |  |

| IOCD12          | _                                   | _                                | 79                               | 79                               | A9                      | A9                      | Ι   | ST              |                           |  |

| IOCD13          | _                                   | —                                | 80                               | 80                               | D8                      | D8                      | Ι   | ST              |                           |  |

| IOCD14          | —                                   | —                                | 47                               | 47                               | L9                      | L9                      | Ι   | ST              |                           |  |

| IOCD15          | _                                   | _                                | 48                               | 48                               | K9                      | K9                      | Ι   | ST              |                           |  |

| IOCE0           | 60                                  | 60                               | 93                               | 93                               | A4                      | A4                      | Ι   | ST              | PORTE Interrupt-on-Change |  |

| IOCE1           | 61                                  | 61                               | 94                               | 94                               | B4                      | B4                      | Ι   | ST              |                           |  |

| IOCE2           | 62                                  | 62                               | 98                               | 98                               | B3                      | B3                      | Ι   | ST              |                           |  |

| IOCE3           | 63                                  | 63                               | 99                               | 99                               | A2                      | A2                      | Ι   | ST              |                           |  |

| IOCE4           | 64                                  | 64                               | 100                              | 100                              | A1                      | A1                      | Ι   | ST              |                           |  |

| IOCE5           | 1                                   | 1                                | 3                                | 3                                | D3                      | D3                      | Ι   | ST              |                           |  |

| IOCE6           | 2                                   | 2                                | 4                                | 4                                | C1                      | C1                      | Ι   | ST              |                           |  |

| IOCE7           | 3                                   | 3                                | 5                                | 5                                | D2                      | D2                      | Ι   | ST              |                           |  |

| IOCE8           |                                     | _                                | 18                               | 18                               | G1                      | G1                      | Ι   | ST              |                           |  |

| IOCE9           | _                                   | _                                | 19                               | 19                               | G2                      | G2                      | Ι   | ST              |                           |  |

#### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer

$I^2C = I^2C/SMBus$  input buffer XCVR = Dedicated Transceiver

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                 |                                                                                |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|--------------------------------------------------------------------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer | Description                                                                    |

| OCM2A           | 6                                   | 6                                | 12                               | 12                               | F2                      | F2                      | 0   | DIG             | MCCP2 Outputs                                                                  |

| OCM2B           | 8                                   | 8                                | 14                               | 14                               | F3                      | F3                      | 0   | DIG             |                                                                                |

| OCM2C           | _                                   | —                                | 7                                | 7                                | E4                      | E4                      | 0   | DIG             |                                                                                |

| OCM2D           | _                                   | _                                | 8                                | 8                                | E2                      | E2                      | 0   | DIG             |                                                                                |

| OCM2E           | _                                   | —                                | 96                               | 96                               | C3                      | C3                      | 0   | DIG             |                                                                                |

| OCM2F           | _                                   | _                                | 97                               | 97                               | A3                      | A3                      | 0   | DIG             |                                                                                |

| ОСМЗА           | 11                                  | 11                               | 20                               | 20                               | H1                      | H1                      | 0   | DIG             | MCCP3 Outputs                                                                  |

| OCM3B           | 12                                  | 12                               | 21                               | 21                               | H2                      | H2                      | 0   | DIG             |                                                                                |

| OCM3C           | _                                   | _                                | 9                                | 9                                | E1                      | E1                      | 0   | DIG             |                                                                                |

| OCM3D           | _                                   | _                                | 17                               | 17                               | G3                      | G3                      | 0   | DIG             |                                                                                |

| OCM3E           | _                                   | _                                | 79                               | 79                               | A9                      | A9                      | 0   | DIG             |                                                                                |

| OCM3F           | _                                   | _                                | 80                               | 80                               | D8                      | D8                      | 0   | DIG             |                                                                                |

| OSCI            | 39                                  | 39                               | 63                               | 63                               | F9                      | F9                      | I   | ANA/<br>ST      | Main Oscillator Input Connection                                               |

| OSCO            | 40                                  | 40                               | 64                               | 64                               | F11                     | F11                     | 0   | ANA             | Main Oscillator Output<br>Connection                                           |

| PGEC1           | 15                                  | 15                               | 24                               | 24                               | K1                      | K1                      | I   | ST              | ICSP™ Programming Clock                                                        |

| PGEC2           | 17                                  | 17                               | 26                               | 26                               | L1                      | L1                      | Ι   | ST              |                                                                                |

| PGEC3           | 11                                  | 11                               | 20                               | 20                               | H1                      | H1                      | I   | ST              |                                                                                |

| PGED1           | 16                                  | 16                               | 25                               | 25                               | K2                      | K2                      | I/O | DIG/ST          | ICSP Programming Data                                                          |

| PGED2           | 18                                  | 18                               | 27                               | 27                               | J3                      | J3                      | I/O | DIG/ST          |                                                                                |

| PGED3           | 12                                  | 12                               | 21                               | 21                               | H2                      | H2                      | I/O | DIG/ST          |                                                                                |

| PMA0/<br>PMALL  | 30                                  | 30                               | 44                               | 44                               | L8                      | L8                      | I/O | DIG/<br>ST/TTL  | Parallel Master Port Address<0>/<br>Address Latch Low                          |

| PMA1/<br>PMALH  | 29                                  | 29                               | 43                               | 43                               | K7                      | K7                      | I/O | DIG/<br>ST/TTL  | Parallel Master Port Address<1>/<br>Address Latch High                         |

| PMA14/<br>PMCS1 | 45                                  | 45                               | 71                               | 71                               | C11                     | C11                     | I/O | DIG/<br>ST/TTL  | Parallel Master Port Address<14>/<br>Slave Chip Select/Chip Select 1<br>Strobe |

| PMA15/<br>PMCS2 | 44                                  | 44                               | 70                               | 70                               | D11                     | D11                     | I/O | DIG/<br>ST/TTL  | Parallel Master Port Address<15>/<br>Chip Select 2 Strobe                      |

| PMA6            | 16                                  | 16                               | 29                               | 29                               | K3                      | K3                      | 0   | DIG             | Parallel Master Port Address                                                   |

| PMA7            | 22                                  | 22                               | 28                               | 28                               | L2                      | L2                      | 0   | DIG             |                                                                                |

#### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

XCVR = Dedicated Transceiver

|                 |                                     | Pin N                            | umber/Gri                        | d Locator                        |                         |                         |     |                 |                        |

|-----------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|-------------------------|-------------------------|-----|-----------------|------------------------|

| Pin<br>Function | GA606<br>64-Pin<br>QFN/TQFP/<br>QFP | GB606<br>64-Pin QFN/<br>TQFP/QFP | GA610<br>100-Pin<br>TQFP/<br>QFP | GB610<br>100-Pin<br>TQFP/<br>QFP | GA612<br>121-Pin<br>BGA | GB612<br>121-Pin<br>BGA | I/O | Input<br>Buffer | Description            |

| RP0             | 16                                  | 16                               | 25                               | 25                               | K2                      | K2                      | I/O | DIG/ST          | Remappable Peripherals |

| RP1             | 15                                  | 15                               | 24                               | 24                               | K1                      | K1                      | I/O | DIG/ST          | (input or output)      |

| RP2             | 42                                  | 42                               | 68                               | 68                               | E9                      | E9                      | I/O | DIG/ST          |                        |

| RP3             | 44                                  | 44                               | 70                               | 70                               | D11                     | D11                     | I/O | DIG/ST          |                        |

| RP4             | 43                                  | 43                               | 69                               | 69                               | E10                     | E10                     | I/O | DIG/ST          |                        |

| RP5             | _                                   | —                                | 48                               | 48                               | K9                      | K9                      | I/O | DIG/ST          |                        |

| RP6             | 17                                  | 17                               | 26                               | 26                               | L1                      | L1                      | I/O | DIG/ST          |                        |

| RP7             | 18                                  | 18                               | 27                               | 27                               | J3                      | J3                      | I/O | DIG/ST          |                        |

| RP8             | 21                                  | 21                               | 32                               | 32                               | K4                      | K4                      | I/O | DIG/ST          |                        |

| RP9             | 22                                  | 22                               | 33                               | 33                               | L4                      | L4                      | I/O | DIG/ST          |                        |

| RP10            | 31                                  | 31                               | 49                               | 49                               | L10                     | L10                     | I/O | DIG/ST          |                        |

| RP11            | 46                                  | 46                               | 72                               | 72                               | D9                      | D9                      | I/O | DIG/ST          |                        |

| RP12            | 45                                  | 45                               | 71                               | 71                               | C11                     | C11                     | I/O | DIG/ST          |                        |

| RP13            | 14                                  | 14                               | 23                               | 23                               | J2                      | J2                      | I/O | DIG/ST          |                        |

| RP14            | 29                                  | 29                               | 43                               | 43                               | K7                      | K7                      | I/O | DIG/ST          |                        |

| RP15            | _                                   | _                                | 53                               | 53                               | J10                     | J10                     | I/O | DIG/ST          |                        |

| RP16            | 33                                  | 33                               | 51                               | 51                               | K10                     | K10                     | I/O | DIG/ST          |                        |

| RP17            | 32                                  | 32                               | 50                               | 50                               | L11                     | L11                     | I/O | DIG/ST          |                        |

| RP18            | 11                                  | 11                               | 20                               | 20                               | H1                      | H1                      | I/O | DIG/ST          |                        |

| RP19            | 6                                   | 6                                | 12                               | 12                               | F2                      | F2                      | I/O | DIG/ST          |                        |

| RP20            | 53                                  | 53                               | 82                               | 82                               | B8                      | B8                      | I/O | DIG/ST          |                        |

| RP21            | 4                                   | 4                                | 10                               | 10                               | E3                      | E3                      | I/O | DIG/ST          |                        |

| RP22            | 51                                  | 51                               | 78                               | 78                               | B9                      | B9                      | I/O | DIG/ST          |                        |

| RP23            | 50                                  | 50                               | 77                               | 77                               | A10                     | A10                     | I/O | DIG/ST          |                        |

| RP24            | 49                                  | 49                               | 76                               | 76                               | A11                     | A11                     | I/O | DIG/ST          |                        |

| RP25            | 52                                  | 52                               | 81                               | 81                               | C8                      | C8                      | I/O | DIG/ST          |                        |

| RP26            | 5                                   | 5                                | 11                               | 11                               | F4                      | F4                      | I/O | DIG/ST          |                        |

| RP27            | 8                                   | 8                                | 14                               | 14                               | F3                      | F3                      | I/O | DIG/ST          |                        |

| RP28            | 12                                  | 12                               | 21                               | 21                               | H2                      | H2                      | I/O | DIG/ST          |                        |

| RP29            | 30                                  | 30                               | 44                               | 44                               | L8                      | L8                      | I/O | DIG/ST          |                        |

| RP30            | 34                                  | _                                | 52                               | 52                               | K11                     | K11                     | I/O | DIG/ST          |                        |

| RP31            | _                                   | —                                | 39                               | 39                               | L6                      | L6                      | I/O | DIG/ST          |                        |

#### TABLE 1-3: PIC24FJ1024GA610/GB610 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL input buffer ANA = Analog level input/output DIG = Digital input/output ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

I<sup>2</sup>C = I<sup>2</sup>C/SMBus input buffer XCVR = Dedicated Transceiver

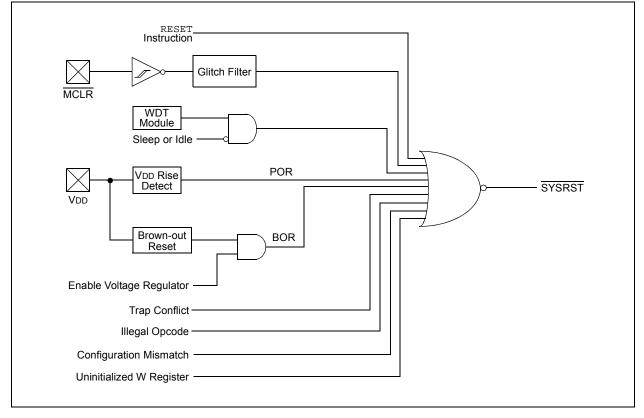

# 7.0 RESETS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Reset" (DS39712), which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Opcode Reset

- UWR: Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 7-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Note: Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 7-1). A POR will clear all bits, except for the BOR and POR (RCON<1:0>) bits, which are set. The user may set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software will not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register values after a device Reset will be meaningful.

#### FIGURE 7-1: RESET SYSTEM BLOCK DIAGRAM

© 2015-2016 Microchip Technology Inc.

| Oscillator Mode                                   | Oscillator Source | FNOSC<2:0> | Notes   |  |  |  |  |  |  |

|---------------------------------------------------|-------------------|------------|---------|--|--|--|--|--|--|

| Oscillator with Frequency Division (OSCFDIV)      | Internal/External | 111        | 1, 2, 3 |  |  |  |  |  |  |

| Digitally Controlled Oscillator (DCO)             | Internal          | 110        | 3       |  |  |  |  |  |  |

| Low-Power RC Oscillator (LPRC)                    | Internal          | 101        | 3       |  |  |  |  |  |  |

| Secondary (Timer1) Oscillator (SOSC)              | Secondary         | 100        | 3       |  |  |  |  |  |  |

| Primary Oscillator (XT, HS or EC) with PLL Module | Primary           | 011        | 4       |  |  |  |  |  |  |

| Primary Oscillator (XT, HS or EC)                 | Primary           | 010        | 4       |  |  |  |  |  |  |

| Fast RC Oscillator with PLL Module (FRCPLL)       | Internal          | 3          |         |  |  |  |  |  |  |

| Fast RC Oscillator (FRC)                          | Internal          | 000        | 3       |  |  |  |  |  |  |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

**Note 1:** The input oscillator to the OSCFDIV Clock mode is determined by the RCDIV<2:0> (CLKDIV<10:8) bits. At POR, the default value selects the FRC module.

- **2:** This is the default oscillator mode for an unprogrammed (erased) device.

- 3: OSCO pin function is determined by the OSCIOFCN Configuration bit.

- 4: The POSCMD<1:0> Configuration bits select the oscillator driver mode (XT, HS or EC).

### 9.3 Control Registers

The operation of the oscillator is controlled by five Special Function Registers:

- OSCCON

- CLKDIV

- OSCTUN

- OSCDIV

- OSCFDIV

In addition, two registers are used to control the DCO:

- DCOCON

- DCOTUN

The OSCCON register (Register 9-1) is the main control register for the oscillator. It controls clock source switching and allows the monitoring of clock sources. OSCCON is protected by a write lock to prevent inadvertent clock switches. See **Section 9.4 "Clock Switching Operation**" for more information. The CLKDIV register (Register 9-2) controls the features associated with Doze mode, as well as the postscalers for the OSCFDIV Clock mode and the PLL module.

The OSCTUN register (Register 9-3) allows the user to fine-tune the FRC Oscillator over a range of approximately  $\pm 1.5\%$ . It also controls the FRC self-tuning features described in **Section 9.5 "FRC Active Clock Tuning"**.

The OSCDIV and OSCFDIV registers provide control for the system Oscillator Frequency Divider.

#### 9.3.1 DCO OVERVIEW

The DCO (Digitally Controlled Oscillator) is a lowpower alternative to the FRC. It can generate a wider selection of operating frequencies and can be trimmed to correct process variations if an exact frequency is required. However, the DCO is not designed for use with USB applications and cannot meet USB timing restrictions.

| U-0                                                                                 | U-0                                                                                                | U-0                                                      | U-0           | U-0              | R/W-0            | R/W-0           | R/W-0 |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------|------------------|------------------|-----------------|-------|--|--|--|

| _                                                                                   | _                                                                                                  | _                                                        | _             | _                | CMPMD            | RTCCMD          | PMPMD |  |  |  |

| bit 15                                                                              |                                                                                                    |                                                          |               |                  |                  |                 | bit   |  |  |  |

|                                                                                     |                                                                                                    |                                                          |               |                  |                  |                 |       |  |  |  |

| R/W-0                                                                               | U-0                                                                                                | U-0                                                      | U-0           | R/W-0            | R/W-0            | R/W-0           | U-0   |  |  |  |

| CRCMD                                                                               | —                                                                                                  | —                                                        |               | U3MD             | I2C3MD           | I2C2MD          | _     |  |  |  |

| bit 7                                                                               |                                                                                                    | •<br>•                                                   |               |                  |                  |                 | bit   |  |  |  |

| <u> </u>                                                                            |                                                                                                    |                                                          |               |                  |                  |                 |       |  |  |  |

| Legend:                                                                             | la hit                                                                                             | $\Lambda I = \Lambda I = 1$                              | L:4           |                  | anted bit was    |                 |       |  |  |  |

| R = Readab                                                                          |                                                                                                    | W = Writable                                             |               | •                | nented bit, read |                 |       |  |  |  |

| -n = Value a                                                                        | t POR                                                                                              | '1' = Bit is set                                         |               | '0' = Bit is cle | ared             | x = Bit is unkn | iown  |  |  |  |

| bit 15-11                                                                           | Unimplemen                                                                                         | ted: Read as '                                           | ٥'            |                  |                  |                 |       |  |  |  |

| bit 10                                                                              | -                                                                                                  |                                                          |               | le hit           |                  |                 |       |  |  |  |

| bit 10 <b>CMPMD:</b> Triple Comparator Module Disable bit<br>1 = Module is disabled |                                                                                                    |                                                          |               |                  |                  |                 |       |  |  |  |

|                                                                                     | 0 = Module power and clock sources are enabled                                                     |                                                          |               |                  |                  |                 |       |  |  |  |

| bit 9                                                                               |                                                                                                    | TCC Module Di                                            |               |                  |                  |                 |       |  |  |  |

|                                                                                     | 1 = Module is disabled                                                                             |                                                          |               |                  |                  |                 |       |  |  |  |

|                                                                                     | 0 = Module p                                                                                       | power and cloc                                           | k sources are | enabled          |                  |                 |       |  |  |  |

| bit 8                                                                               | PMPMD: Enl                                                                                         | nanced Parallel                                          | Master Port D | Disable bit      |                  |                 |       |  |  |  |

|                                                                                     | <ul> <li>1 = Module is disabled</li> <li>0 = Module power and clock sources are enabled</li> </ul> |                                                          |               |                  |                  |                 |       |  |  |  |

|                                                                                     |                                                                                                    |                                                          |               | enabled          |                  |                 |       |  |  |  |

| bit 7                                                                               |                                                                                                    | C Module Disa                                            | ble bit       |                  |                  |                 |       |  |  |  |

|                                                                                     | <ol> <li>1 = Module is disabled</li> <li>0 = Module power and clock sources are enabled</li> </ol> |                                                          |               |                  |                  |                 |       |  |  |  |

| bit 6-4                                                                             |                                                                                                    | nted: Read as '                                          |               |                  |                  |                 |       |  |  |  |

| bit 3                                                                               | -                                                                                                  |                                                          |               |                  |                  |                 |       |  |  |  |

|                                                                                     |                                                                                                    | U3MD: UART3 Module Disable bit<br>1 = Module is disabled |               |                  |                  |                 |       |  |  |  |

|                                                                                     |                                                                                                    | power and cloc                                           | k sources are | enabled          |                  |                 |       |  |  |  |

| bit 2                                                                               | 12C3MD: 12C                                                                                        | 3 Module Disal                                           | ole bit       |                  |                  |                 |       |  |  |  |

|                                                                                     | 1 = Module is disabled                                                                             |                                                          |               |                  |                  |                 |       |  |  |  |

|                                                                                     | 0 = Module p                                                                                       | power and cloc                                           | k sources are | enabled          |                  |                 |       |  |  |  |

| bit 1                                                                               |                                                                                                    | 2 Module Disal                                           | ole bit       |                  |                  |                 |       |  |  |  |

|                                                                                     | 1 = Module i                                                                                       |                                                          |               | o a o b l o d    |                  |                 |       |  |  |  |

| 1.1.0                                                                               |                                                                                                    | oower and cloc                                           |               | enabled          |                  |                 |       |  |  |  |

| bit 0                                                                               | Unimplemen                                                                                         | nted: Read as '                                          | 0             |                  |                  |                 |       |  |  |  |

####

#### REGISTER 11-3: ANSC: PORTC ANALOG FUNCTION SELECTION REGISTER

| U-0                              | R/W-1         | R/W-1                                                                                                                                                        | U-0                  | U-0                  | U-0      | U-0                | U-0   |  |  |

|----------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------|--------------------|-------|--|--|

|                                  | ANSC          | <14:13>                                                                                                                                                      |                      | —                    |          | —                  | —     |  |  |

| bit 15                           |               |                                                                                                                                                              |                      |                      |          |                    | bit 8 |  |  |

|                                  |               |                                                                                                                                                              |                      |                      |          |                    |       |  |  |

| U-0                              | U-0           | U-0                                                                                                                                                          | R/W-1                | U-0                  | U-0      | U-0                | U-0   |  |  |

| —                                | —             | —                                                                                                                                                            | ANSC4 <sup>(1)</sup> | —                    |          | —                  | —     |  |  |

| bit 7                            |               |                                                                                                                                                              |                      |                      |          |                    | bit 0 |  |  |

|                                  |               |                                                                                                                                                              |                      |                      |          |                    |       |  |  |

| Legend:                          |               |                                                                                                                                                              |                      |                      |          |                    |       |  |  |

| R = Readable bit W = Writable bi |               | bit                                                                                                                                                          | U = Unimplem         | nented bit, read     | l as '0' |                    |       |  |  |

| -n = Value a                     | at POR        | '1' = Bit is se                                                                                                                                              | t                    | '0' = Bit is clea    | ared     | x = Bit is unknown |       |  |  |

|                                  |               |                                                                                                                                                              |                      |                      |          |                    |       |  |  |

| bit 15                           | Unimpleme     | nted: Read as '                                                                                                                                              | 0'                   |                      |          |                    |       |  |  |

| bit 14-13                        | ANSC<14:1     | 3>: PORTC An                                                                                                                                                 | alog Function S      | Selection bits       |          |                    |       |  |  |

|                                  | 1 = Pin is co | nfigured in Ana                                                                                                                                              | log mode; I/O p      | ort read is disa     | bled     |                    |       |  |  |

|                                  | 0 = Pin is co | nfigured in Digi                                                                                                                                             | tal mode; I/O p      | ort read is enab     | oled     |                    |       |  |  |

| bit 12-5                         | Unimpleme     | nted: Read as '                                                                                                                                              | 0'                   |                      |          |                    |       |  |  |

| bit 4                            | ANSC4: PO     | RTC Analog Fu                                                                                                                                                | nction Selectio      | n bit <sup>(1)</sup> |          |                    |       |  |  |

|                                  |               | <ul> <li>1 = Pin is configured in Analog mode; I/O port read is disabled</li> <li>0 = Pin is configured in Digital mode; I/O port read is enabled</li> </ul> |                      |                      |          |                    |       |  |  |

| bit 3-0                          | Unimpleme     | Unimplemented: Read as '0'                                                                                                                                   |                      |                      |          |                    |       |  |  |

- bit 3-0 Unimplemented: Read as '0'

- Note 1: ANSC4 is not available on 64-pin devices.

#### REGISTER 11-4: ANSD: PORTD ANALOG FUNCTION SELECTION REGISTER

| U-0    | U-0 | r-1 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-1 | R/W-1  | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|--------|-----|-----|-----|-----|-----|-------|

| ANSE  | )<7:6> | —   | —   | —   | —   | —   | —     |

| bit 7 |        |     |     |     |     |     | bit 0 |

| Legend:           | r = Reserved bit |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

| bit 13    | Reserved: Read as '1'      |

bit 12-8 Unimplemented: Read as '0'

- bit 7-6 ANSD<7:6>: PORTD Analog Function Selection bits

- 1 = Pin is configured in Analog mode; I/O port read is disabled

- 0 = Pin is configured in Digital mode; I/O port read is enabled

bit 5-0 Unimplemented: Read as '0'

#### 11.4.6 PERIPHERAL PIN SELECT REGISTERS

The PIC24FJ1024GA610/GB610 family of devices implements a total of 40 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (24)

- Output Remappable Peripheral Registers (16)

Note: Input and Output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 11.4.4.1 "Control Register Lock" for a specific command sequence.

#### REGISTER 11-12: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | INT1R5 | INT1R4 | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1     | R/W-1     | R/W-1     | R/W-1     | R/W-1     | R/W-1     |

|-------|-----|-----------|-----------|-----------|-----------|-----------|-----------|

| —     | —   | OCTRIG1R5 | OCTRIG1R4 | OCTRIG1R3 | OCTRIG1R2 | OCTRIG1R1 | OCTRIG1R0 |

| bit 7 |     |           |           |           |           |           | bit 0     |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-14 **Unimplemented:** Read as '0'

bit 7-6 Unimplemented: Read as '0'

bit 5-0 OCTRIG1R<5:0>: Assign Output Compare Trigger 1 to Corresponding RPn or RPIn Pin bits

#### REGISTER 11-13: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0                            | U-0        | R/W-1            | R/W-1  | R/W-1                              | R/W-1         | R/W-1              | R/W-1  |  |

|--------------------------------|------------|------------------|--------|------------------------------------|---------------|--------------------|--------|--|

| _                              | —          | INT3R5           | INT3R4 | INT3R3                             | INT3R2        | INT3R1             | INT3R0 |  |

| bit 15                         |            |                  |        |                                    |               |                    | bit 8  |  |

| U-0                            | U-0        | R/W-1            | R/W-1  | R/W-1                              | R/W-1         | R/W-1              | R/W-1  |  |

| _                              | _          | INT2R5           | INT2R4 | INT2R3                             | INT2R2        | INT2R1             | INT2R0 |  |

| bit 7                          |            |                  |        |                                    |               |                    | bit 0  |  |

| Legend:                        |            |                  |        |                                    |               |                    |        |  |

| R = Readable                   | e bit      | W = Writable     | bit    | U = Unimplemented bit, read as '0' |               |                    |        |  |

| -n = Value at POR '1' = Bit is |            | '1' = Bit is set |        | '0' = Bit is clea                  | ared          | x = Bit is unknown |        |  |

| bit 15-14                      | Unimplemer | ited: Read as 'o | )'     |                                    |               |                    |        |  |

| bit 13-8                       | -          |                  |        | NT3) to Corres                     | oonding RPn o | r RPIn Pin bits    |        |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 INT2R<5:0>: Assign External Interrupt 2 (INT2) to Corresponding RPn or RPIn Pin bits

#### REGISTER 11-24: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15

| U-0     | U-0 | U-0          | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|--------------|-----|-----|-----|-----|-------|

| —       | —   | —            | —   | —   | —   | —   | —     |

| bit 15  |     |              |     |     |     |     | bit 8 |

|         |     |              |     |     |     |     |       |

| U-0     | U-0 | r-1          | r-1 | r-1 | r-1 | r-1 | r-1   |

| —       | —   | —            | —   | —   | _   | —   | _     |

| bit 7   |     |              |     |     |     |     | bit 0 |

|         |     |              |     |     |     |     |       |

| Legend: |     | r = Reserved | bit |     |     |     |       |

| Legenu.           | I – Reserved bit |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **Reserved**: Maintain as '1'

#### REGISTER 11-25: RPINR17: PERIPHERAL PIN SELECT INPUT REGISTER 17

| U-0           | U-0   | R/W-1            | R/W-1  | R/W-1                                   | R/W-1  | R/W-1  | R/W-1  |

|---------------|-------|------------------|--------|-----------------------------------------|--------|--------|--------|

| —             | —     | U3RXR5           | U3RXR4 | U3RXR3                                  | U3RXR2 | U3RXR1 | U3RXR0 |

| bit 15        |       |                  |        |                                         |        |        | bit 8  |

|               |       |                  |        |                                         |        |        |        |

| U-0           | U-0   | U-0              | U-0    | U-0                                     | U-0    | U-0    | U-0    |

|               | —     | —                | —      | —                                       | —      | —      | —      |

| bit 7         |       |                  |        |                                         |        |        | bit 0  |

|               |       |                  |        |                                         |        |        |        |

| Legend:       |       |                  |        |                                         |        |        |        |

| R = Readable  | e bit | W = Writable     | bit    | U = Unimplemented bit, read as '0'      |        |        |        |

| -n = Value at | POR   | '1' = Bit is set |        | '0' = Bit is cleared x = Bit is unknown |        |        | nown   |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U3RXR<5:0>: Assign UART3 Receive (U3RX) to Corresponding RPn or RPIn Pin bits

bit 7-0 Unimplemented: Read as '0'

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP29R5 | RP29R4 | RP29R3 | RP29R2 | RP29R1 | RP29R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP28R5 | RP28R4 | RP28R3 | RP28R2 | RP28R1 | RP28R0 |

| h 14 7 |     |        |        |        |        |        | hit O  |

| bit 7  |     |        |        |        |        |        | bit 0  |

#### REGISTER 11-50: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------|

| bit 13-8  | RP29R<5:0>: RP29 Output Pin Mapping bits                                                              |

|           | Peripheral Output Number n is assigned to pin, RP29 (see Table 11-4 for peripheral function numbers). |

| bit 7-6   | Unimplemented: Read as '0'                                                                            |

| bit 5-0   | RP28R<5:0>: RP28 Output Pin Mapping bits                                                              |

|           | Peripheral Output Number n is assigned to pin, RP28 (see Table 11-4 for peripheral function numbers). |

#### REGISTER 11-51: RPOR15: PERIPHERAL PIN SELECT OUTPUT REGISTER 15

| U-0    | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | RP31R5 <sup>(1)</sup> | RP31R4 <sup>(1)</sup> | RP31R3 <sup>(1)</sup> | RP31R2 <sup>(1)</sup> | RP31R1 <sup>(1)</sup> | RP31R0 <sup>(1)</sup> |

| bit 15 |     |                       |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _     | —   | RP30R5 <sup>(2)</sup> | RP30R4 <sup>(2)</sup> | RP30R3 <sup>(2)</sup> | RP30R2 <sup>(2)</sup> | RP30R1 <sup>(2)</sup> | RP30R0 <sup>(2)</sup> |

| bit 7 |     |                       |                       |                       |                       |                       | bit 0                 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP31R<5:0>:** RP31 Output Pin Mapping bits<sup>(1)</sup>

Peripheral Output Number n is assigned to pin, RP31 (see Table 11-4 for peripheral function numbers).bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP30R<5:0>:** RP30 Output Pin Mapping bits<sup>(2)</sup> Peripheral Output Number n is assigned to pin, RP30 (see Table 11-4 for peripheral function numbers).

Note 1: These pins are not available in 64-pin devices.

2: These pins are not available on the PIC24FJXXXGB606.

#### REGISTER 17-4: SPIx STATL: SPIx STATUS REGISTER LOW

| U-0    | U-0 | U-0 | R/C-0, HS | R-0, HSC | U-0 | U-0 | R-0, HSC              |

|--------|-----|-----|-----------|----------|-----|-----|-----------------------|

| —      | —   | —   | FRMERR    | SPIBUSY  | —   | —   | SPITUR <sup>(1)</sup> |

| bit 15 |     |     |           |          |     |     | bit 8                 |

| R-0, HSC | R/C-0, HS | R-1, HSC | U-0 | R-1, HSC | U-0 | R-0, HSC | R-0, HSC |

|----------|-----------|----------|-----|----------|-----|----------|----------|

| SRMT     | SPIROV    | SPIRBE   | —   | SPITBE   | _   | SPITBF   | SPIRBF   |

| bit 7    |           |          |     |          |     |          | bit 0    |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit         | x = Bit is unknown                    |  |  |

|-------------------|-------------------|------------------------------------|---------------------------------------|--|--|

| R = Readable bit  | W = Writable bit  | '0' = Bit is cleared               | HSC = Hardware Settable/Clearable bit |  |  |

| -n = Value at POR | '1' = Bit is set  | U = Unimplemented bit, read as '0' |                                       |  |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                                                                                                                     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12    | FRMERR: SPIx Frame Error Status bit                                                                                                                                                            |

|           | <ul><li>1 = Frame error is detected</li><li>0 = No frame error is detected</li></ul>                                                                                                           |

| bit 11    | SPIBUSY: SPIx Activity Status bit                                                                                                                                                              |

|           | <ul><li>1 = Module is currently busy with some transactions</li><li>0 = No ongoing transactions (at time of read)</li></ul>                                                                    |

| bit 10-9  | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 8     | SPITUR: SPIx Transmit Underrun Status bit <sup>(1)</sup>                                                                                                                                       |

|           | <ul> <li>1 = Transmit buffer has encountered a Transmit Underrun condition</li> <li>0 = Transmit buffer does not have a Transmit Underrun condition</li> </ul>                                 |

| bit 7     | SRMT: Shift Register Empty Status bit                                                                                                                                                          |

|           | <ul> <li>1 = No current or pending transactions (i.e., neither SPIxTXB or SPIxTXSR contains data to transmit)</li> <li>0 = Current or pending transactions</li> </ul>                          |

| bit 6     | SPIROV: SPIx Receive Overflow Status bit                                                                                                                                                       |

|           | <ul> <li>1 = A new byte/half-word/word has been completely received when the SPIxRXB is full</li> <li>0 = No overflow</li> </ul>                                                               |

| bit 5     | SPIRBE: SPIx RX Buffer Empty Status bit                                                                                                                                                        |

|           | 1 = RX buffer is empty<br>0 = RX buffer is not empty                                                                                                                                           |

|           | <u>Standard Buffer Mode:</u><br>Automatically set in hardware when SPIxBUF is read from, reading SPIxRXB. Automatically cleared in hardware when SPIx transfers data from SPIxRXSR to SPIxRXB. |

|           | Enhanced Buffer Mode:<br>Indicates RXELM<5:0> = 6'b000000.                                                                                                                                     |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 3     | SPITBE: SPIx Transmit Buffer Empty Status bit                                                                                                                                                  |

|           | 1 = SPIxTXB is empty<br>0 = SPIxTXB is not empty                                                                                                                                               |

|           | <u>Standard Buffer Mode:</u><br>Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxTXSR. Automatically cleared in hardware when SPIxBUF is written, loading SPIxTXB.   |

|           | Enhanced Buffer Mode:<br>Indicates TXELM<5:0> = 6'b000000.                                                                                                                                     |

|           |                                                                                                                                                                                                |

**Note 1:** SPITUR is cleared when SPIEN = 0. When IGNTUR = 1, SPITUR provides dynamic status of the Transmit Underrun condition, but does not stop RX/TX operation and does not need to be cleared by software.

# PIC24FJ1024GA610/GB610 FAMILY

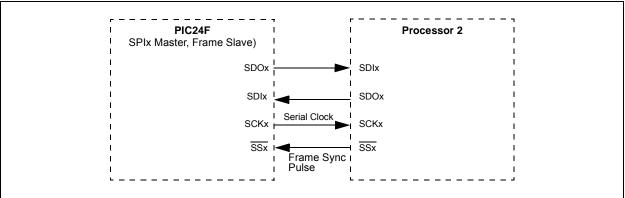

#### FIGURE 17-5: SPIx MASTER, FRAME SLAVE CONNECTION DIAGRAM

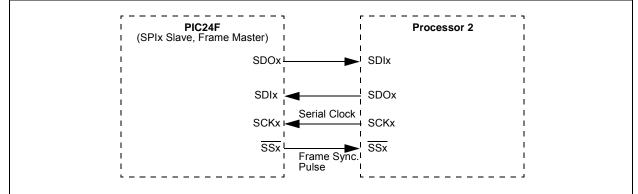

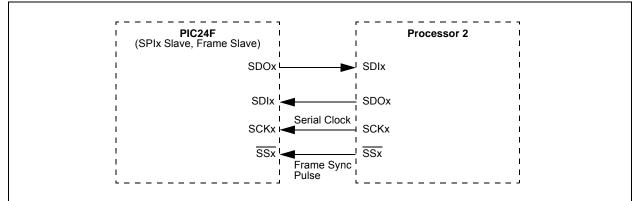

#### FIGURE 17-7: SPIx SLAVE, FRAME SLAVE CONNECTION DIAGRAM

#### EQUATION 17-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED

$Baud Rate = \frac{FPB}{(2 * (SPIxBRG + 1))}$  Where: FPB is the Peripheral Bus Clock Frequency.

| U-0          | U-0                                                                                                                                                                                                | U-0                                                                                                | U-0                         | U-0                          | U-0             | U-0             | U-0         |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------|------------------------------|-----------------|-----------------|-------------|--|--|--|--|

| _            | _                                                                                                                                                                                                  |                                                                                                    |                             | —                            | _               | _               | _           |  |  |  |  |

| bit 15       |                                                                                                                                                                                                    |                                                                                                    |                             |                              |                 |                 | bita        |  |  |  |  |

| U-0          | R/W-0                                                                                                                                                                                              | R/W-0                                                                                              | R/W-0                       | R/W-0                        | R/W-0           | R/W-0           | R/W-0       |  |  |  |  |

| _            | PCIE                                                                                                                                                                                               | SCIE                                                                                               | BOEN                        | SDAHT <sup>(1)</sup>         | SBCDE           | AHEN            | DHEN        |  |  |  |  |

| bit 7        |                                                                                                                                                                                                    |                                                                                                    |                             |                              |                 |                 | bit         |  |  |  |  |

| Legend:      |                                                                                                                                                                                                    |                                                                                                    |                             |                              |                 |                 |             |  |  |  |  |

| R = Readab   | le bit                                                                                                                                                                                             | W = Writable                                                                                       | bit                         | U = Unimplem                 | ented bit, read | as '0'          |             |  |  |  |  |

| -n = Value a | It POR                                                                                                                                                                                             | '1' = Bit is set                                                                                   |                             | '0' = Bit is clea            |                 | x = Bit is unkn | own         |  |  |  |  |

|              |                                                                                                                                                                                                    |                                                                                                    |                             |                              |                 |                 |             |  |  |  |  |