Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 50MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-LQFP                                                                   |

| Supplier Device Package    | 48-LQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc11c22fbd48-301 |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

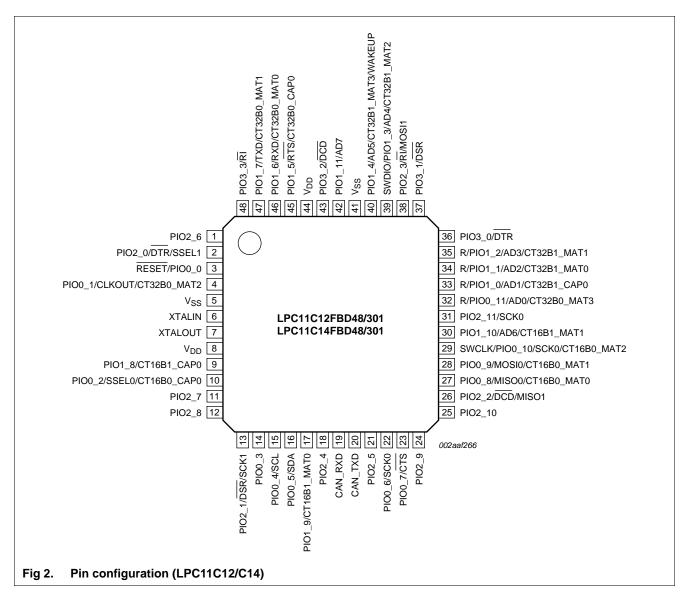

# 6. Pinning information

### 6.1 Pinning

### 32-bit ARM Cortex-M0 microcontroller

| Symbol          | Pin           | Start<br>logic<br>inputs | Туре | Reset<br>state<br>[1] | Description                                                                                                       |

|-----------------|---------------|--------------------------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------|

| PIO3_0/DTR      | 36 <u>[3]</u> | no                       | I/O  | I; PU                 | PIO3_0 — General purpose digital input/output pin.                                                                |

|                 |               |                          | 0    | -                     | <b>DTR</b> — Data Terminal Ready output for UART.                                                                 |

| PIO3_1/DSR      | 37 <u>[3]</u> | no                       | I/O  | I; PU                 | PIO3_1 — General purpose digital input/output pin.                                                                |

|                 |               |                          | I    | -                     | <b>DSR</b> — Data Set Ready input for UART.                                                                       |

| PIO3_2/DCD      | 43 <u>[3]</u> | no                       | I/O  | I; PU                 | PIO3_2 — General purpose digital input/output pin.                                                                |

|                 |               |                          | I    |                       | DCD — Data Carrier Detect input for UART.                                                                         |

| PIO3_3/RI       | 48 <u>[3]</u> | no                       | I/O  | I; PU                 | PIO3_3 — General purpose digital input/output pin.                                                                |

|                 |               |                          | I    | -                     | <b>RI</b> — Ring Indicator input for UART.                                                                        |

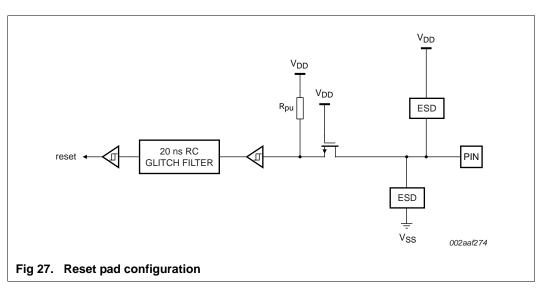

| CAN_RXD         | 19 <u>[6]</u> | no                       | I    | I; IA                 | CAN_RXD — C_CAN receive data input.                                                                               |

| CAN_TXD         | 20 <u>[6]</u> | no                       | 0    | I; IA                 | CAN_TXD — C_CAN transmit data output.                                                                             |

| V <sub>DD</sub> | 8; 44         | -                        | I    | -                     | Supply voltage to the internal regulator, the external rail, and the ADC. Also used as the ADC reference voltage. |

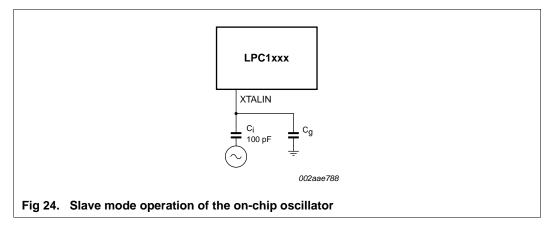

| XTALIN          | 6 <u>[7]</u>  | -                        | I    | -                     | Input to the oscillator circuit and internal clock generator circuits.<br>Input voltage must not exceed 1.8 V.    |

| XTALOUT         | 7 <u>[7]</u>  | -                        | 0    | -                     | Output from the oscillator amplifier.                                                                             |

| V <sub>SS</sub> | 5; 41         | -                        | I    | -                     | Ground.                                                                                                           |

### Table 3. LPC11C12/C14 pin description table

[1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up enabled (pins pulled up to full V<sub>DD</sub> level); IA = inactive, no pull-up/down enabled.

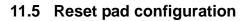

[2] 5 V tolerant pad. RESET functionality is not available in Deep power-down mode. Use the WAKEUP pin to reset the chip and wake up from Deep power-down mode. An external pull-up resistor is required on this pin for the Deep power-down mode. See Figure 27 for the reset pad configuration.

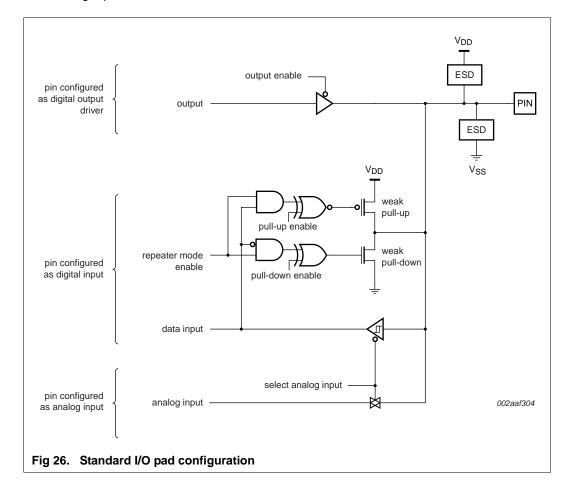

[3] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors and configurable hysteresis (see Figure 26).

[4]  $I^2C$ -bus pads compliant with the  $I^2C$ -bus specification for  $I^2C$  standard mode and  $I^2C$  Fast-mode Plus.

[5] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see Figure 26).

[6] 5 V tolerant digital I/O pad without pull-up/pull-down resistors.

[7] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating.

| Symbol            | Pin          | Start<br>logic<br>inputs | Туре | Reset<br>state<br>[1] | Description                                                                                                                                                                                                                                        |

|-------------------|--------------|--------------------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_0 to PIO0_11 |              |                          |      |                       | <b>Port 0</b> — Port 0 is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 pins depends on the function selected through the IOCONFIG register block.                                       |

| RESET/PIO0_0      | 3 <u>[2]</u> | yes                      | I    | I; PU                 | <b>RESET</b> — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. |

|                   |              |                          | I/O  | -                     | <b>PIO0_0</b> — General purpose digital input/output pin with 10 ns glitch filter.                                                                                                                                                                 |

# 7. Functional description

# 7.1 ARM Cortex-M0 processor

The ARM Cortex-M0 is a general purpose, 32-bit microprocessor, which offers high performance and very low power consumption.

# 7.2 On-chip flash program memory

The LPC11Cx2/Cx4 contain 32 kB (LPC11C14/C24) or 16 kB (LPC11C12/C22) of on-chip flash program memory.

# 7.3 On-chip SRAM

The LPC11Cx2/Cx4 contain a total of 8 kB on-chip static RAM data memory.

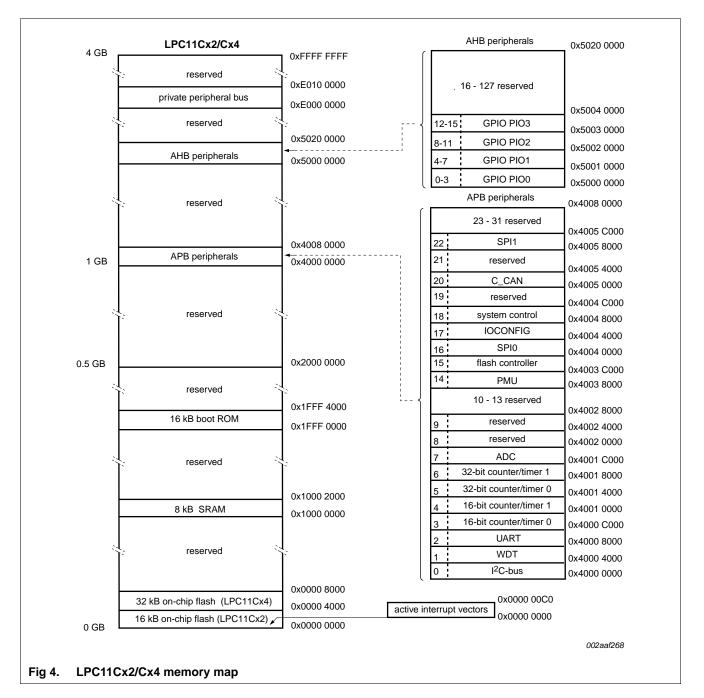

# 7.4 Memory map

The LPC11Cx2/Cx4 incorporates several distinct memory regions, shown in the following figures. <u>Figure 4</u> shows the overall map of the entire address space from the user program viewpoint following reset. The interrupt vector area supports address remapping.

The AHB peripheral area is 2 megabyte in size, and is divided to allow for up to 128 peripherals. The APB peripheral area is 512 kB in size and is divided to allow for up to 32 peripherals. Each peripheral of either type is allocated 16 kilobytes of space. This allows simplifying the address decoding for each peripheral.

### 32-bit ARM Cortex-M0 microcontroller

## 7.5 Nested Vectored Interrupt Controller (NVIC)

The Nested Vectored Interrupt Controller (NVIC) is an integral part of the Cortex-M0. The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

### 7.5.1 Features

- Controls system exceptions and peripheral interrupts.

- In the LPC11Cx2/Cx4, the NVIC supports 32 vectored interrupts including 13 inputs to the start logic from individual GPIO pins.

LPC11CX2\_CX4

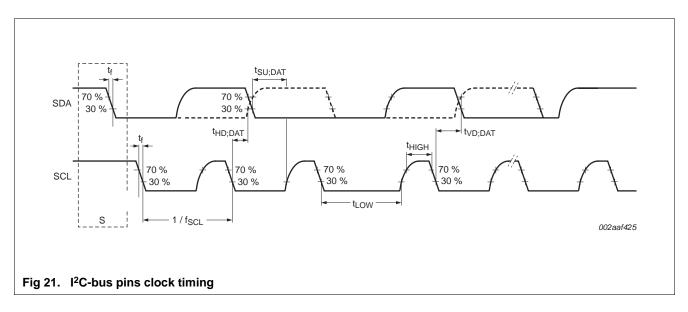

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial CLock line (SCL) and a Serial DAta line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (e.g., an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

### 7.10.1 Features

- The I<sup>2</sup>C-interface is a standard I<sup>2</sup>C-bus compliant interface with open-drain pins. The I<sup>2</sup>C-bus interface also supports Fast-mode Plus with bit rates up to 1 Mbit/s.

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- The I<sup>2</sup>C-bus controller supports multiple address recognition and a bus monitor mode.

## 7.11 C\_CAN controller

Controller Area Network (CAN) is the definition of a high performance communication protocol for serial data communication. The C\_CAN controller is designed to provide a full implementation of the CAN protocol according to the CAN Specification Version 2.0B. The C\_CAN controller allows to build powerful local networks with low-cost multiplex wiring by supporting distributed real-time control with a very high level of security.

On-chip C\_CAN drivers provide an API for initialization and communication using CAN and CANopen standards.

### 7.11.1 Features

- Conforms to protocol version 2.0 parts A and B.

- Supports bit rate of up to 1 Mbit/s.

- Supports 32 Message Objects.

- Each Message Object has its own identifier mask.

- Provides programmable FIFO mode (concatenation of Message Objects).

- Provides maskable interrupts.

- Supports Disabled Automatic Retransmission (DAR) mode for time-triggered CAN applications.

- Provides programmable loop-back mode for self-test operation.

### 7.16.1.3 Watchdog oscillator

The watchdog oscillator can be used as a clock source that directly drives the CPU, the watchdog timer, or the CLKOUT pin. The watchdog oscillator nominal frequency is programmable between 7.8 kHz and 1.7 MHz. The frequency spread over processing and temperature is  $\pm 40$  % (see <u>Table 16</u>).

### 7.16.2 System PLL

The PLL accepts an input clock frequency in the range of 10 MHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The multiplier can be an integer value from 1 to 32. The CCO operates in the range of 156 MHz to 320 MHz, so there is an additional divider in the loop to keep the CCO within its frequency range while the PLL is providing the desired output frequency. The output divider may be set to divide by 2, 4, 8, or 16 to produce the output clock. The PLL output frequency must be lower than 100 MHz. Since the minimum output divider value is 2, it is insured that the PLL output has a 50 % duty cycle. The PLL is turned off and bypassed following a chip reset and may be enabled by software. The program must configure and activate the PLL, wait for the PLL to lock, and then connect to the PLL as a clock source. The PLL settling time is 100  $\mu$ s.

### 7.16.3 Clock output

The LPC11Cx2/Cx4 features a clock output function that routes the IRC oscillator, the system oscillator, the watchdog oscillator, or the main clock to an output pin.

### 7.16.4 Wake-up process

The LPC11Cx2/Cx4 begin operation at power-up and when awakened from Deep power-down mode by using the 12 MHz IRC oscillator as the clock source. This allows chip operation to resume quickly. If the system oscillator or the PLL is needed by the application, software will need to enable these features and wait for them to stabilize before they are used as a clock source.

### 7.16.5 Power control

The LPC11Cx2/Cx4 support a variety of power control features. There are three special modes of processor power reduction: Sleep mode, Deep-sleep mode, and Deep power-down mode. The CPU clock rate may also be controlled as needed by changing clock sources, reconfiguring PLL values, and/or altering the CPU clock divider value. This allows a trade-off of power versus processing speed based on application requirements. In addition, a register is provided for shutting down the clocks to individual on-chip peripherals, allowing fine tuning of power consumption by eliminating all dynamic power use in any peripherals that are not required for the application. Selected peripherals have their own clock divider which provides even better power control.

### 7.16.5.1 Sleep mode

When Sleep mode is entered, the clock to the core is stopped. Resumption from the Sleep mode does not need any special sequence but re-enabling the clock to the ARM core.

In Sleep mode, execution of instructions is suspended until either a reset or interrupt occurs. Peripheral functions continue operation during Sleep mode and may generate interrupts to cause the processor to resume execution. Sleep mode eliminates dynamic power used by the processor itself, memory systems and related controllers, and internal buses.

LPC11CX2\_CX4

### 7.16.5.2 Deep-sleep mode

In Deep-sleep mode, the chip is in Sleep mode, and in addition all analog blocks are shut down. As an exception, the user has the option to keep the watchdog oscillator and the BOD circuit running for self-timed wake-up and BOD protection. Deep-sleep mode allows for additional power savings.

Up to 13 pins total, see <u>Table 3</u>, serve as external wake-up pins to a dedicated start logic to wake up the chip from Deep-sleep mode.

Unless the watchdog oscillator is selected to run in Deep-sleep mode, the clock source should be switched to IRC before entering Deep-sleep mode, because the IRC can be switched on and off glitch-free.

### 7.16.5.3 Deep power-down mode

In Deep power-down mode, power is shut off to the entire chip with the exception of the WAKEUP pin. The LPC11Cx2/Cx4 can wake up from Deep power-down mode via the WAKEUP pin.

When entering Deep power-down mode, an external pull-up resistor is required on the WAKEUP pin to hold it HIGH. The RESET pin must also be held HIGH to prevent it from floating while in Deep power-down mode.

### 7.17 System control

### 7.17.1 Start logic

The start logic connects external pins to corresponding interrupts in the NVIC. Each pin shown in <u>Table 3</u> as input to the start logic has an individual interrupt in the NVIC interrupt vector table. The start logic pins can serve as external interrupt pins when the chip is running. In addition, an input signal on the start logic pins can wake up the chip from Deep-sleep mode when all clocks are shut down.

The start logic must be configured in the system configuration block and in the NVIC before being used.

### 7.17.2 Reset

Reset has four sources on the LPC11Cx2/Cx4: the RESET pin, the Watchdog reset, power-on reset (POR), and the BrownOut Detection (BOD) circuit. The RESET pin is a Schmitt trigger input pin. Assertion of chip reset by any source, once the operating voltage attains a usable level, starts the IRC and initializes the flash controller.

When the internal Reset is removed, the processor begins executing at address 0, which is initially the Reset vector mapped from the boot block. At that point, all of the processor and peripheral registers have been initialized to predetermined values.

An external pull-up resistor is required on the RESET pin if Deep power-down mode is used.

# 9. Static characteristics

### Table 6. Static characteristics

$T_{amb} = -40$  °C to +85 °C, unless otherwise specified.

| Symbol           | Parameter                               | Conditions                                                                                                                         |                               | Min          | Typ[1] | Мах                | Unit |

|------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------|--------|--------------------|------|

| V <sub>DD</sub>  | supply voltage (core and external rail) | on pins $V_{DD}$                                                                                                                   |                               | 1.8          | 3.3    | 3.6                | V    |

| I <sub>DD</sub>  | supply current                          | Active mode; code                                                                                                                  |                               |              |        |                    |      |

|                  |                                         | while(1){}                                                                                                                         |                               |              |        |                    |      |

|                  |                                         | executed from flash                                                                                                                |                               |              |        |                    |      |

|                  |                                         | system<br>clock = 12 MHz                                                                                                           | <u>[2][3][4]</u><br>[5][6][7] | -            | 3      | -                  | mA   |

|                  |                                         | V <sub>DD</sub> = 3.3 V                                                                                                            |                               |              |        |                    |      |

|                  |                                         | system<br>clock = 50 MHz                                                                                                           | <u>[2][3][6]</u><br>[5][7][8] | -            | 9      | -                  | mA   |

|                  |                                         | $V_{DD} = 3.3 V$                                                                                                                   |                               |              |        |                    |      |

|                  |                                         | Sleep mode;                                                                                                                        | [2][3][4]                     | -            | 2      | -                  | mA   |

|                  |                                         | system clock = 12<br>MHz                                                                                                           | <u>[5][6][7]</u>              |              |        |                    |      |

|                  |                                         | $V_{DD} = 3.3 V$                                                                                                                   |                               |              |        |                    |      |

|                  |                                         | Deep-sleep mode;<br>V <sub>DD</sub> = 3.3 V                                                                                        | <u>[2][3][5]</u><br>[9]       | -            | 6      | -                  | μA   |

|                  |                                         | Deep power-down mode; $V_{DD} = 3.3 \text{ V}$                                                                                     | [2][10]                       | -            | 220    | -                  | nA   |

| Standard p       | oort pins, RESET                        |                                                                                                                                    |                               |              |        |                    |      |

| IIL              | LOW-level input current                 | V <sub>I</sub> = 0 V; on-chip<br>pull-up resistor<br>disabled                                                                      |                               | -            | 0.5    | 10                 | nA   |

| I <sub>IH</sub>  | HIGH-level input current                | V <sub>I</sub> = V <sub>DD</sub> ; on-chip<br>pull-down resistor<br>disabled                                                       |                               | -            | 0.5    | 10                 | nA   |

| I <sub>OZ</sub>  | OFF-state output current                | V <sub>O</sub> = 0 V; V <sub>O</sub> = V <sub>DD</sub> ;<br>on-chip pull-up/down<br>resistors disabled                             |                               | -            | 0.5    | 10                 | nA   |

| VI               | input voltage                           | $V_{DD} \ge 1.8 \text{ V}$                                                                                                         | [11]<br>[12]                  | 0            | -      | 5.0                | V    |

|                  |                                         | $V_{DD} = 0 V$                                                                                                                     |                               | 0            | -      | 3.6                | V    |

| Vo               | output voltage                          | output active                                                                                                                      |                               | 0            | -      | V <sub>DD</sub>    | V    |

| V <sub>IH</sub>  | HIGH-level input voltage                |                                                                                                                                    |                               | $0.7V_{DD}$  | -      | -                  | V    |

| V <sub>IL</sub>  | LOW-level input voltage                 |                                                                                                                                    |                               | -            | -      | $0.3V_{\text{DD}}$ | V    |

| V <sub>hys</sub> | hysteresis voltage                      |                                                                                                                                    |                               | -            | 0.4    | -                  | V    |

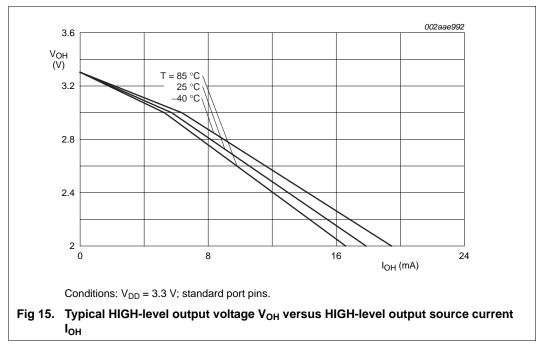

| V <sub>OH</sub>  | HIGH-level output voltage               | $\begin{array}{l} 2.0 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}; \\ \text{I}_{\text{OH}} = -4 \text{ mA} \end{array}$ |                               | $V_{DD}-0.4$ | -      | -                  | V    |

|                  | -                                       | 1.8 V $\leq$ V <sub>DD</sub> < 2.0 V;<br>I <sub>OH</sub> = -3 mA                                                                   |                               | $V_{DD}-0.4$ | -      | -                  | V    |

| Symbol                   | Parameter                                    | Conditions                                                                                                                      |      | Min         | Typ <u>[1]</u> | Max         | Unit |

|--------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|-------------|----------------|-------------|------|

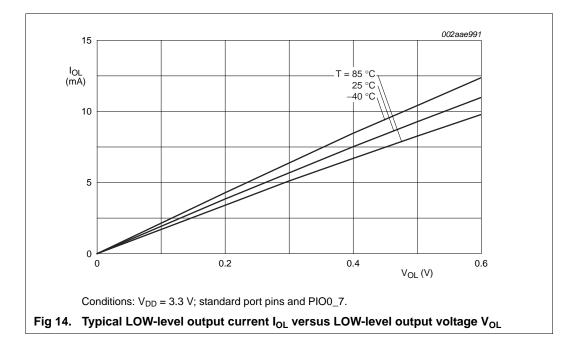

| V <sub>OL</sub>          | LOW-level output voltage                     | $\begin{array}{l} 2.0 \ V \leq V_{DD} \ \leq 3.6 \ V; \\ I_{OL} = 4 \ mA \end{array} \label{eq:VDD}$                            |      | -           | -              | 0.4         | V    |

|                          |                                              | 1.8 V $\leq$ V_{DD} < 2.0 V; I_{OL} = 3 mA                                                                                      |      | -           | -              | 0.4         | V    |

| l <sub>OH</sub>          | HIGH-level output<br>current                 | $\begin{array}{l} V_{OH}=V_{DD}-0.4 \text{ V};\\ \textbf{2.5 V}\leqV_{DD}\leq\textbf{3.6 V} \end{array}$                        |      | 20          | -              | -           | mA   |

|                          |                                              | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.5 \text{ V}$                                                                       |      | 12          | -              | -           | mA   |

| I <sub>OL</sub>          | LOW-level output                             | $V_{OL} = 0.4 V$                                                                                                                |      | 4           | -              | -           | mA   |

|                          | current                                      | $2.0~V \leq V_{DD}~\leq 3.6~V$                                                                                                  |      |             |                |             |      |

|                          |                                              | $1.8~\text{V} \leq \text{V}_{DD} < 2.0~\text{V}$                                                                                |      | 3           | -              | -           | mA   |

| I <sub>OLS</sub>         | LOW-level<br>short-circuit output<br>current | $V_{OL} = V_{DD}$                                                                                                               | [13] | -           | -              | 50          | mA   |

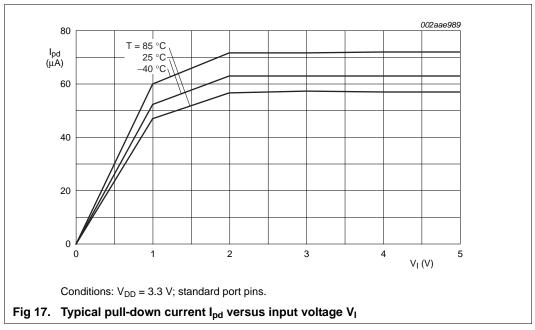

| I <sub>pd</sub>          | pull-down current                            | V <sub>I</sub> = 5 V                                                                                                            |      | 10          | 50             | 150         | μA   |

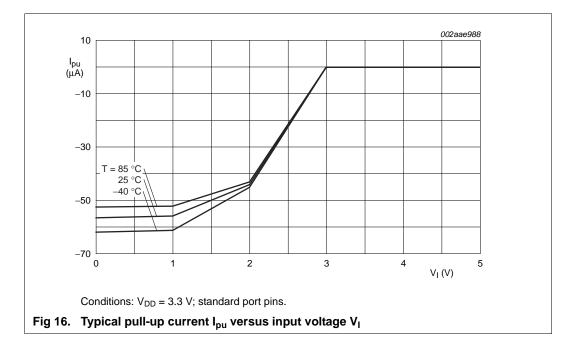

| I <sub>pu</sub>          | pull-up current                              | V <sub>I</sub> = 0 V                                                                                                            |      | –15         | -50            | -85         | μA   |

|                          |                                              | $2.0~V \leq V_{DD}~\leq 3.6~V$                                                                                                  |      |             |                |             |      |

|                          |                                              | $1.8~V \leq V_{DD} < 2.0~V$                                                                                                     |      | -10         | -50            | -85         | μA   |

|                          |                                              | $V_{DD} < V_{I} < 5 V$                                                                                                          |      | 0           | 0              | 0           | μA   |

| I <sup>2</sup> C-bus pir | ns (PIO0_4 and PIO0_5)                       |                                                                                                                                 |      |             |                |             |      |

| V <sub>IH</sub>          | HIGH-level input voltage                     |                                                                                                                                 |      | $0.7V_{DD}$ | -              | -           | V    |

| V <sub>IL</sub>          | LOW-level input voltage                      |                                                                                                                                 |      | -           | -              | $0.3V_{DD}$ | V    |

| V <sub>hys</sub>         | hysteresis voltage                           |                                                                                                                                 |      | -           | $0.05V_{DD}$   | -           | V    |

| I <sub>OL</sub>          | LOW-level output current                     | $V_{OL}$ = 0.4 V; I <sup>2</sup> C-bus<br>pins configured as<br>standard mode pins<br>2.0 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V |      | 3.5         | -              | -           | mA   |

|                          |                                              | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.0 \text{ V}$                                                                        |      | 3           | -              | -           |      |

| I <sub>OL</sub>          | LOW-level output current                     | V <sub>OL</sub> = 0.4 V; I <sup>2</sup> C-bus<br>pins configured as<br>Fast-mode Plus pins                                      |      | 20          | -              | -           | mA   |

|                          |                                              | $2.0~V \leq V_{DD}~\leq 3.6~V$                                                                                                  |      |             |                |             |      |

|                          |                                              | $1.8~\text{V} \leq \text{V}_{\text{DD}} < 2.0~\text{V}$                                                                         |      | 16          | -              | -           |      |

| ILI                      | input leakage current                        | $V_{I} = V_{DD}$                                                                                                                | [14] | -           | 2              | 4           | μA   |

|                          |                                              | V <sub>I</sub> = 5 V                                                                                                            |      | -           | 10             | 22          | μA   |

| Oscillator               | pins                                         |                                                                                                                                 |      |             |                |             |      |

| V <sub>i(xtal)</sub>     | crystal input voltage                        |                                                                                                                                 |      | -0.5        | 1.8            | 1.95        | V    |

| V <sub>o(xtal)</sub>     | crystal output voltage                       |                                                                                                                                 |      | -0.5        | 1.8            | 1.95        | V    |

#### Table 6. Static characteristics ... continued

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] T<sub>amb</sub> = 25 °C.

I<sub>DD</sub> measurements were performed with all pins configured as GPIO outputs driven LOW and pull-up resistors disabled. [3]

[4] IRC enabled; system oscillator disabled; system PLL disabled.

LPC11CX2\_CX4

### 32-bit ARM Cortex-M0 microcontroller

### 32-bit ARM Cortex-M0 microcontroller

# **10.** Dynamic characteristics

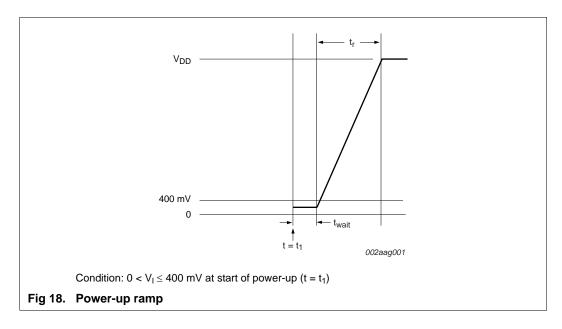

### 10.1 Power-up ramp conditions

### Table 12. Power-up characteristics

$T_{amb} = -40 \ ^{\circ}C \ to +85 \ ^{\circ}C.$

| Symbol            | Parameter     | Conditions                                               |        | Min | Тур | Max | Unit |

|-------------------|---------------|----------------------------------------------------------|--------|-----|-----|-----|------|

| t <sub>r</sub>    | rise time     | at t = t <sub>1</sub> : 0 < V <sub>1</sub> $\leq$ 400 mV | [1]    | 0   | -   | 500 | ms   |

| t <sub>wait</sub> | wait time     |                                                          | [1][2] | 12  | -   | -   | μS   |

| VI                | input voltage | at t = $t_1$ on pin $V_{DD}$                             |        | 0   | -   | 400 | mV   |

[1] See Figure 18.

[2] The wait time specifies the time the power supply must be at levels below 400 mV before ramping up.

### 10.2 Flash memory

### Table 13. Flash characteristics

$T_{amb} = -40$  °C to +85 °C, unless otherwise specified.

| Symbol            | Parameter           | Conditions                                   |     | Min   | Тур    | Max  | Unit   |

|-------------------|---------------------|----------------------------------------------|-----|-------|--------|------|--------|

| N <sub>endu</sub> | endurance           |                                              | [1] | 10000 | 100000 | -    | cycles |

| t <sub>ret</sub>  | retention time      | powered                                      |     | 10    | -      | -    | years  |

|                   |                     | unpowered                                    |     | 20    | -      | -    | years  |

| t <sub>er</sub>   | erase time          | sector or multiple<br>consecutive<br>sectors |     | 95    | 100    | 105  | ms     |

| t <sub>prog</sub> | programming<br>time |                                              | [2] | 0.95  | 1      | 1.05 | ms     |

[1] Number of program/erase cycles.

[2] Programming times are given for writing 256 bytes from RAM to the flash. Data must be written to the flash in blocks of 256 bytes.

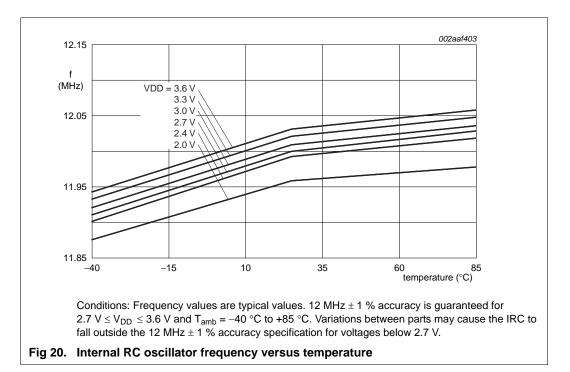

## 10.4 Internal oscillators

### Table 15. Dynamic characteristic: internal oscillators

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; 2.7 \text{ V} \le V_{DD} \le 3.6 \text{ V}.$ <sup>[1]</sup>

| Symbol               | Parameter                        | Conditions | Min   | Typ <u><sup>[2]</sup></u> | Max   | Unit |

|----------------------|----------------------------------|------------|-------|---------------------------|-------|------|

| f <sub>osc(RC)</sub> | internal RC oscillator frequency | -          | 11.88 | 12                        | 12.12 | MHz  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

### Table 16. Dynamic characteristics: Watchdog oscillator

| Symbol                | Parameter                        | Conditions                                                  |        | Min | Typ[1] | Max | Unit |

|-----------------------|----------------------------------|-------------------------------------------------------------|--------|-----|--------|-----|------|

| f <sub>osc(int)</sub> | internal oscillator<br>frequency | DIVSEL = 0x1F, FREQSEL = 0x1<br>in the WDTOSCCTRL register; | [2][3] | -   | 7.8    | -   | kHz  |

|                       |                                  | DIVSEL = 0x00, FREQSEL = 0xF<br>in the WDTOSCCTRL register  | [2][3] | -   | 1700   | -   | kHz  |

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] The typical frequency spread over processing and temperature (T<sub>amb</sub> = -40 °C to +85 °C) is ±40 %.

[3] See the LPC11Cx user manual.

- [6] The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- [7] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- [8] The maximum  $t_{HD;DAT}$  could be 3.45  $\mu$ s and 0.9  $\mu$ s for Standard-mode and Fast-mode but must be less than the maximum of  $t_{VD;DAT}$  or  $t_{VD;ACK}$  by a transition time (see *UM10204*). This maximum must only be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

- [9] tSU;DAT is the data set-up time that is measured with respect to the rising edge of SCL; applies to data in transmission and the acknowledge.

- [10] A Fast-mode l<sup>2</sup>C-bus device can be used in a Standard-mode l<sup>2</sup>C-bus system but the requirement  $t_{SU;DAT}$  = 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{r(max)} + t_{SU;DAT} = 1000 + 250 = 1250$  ns (according to the Standard-mode l<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

### 10.7 SPI interfaces

| Table 19. | Dynamic characteristics of SPI pins in SPI mode |

|-----------|-------------------------------------------------|

|-----------|-------------------------------------------------|

| Symbol                | Parameter              | Conditions                                              |           | Min                                  | Тур | Max | Unit                                |

|-----------------------|------------------------|---------------------------------------------------------|-----------|--------------------------------------|-----|-----|-------------------------------------|

| SPI maste             | er (in SPI mode)       |                                                         |           |                                      |     |     |                                     |

| T <sub>cy(clk)</sub>  | clock cycle time       | full-duplex mode                                        | [1]       | 50                                   | -   | -   | ns                                  |

|                       |                        | when only transmitting                                  | [1]       | 40                                   |     |     | ns                                  |

| t <sub>DS</sub>       | data set-up time       | in SPI mode                                             | [2]       | 15                                   | -   | -   | ns                                  |

|                       |                        | $2.4~V \leq V_{DD} \leq 3.6~V$                          |           |                                      |     |     |                                     |

|                       |                        | $2.0~\text{V} \leq \text{V}_{\text{DD}} < 2.4~\text{V}$ | [2]       | 20                                   |     |     | ns                                  |

|                       |                        | $1.8~V \leq V_{DD} < 2.0~V$                             | [2]       | 24                                   | -   | -   | ns                                  |

| t <sub>DH</sub>       | data hold time         | in SPI mode                                             | [2]       | 0                                    | -   | -   | ns                                  |

| t <sub>v(Q)</sub>     | data output valid time | in SPI mode                                             | [2]       | -                                    | -   | 10  | ns                                  |

| t <sub>h(Q)</sub>     | data output hold time  | in SPI mode                                             | [2]       | 0                                    | -   | -   | ns                                  |

| SPI slave             | (in SPI mode)          |                                                         |           |                                      |     |     |                                     |

| T <sub>cy(PCLK)</sub> | PCLK cycle time        |                                                         |           | 20                                   | -   | -   | ns                                  |

| LPC11CX2_CX4          |                        | All information provided in th                          | is docume | ent is subject to legal disclaimers. |     |     | © NXP B.V. 2016. All rights reserve |

# **11.** Application information

### 11.1 ADC usage notes

The following guidelines show how to increase the performance of the ADC in a noisy environment beyond the ADC specifications listed in <u>Table 7</u>:

- The ADC input trace must be short and as close as possible to the LPC11Cx2/Cx4 chip.

- The ADC input traces must be shielded from fast switching digital signals and noisy power supply lines.

- Because the ADC and the digital core share the same power supply, the power supply line must be adequately filtered.

- To improve the ADC performance in a very noisy environment, put the device in Sleep mode during the ADC conversion.

## 11.2 XTAL input

The input voltage to the on-chip oscillators is limited to 1.8 V. If the oscillator is driven by a clock in slave mode, it is recommended that the input be coupled through a capacitor with  $C_i = 100 \text{ pF}$ . To limit the input voltage to the specified range, choose an additional capacitor to ground  $C_g$  which attenuates the input voltage by a factor  $C_i/(C_i + C_g)$ . In slave mode, a minimum of 200 mv (RMS) is needed.

In slave mode the input clock signal should be coupled by means of a capacitor of 100 pF (Figure 24), with an amplitude between 200 mv (RMS) and 1000 mv (RMS). This corresponds to a square wave signal with a signal swing of between 280 mV and 1.4 V. The XTALOUT pin in this configuration can be left unconnected.

External components and models used in oscillation mode are shown in Figure 25 and in Table 20 and Table 21. Since the feedback resistance is integrated on chip, only a crystal and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally in case of fundamental mode oscillation (the fundamental frequency is represented by L,  $C_L$  and  $R_S$ ). Capacitance  $C_P$  in Figure 25 represents the parallel package capacitance and should not be larger than 7 pF. Parameters  $F_{OSC}$ ,  $C_L$ ,  $R_S$  and  $C_P$  are supplied by the crystal manufacturer (see Table 20).

order to keep the noise coupled in via the PCB as small as possible. Also parasitics should stay as small as possible. Values of  $C_{x1}$  and  $C_{x2}$  should be chosen smaller accordingly to the increase in parasitics of the PCB layout.

## 11.4 Standard I/O pad configuration

Figure 26 shows the possible pin modes for standard I/O pins with analog input function:

- Digital output driver

- Digital input: Pull-up enabled/disabled

- Digital input: Pull-down enabled/disabled

- Digital input: Repeater mode enabled/disabled

- Analog input

# 11.6 C\_CAN with external transceiver (LPC11C12/C14 only)

### 32-bit ARM Cortex-M0 microcontroller

| Document ID      | Release date                                                                                                                                        | Data sheet status  | Change notice | Supersedes |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------|------------|--|

| Modifications:   | <ul> <li>Parts LPC11C22 and LPC11C24 added.</li> </ul>                                                                                              |                    |               |            |  |

|                  | <ul> <li>Pin description for parts LPC11C22 and LPC11C24 added (Table 4).</li> </ul>                                                                |                    |               |            |  |

|                  | <ul> <li>Static characteristics for CAN transceiver added (Table 8).</li> </ul>                                                                     |                    |               |            |  |

|                  | <ul> <li>Description of high-speed, on-chip CAN transceiver added (LPC11C22/C24). See<br/>Section 7.11.2.</li> </ul>                                |                    |               |            |  |

|                  | <ul> <li>Application diagram for connecting the C_CAN to an external transceiver added<br/>(Section 11.6).</li> </ul>                               |                    |               |            |  |

|                  | • Application diagram for high-speed, on-chip CAN transceiver added (Section 11.7).                                                                 |                    |               |            |  |

|                  | <ul> <li>Typical value for parameter N<sub>endu</sub> added in Table 12 "Flash characteristics".</li> </ul>                                         |                    |               |            |  |

|                  | <ul> <li>Description of RESET and WAKEKUP pins updated in Table 3.</li> </ul>                                                                       |                    |               |            |  |

|                  | <ul> <li>PLL output frequency limited to &lt; 100 MHz in Section 7.16.2 "System PLL".</li> </ul>                                                    |                    |               |            |  |

|                  | <ul> <li>Parameter V<sub>hys</sub> for I<sup>2</sup>C bus pins: typical value corrected V<sub>hys</sub> = 0.05V<sub>DD</sub> in Table 6.</li> </ul> |                    |               |            |  |

| LPC11C12_C14 v.1 | 20100921                                                                                                                                            | Product data sheet | -             | -          |  |

### Table 23. Revision history ... continued

LPC11CX2\_CX4

32-bit ARM Cortex-M0 microcontroller

# 18. Contents

| 1            | General description 1                            |

|--------------|--------------------------------------------------|

| 2            | Features and benefits 1                          |

| 3            | Applications 2                                   |

| 4            | Ordering information                             |

| 4.1          | Ordering options                                 |

| 5            | Block diagram 4                                  |

| 6            | Pinning information 5                            |

| 6.1          | Pinning                                          |

| 6.2          | Pin description                                  |

| 7            | Functional description                           |

| 7.1          | ARM Cortex-M0 processor                          |

| 7.2          | On-chip flash program memory 15                  |

| 7.3          | On-chip SRAM                                     |

| 7.4          | Memory map 15                                    |

| 7.5          | Nested Vectored Interrupt Controller (NVIC) . 16 |

| 7.5.1        | Features 16                                      |

| 7.5.2        | Interrupt sources                                |

| 7.6          | IOCONFIG block                                   |

| 7.7<br>7.7.1 | Fast general purpose parallel I/O 17             |

| 7.7.1        | Features                                         |

| 7.8.1        | Features                                         |

| 7.9          | SPI serial I/O controller                        |

| 7.9.1        | Features                                         |

| 7.10         | l <sup>2</sup> C-bus serial I/O controller       |

| 7.10.1       | Features                                         |

| 7.11         | C_CAN controller 19                              |

| 7.11.1       | Features                                         |

| 7.11.2       | On-chip, high-speed CAN transceiver 20           |

| 7.11.2.1     | Features                                         |

| 7.11.2.2     |                                                  |

| 7.11.2.3     |                                                  |

| 7.11.2.4     | 0 1                                              |

| 7.11.2.5     |                                                  |

| 7.11.2.0     | 10-bit ADC                                       |

| 7.12.1       | Features                                         |

| 7.13         | General purpose external event                   |

|              | counter/timers                                   |

| 7.13.1       | Features                                         |

| 7.14         | System tick timer 22                             |

| 7.15         | Watchdog timer 22                                |

| 7.15.1       | Features                                         |

| 7.16         | Clocking and power control 22                    |

| 7.16.1       | Crystal oscillators                              |

| 7.16.1.1     |                                                  |

| 7.16.1.2     | System oscillator 23                             |

| 7.16.1.3 | Watchdog oscillator                        | 24 |

|----------|--------------------------------------------|----|

| 7.16.2   | System PLL                                 | 24 |

| 7.16.3   | Clock output                               | 24 |

| 7.16.4   | Wake-up process                            | 24 |

| 7.16.5   | Power control                              | 24 |

| 7.16.5.1 | Sleep mode                                 | 24 |

| 7.16.5.2 | Deep-sleep mode                            | 25 |

| 7.16.5.3 | Deep power-down mode                       | 25 |

| 7.17     | System control                             | 25 |

| 7.17.1   | Start logic                                | 25 |

| 7.17.2   | Reset                                      | 25 |

| 7.17.3   | Brownout detection                         | 26 |

| 7.17.4   | Code security (Code Read Protection - CRP) | 26 |

| 7.17.5   | Bootloader                                 | 27 |

| 7.17.6   | APB interface                              | 27 |

| 7.17.7   | AHBLite                                    | 27 |

| 7.17.8   | External interrupt inputs                  | 27 |

| 7.18     | Emulation and debugging                    | 27 |

| 8        | Limiting values                            | 28 |

| 9        | Static characteristics                     | 29 |

| 9.1      | ADC characteristics                        | 32 |

| 9.2      | C_CAN on-chip, high-speed transceiver      |    |

|          | characteristics                            | 34 |

| 9.3      | BOD static characteristics                 | 36 |

| 9.4      | Power consumption                          | 36 |

| 9.5      | Peripheral power consumption               | 40 |

| 9.6      | Electrical pin characteristics             | 41 |

| 10       | Dynamic characteristics                    | 44 |

| 10.1     | Power-up ramp conditions                   | 44 |

| 10.2     | Flash memory                               | 44 |

| 10.3     | External clock.                            | 45 |

| 10.4     | Internal oscillators                       | 46 |

| 10.5     | I/O pins                                   | 47 |

| 10.6     | I <sup>2</sup> C-bus                       | 47 |

| 10.7     | SPI interfaces                             | 48 |

| 11       | Application information                    | 51 |

| 11.1     | ADC usage notes                            | 51 |

| 11.2     | XTAL input                                 | 51 |

| 11.3     | XTAL Printed Circuit Board (PCB) layout    |    |

|          | guidelines                                 | 52 |

| 11.4     | Standard I/O pad configuration             | 53 |

| 11.5     | Reset pad configuration                    | 54 |

| 11.6     | C_CAN with external transceiver            |    |

| -        | (LPC11C12/C14 only)                        | 54 |

| 11.7     | C_CAN with on-chip, high-speed transceiver |    |

|          | (LPC11C22/C24 only)                        | 55 |

| 12       | Package outline                            | 56 |

|          | -                                          |    |

### continued >>

| 13   | Soldering           | 57 |

|------|---------------------|----|

| 14   | Abbreviations       | 58 |

| 15   | Revision history    | 59 |

| 16   | Legal information   | 61 |

| 16.1 | Data sheet status   | 61 |

| 16.2 | Definitions         | 61 |

| 16.3 | Disclaimers         | 61 |

| 16.4 | Trademarks          | 62 |

| 17   | Contact information | 62 |

| 18   | Contents            | 63 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

### © NXP B.V. 2016.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 4 January 2016 Document identifier: LPC11CX2\_CX4

All rights reserved.