#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 768B (512 x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 25 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VFDFN Exposed Pad                                                      |

| Supplier Device Package    | 8-DFN (2x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f508-i-mc |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

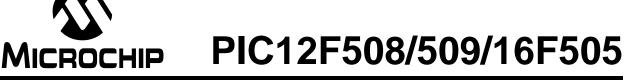

## 8/14-Pin, 8-Bit Flash Microcontrollers

### **Devices Included In This Data Sheet:**

• PIC12F508 • PIC12F509 • PIC16F505

### High-Performance RISC CPU:

- Only 33 Single-Word Instructions to Learn

- All Single-Cycle Instructions Except for Program Branches, which are Two-Cycle

- 12-Bit Wide Instructions

- 2-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes for Data and Instructions

- 8-Bit Wide Data Path

- 8 Special Function Hardware Registers

- Operating Speed:

- DC 20 MHz clock input (PIC16F505 only)

- DC 200 ns instruction cycle (PIC16F505 only)

- DC 4 MHz clock input

- DC 1000 ns instruction cycle

### **Special Microcontroller Features:**

- 4 MHz Precision Internal Oscillator:

- Factory calibrated to ±1%

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Debugging (ICD) Support

- Power-On Reset (POR)

- Device Reset Timer (DRT)

- Watchdog Timer (WDT) with Dedicated On-Chip RC Oscillator for Reliable Operation

- Programmable Code Protection

- Multiplexed MCLR Input Pin

- Internal Weak Pull-Ups on I/O Pins

- Power-Saving Sleep mode

- Wake-Wp from Sleep on Pin Change

- Selectable Oscillator Options:

- INTRC: 4 MHz precision Internal oscillator

- EXTRC: External low-cost RC oscillator

- XT: Standard crystal/resonator

- HS: High-speed crystal/resonator (PIC16F505 only)

- LP: Power-saving, low-frequency crystal

- EC: High-speed external clock input (PIC16F505 only)

### Low-Power Features/CMOS Technology:

- Operating Current:

- < 175 μA @ 2V, 4 MHz, typical

- Standby Current:

- 100 nA @ 2V, typical

- Low-Power, High-Speed Flash Technology:

- 100,000 Flash endurance

- > 40 year retention

- Fully Static Design

- Wide Operating Voltage Range: 2.0V to 5.5V

- Wide Temperature Range:

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

### Peripheral Features (PIC12F508/509):

- 6 I/O Pins:

- 5 I/O pins with individual direction control

- 1 input only pin

- High current sink/source for direct LED drive

- Wake-on-change

- Weak pull-ups

- 8-Bit Real-Time Clock/Counter (TMR0) with 8-Bit Programmable Prescaler

### Peripheral Features (PIC16F505):

- 12 I/O Pins:

- 11 I/O pins with individual direction control

- 1 input only pin

- High current sink/source for direct LED drive

- Wake-on-change

- Weak pull-ups

- 8-Bit Real-Time Clock/Counter (TMR0) with 8-Bit Programmable Prescaler

### 2.0 PIC12F508/509/16F505 DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12F508/509/16F505 Product Identification System at the back of this data sheet to specify the correct part number.

### 2.1 Quick Turn Programming (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who choose not to program medium-to-high quantity units and whose code patterns have stabilized. The devices are identical to the Flash devices but with all Flash locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

### 2.2 Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry code, password or ID number.

| R/W-0                                                                    | R/W-0                          | R/W-0                                | 、<br>R-1        | R-1            | ,<br>R/W-x       | R/W-x             | R/W-x    |

|--------------------------------------------------------------------------|--------------------------------|--------------------------------------|-----------------|----------------|------------------|-------------------|----------|

| RBWUF                                                                    | N/W-0                          |                                      | TO              | PD             | Z                | -                 |          |

| bit 7                                                                    |                                | PA0                                  | 10              | PD             | Z                | DC                | C        |

|                                                                          |                                |                                      |                 |                |                  |                   | bit 0    |

| Legend:                                                                  |                                |                                      |                 |                |                  |                   |          |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |                                |                                      |                 |                |                  |                   |          |

| -n = Value at I                                                          | POR                            | '1' = Bit is set                     |                 | '0' = Bit is c |                  | x = Bit is unkr   | nown     |

|                                                                          |                                |                                      |                 |                |                  |                   |          |

| bit 7                                                                    | RBWUF: POF                     | RTB Reset bit                        |                 |                |                  |                   |          |

|                                                                          |                                | e to wake-up fro                     |                 | pin change     |                  |                   |          |

|                                                                          | •                              | er-up or other f                     | Reset           |                |                  |                   |          |

| bit 6                                                                    | Reserved: Do                   |                                      |                 |                |                  |                   |          |

| bit 5                                                                    | -                              | n Page Presele                       | Ct Dits         |                |                  |                   |          |

|                                                                          | 1 = Page 1 (2<br>0 = Page 0 (0 |                                      |                 |                |                  |                   |          |

|                                                                          | Each page is                   |                                      |                 |                |                  |                   |          |

|                                                                          |                                |                                      |                 |                | devices which d  |                   |          |

|                                                                          | ·                              |                                      | ed, since this  | may affect up  | ward compatibili | ty with future pi | roducts. |

| bit 4                                                                    | TO: Time-Out                   |                                      |                 |                |                  |                   |          |

|                                                                          |                                | er-up, CLRWDT                        |                 | r sleep instr  | uction           |                   |          |

| bit 3                                                                    | PD: Power-Do                   |                                      |                 |                |                  |                   |          |

|                                                                          | 1 = After pow                  | er-up or by the                      | CLRWDT inst     | ruction        |                  |                   |          |

|                                                                          | 0 = By execut                  | tion of the SLEI                     | EP instruction  |                |                  |                   |          |

| bit 2                                                                    | Z: Zero bit                    |                                      |                 |                |                  |                   |          |

|                                                                          |                                | t of an arithmet                     |                 |                |                  |                   |          |

| h:+ 1                                                                    |                                | t of an arithmet                     |                 |                |                  |                   |          |

| bit 1                                                                    | ADDWF :                        | ry/Borrow bit (fe                    | JI ADDWF and    | I SUBME INSU   | ictions)         |                   |          |

|                                                                          |                                | om the 4th low-                      | order bit of th | ne result occu | rred             |                   |          |

|                                                                          | •                              | om the 4th low-                      |                 |                |                  |                   |          |

|                                                                          | SUBWF:                         | · · · · · ·                          |                 |                |                  |                   |          |

|                                                                          |                                | from the 4th lov<br>from the 4th lov |                 |                |                  |                   |          |

| bit 0                                                                    |                                | ow bit (for ADDI                     |                 |                |                  |                   |          |

|                                                                          | ADDWF:                         | -                                    | JBWF:           |                | RRF OF RLF:      |                   |          |

|                                                                          | 1 = A carry oc                 | curred 1                             | = A borrow d    |                | Load bit with LS | b or MSb, respe   | ectively |

|                                                                          | 0 = A carry di                 | d not occur 0                        | = A borrow o    | ccurred        |                  |                   |          |

### REGISTER 4-2: STATUS REGISTER (ADDRESS: 03h) (PIC16F505)

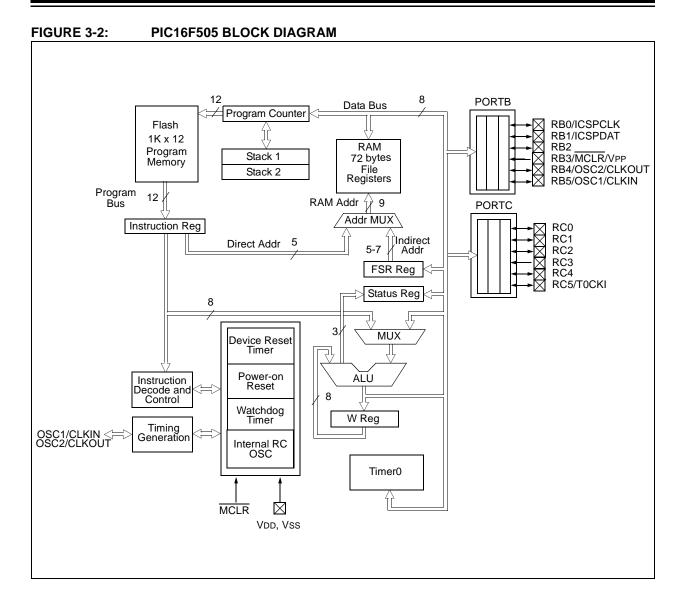

### 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select:

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1 "Using Timer0 with an External Clock".

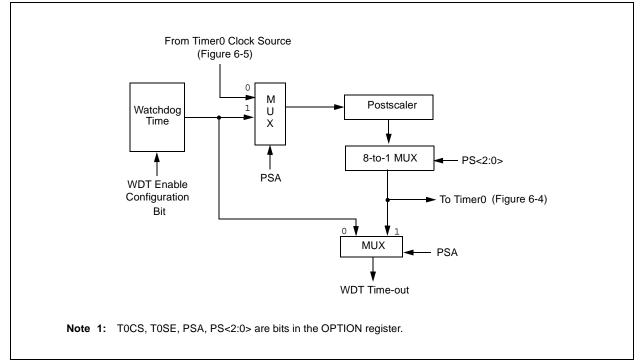

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit, PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 6.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| PC<br>(Program<br>Counter)        | PC – 1 |            | Q1 Q2 Q3 Q4<br>PC + 1 | PC + 2      | (PC + 3     | $\frac{Q1}{Q2}\frac{Q3}{Q4}$ | PC + 5      | (PC+6)  |

|-----------------------------------|--------|------------|-----------------------|-------------|-------------|------------------------------|-------------|---------|

| Instruction<br>Fetch              |        | MOVWF TMR0 | MOVF TMR0,W           | MOVF TMR0,W | MOVF TMR0,W | MOVF TMR0,W                  | MOVF TMR0,W |         |

| Timer0<br>Instruction<br>Executed | (то)   | T0 + 1 )   | T0 + 2)               | Read TMR0   | NT0         | Read TMR0                    | NT0 + 1)∕   | NT0 + 2 |

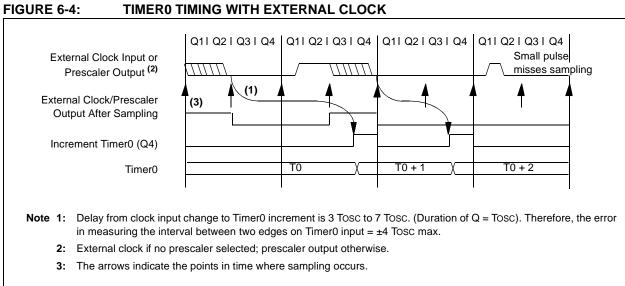

#### 6.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### EXTERNAL CLOCK 6.1.1 **SYNCHRONIZATION**

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 2 Tt0H) and low for at least 2 Tosc (and a small RC delay of 2 Tt0H). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4 Tosc (and a small RC delay of 4 Tt0H) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of Tt0H. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### TIMER0 INCREMENT DELAY 6.1.2

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-4 shows the delay from the external clock edge to the timer incrementing.

# 7.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of real-time applications. The PIC12F508/509/16F505 microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These features are:

- Oscillator Selection

- Reset:

- Power-on Reset (POR)

- Device Reset Timer (DRT)

- Wake-up from Sleep on Pin Change

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

- Clock Out

The PIC12F508/509/16F505 devices have a Watchdog Timer, which can be shut off only through Configuration bit WDTE. It runs off of its own RC oscillator for added reliability. If using HS (PIC16F505), XT or LP selectable oscillator options, there is always an 18 ms (nominal) delay provided by the Device Reset Timer (DRT), intended to keep the chip in Reset until the crystal oscillator is stable. If using INTRC or EXTRC, there is an 18 ms delay only on VDD power-up. With this timer on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through a change on input pins or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application, including an internal 4 MHz oscillator. The EXTRC oscillator option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options.

### 7.1 Configuration Bits

The PIC12F508/509/16F505 Configuration Words consist of 12 bits. Configuration bits can be programmed to select various device configurations. Three bits are for the selection of the oscillator type; (two bits on the PIC12F508/509), one bit is the Watchdog Timer enable bit, one bit is the MCLR enable bit and one bit is for code protection (Register 7-1, Register 7-2).

### REGISTER 7-1: CONFIGURATION WORD FOR PIC12F508/509<sup>(1)</sup>

|           |                                                                         | -            | 1          | -         |             |              |            |             |            |       |

|-----------|-------------------------------------------------------------------------|--------------|------------|-----------|-------------|--------------|------------|-------------|------------|-------|

|           | — —                                                                     | —            | —          | —         | _           | MCLRE        | CP         | WDTE        | FOSC1      | FOSC0 |

| bit 11    |                                                                         |              |            |           |             |              |            |             |            | bit 0 |

|           |                                                                         |              |            |           |             |              |            |             |            |       |

| Legend:   |                                                                         |              |            |           |             |              |            |             |            |       |

| R = Read  | dable bit                                                               | W = Writa    | able bit   |           | U = Unin    | nplemented   | d bit, rea | d as '0'    |            |       |

| -n = Valu | ie at POR                                                               | '1' = Bit is | s set      |           | '0' = Bit i | s cleared    |            | x = Bit is  | unknown    |       |

|           |                                                                         |              |            |           |             |              |            |             |            |       |

| bit 11-5  | Unimplemented:                                                          | Read as '0   | ,          |           |             |              |            |             |            |       |

| bit 4     | MCLRE: GP3/MC                                                           | LR Pin Fur   | nction Sel | ect bit   |             |              |            |             |            |       |

|           | 1 = GP3/MCLR pi                                                         |              |            |           | _           |              |            |             |            |       |

|           | 0 = GP3/MCLR pin function is digital input, MCLR internally tied to VDD |              |            |           |             |              |            |             |            |       |

| bit 3     | CP: Code Protecti                                                       | on bit       |            |           |             |              |            |             |            |       |

|           | 1 = Code protectio                                                      |              |            |           |             |              |            |             |            |       |

|           | 0 = Code protectio                                                      | on on        |            |           |             |              |            |             |            |       |

| bit 2     | WDTE: Watchdog                                                          | Timer Ena    | ble bit    |           |             |              |            |             |            |       |

|           | 1 = WDT enabled                                                         |              |            |           |             |              |            |             |            |       |

|           | 0 = WDT disabled                                                        |              |            |           |             |              |            |             |            |       |

| bit 1-0   | FOSC<1:0>: Osci                                                         |              |            |           |             |              |            |             |            |       |

|           | 11 = EXTRC = external RC oscillator                                     |              |            |           |             |              |            |             |            |       |

|           | 10 = INTRC = internal RC oscillator<br>01 = XT oscillator               |              |            |           |             |              |            |             |            |       |

|           | 00 = LP oscillator                                                      |              |            |           |             |              |            |             |            |       |

| Note 1:   | Refer to the "PIC                                                       | 12F508/50    | 9 Memor    | y Program | ming Spe    | cifications" | (DS4122    | 27) to dete | ermine hov | v to  |

|           | access the Config                                                       |              | -          | •         | • •         |              | •          | ,           |            |       |

|           |                                                                         |              |            |           |             |              |            |             |            |       |

TMR0

STATUS

OSCCAL

PORTB

PORTC

OPTION

TRISB

TRISC

PC

FSR

| IABLE /-4: F | TABLE 7-4: RESET CONDITIONS FOR REGISTERS – PIC16F505 |                |                                                  |  |  |  |  |

|--------------|-------------------------------------------------------|----------------|--------------------------------------------------|--|--|--|--|

| Register     | Address                                               | Power-on Reset | MCLR Reset, WDT Time-ou<br>Wake-up On Pin Change |  |  |  |  |

| W            | —                                                     | qqqq qqqu(1)   | qqqq qqqu <sup>(1)</sup>                         |  |  |  |  |

| INDF         | 00h                                                   | XXXX XXXX      | <u>uuuu</u> uuuu                                 |  |  |  |  |

#### DECET CONDITIONS FOR DECISTERS DICACEEOE

01h

02h

03h

04h

05h

06h

07h

\_

\_

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

XXXX XXXX

1111 1111

0001 1xxx

100x xxxx

1111 111-

--xx xxxx

--xx xxxx

1111 1111

--11 1111

--11 1111

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

- 2: See Table 7-5 for Reset value for specific conditions.

- 3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

#### **TABLE 7-5**: **RESET CONDITION FOR SPECIAL REGISTERS**

|                                    | STATUS Addr: 03h | PCL Addr: 02h |

|------------------------------------|------------------|---------------|

| Power-on Reset                     | 0001 1xxx        | 1111 1111     |

| MCLR Reset during normal operation | 000u uuuu        | 1111 1111     |

| MCLR Reset during Sleep            | 0001 0uuu        | 1111 1111     |

| WDT Reset during Sleep             | 0000 Ouuu        | 1111 1111     |

| WDT Reset normal operation         | 0000 uuuu        | 1111 1111     |

| Wake-up from Sleep on pin change   | 1001 Ouuu        | 1111 1111     |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

WDT Time-out,

uuuu uuuu

1111 1111 q00q quuu**(2), (3)**

1uuu uuuu

uuuu uuu-

--uu uuuu

--uu uuuu

1111 1111

--11 1111

--11 1111

TABLE 7-7: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-----------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | OPTION <sup>(1)</sup> | GPWU  | GPPU  | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup> | RBWU  | RBPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: Shaded boxes = Not used by Watchdog Timer. - = unimplemented, read as '0', u = unchanged.

**Note 1:** PIC12F508/509 only.

2: PIC16F505 only.

### 7.9 Power-down Mode (Sleep)

A device may be powered down (Sleep) and later powered up (wake-up from Sleep).

### 7.9.1 SLEEP

The Power-Down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit (STATUS<4>) is set, the PD bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low or high-impedance).

**Note:** A Reset generated by a WDT time-out does not drive the MCLR pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or Vss and the (GP3/RB3)/MCLR/VPP pin must be at a logic high level if MCLR is enabled.

### 7.9.2 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- An external Reset input on (GP3/RB3)/MCLR/ VPP pin, when configured as MCLR.

- 2. A Watchdog Timer time-out Reset (if WDT was enabled).

- A change on input pin GP0/RB0, GP1/RB1, GP3/RB3 or RB4 when wake-up on change is enabled.

These events cause a device Reset. The  $\overline{TO}$ ,  $\overline{PD}$  and GPWUF/RBWUF bits can be used to determine the cause of device Reset. The  $\overline{TO}$  bit is cleared if a WDT time-out occurred (and caused wake-up). The  $\overline{PD}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The GPWUF/RBWUF bit indicates a change in state while in Sleep at pins GP0/RB0, GP1/RB1, GP3/RB3 or RB4 (since the last file or bit operation on GP/RB port).

Note: Caution: Right before entering Sleep, read the input pins. When in Sleep, wakeup occurs when the values at the pins change from the state they were in at the last reading. If a wake-up on change occurs and the pins are not read before reentering Sleep, a wake-up will occur immediately even if no pins change while in Sleep mode.

The WDT is cleared when the device wakes from Sleep, regardless of the wake-up source.

### 7.10 Program Verification/Code Protection

If the code protection bit has not been programmed, the on-chip program memory can be read out for verification purposes.

The first 64 locations and the last location (OSCCAL) can be read, regardless of the code protection bit setting.

The last memory location can be read regardless of the code protection bit setting on the PIC12F508/509/ 16F505 devices.

### 7.11 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '0's.

### 7.12 In-Circuit Serial Programming™

The PIC12F508/509/16F505 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The devices are placed into a Program/Verify mode by holding the <u>GP1/RB1</u> and GP0/RB0 pins low while raising the <u>MCLR</u> (VPP) pin from VIL to VIHH (see programming specification). GP1/RB1 becomes the programming clock and GP0/RB0 becomes the programming data. Both GP1/RB1 and GP0/RB0 are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial programming, please refer to the PIC12F508/509/16F505 Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 7-15.

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address). This<br>is a two-cycle instruction. |

| SLEEP            | Enter SLEEP Mode                                                                                                                                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                                                                                                |

| Operands:        | None                                                                                                                                                                                                                                                                                                         |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT; \\ 0 \rightarrow WDT \mbox{ prescaler}; \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                                                                   |

| Status Affected: | TO, PD, RBWUF                                                                                                                                                                                                                                                                                                |

| Description:     | Time-out Status bit (TO) is set. The<br>Power-down Status bit (PD) is<br>cleared.<br>RBWUF is unaffected.<br>The WDT and its prescaler are<br>cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped.<br>See Section 7.9 "Power-down<br>Mode (Sleep)" on Sleep for more<br>details. |

| RLF              | Rotate Left f th                                                             | nrough Carry                                                             |  |  |  |  |

|------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ]                                                                    | RLF f,d                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$             |                                                                          |  |  |  |  |

| Operation:       | See description below                                                        |                                                                          |  |  |  |  |

| Status Affected: | С                                                                            |                                                                          |  |  |  |  |

| Description:     | the Carry flag. I<br>is placed in the<br>'1', the result is<br>register 'f'. | to the left through<br>f 'd' is '0', the result<br>W register. If 'd' is |  |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                                |

| Operation:       | $(f) - (W) \rightarrow (dest)$                                                                                                                                                                  |

| Status Affected: | C, DC, Z                                                                                                                                                                                        |

| Description:     | Subtract (2's complement method)<br>the W register from register 'f'. If 'd'<br>is '0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                                                      |

| Operation:       | See description below                                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

|                  | C register 'f'                                                                                                                                                                                                        |

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                   |

| Operation:       | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                          |

| Status Affected: | None                                                                                                                                                               |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in W register. If 'd' is '1', the result is placed in register 'f'. |

(W) .XOR.  $k \rightarrow (W)$

The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in the W

Ζ

register.

Operation: Status Affected:

Description:

| TRIS             | Load TRIS Register                         | XORWF            | Exclusive OR W with f                                                                                                                              |  |

|------------------|--------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [label] TRIS f                             | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                         |  |

| Operands:        | f = 6                                      | Operands:        | $0 \le f \le 31$                                                                                                                                   |  |

| Operation:       | (W) $\rightarrow$ TRIS register f          |                  | d ∈ [0,1]                                                                                                                                          |  |

| Status Affected: | None                                       | Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                 |  |

| Description:     | TRIS register 'f' (f = 6 or 7) is          | Status Affected: | Z                                                                                                                                                  |  |

|                  | loaded with the contents of the W register | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is |  |

| XORLW            | Exclusive OR literal with W                |                  | stored back in register 'f'.                                                                                                                       |  |

| Syntax:          | [ <i>label</i> ] XORLW k                   |                  | <u> </u>                                                                                                                                           |  |

| Operands:        | $0 \le k \le 255$                          |                  |                                                                                                                                                    |  |

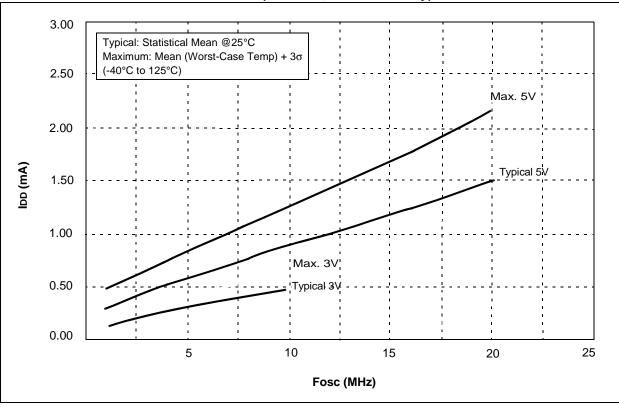

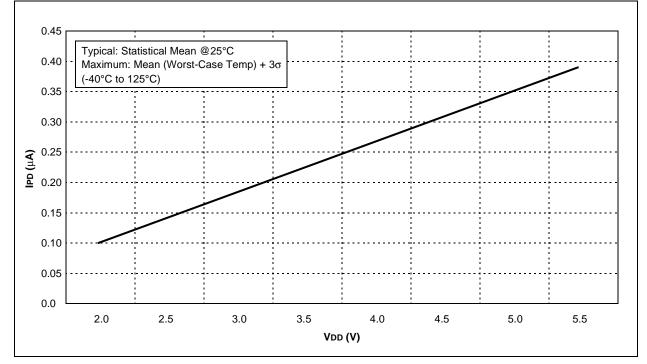

### 10.2 DC Characteristics: PIC12F508/509/16F505 (Extended)

| DC Characteristics |      | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended) |       |                    |             |          |                                                                            |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|-------------|----------|----------------------------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                                                                                                         | Min.  | Typ <sup>(1)</sup> | Max.        | Units    | Conditions                                                                 |

| D001               | Vdd  | Supply Voltage                                                                                                                         | 2.0   |                    | 5.5         | V        | See Figure 10-1                                                            |

| D002               | Vdr  | RAM Data Retention Voltage <sup>(2)</sup>                                                                                              | _     | 1.5*               |             | V        | Device in Sleep mode                                                       |

| D003               | VPOR | VDD Start Voltage to ensure<br>Power-on Reset                                                                                          | —     | Vss                | —           | V        | See Section 7.4 "Power-on<br>Reset (POR)" for details                      |

| D004               | SVDD | VDD Rise Rate to ensure<br>Power-on Reset                                                                                              | 0.05* | —                  | —           | V/ms     | See Section 7.4 "Power-on<br>Reset (POR)" for details                      |

| D010               | IDD  | Supply Current <sup>(3,4)</sup>                                                                                                        | _     | 175<br>0.625       | 275<br>1.1  | μA<br>mA | Fosc = 4 MHz, Vdd = 2.0V<br>Fosc = 4 MHz, Vdd = 5.0V                       |

|                    |      |                                                                                                                                        | _     | 500<br>1.5         | 650<br>2.2  | μA<br>mA | Fosc = 10 MHz, VDD = 3.0V<br>Fosc = 20 MHz, VDD = 5.0V<br>(PIC16F515 only) |

|                    |      |                                                                                                                                        | _     | 11<br>38           | 26<br>110   | μΑ<br>μΑ | Fosc = 32 kHz, VDD = 2.0V<br>Fosc = 32 kHz, VDD = 5.0V                     |

| D020               | IPD  | Power-down Current <sup>(5)</sup>                                                                                                      | _     | 0.1<br>0.35        | 9.0<br>15.0 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                   |

| D022               | Iwdt | WDT Current <sup>(5)</sup>                                                                                                             |       | 1.0<br>7.0         | 18<br>22    | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                   |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- 4: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- 5: For standby current measurements, the conditions are the same as IDD, except that the device is in Sleep mode. If a module current is listed, the current is for that specific module enabled and the device in Sleep.

### TABLE 10-6: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER – PIC12F508/509/16F505

| AC CHARACTERISTICS |      | $\label{eq:standard operating Conditions (unless otherwise specified)} Operating Temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial) $-40^{\circ}C \leq TA \leq +125^{\circ}C$ (extended)$ (extended) $-40^{\circ}C \leq TA \leq +125^{\circ}C$ (extended) $-40^{\circ}C \leq -125^{\circ}C$ (extended) $-40^{\circ}C < -125^{\circ}C$ (extended) $-40^{\circ}C < -125^{\circ}C$ (extended) $-40^{\circ}C < -125^{\circ}C$ (extende$ |          |                    |            |          |                                                  |

|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|------------|----------|--------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Min.     | Typ <sup>(1)</sup> | Max.       | Units    | Conditions                                       |

| 30                 | TMCL | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2000*    | _                  | _          | ns       | VDD = 5.0V                                       |

| 31                 | Twdt | Watchdog Timer Time-out Period (no prescaler)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9*<br>9* | 18*<br>18*         | 30*<br>40* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 32                 | Tdrt | Device Reset Timer Period <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9*<br>9* | 18*<br>18*         | 30*<br>40* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 34                 | Tioz | I/O High-impedance from MCLR low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | —        |                    | 2000*      | ns       |                                                  |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### FIGURE 11-2: IDD VS. FOSC Over VDD (HS MODE, PIC16F505 only)

### 16-Lead Plastic Quad Flat, No Lead Package (MG) - 3x3x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units           | MILLIMETERS   |          |      |  |  |

|------------------------|-----------------|---------------|----------|------|--|--|

| D                      | imension Limits | MIN           | NOM      | MAX  |  |  |

| Number of Pins         | N               | 16            |          |      |  |  |

| Pitch                  | е               |               | 0.50 BSC |      |  |  |

| Overall Height         | A               | 0.80          | 0.85     | 0.90 |  |  |

| Standoff               | A1              | 0.00          | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3              | 0.20 REF      |          |      |  |  |

| Overall Width          | E               | 3.00 BSC      |          |      |  |  |

| Exposed Pad Width      | E2              | 1.00 1.10 1.5 |          |      |  |  |

| Overall Length         | D               | 3.00 BSC      |          |      |  |  |

| Exposed Pad Length     | D2              | 1.00          | 1.10     | 1.50 |  |  |

| Contact Width          | b               | 0.18          | 0.25     | 0.30 |  |  |

| Contact Length         | L               | 0.25          | 0.35     | 0.45 |  |  |

| Contact-to-Exposed Pad | K               | 0.20          | -        | -    |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-142A Sheet 2 of 2

NOTES:

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com

## WORLDWIDE SALES AND SERVICE

### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820