Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014.10                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 768B (512 x 12)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 25 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f508-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC12F508/509/16F505 devices from Microchip Technology are low-cost, high-performance, 8-bit, fully-static, Flash-based CMOS microcontrollers. They employ a RISC architecture with only 33 single-word/ single-cycle instructions. All instructions are single cycle (200 µs) except for program branches, which take two cycles. The PIC12F508/509/16F505 devices deliver performance an order of magnitude higher than their competitors in the same price category. The 12-bit wide instructions are highly symmetrical, resulting in a typical 2:1 code compression over other 8-bit microcontrollers in its class. The easy to use and easy to remember instruction set reduces development time significantly.

The PIC12F508/509/16F505 products are equipped with special features that reduce system cost and power requirements. The Power-on Reset (POR) and Device Reset Timer (DRT) eliminate the need for external Reset circuitry. There are four oscillator configurations to choose from (six on the PIC16F505), including INTRC Internal Oscillator mode and the power-saving LP (Low-Power) Oscillator mode. Power-Saving Sleep mode, Watchdog Timer and code protection features improve system cost, power and reliability.

The PIC12F508/509/16F505 devices are available in the cost-effective Flash programmable version, which is suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in Flash programmable microcontrollers, while benefiting from the Flash programmable flexibility.

The PIC12F508/509/16F505 products are supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a 'C' compiler, a low-cost development programmer and a full featured programmer. All the tools are supported on  $\text{IBM}^{\textcircled{B}}$  PC and compatible machines.

## 1.1 Applications

The PIC12F508/509/16F505 devices fit in applications ranging from personal care appliances and security systems to low-power remote transmitters/receivers. The Flash technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages, for through hole or surface mounting, make these microcontrollers perfect for applications with space limitations. Low cost, low power, high performance, ease-of-use and I/O flexibility make the PIC12F508/509/16F505 devices very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions, logic and PLDs in larger systems and coprocessor applications).

|             |                                      | PIC12F508                      | PIC12F509                      | PIC16F505                   |

|-------------|--------------------------------------|--------------------------------|--------------------------------|-----------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 4                              | 4                              | 20                          |

| Memory      | Flash Program Memory (words)         | 512                            | 1024                           | 1024                        |

|             | Data Memory (bytes)                  | 25                             | 41                             | 72                          |

| Peripherals | Timer Module(s)                      | TMR0                           | TMR0                           | TMR0                        |

|             | Wake-up from Sleep on Pin Change     | Yes                            | Yes                            | Yes                         |

| Features    | I/O Pins                             | 5                              | 5                              | 11                          |

|             | Input Pins                           | 1                              | 1                              | 1                           |

|             | Internal Pull-ups                    | Yes                            | Yes                            | Yes                         |

|             | In-Circuit Serial Programming        | Yes                            | Yes                            | Yes                         |

|             | Number of Instructions               | 33                             | 33                             | 33                          |

|             | Packages                             | 8-pin PDIP, SOIC,<br>MSOP, DFN | 8-pin PDIP, SOIC,<br>MSOP, DFN | 14-pin PDIP, SOIC,<br>TSSOP |

### TABLE 1-1: PIC12F508/509/16F505 DEVICES

The PIC12F508/509/16F505 devices have Power-on Reset, selectable Watchdog Timer, selectable code-protect, high I/O current capability and precision internal oscillator.

The PIC12F508/509/16F505 devices use serial programming with data pin RB0/GP0 and clock pin RB1/GP1.

NOTES:

| Name            | Function | Input<br>Type | Output<br>Type | Description                                                                                                                                                                                                                                                                                                         |

|-----------------|----------|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/ICSPDAT     | RB0      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                                                   |

|                 | ICSPDAT  | ST            | CMOS           | In-Circuit Serial Programming™ data pin.                                                                                                                                                                                                                                                                            |

| RB1/ICSPCLK     | RB1      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                                                   |

|                 | ICSPCLK  | ST            | CMOS           | In-Circuit Serial Programming clock pin.                                                                                                                                                                                                                                                                            |

| RB2             | RB2      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                              |

| RB3/MCLR/Vpp    | RB3      | TTL           | —              | Input port. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                                                              |

|                 | MCLR     | ST            | _              | Master Clear (Reset). When configured as $\overline{\text{MCLR}}$ , this pin is<br>an active-low Reset to the device. Voltage on $\overline{\text{MCLR}}$ /VPP must<br>not exceed VDD during normal device operation or the device<br>will enter Programming mode. Weak pull-up always on if<br>configured as MCLR. |

|                 | VPP HV – |               | —              | Programming voltage input.                                                                                                                                                                                                                                                                                          |

| RB4/OSC2/CLKOUT | RB4      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                                                   |

|                 | OSC2     | _             | XTAL           | Oscillator crystal output. Connections to crystal or resonator in Crystal Oscillator mode (XT, HS and LP modes only).                                                                                                                                                                                               |

|                 | CLKOUT   | _             | CMOS           | In EXTRC and INTRC modes, the pin output can be configured for CLKOUT, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                                                                                                                                                                  |

| RB5/OSC1/CLKIN  | RB5      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                              |

|                 | OSC1     | XTAL          |                | Crystal input.                                                                                                                                                                                                                                                                                                      |

|                 | CLKIN    | ST            |                | External clock source input.                                                                                                                                                                                                                                                                                        |

| RC0             | RC0      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                              |

| RC1             | RC1      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                              |

| RC2             | RC2      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                              |

| RC3             | RC3      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                              |

| RC4             | RC4      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                              |

| RC5/T0CKI       | RC5      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                              |

|                 | TOCKI    | ST            | —              | Clock input to TMR0.                                                                                                                                                                                                                                                                                                |

| Vdd             | Vdd      | _             | Р              | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                                                             |

| Vss             | Vss      | _             | Р              | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                                            |

| TABLE 3-3: | <b>PIC16F505 PINOUT DESCRIPTION</b> |

|------------|-------------------------------------|

|            |                                     |

**Legend:** I = Input, O = Output, I/O = Input/Output, P = Power, — = Not used, TTL = TTL input, ST = Schmitt Trigger input, HV = High Voltage

## 3.1 Clocking Scheme/Instruction Cycle

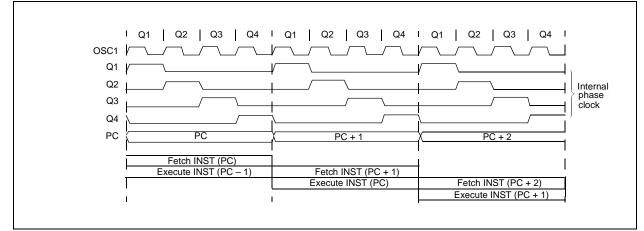

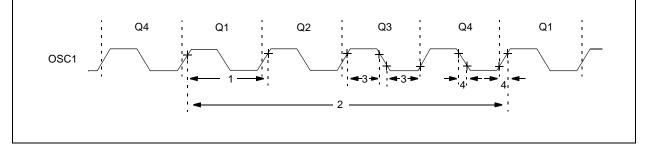

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the PC is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-3 and Example 3-1.

### 3.2 Instruction Flow/Pipelining

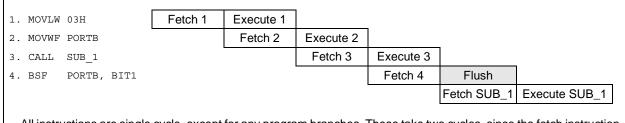

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

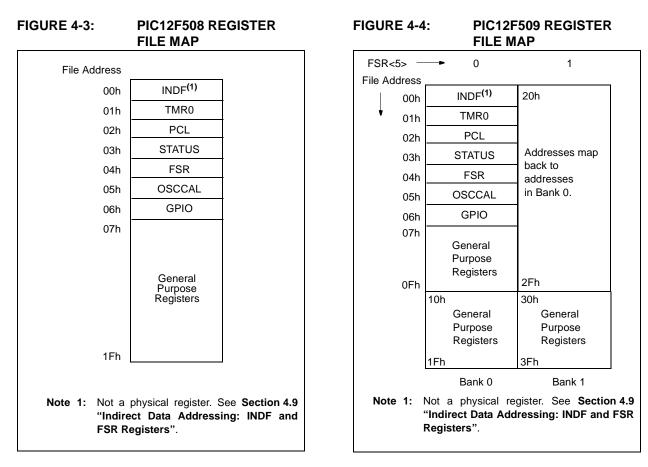

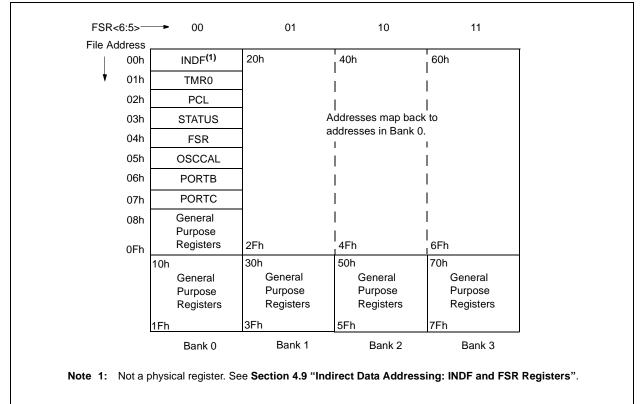

### FIGURE 4-5: PIC16F505 REGISTER FILE MAP

| W-1          | W-1                         | VV-1                                 | W-1          | W-1               | VV-1            | W-1             | W-1  |

|--------------|-----------------------------|--------------------------------------|--------------|-------------------|-----------------|-----------------|------|

| RBWU         | RBPU                        | TOCS                                 | T0SE         | PSA               | PS2             | PS1             | PS0  |

| oit 7        | ·                           |                                      |              |                   |                 |                 | bi   |

|              |                             |                                      |              |                   |                 |                 |      |

| Legend:      |                             |                                      |              |                   |                 |                 |      |

| R = Readal   | ole bit                     | W = Writable                         | bit          | U = Unimplen      | nented bit, rea | d as '0'        |      |

| -n = Value a | at POR                      | '1' = Bit is set                     |              | '0' = Bit is clea | ared            | x = Bit is unkr | nown |

|              |                             |                                      |              |                   |                 |                 |      |

| bit 7        |                             | le Wake-up on                        | Pin Change   | bit (RB0, RB1, I  | RB3, RB4)       |                 |      |

|              | 1 = Disabled<br>0 = Enabled |                                      |              |                   |                 |                 |      |

| bit 6        |                             | la Weak Pull-ur                      | s hit (RB0 R | B1, RB3, RB4)     |                 |                 |      |

|              | 1 = Disabled                | le weak i ui-up                      |              |                   |                 |                 |      |

|              | 0 = Enabled                 |                                      |              |                   |                 |                 |      |

| bit 5        | TOCS: Timer                 | 0 clock Source                       | Select bit   |                   |                 |                 |      |

|              |                             |                                      |              | IS on the TOCH    | (I pin)         |                 |      |

|              |                             | n on internal ins                    | -            | clock, Fosc/4     |                 |                 |      |

| bit 4        |                             | ) Source Edge                        |              |                   |                 |                 |      |

|              |                             | t on high-to-low<br>t on low-to-high |              |                   |                 |                 |      |

| bit 3        |                             | ler Assignment                       |              | ·                 |                 |                 |      |

|              |                             | r assigned to th                     |              |                   |                 |                 |      |

|              | 0 = Prescaler               | assigned to Ti                       | mer0         |                   |                 |                 |      |

| bit 2-0      | <b>PS&lt;2:0&gt;:</b> Pre   | escaler Rate Se                      | elect bits   |                   |                 |                 |      |

|              | Bit                         | Value Timer0                         | Rate WDT R   | late              |                 |                 |      |

|              |                             | 000 1:2                              |              |                   |                 |                 |      |

|              |                             | 001 1:4                              |              |                   |                 |                 |      |

|              |                             | 011 1:1                              |              |                   |                 |                 |      |

|              |                             | LOO 1:3                              | -            |                   |                 |                 |      |

|              |                             | LO1 1:6<br>L10 1:1                   |              |                   |                 |                 |      |

|              |                             | L10 1:1<br>L11 1:2                   |              |                   |                 |                 |      |

## REGISTER 4-4: OPTION REGISTER (PIC16F505)

### TABLE 5-1:SUMMARY OF PORT REGISTERS

| Address | Name                    | Bit 7 | Bit 6 | Bit 5     | Bit 4                | Bit 3 | Bit 2 | Bit 1   | Bit 0   | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-------------------------|-------|-------|-----------|----------------------|-------|-------|---------|---------|-------------------------------|---------------------------------|

| N/A     | TRISGPIO <sup>(1)</sup> | -     | _     | I/O Contr | ol Registe           | r     |       |         |         | 11 1111                       | 11 1111                         |

| N/A     | TRISB <sup>(2)</sup>    | —     | —     | I/O Contr | ol Registe           | r     |       |         |         | 11 1111                       | 11 1111                         |

| N/A     | TRISC <sup>(2)</sup>    | _     | —     | I/O Contr | I/O Control Register |       |       | 11 1111 | 11 1111 |                               |                                 |

| N/A     | OPTION <sup>(1)</sup>   | GPWU  | GPPU  | TOCS      | TOSE                 | PSA   | PS2   | PS1     | PS0     | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup>   | RBWU  | RBPU  | TOCS      | TOSE                 | PSA   | PS2   | PS1     | PS0     | 1111 1111                     | 1111 1111                       |

| 03h     | STATUS <sup>(1)</sup>   | GPWUF | —     | PAO       | ТО                   | PD    | Z     | DC      | С       | 0-01 1xxx                     | q00q quuu <sup>(3)</sup>        |

| 03h     | STATUS <sup>(2)</sup>   | RBWUF | _     | PAO       | TO                   | PD    | Z     | DC      | С       | 0-01 1xxx                     | q00q quuu <b>(3)</b>            |

| 06h     | GPIO <sup>(1)</sup>     | —     | —     | GP5       | GP4                  | GP3   | GP2   | GP1     | GP0     | xx xxxx                       | uu uuuu                         |

| 06h     | PORTB <sup>(2)</sup>    | _     | _     | RB5       | RB4                  | RB3   | RB2   | RB1     | RB0     | xx xxxx                       | uu uuuu                         |

| 07h     | PORTC <sup>(2)</sup>    | _     | _     | RC5       | RC4                  | RC3   | RC2   | RC1     | RC0     | xx xxxx                       | uu uuuu                         |

**Legend:** Shaded cells are not used by Port registers, read as '0'. – = unimplemented, read as '0', x = unknown, u = unchanged, q = depends on condition.

Note 1: PIC12F508/509 only.

2: PIC16F505 only.

3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

### 6.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (see Section 7.6 "Watchdog Timer (WDT)"). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

| Note: | The prescaler may be used by either the |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | Timer0 module or the WDT, but not both. |  |  |  |  |  |  |

|       | Thus, a prescaler assignment for the    |  |  |  |  |  |  |

|       | Timer0 module means that there is no    |  |  |  |  |  |  |

|       | prescaler for the WDT and vice versa.   |  |  |  |  |  |  |

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a Reset, the prescaler contains all '0's.

### 6.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

## EXAMPLE 6-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

|        | •           | ,                        |

|--------|-------------|--------------------------|

| CLRWDT |             | ;Clear WDT               |

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler  |

| MOVLW  | `00xx1111'b | ;These 3 lines (5, 6, 7) |

| OPTION |             | ;are required only if    |

|        |             | ;desired                 |

| CLRWDT |             | ;PS<2:0> are 000 or 001  |

| MOVLW  | `00xx1xxx'b | ;Set Postscaler to       |

| OPTION |             | ;desired WDT rate        |

|        |             |                          |

To change the prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

| EXAMPLE 6-2: | CHANGING PRESCALER         |

|--------------|----------------------------|

|              | (WDT $\rightarrow$ TIMER0) |

| CLRWDT           | ;Clear WDT and                  |

|------------------|---------------------------------|

| MOVLW 'xxxx0xxx' | ;prescaler<br>;Select TMR0, new |

| HOVEN AAAAAAAA   | ;prescale value and             |

|                  | ;clock source                   |

| OPTION           |                                 |

NOTES:

### 7.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT time-out Reset during normal operation

- WDT time-out Reset during Sleep

- Wake-up from Sleep on pin change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up on pin change Reset during normal operation. They are not affected by a WDT Reset during Sleep or MCLR Reset during Sleep, since these Resets are viewed as resumption of normal operation. The exceptions to this are TO, PD and RBWUF/GPWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 7-4 for a full description of Reset states of all registers.

| Register Address   |     | Power-on Reset           | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change |  |  |  |

|--------------------|-----|--------------------------|----------------------------------------------------|--|--|--|

| W                  | _   | qqqq qqqu <sup>(1)</sup> | qqqq qqqu <sup>(1)</sup>                           |  |  |  |

| INDF               | 00h | XXXX XXXX                | uuuu uuuu                                          |  |  |  |

| TMR0               | 01h | xxxx xxxx                | uuuu uuuu                                          |  |  |  |

| PC                 | 02h | 1111 1111                | 1111 1111                                          |  |  |  |

| STATUS             | 03h | 0001 1xxx                | q00q quuu <b>(2), (3)</b>                          |  |  |  |

| FSR <sup>(4)</sup> | 04h | 110x xxxx                | 11uu uuuu                                          |  |  |  |

| FSR <sup>(5)</sup> | 04h | 111x xxxx                | 111u uuuu                                          |  |  |  |

| OSCCAL             | 05h | 1111 111-                | uuuu uuu-                                          |  |  |  |

| GPIO               | 06h | xx xxxx                  | uu uuuu                                            |  |  |  |

| OPTION             | —   | 1111 1111                | 1111 1111                                          |  |  |  |

| TRIS               | —   | 11 1111                  | 11 1111                                            |  |  |  |

|                    |     |                          |                                                    |  |  |  |

### TABLE 7-3: RESET CONDITIONS FOR REGISTERS – PIC12F508/509

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

2: See Table 7-5 for Reset value for specific conditions.

**3:** If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

4: PIC12F509 only.

5: PIC12F508 only.

| Mnem    | onic,   | Description                                       | Cycles           | 12-       | Bit Opc   | Status    | Notes     |          |

|---------|---------|---------------------------------------------------|------------------|-----------|-----------|-----------|-----------|----------|

| Opera   | ands    | Description                                       | Cycles           | MSb       |           | LSb       | Affected  | notes    |

| ADDWF   | f, d    | Add W and f                                       | 1                | 0001      | 11df      | ffff      | C, DC, Z  | 1, 2, 4  |

| ANDWF   | f, d    | AND W with f                                      | 1                | 0001      | 01df      | ffff      | Z         | 2, 4     |

| CLRF    | f       | Clear f                                           | 1                | 0000      | 011f      | ffff      | Z         | 4        |

| CLRW    | —       | Clear W                                           | 1                | 0000      | 0100      | 0000      | Z         |          |

| COMF    | f, d    | Complement f                                      | 1                | 0010      | 01df      | ffff      | Z         |          |

| DECF    | f, d    | Decrement f                                       | 1                | 0000      | 11df      | ffff      | Z         | 2, 4     |

| DECFSZ  | f, d    | Decrement f, Skip if 0                            | 1 <sup>(2)</sup> | 0010      | 11df      | ffff      | None      | 2, 4     |

| INCF    | f, d    | Increment f                                       | 1                | 0010      | 10df      | ffff      | Z         | 2, 4     |

| INCFSZ  | f, d    | Increment f, Skip if 0                            | 1 <sup>(2)</sup> | 0011      | 11df      | ffff      | None      | 2, 4     |

| IORWF   | f, d    | Inclusive OR W with f                             | 1                | 0001      | 00df      | ffff      | Z         | 2, 4     |

| MOVF    | f, d    | Move f                                            | 1                | 0010      | 00df      | ffff      | Z         | 2, 4     |

| MOVWF   | f       | Move W to f                                       | 1                | 0000      | 001f      | ffff      | None      | 1, 4     |

| NOP     | _       | No Operation                                      | 1                | 0000      | 0000      | 0000      | None      |          |

| RLF     | f, d    | Rotate left f through Carry                       | 1                | 0011      | 01df      | ffff      | С         | 2, 4     |

| RRF     | f, d    | Rotate right f through Carry                      | 1                | 0011      | 00df      | ffff      | С         | 2, 4     |

| SUBWF   | f, d    | Subtract W from f                                 | 1                | 0000      | 10df      | ffff      | C, DC, Z  | 1, 2, 4  |

| SWAPF   | f, d    | Swap f                                            | 1                | 0011      | 10df      | ffff      | None      | 2, 4     |

| XORWF   | f, d    | Exclusive OR W with f                             | 1                | 0001      | 10df      | ffff      | Z         | 2, 4     |

|         |         | BIT-ORIENTED FILE REGISTE                         | R OPER           | ATIONS    | 5         |           |           |          |

| BCF     | f, b    | Bit Clear f                                       | 1                | 0100      | bbbf      | ffff      | None      | 2, 4     |

| BSF     | f, b    | Bit Set f                                         | 1                | 0101      | bbbf      | ffff      | None      | 2, 4     |

| BTFSC   | f, b    | Bit Test f, Skip if Clear                         | 1 <sup>(2)</sup> | 0110      | bbbf      | ffff      | None      |          |

| BTFSS   | f, b    | Bit Test f, Skip if Set                           | 1 <sup>(2)</sup> | 0111      | bbbf      | ffff      | None      |          |

|         |         | LITERAL AND CONTROL                               | OPERATI          | ONS       |           |           |           |          |

| ANDLW   | k       | AND literal with W                                | 1                | 1110      | kkkk      | kkkk      | Z         |          |

| CALL    | k       | Call Subroutine                                   | 2                | 1001      | kkkk      | kkkk      | None      | 1        |

| CLRWDT  | _       | Clear Watchdog Timer                              | 1                | 0000      | 0000      | 0100      | TO, PD    |          |

| GOTO    | k       | Unconditional branch                              | 2                | 101k      | kkkk      | kkkk      | None      |          |

| IORLW   | k       | Inclusive OR literal with W                       | 1                | 1101      | kkkk      | kkkk      | Z         |          |

| MOVLW   | k       | Move literal to W                                 | 1                | 1100      | kkkk      | kkkk      | None      |          |

| OPTION  | _       | Load OPTION register                              | 1                | 0000      | 0000      | 0010      | None      |          |

| RETLW   | k       | Return, place literal in W                        | 2                | 1000      | kkkk      | kkkk      | None      |          |

| SLEEP   | _       | Go into Standby mode                              | 1                | 0000      | 0000      | 0011      | TO, PD    |          |

| TRIS    | f       | Load TRIS register                                | 1                | 0000      | 0000      | Offf      | None      | 3        |

| XORLW   | k       | Exclusive OR literal to W                         | 1                | 1111      | kkkk      | kkkk      | Z         |          |

| Note 1: | The 9th | bit of the program counter will be forced to a 'o | ' by any i       | nstructio | on that v | writes to | the PC ex | cept for |

### TABLE 8-2: INSTRUCTION SET SUMMARY

ote 1: The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO. See Section 4.7 "Program Counter".

When an I/O register is madified as a function of itself (a g. NONE, DODED, 1), the value used will be that

2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 6, causes the contents of the W register to be written to the tri-state latches of PORTB. A '1' forces the pin to a high-impedance state and disables the output buffers.

4: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

Increment f

INCF

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                  |

| Operation:       | $(f) - 1 \rightarrow (dest)$                                                                                                                      |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is 'o',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

Decrement f, Skip if 0

[label] DECFSZ f,d

(f)  $-1 \rightarrow d$ ; skip if result = 0

The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in

If the result is '0', the next instruction, which is already fetched, is discarded and a NOP is executed instead making it a two-cycle

$\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$

None

register 'f'.

instruction.

DECFSZ

Syntax:

Operands:

Operation:

Description:

Status Affected:

| [label] INCF f,d                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                           |

| (f) + 1 $\rightarrow$ (dest)                                                                                                                                               |

| Z                                                                                                                                                                          |

| The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| Increment f, Skip if 0                                                                                                                                                     |

|                                                                                                                                                                            |

| [ <i>label</i> ] INCFSZ f,d                                                                                                                                                |

| $\begin{bmatrix} label \end{bmatrix}  INCFSZ  f,d$<br>$0 \le f \le 31$<br>$d \in [0,1]$                                                                                    |

| $0 \le f \le 31$                                                                                                                                                           |

| $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                          |

| $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \\ (f) + 1 \rightarrow (dest), \ skip \ if \ result = 0 \end{array}$                                                   |

|                                                                                                                                                                            |

| GOTO             | Unconditional Branch                                                                                                                                                                        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                     |

| Operands:        | $0 \le k \le 511$                                                                                                                                                                           |

| Operation:       | $k \rightarrow PC<8:0>;$<br>STATUS<6:5> $\rightarrow PC<10:9>$                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                        |

| Description:     | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a two-<br>cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |

| Operands:        | $0 \le k \le 255$                                                                                                         |

| Operation:       | (W) .OR. (k) $\rightarrow$ (W)                                                                                            |

| Status Affected: | Z                                                                                                                         |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |

(W) .XOR.  $k \rightarrow (W)$

The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in the W

Ζ

register.

Operation: Status Affected:

Description:

| TRIS             | Load TRIS Register                         | XORWF            | Exclusive OR W with f                                                                                                                              |

|------------------|--------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] TRIS f                             | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                         |

| Operands:        | f = 6                                      | Operands:        | $0 \le f \le 31$                                                                                                                                   |

| Operation:       | (W) $\rightarrow$ TRIS register f          |                  | d ∈ [0,1]                                                                                                                                          |

| Status Affected: | None                                       | Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                 |

| Description:     | TRIS register 'f' (f = 6 or 7) is          | Status Affected: | Z                                                                                                                                                  |

|                  | loaded with the contents of the W register | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is |

| XORLW            | Exclusive OR literal with W                |                  | stored back in register 'f'.                                                                                                                       |

| Syntax:          | [ <i>label</i> ] XORLW k                   |                  | <u> </u>                                                                                                                                           |

| Operands:        | $0 \le k \le 255$                          |                  |                                                                                                                                                    |

## 10.3 Timing Parameter Symbology and Load Conditions – PIC12F508/509/16F505

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

2. TppS

| z. 1pp0     |        |

|-------------|--------|

| Т           |        |

| F Frequency | T Time |

Lowercase subscripts (pp) and their meanings:

| рр      |                                 |     |                |

|---------|---------------------------------|-----|----------------|

| 2       | to                              | mc  | MCLR           |

| ck      | CLKOUT                          | osc | Oscillator     |

| су      | Cycle time                      | os  | OSC1           |

| drt     | Device Reset Timer              | tO  | ТОСКІ          |

| io      | I/O port                        | wdt | Watchdog Timer |

| Upperca | ase letters and their meanings: |     |                |

| S       |                                 |     |                |

| F       | Fall                            | Р   | Period         |

| н       | High                            | R   | Rise           |

| I       | Invalid (high-impedance)        | V   | Valid          |

| L       | Low                             | Z   | High-impedance |

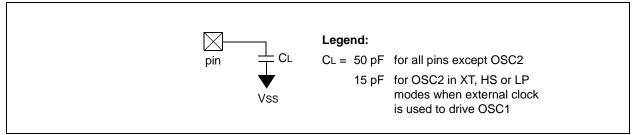

### FIGURE 10-3: LOAD CONDITIONS – PIC12F508/509/16F505

### FIGURE 10-4: EXTERNAL CLOCK TIMING – PIC12F508/509/16F505

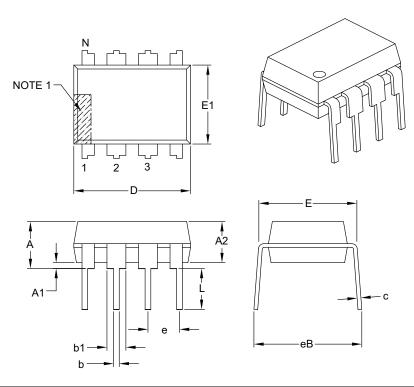

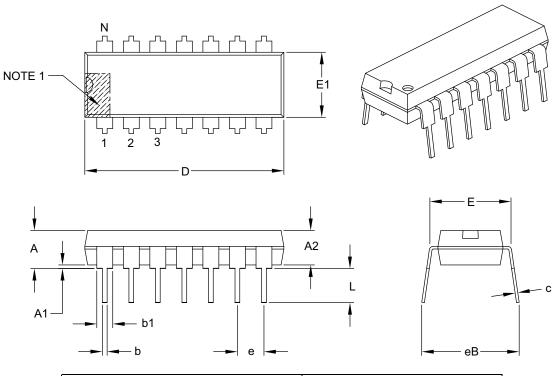

## 8-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |      | INCHES   |      |

|----------------------------|----------|------|----------|------|

| Dimensior                  | n Limits | MIN  | NOM      | MAX  |

| Number of Pins             | N        |      | 8        |      |

| Pitch                      | е        |      | .100 BSC |      |

| Top to Seating Plane       | Α        | -    | -        | .210 |

| Molded Package Thickness   | A2       | .115 | .130     | .195 |

| Base to Seating Plane      | A1       | .015 | -        | -    |

| Shoulder to Shoulder Width | E        | .290 | .310     | .325 |

| Molded Package Width       | E1       | .240 | .250     | .280 |

| Overall Length             | D        | .348 | .365     | .400 |

| Tip to Seating Plane       | L        | .115 | .130     | .150 |

| Lead Thickness             | С        | .008 | .010     | .015 |

| Upper Lead Width           | b1       | .040 | .060     | .070 |

| Lower Lead Width           | b        | .014 | .018     | .022 |

| Overall Row Spacing §      | eB       | _    | -        | .430 |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

## 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units       |      | INCHES   |      |

|----------------------------|-------------|------|----------|------|

| Dimen                      | sion Limits | MIN  | NOM      | MAX  |

| Number of Pins             | N           | 14   |          |      |

| Pitch                      | е           |      | .100 BSC |      |

| Top to Seating Plane       | А           | -    | -        | .210 |

| Molded Package Thickness   | A2          | .115 | .130     | .195 |

| Base to Seating Plane      | A1          | .015 | -        | -    |

| Shoulder to Shoulder Width | E           | .290 | .310     | .325 |

| Molded Package Width       | E1          | .240 | .250     | .280 |

| Overall Length             | D           | .735 | .750     | .775 |

| Tip to Seating Plane       | L           | .115 | .130     | .150 |

| Lead Thickness             | С           | .008 | .010     | .015 |

| Upper Lead Width           | b1          | .045 | .060     | .070 |

| Lower Lead Width           | b           | .014 | .018     | .022 |

| Overall Row Spacing §      | eB          | -    | -        | .430 |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

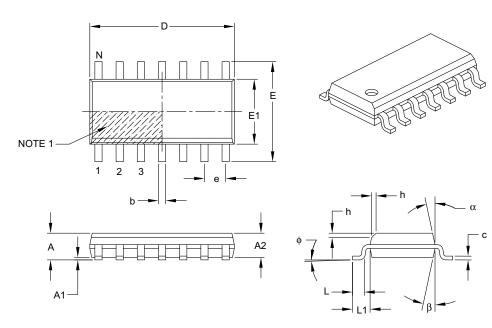

### 14-Lead Plastic Small Outline (SL) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |      |  |

|--------------------------|------------------|-------------|----------|------|--|

|                          | Dimension Limits | MIN         | NOM      | MAX  |  |

| Number of Pins           | N                |             | 14       |      |  |

| Pitch                    | е                |             | 1.27 BSC |      |  |

| Overall Height           | A                | -           | -        | 1.75 |  |

| Molded Package Thickness | A2               | 1.25        | -        | -    |  |

| Standoff §               | A1               | 0.10        | -        | 0.25 |  |

| Overall Width            | E                | 6.00 BSC    |          |      |  |

| Molded Package Width     | E1               | 3.90 BSC    |          |      |  |

| Overall Length           | D                |             | 8.65 BSC |      |  |

| Chamfer (optional)       | h                | 0.25        | -        | 0.50 |  |

| Foot Length              | L                | 0.40        | -        | 1.27 |  |

| Footprint                | L1               |             | 1.04 REF |      |  |

| Foot Angle               | φ                | 0°          | -        | 8°   |  |

| Lead Thickness           | С                | 0.17        | -        | 0.25 |  |

| Lead Width               | b                | 0.31        | -        | 0.51 |  |

| Mold Draft Angle Top     | α                | 5°          | -        | 15°  |  |

| Mold Draft Angle Bottom  | β                | 5°          | _        | 15°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-065B

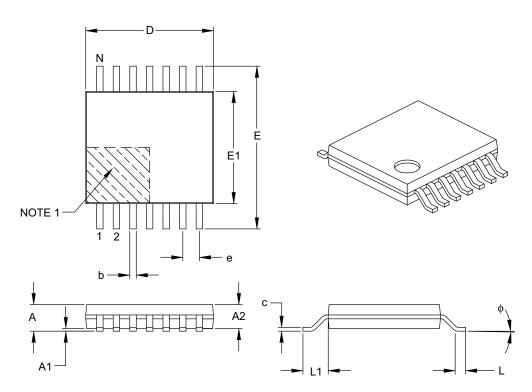

## 14-Lead Plastic Thin Shrink Small Outline (ST) – 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |          |      |      |

|--------------------------|------------------|----------|------|------|

| Dimensio                 | Dimension Limits |          | NOM  | MAX  |

| Number of Pins           | Ν                | 14       |      |      |

| Pitch                    | е                | 0.65 BSC |      |      |

| Overall Height           | А                | _        | -    | 1.20 |

| Molded Package Thickness | A2               | 0.80     | 1.00 | 1.05 |

| Standoff                 | A1               | 0.05     | -    | 0.15 |

| Overall Width            | Е                | 6.40 BSC |      |      |

| Molded Package Width     | E1               | 4.30     | 4.40 | 4.50 |

| Molded Package Length    | D                | 4.90     | 5.00 | 5.10 |

| Foot Length              | L                | 0.45     | 0.60 | 0.75 |

| Footprint                | L1               | 1.00 REF |      |      |

| Foot Angle               | φ                | 0°       | _    | 8°   |

| Lead Thickness           | с                | 0.09     | -    | 0.20 |

| Lead Width               | b                | 0.19     | -    | 0.30 |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-087B

## APPENDIX A: REVISION HISTORY

### Revision A (April 2004)

Original data sheet for PIC12F508/509/16F505 devices

### Revision B (June 2005)

Update packages

### Revision C (03/2007)

Revised Table 3-2 Legend; Revised Table 3-3 RB3 and Legend; Revised Table 10-4 F10; Replaced Package Drawings (Rev. AN); Added DFN package; Replaced Development Support Section; Revised Product ID System.

### Revision D (12/2007)

Revised Title; Operating Current; Table 1-1 added DFN and revised note; Revised Section 3.0, last paragraph; Revised Figure 4-4; Revised Table 4-2 (FSR); Revised Register 7-1 and Register 7-2; Revised Section 7.2.2; Revised Table 7-3, Note 2; Revised Table 7-4 (FSR) and Note 2; Deleted Section 7.3.1: External Clock In and Figure 7-6; Revised new Section 7.3.1; Replaced TBD with new data in Tables 10-4 and 10-5; Revised Tables 10-1 (Industrial), 10-2 (Extended), and Tables 10-1 (Industrial, Extended) and 10-2 (Pull-up Resistor Ranges), 10-3, 10-4 and 10-6; Revised Figure 10-1, Figure 10-2; Section 11.0, Added Char data; Revised Package Marking Information; Revised Product ID System.

#### Revision E (08/2009)

Added PIC16F505 16-Pin diagram (QFN); Added Note after subsection 5.2 PORTC; Updated Note 4 and deleted Note 5, Table 10-1; Deleted Param. No. D061 (Table 10-1) and Param. No. D061A becomes D061; Added QFN Package Information; Revised Product Identification System; Added Figures 11-14, 11-15, 11-16, 11-7 to Char Data section; Other minor corrections; Removed Preliminary status.

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com