Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 25 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 8-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f508t-e-sn |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | General Description                                          | . 7 |

|-------|--------------------------------------------------------------|-----|

| 2.0   | General Description<br>PIC12F508/509/16F505 Device Varieties | . 9 |

| 3.0   | Architectural Overview                                       | 11  |

| 4.0   | Memory Organization                                          | 17  |

| 5.0   | I/O Port                                                     | 31  |

| 6.0   | Timer0 Module and TMR0 Register                              |     |

| 7.0   | Special Features Of The CPU                                  | 41  |

| 8.0   | Instruction Set Summary<br>Development Support               | 57  |

| 9.0   | Development Support                                          | 65  |

| 10.0  | Electrical Characteristics                                   | 69  |

| 11.0  | DC and AC Characteristics Graphs and Charts                  | 81  |

| 12.0  | Packaging Information                                        | 91  |

| Index | 1                                                            | 05  |

| Tho N | Aicrochin Web Site                                           | 07  |

| Custo | mer Change Notification Service                              | 07  |

| Custo | mer Support                                                  | 07  |

| Read  | er Response                                                  | 80  |

| Produ | ict Identification System                                    | 09  |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

### 2.0 PIC12F508/509/16F505 DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12F508/509/16F505 Product Identification System at the back of this data sheet to specify the correct part number.

#### 2.1 Quick Turn Programming (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who choose not to program medium-to-high quantity units and whose code patterns have stabilized. The devices are identical to the Flash devices but with all Flash locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.2 Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry code, password or ID number.

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC12F508/509/16F505 devices can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC12F508/509/16F505 devices use a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architectures where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12 bits wide, making it possible to have all single-word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle (200 ns @ 20 MHz, 1 µs @ 4 MHz) except for program branches.

Table 3-1 below lists program memory (Flash) and data memory (RAM) for the PIC12F508/509/16F505 devices.

TABLE 3-1: PIC12F508/509/16F505 MEMORY

| Device    | Memory    |        |  |  |

|-----------|-----------|--------|--|--|

| Device    | Program   | Data   |  |  |

| PIC12F508 | 512 x 12  | 25 x 8 |  |  |

| PIC12F509 | 1024 x 12 | 41 x 8 |  |  |

| PIC16F505 | 1024 x 12 | 72 x 8 |  |  |

The PIC12F508/509/16F505 devices can directly or indirectly address its register files and data memory. All Special Function Registers (SFR), including the PC, are mapped in the data memory. The PIC12F508/509/16F505 devices have a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any addressing mode. This symmetrical nature and lack of "special optimal situations" make programming with the PIC12F508/509/16F505 devices simple, yet efficient. In addition, the learning curve is reduced significantly.

The PIC12F508/509/16F505 devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, one operand is typically the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC) and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

Simplified block diagrams are shown in Figure 3-1 and Figure 3-2, with the corresponding pin described in Table 3-2 and Table 3-3.

| R/W-0           | R/W-0                                                                                                                                                     | R/W-0                                | 、<br>R-1        | R-1            | ,<br>R/W-x        | R/W-x             | R/W-x    |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|----------------|-------------------|-------------------|----------|

| RBWUF           | N/W-0                                                                                                                                                     |                                      | TO              | PD             | Z                 | -                 |          |

| bit 7           |                                                                                                                                                           | PA0                                  | 10              | PD             | Z                 | DC                | C        |

|                 |                                                                                                                                                           |                                      |                 |                |                   |                   | bit 0    |

| Legend:         |                                                                                                                                                           |                                      |                 |                |                   |                   |          |

| R = Readable    | bit                                                                                                                                                       | W = Writable                         | bit             | U = Unimpl     | emented bit, read | d as '0'          |          |

| -n = Value at I | POR                                                                                                                                                       | '1' = Bit is set                     |                 | '0' = Bit is c |                   | x = Bit is unkr   | nown     |

|                 |                                                                                                                                                           |                                      |                 |                |                   |                   |          |

| bit 7           | RBWUF: POF                                                                                                                                                | RTB Reset bit                        |                 |                |                   |                   |          |

|                 |                                                                                                                                                           | e to wake-up fro                     |                 | pin change     |                   |                   |          |

|                 | •                                                                                                                                                         | er-up or other f                     | Reset           |                |                   |                   |          |

| bit 6           | Reserved: Do                                                                                                                                              |                                      |                 |                |                   |                   |          |

| bit 5           | -                                                                                                                                                         | n Page Presele                       | Ct Dits         |                |                   |                   |          |

|                 | 1 = Page 1 (2<br>0 = Page 0 (0                                                                                                                            |                                      |                 |                |                   |                   |          |

|                 | Each page is                                                                                                                                              |                                      |                 |                |                   |                   |          |

|                 |                                                                                                                                                           |                                      |                 |                | devices which d   |                   |          |

|                 | ·                                                                                                                                                         |                                      | ed, since this  | may affect up  | ward compatibili  | ty with future pi | roducts. |

| bit 4           | TO: Time-Out                                                                                                                                              |                                      |                 |                |                   |                   |          |

|                 | <ul> <li>1 = After power-up, CLRWDT instruction, or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul>                                     |                                      |                 |                |                   |                   |          |

| bit 3           | PD: Power-Down bit                                                                                                                                        |                                      |                 |                |                   |                   |          |

|                 | 1 = After power-up or by the CLRWDT instruction                                                                                                           |                                      |                 |                |                   |                   |          |

|                 | 0 = By execution of the SLEEP instruction                                                                                                                 |                                      |                 |                |                   |                   |          |

| bit 2           | Z: Zero bit                                                                                                                                               |                                      |                 |                |                   |                   |          |

|                 | 1 = The result of an arithmetic or logic operation is zero                                                                                                |                                      |                 |                |                   |                   |          |

| h:+ 1           | <ul> <li>0 = The result of an arithmetic or logic operation is not zero</li> <li>DC: Digit Carry/Borrow bit (for ADDWF and SUBWF instructions)</li> </ul> |                                      |                 |                |                   |                   |          |

| bit 1           | ADDWF :                                                                                                                                                   | IV/DOITOW DIL (IG                    | JI ADDWF and    | I SUBME INSU   | ictions)          |                   |          |

|                 |                                                                                                                                                           | om the 4th low-                      | order bit of th | ne result occu | rred              |                   |          |

|                 | •                                                                                                                                                         | om the 4th low-                      |                 |                |                   |                   |          |

|                 | SUBWF:                                                                                                                                                    | · · · · · ·                          |                 |                |                   |                   |          |

|                 |                                                                                                                                                           | from the 4th lov<br>from the 4th lov |                 |                |                   |                   |          |

| bit 0           |                                                                                                                                                           | ow bit (for ADDI                     |                 |                |                   |                   |          |

|                 | ADDWF:                                                                                                                                                    | -                                    | JBWF:           |                | RRF OF RLF:       |                   |          |

|                 | 1 = A carry oc                                                                                                                                            | curred 1                             | = A borrow d    |                | Load bit with LS  | b or MSb, respe   | ectively |

|                 | 0 = A carry di                                                                                                                                            | d not occur 0                        | = A borrow o    | ccurred        |                   |                   |          |

## REGISTER 4-2: STATUS REGISTER (ADDRESS: 03h) (PIC16F505)

## 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all set.

| Note: | On the PIC12F508/509, I/O PORTB is ref- |

|-------|-----------------------------------------|

|       | erenced as GPIO. On the PIC16F505, I/O  |

|       | PORTB is referenced as PORTB.           |

#### 5.1 PORTB/GPIO

PORTB/GPIO is an 8-bit I/O register. Only the loworder 6 bits are used (RB/GP<5:0>). Bits 7 and 6 are unimplemented and read as '0's. Please note that RB3/ GP3 is an input only pin. The Configuration Word can set several I/O's to alternate functions. When acting as alternate functions, the pins will read as '0' during a port read. Pins RB0/GP0, RB1/GP1, RB3/GP3 and RB4 can be configured with weak pull-ups and also for wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If RB3/GP3/ MCLR is configured as MCLR, weak pull-up is always on and wake-up on change for this pin is not enabled.

## 5.2 PORTC (PIC16F505 Only)

PORTC is an 8-bit I/O register. Only the low-order 6 bits are used (RC<5:0>). Bits 7 and 6 are unimplemented and read as '0's.

| Note: | On power-up, TOCKI functionality is     |

|-------|-----------------------------------------|

|       | enabled in the OPTION register and must |

|       | be disabled to allow RC5 to be used as  |

|       | general purpose I/O.                    |

#### 5.3 TRIS Registers

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are RB3/GP3, which is input only and the TOCKI pin, which may be controlled by the OPTION register. See Register 4-3 and Register 4-4.

| Note: | A read of the ports reads the pins, not the    |

|-------|------------------------------------------------|

|       | output data latches. That is, if an output     |

|       | driver on a pin is enabled and driven high,    |

|       | but the external system is holding it low, a   |

|       | read of the port will indicate that the pin is |

|       | low.                                           |

The TRIS registers are "write-only" and are set (output drivers disabled) upon Reset.

## 5.4 I/O Interfacing

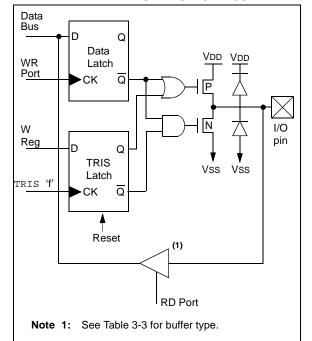

The equivalent circuit for an I/O port pin is shown in Figure 5-2. All port pins, except RB3/GP3 which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except RB3/GP3) can be programmed individually as input or output.

FIGURE 5-1:

#### PIC12F508/509/16F505 EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

# 7.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of real-time applications. The PIC12F508/509/16F505 microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These features are:

- Oscillator Selection

- Reset:

- Power-on Reset (POR)

- Device Reset Timer (DRT)

- Wake-up from Sleep on Pin Change

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

- Clock Out

The PIC12F508/509/16F505 devices have a Watchdog Timer, which can be shut off only through Configuration bit WDTE. It runs off of its own RC oscillator for added reliability. If using HS (PIC16F505), XT or LP selectable oscillator options, there is always an 18 ms (nominal) delay provided by the Device Reset Timer (DRT), intended to keep the chip in Reset until the crystal oscillator is stable. If using INTRC or EXTRC, there is an 18 ms delay only on VDD power-up. With this timer on-chip, most applications need no external Reset circuitry.

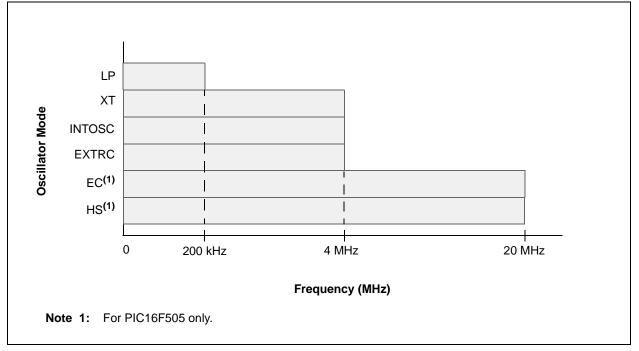

The Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through a change on input pins or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application, including an internal 4 MHz oscillator. The EXTRC oscillator option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options.

### 7.1 Configuration Bits

The PIC12F508/509/16F505 Configuration Words consist of 12 bits. Configuration bits can be programmed to select various device configurations. Three bits are for the selection of the oscillator type; (two bits on the PIC12F508/509), one bit is the Watchdog Timer enable bit, one bit is the MCLR enable bit and one bit is for code protection (Register 7-1, Register 7-2).

# TABLE 7-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR – PIC12F508/509/16F505<sup>(2)</sup>

| Osc<br>Type       | Resonator<br>Freq.                                                                                                                                                                                                                                                                                    | Cap. Range<br>C1           | Cap. Range<br>C2           |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|--|

| LP                | 32 kHz <sup>(1)</sup>                                                                                                                                                                                                                                                                                 | 15 pF                      | 15 pF                      |  |

| XT                | 200 kHz<br>1 MHz<br>4 MHz                                                                                                                                                                                                                                                                             | 47-68 pF<br>15 pF<br>15 pF | 47-68 pF<br>15 pF<br>15 pF |  |

| HS <sup>(3)</sup> | 20 MHz                                                                                                                                                                                                                                                                                                | 15-47 pF                   | 15-47 pF                   |  |

| Note 1:           | For VDD > 4.5V, C1 = C2 $\approx$ 30 pF is recommended.                                                                                                                                                                                                                                               |                            |                            |  |

| 2:                | These values are for design guidance<br>only. Rs may be required to avoid over-<br>driving crystals with low drive level specifi-<br>cation. Since each crystal has its own<br>characteristics, the user should consult<br>the crystal manufacturer for appropriate<br>values of external components. |                            |                            |  |

| 3:                | PIC16F505 only.                                                                                                                                                                                                                                                                                       |                            |                            |  |

#### 7.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

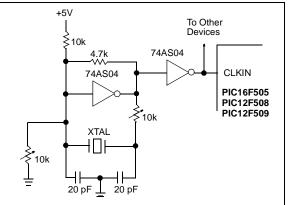

Figure 7-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

### FIGURE 7-3:

#### EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

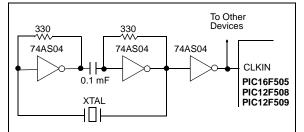

Figure 7-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

## 7.2.4 EXTERNAL RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit-to-unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 7-5 shows how the R/C combination is connected to the PIC12F508/509/16F505 devices. For REXT values below 3.0 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 5.0 k $\Omega$  and 100 k $\Omega$ .

### 7.5 Device Reset Timer (DRT)

On the PIC12F508/509/16F505 devices, the DRT runs any time the device is powered up. DRT runs from Reset and varies based on oscillator selection and Reset type (see Table 7-6).

The DRT operates on an internal RC oscillator. The processor is kept in Reset as long as the DRT is active. The DRT delay allows VDD to rise above VDD min. and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the devices in a Reset condition for approximately 18 ms after MCLR has reached a logic high (VIH MCLR) level. Programming (GP3/RB3)/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases. This allows savings in cost-sensitive and/or space restricted applications, as well as allowing the use of the (GP3/RB3)/MCLR/VPP pin as a general purpose input.

The Device Reset Time delays will vary from chip-tochip due to VDD, temperature and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out from Sleep. This is particularly important for applications using the WDT to wake from Sleep mode automatically.

Reset sources are POR, MCLR, WDT time-out and wake-up on pin change. See Section 7.9.2 "Wake-up from Sleep", Notes 1, 2 and 3.

## 7.6 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the external RC oscillator of the (GP5/RB5)/OSC1/CLKIN pin and the internal 4 MHz oscillator. This means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or Sleep, a WDT Reset or wake-up Reset, generates a device Reset.

The  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset.

The WDT can be permanently disabled by programming the configuration WDTE as a '0' (see **Section 7.1 "Configuration Bits"**). Refer to the PIC12F508/509/16F505 Programming Specifications to determine how to access the Configuration Word.

## TABLE 7-6:DRT (DEVICE RESET TIMER<br/>PERIOD)

| Oscillator<br>Configuration | POR Reset       | Subsequent<br>Resets |  |

|-----------------------------|-----------------|----------------------|--|

| INTOSC, EXTRC               | 18 ms (typical) | 10 μs (typical)      |  |

| HS <sup>(1)</sup> , XT, LP  | 18 ms (typical) | 18 ms (typical)      |  |

| EC <sup>(1)</sup>           | 18 ms (typical) | 10 μs (typical)      |  |

Note 1: PIC16F505 only.

#### 7.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, a time-out period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see DC specs).

Under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

#### 7.6.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the postscaler, if assigned to the WDT, and prevents it from timing out and generating a device Reset.

The SLEEP instruction resets the WDT and the postscaler, if assigned to the WDT. This gives the maximum Sleep time before a WDT wake-up Reset.

## 8.0 INSTRUCTION SET SUMMARY

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories.

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 12-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands** which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 8-1, while the various opcode fields are summarized in Table 8-1.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

#### TABLE 8-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                         |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                                |

| W             | Working register (accumulator)                                                                                                                                                      |

| b             | Bit address within an 8-bit file register                                                                                                                                           |

| k             | Literal field, constant data or label                                                                                                                                               |

| x             | Don't care location (= $0$ or $1$ )<br>The assembler will generate code with x = $0$ . It is<br>the recommended form of use for compatibility with<br>all Microchip software tools. |

| d             | Destination select;<br>d = 0 (store result in W)<br>d = 1 (store result in file register 'f')<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                          |

| TOS           | Top-of-Stack                                                                                                                                                                        |

| PC            | Program Counter                                                                                                                                                                     |

| WDT           | Watchdog Timer counter                                                                                                                                                              |

| TO            | Time-out bit                                                                                                                                                                        |

| PD            | Power-down bit                                                                                                                                                                      |

| dest          | Destination, either the W register or the specified register file location                                                                                                          |

| []            | Options                                                                                                                                                                             |

| ()            | Contents                                                                                                                                                                            |

| $\rightarrow$ | Assigned to                                                                                                                                                                         |

| < >           | Register bit field                                                                                                                                                                  |

| E             | In the set of                                                                                                                                                                       |

| italics       | User defined term (font is courier)                                                                                                                                                 |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Figure 8-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

## FIGURE 8-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                                                                   |        |       |                |      |

|------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|----------------|------|

| <u>11 6</u>                                                                                                                              | 5      | 4     |                | 0    |

| OPCODE                                                                                                                                   | d      |       | f (FILE #)     |      |

| d = 0 for destinati<br>d = 1 for destinati<br>f = 5-bit file regis                                                                       | on f   |       | s              |      |

| Bit-oriented file regist                                                                                                                 | ter op | erat  | ions           |      |

| <u>11 8</u>                                                                                                                              | 7      | 5     | 4              | 0    |

| OPCODE                                                                                                                                   | b (Bl  | T #)  | f (FILE #)     |      |

| <ul> <li>b = 3-bit bit address</li> <li>f = 5-bit file register address</li> <li>Literal and control operations (except GOTO)</li> </ul> |        |       |                |      |

| 11                                                                                                                                       | 8      | 7     |                | 0    |

| OPCODE                                                                                                                                   |        |       | k (literal)    |      |

| k = 8-bit immediate value                                                                                                                |        |       |                |      |

| Literal and control op                                                                                                                   | eratio | ons - | - GOTO instruc | tion |

| 11                                                                                                                                       | 9      | 8     |                | 0    |

| OPCODE k (literal)                                                                                                                       |        |       |                |      |

| k = 9-bit immediate value                                                                                                                |        |       |                |      |

| ADDWF            | Add W and f                                                                                                                                                                      |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                              |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                   |  |

| Operation:       | (W) + (f) $\rightarrow$ (dest)                                                                                                                                                   |  |

| Status Affected: | C, DC, Z                                                                                                                                                                         |  |

| Description:     | Add the contents of the W register<br>and register 'f'. If 'd' is'0', the result<br>is stored in the W register. If 'd' is<br>'1', the result is stored back in<br>register 'f'. |  |

| BCF              | Bit Clear f                                                        |  |  |

|------------------|--------------------------------------------------------------------|--|--|

| Syntax:          | [label] BCF f,b                                                    |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |  |  |

| Operation:       | $0 \rightarrow (f < b >)$                                          |  |  |

| Status Affected: | None                                                               |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                |  |  |

| ANDLW            | AND literal with W                                                                                                         |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                                   |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |

| Operation:       | (W).AND. (k) $\rightarrow$ (W)                                                                                             |  |  |  |  |

| Status Affected: | Z                                                                                                                          |  |  |  |  |

| Description:     | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |

| BSF              | Bit Set f                                                          |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                          |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is set.                                    |

| ANDWF            | AND W with f                                                                                                                                                                              |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                 |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                         |  |  |  |  |  |

| Description:     | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 'o',<br>the result is stored in the W register.<br>If 'd' is '1', the result is stored back<br>in register 'f'. |  |  |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                                                                    |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] BTFSC f,b                                                                                                                                                                                                                                                            |  |  |  |  |

| Operands:        | $0 \le f \le 31$ $0 \le b \le 7$                                                                                                                                                                                                                                             |  |  |  |  |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                                                                         |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                         |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', then the<br>next instruction is skipped.<br>If bit 'b' is '0', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded,<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |  |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                     |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] BTFSS f,b                                                                                                                                                                                                                                           |  |  |  |  |

| Operands:        | $0 \le f \le 31$<br>$0 \le b < 7$                                                                                                                                                                                                                           |  |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                     |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                        |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', then the next instruction is skipped.<br>If bit 'b' is '1', then the next instruction fetched during the current instruction execution, is discarded and a NOP is executed instead, making this a two-cycle instruction. |  |  |  |  |

| CLRW             | Clear W                                                                |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [ label ] CLRW                                                         |

| Operands:        | None                                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                      |

| Description:     | The W register is cleared. Zero bit (Z) is set.                        |

| CALL             | Subroutine Call                                                                                                                                                                                                                                                      |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                              |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                                                                                                    |  |  |  |  |

| Operation:       | (PC) + 1 $\rightarrow$ Top-of-Stack;<br>k $\rightarrow$ PC<7:0>;<br>(STATUS<6:5>) $\rightarrow$ PC<10:9>;<br>0 $\rightarrow$ PC<8>                                                                                                                                   |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                 |  |  |  |  |

| Description:     | Subroutine call. First, return<br>address (PC + 1) is PUSHed onto<br>the stack. The eight-bit immediate<br>address is loaded into PC<br>bits <7:0>. The upper bits<br>PC<10:9> are loaded from<br>STATUS<6:5>, PC<8> is cleared.<br>CALL is a two-cycle instruction. |  |  |  |  |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                                                    |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                                                                                          |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                    |  |  |  |  |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT;} \\ 0 \rightarrow \underline{\text{WDT}} \text{ prescaler (if assigned);} \\ 1 \rightarrow \overline{\text{TO};} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                  |  |  |  |  |

| Description:     | The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits $\overline{TO}$ and $\overline{PD}$ are set.                                   |  |  |  |  |

| CLRF             | Clear f                                                                |  |  |

|------------------|------------------------------------------------------------------------|--|--|

| Syntax:          | [label] CLRF f                                                         |  |  |

| Operands:        | $0 \le f \le 31$                                                       |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |  |  |

| Status Affected: | Z                                                                      |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.         |  |  |

| COMF             | Complement f                                                                                                                                                                |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] COMF f,d                                                                                                                                                            |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                            |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                                         |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back in<br>register 'f'. |  |  |  |  |

#### 10.2 DC Characteristics: PIC12F508/509/16F505 (Extended)

| DC Characteristics |      | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended) |       |                    |             |          |                                                                            |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|-------------|----------|----------------------------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                                                                                                         | Min.  | Typ <sup>(1)</sup> | Max.        | Units    | Conditions                                                                 |

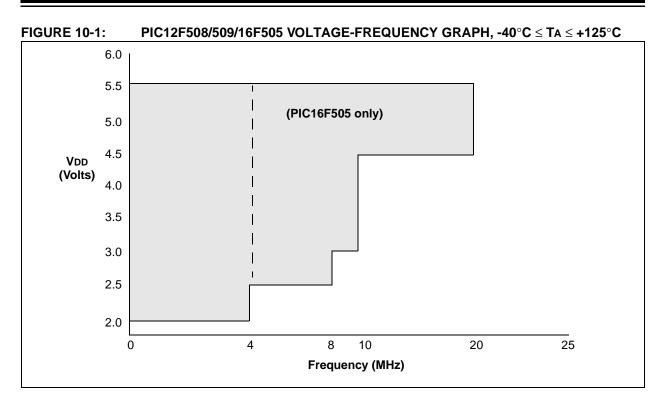

| D001               | Vdd  | Supply Voltage                                                                                                                         | 2.0   |                    | 5.5         | V        | See Figure 10-1                                                            |

| D002               | Vdr  | RAM Data Retention Voltage <sup>(2)</sup>                                                                                              | _     | 1.5*               |             | V        | Device in Sleep mode                                                       |

| D003               | VPOR | VDD Start Voltage to ensure<br>Power-on Reset                                                                                          | —     | Vss                | —           | V        | See Section 7.4 "Power-on<br>Reset (POR)" for details                      |

| D004               | SVDD | VDD Rise Rate to ensure<br>Power-on Reset                                                                                              | 0.05* | —                  | —           | V/ms     | See Section 7.4 "Power-on<br>Reset (POR)" for details                      |

| D010               | IDD  | Supply Current <sup>(3,4)</sup>                                                                                                        | _     | 175<br>0.625       | 275<br>1.1  | μA<br>mA | Fosc = 4 MHz, Vdd = 2.0V<br>Fosc = 4 MHz, Vdd = 5.0V                       |

|                    |      |                                                                                                                                        | _     | 500<br>1.5         | 650<br>2.2  | μA<br>mA | Fosc = 10 MHz, VDD = 3.0V<br>Fosc = 20 MHz, VDD = 5.0V<br>(PIC16F515 only) |

|                    |      |                                                                                                                                        | _     | 11<br>38           | 26<br>110   | μΑ<br>μΑ | Fosc = 32 kHz, VDD = 2.0V<br>Fosc = 32 kHz, VDD = 5.0V                     |

| D020               | IPD  | Power-down Current <sup>(5)</sup>                                                                                                      | _     | 0.1<br>0.35        | 9.0<br>15.0 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                   |

| D022               | Iwdt | WDT Current <sup>(5)</sup>                                                                                                             |       | 1.0<br>7.0         | 18<br>22    | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                   |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- 4: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- 5: For standby current measurements, the conditions are the same as IDD, except that the device is in Sleep mode. If a module current is listed, the current is for that specific module enabled and the device in Sleep.

### TABLE 10-6: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER – PIC12F508/509/16F505

|              |      |                                               |                                               | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended) |            |          |                                                  |

|--------------|------|-----------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|--------------------------------------------------|

| Param<br>No. | Sym. | Characteristic                                | Min. Typ <sup>(1)</sup> Max. Units Conditions |                                                                                                                                                                                        | Conditions |          |                                                  |

| 30           | TMCL | MCLR Pulse Width (low)                        | 2000*                                         | _                                                                                                                                                                                      | _          | ns       | VDD = 5.0V                                       |

| 31           | Twdt | Watchdog Timer Time-out Period (no prescaler) | 9*<br>9*                                      | 18*<br>18*                                                                                                                                                                             | 30*<br>40* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 32           | Tdrt | Device Reset Timer Period <sup>(2)</sup>      | 9*<br>9*                                      | 18*<br>18*                                                                                                                                                                             | 30*<br>40* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 34           | Tioz | I/O High-impedance from MCLR low              | —                                             | _                                                                                                                                                                                      | 2000*      | ns       |                                                  |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## 12.0 PACKAGING INFORMATION

## 12.1 Package Marking Information

#### 8-Lead PDIP

8-Lead SOIC (3.90 mm)

#### 8-Lead MSOP

8-Lead 2x3 DFN\*

| ХХХ |

|-----|

| YWW |

| NN  |

|     |

## Example

#### Example

| 12F509-I<br>/SN @30610 |  |

|------------------------|--|

| 017                    |  |

### Example

## Example

| BEQ |

|-----|

| 610 |

| 17  |

|     |

| Leger | nd: XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>*                                                                                                                                                                 | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line thus limiting the number of available characters<br>for customer specific information. |                                                                                                                                                                                                                                                                                                                                                                              |

\* Standard PIC<sup>®</sup> device marking consists of Microchip part number, year code, week code, and traceability code. For PIC device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

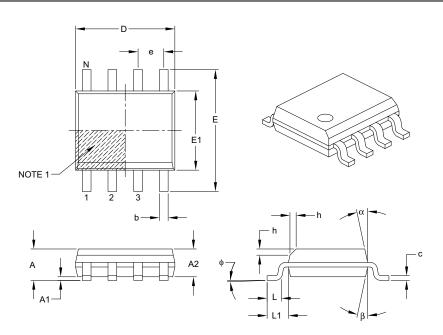

#### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units         |          | MILLIMETERS | 6    |

|--------------------------|---------------|----------|-------------|------|

| Dime                     | ension Limits | MIN      | NOM         | MAX  |

| Number of Pins           | N             |          | 8           |      |

| Pitch                    | е             |          | 1.27 BSC    |      |

| Overall Height           | А             | -        | -           | 1.75 |

| Molded Package Thickness | A2            | 1.25     | -           | -    |

| Standoff §               | A1            | 0.10     | -           | 0.25 |

| Overall Width            | E             |          | 6.00 BSC    |      |

| Molded Package Width     | E1            | 3.90 BSC |             |      |

| Overall Length           | D             |          | 4.90 BSC    |      |

| Chamfer (optional)       | h             | 0.25     | -           | 0.50 |

| Foot Length              | L             | 0.40     | -           | 1.27 |

| Footprint                | L1            |          | 1.04 REF    |      |

| Foot Angle               | ф             | 0°       | -           | 8°   |

| Lead Thickness           | С             | 0.17     | -           | 0.25 |

| Lead Width               | b             | 0.31     | _           | 0.51 |

| Mold Draft Angle Top     | α             | 5°       | _           | 15°  |

| Mold Draft Angle Bottom  | β             | 5°       | _           | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-057B

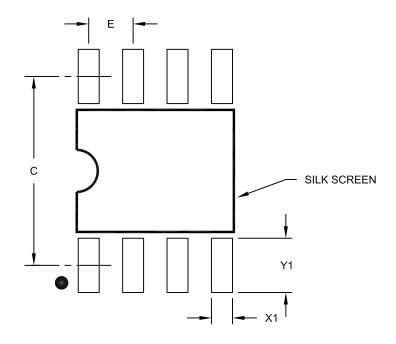

### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |     |          |      |

|----------------------------|-------------|-----|----------|------|

| Dimension                  | MIN         | NOM | MAX      |      |

| Contact Pitch E            |             |     | 1.27 BSC |      |

| Contact Pad Spacing        |             |     | 5.40     |      |

| Contact Pad Width (X8)     | X1          |     |          | 0.60 |

| Contact Pad Length (X8) Y1 |             |     |          | 1.55 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

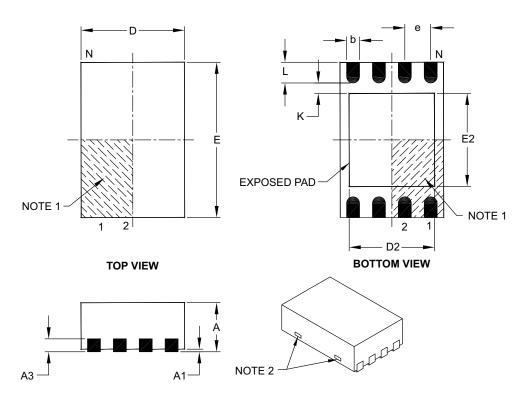

#### 8-Lead Plastic Dual Flat, No Lead Package (MC) – 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          |          | MILLIMETERS |  |  |

|------------------------|------------------|----------|----------|-------------|--|--|

|                        | Dimension Limits | MIN      | NOM      | MAX         |  |  |

| Number of Pins         | N                |          | 8        |             |  |  |

| Pitch                  | e                | 0.50 BSC |          |             |  |  |

| Overall Height         | A                | 0.80     | 0.90     | 1.00        |  |  |

| Standoff               | A1               | 0.00     | 0.02     | 0.05        |  |  |

| Contact Thickness      | A3               |          | 0.20 REF |             |  |  |

| Overall Length         | D                |          | 2.00 BSC |             |  |  |

| Overall Width          | E                |          | 3.00 BSC |             |  |  |

| Exposed Pad Length     | D2               | 1.30     | -        | 1.55        |  |  |

| Exposed Pad Width      | E2               | 1.50     | -        | 1.75        |  |  |

| Contact Width          | b                | 0.20     | 0.25     | 0.30        |  |  |

| Contact Length         | L                | 0.30     | 0.40     | 0.50        |  |  |

| Contact-to-Exposed Pad | К                | 0.20     | -        | _           |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

3. Package is saw singulated.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-123C

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:          | Technical Publications Manager         | Total Pages Sent                                       |

|--------------|----------------------------------------|--------------------------------------------------------|

| RE:          | Reader Response                        |                                                        |