#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.5KB (1K x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 41 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VFDFN Exposed Pad                                                      |

| Supplier Device Package    | 8-DFN (2x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f509-i-mc |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL00® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

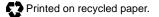

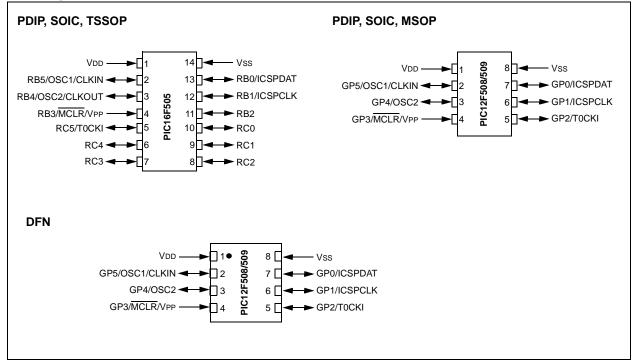

### Pin Diagrams

## PIC16F505 16-Pin Diagram (QFN)

### 2.0 PIC12F508/509/16F505 DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC12F508/509/16F505 Product Identification System at the back of this data sheet to specify the correct part number.

### 2.1 Quick Turn Programming (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who choose not to program medium-to-high quantity units and whose code patterns have stabilized. The devices are identical to the Flash devices but with all Flash locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

### 2.2 Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry code, password or ID number.

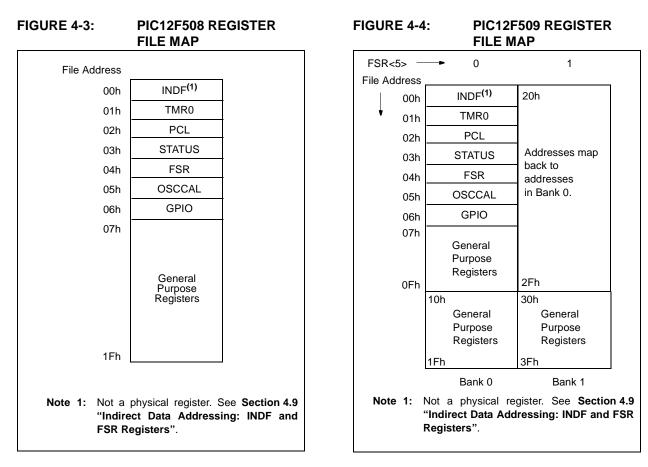

### FIGURE 4-5: PIC16F505 REGISTER FILE MAP

NOTES:

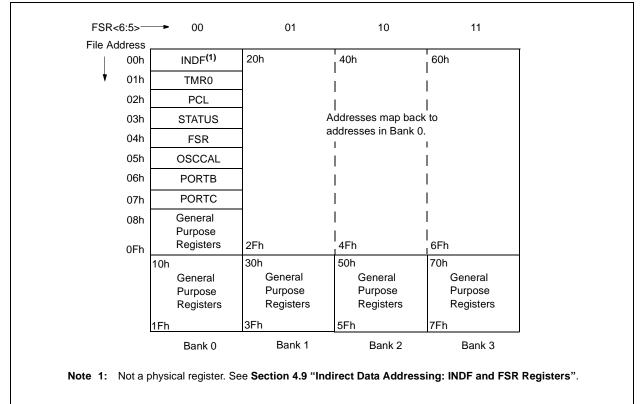

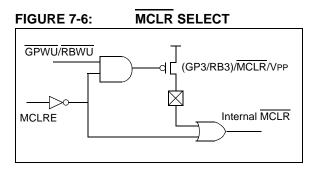

### 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select:

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1 "Using Timer0 with an External Clock".

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit, PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 6.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| PC<br>(Program<br>Counter)        | PC – 1 |            | Q1 Q2 Q3 Q4<br>PC + 1 | PC + 2      | (PC + 3     | $\frac{Q1}{Q2}\frac{Q3}{Q4}$ | PC + 5      | (PC+6)  |

|-----------------------------------|--------|------------|-----------------------|-------------|-------------|------------------------------|-------------|---------|

| Instruction<br>Fetch              |        | MOVWF TMR0 | MOVF TMR0,W           | MOVF TMR0,W | MOVF TMR0,W | MOVF TMR0,W                  | MOVF TMR0,W |         |

| Timer0<br>Instruction<br>Executed | (то)   | T0 + 1 )   | T0 + 2)               | Read TMR0   | NT0         | Read TMR0                    | NT0 + 1)∕   | NT0 + 2 |

### 7.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT time-out Reset during normal operation

- WDT time-out Reset during Sleep

- Wake-up from Sleep on pin change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up on pin change Reset during normal operation. They are not affected by a WDT Reset during Sleep or MCLR Reset during Sleep, since these Resets are viewed as resumption of normal operation. The exceptions to this are TO, PD and RBWUF/GPWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 7-4 for a full description of Reset states of all registers.

| Register           | Address | Power-on Reset           | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change |

|--------------------|---------|--------------------------|----------------------------------------------------|

| W                  | _       | qqqq qqqu <sup>(1)</sup> | qqqq qqqu <sup>(1)</sup>                           |

| INDF               | 00h     | XXXX XXXX                | uuuu uuuu                                          |

| TMR0               | 01h     | xxxx xxxx                | uuuu uuuu                                          |

| PC                 | 02h     | 1111 1111                | 1111 1111                                          |

| STATUS             | 03h     | 0001 1xxx                | q00q quuu <b>(2), (3)</b>                          |

| FSR <sup>(4)</sup> | 04h     | 110x xxxx                | 11uu uuuu                                          |

| FSR <sup>(5)</sup> | 04h     | 111x xxxx                | 111u uuuu                                          |

| OSCCAL             | 05h     | 1111 111-                | uuuu uuu-                                          |

| GPIO               | 06h     | xx xxxx                  | uu uuuu                                            |

| OPTION             | —       | 1111 1111                | 1111 1111                                          |

| TRIS               | —       | 11 1111                  | 11 1111                                            |

|                    |         |                          |                                                    |

### TABLE 7-3: RESET CONDITIONS FOR REGISTERS – PIC12F508/509

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

2: See Table 7-5 for Reset value for specific conditions.

**3:** If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

4: PIC12F509 only.

5: PIC12F508 only.

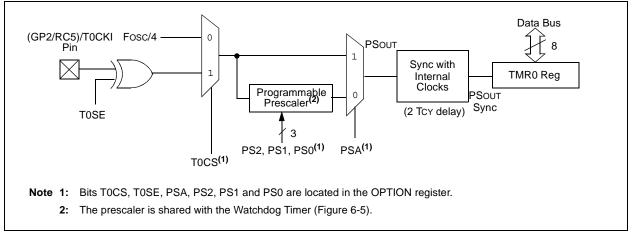

### 7.3.1 MCLR ENABLE

This Configuration bit, when unprogrammed (left in the '1' state), enables the external MCLR function. When programmed, the MCLR function is tied to the internal VDD and the pin is assigned to be an input only. See Figure 7-6.

### 7.4 Power-on Reset (POR)

The PIC12F508/509/16F505 devices incorporate an on-chip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the (GP3/RB3)/MCLR/VPP pin as MCLR and tie through a resistor to VDD, or program the pin as (GP3/RB3). An internal weak pull-up resistor is implemented using a transistor (refer to Table 10-2 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See **Section 10.0 "Electrical Characteristics"** for details.

When the devices start normal operation (exit the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the devices must be held in Reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-on Reset circuit is shown in Figure 7-7.

The Power-on Reset circuit and the Device Reset Timer (see **Section 7.5 "Device Reset Timer (DRT)**") circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will reset the Reset latch and thus end the on-chip Reset signal.

A power-up example where MCLR is held low is shown in Figure 7-8. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of Reset TDRT msec after MCLR goes high.

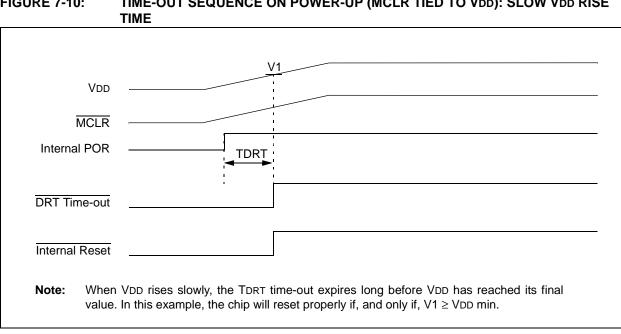

In Figure 7-9, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be (GP3/RB3). The VDD is stable before the start-up timer times out and there is no problem in getting a proper Reset. However, Figure 7-10 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 7-9).

| Note: | When the devices start normal operation     |

|-------|---------------------------------------------|

|       | (exit the Reset condition), device operat-  |

|       | ing parameters (voltage, frequency, tem-    |

|       | perature, etc.) must be met to ensure       |

|       | operation. If these conditions are not met, |

|       | the device must be held in Reset until the  |

|       | operating conditions are met.               |

For additional information, refer to Application Notes AN522 *"Power-Up Considerations"* (DS00522) and AN607 *"Power-up Trouble Shooting"* (DS00607).

### TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE **FIGURE 7-10:**

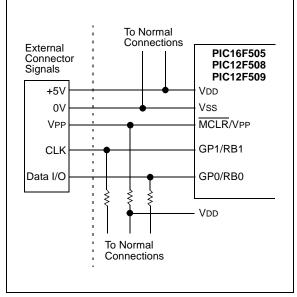

### FIGURE 7-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

### 8.0 INSTRUCTION SET SUMMARY

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories.

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 12-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands** which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 8-1, while the various opcode fields are summarized in Table 8-1.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

### TABLE 8-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                         |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                                |

| W             | Working register (accumulator)                                                                                                                                                      |

| b             | Bit address within an 8-bit file register                                                                                                                                           |

| k             | Literal field, constant data or label                                                                                                                                               |

| x             | Don't care location (= $0$ or $1$ )<br>The assembler will generate code with x = $0$ . It is<br>the recommended form of use for compatibility with<br>all Microchip software tools. |

| d             | Destination select;<br>d = 0 (store result in W)<br>d = 1 (store result in file register 'f')<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                          |

| TOS           | Top-of-Stack                                                                                                                                                                        |

| PC            | Program Counter                                                                                                                                                                     |

| WDT           | Watchdog Timer counter                                                                                                                                                              |

| TO            | Time-out bit                                                                                                                                                                        |

| PD            | Power-down bit                                                                                                                                                                      |

| dest          | Destination, either the W register or the specified register file location                                                                                                          |

| []            | Options                                                                                                                                                                             |

| ()            | Contents                                                                                                                                                                            |

| $\rightarrow$ | Assigned to                                                                                                                                                                         |

| < >           | Register bit field                                                                                                                                                                  |

| ∈             | In the set of                                                                                                                                                                       |

| italics       | User defined term (font is courier)                                                                                                                                                 |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Figure 8-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

# FIGURE 8-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                                                                   |        |      |             |   |

|------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-------------|---|

| <u>11 6</u>                                                                                                                              | 5      | 4    |             | 0 |

| OPCODE                                                                                                                                   | d      |      | f (FILE #)  |   |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 5-bit file register address                                                    |        |      |             |   |

| Bit-oriented file regist                                                                                                                 | ter op | erat | ions        |   |

| <u>11 8</u>                                                                                                                              | 7      | 5    | 4           | 0 |

| OPCODE                                                                                                                                   | b (Bl  | T #) | f (FILE #)  |   |

| <ul> <li>b = 3-bit bit address</li> <li>f = 5-bit file register address</li> <li>Literal and control operations (except GOTO)</li> </ul> |        |      |             |   |

| 11                                                                                                                                       | 8      | 7    |             | 0 |

| OPCODE                                                                                                                                   |        |      | k (literal) |   |

| k = 8-bit immediate value                                                                                                                |        |      |             |   |

| Literal and control operations – GOTO instruction                                                                                        |        |      |             |   |

| 11                                                                                                                                       | 9      | 8    |             | 0 |

| OPCODE k (literal)                                                                                                                       |        |      |             |   |

| k = 9-bit immediate value                                                                                                                |        |      |             |   |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSS f,b                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                                                             |

| Operation:       | skip if (f <b>) = <math>1</math></b>                                                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                                        |

| Description:     | If bit 'b' in register 'f' is '1', then the next instruction is skipped.<br>If bit 'b' is '1', then the next instruction fetched during the current instruction execution, is discarded and a NOP is executed instead, making this a two-cycle instruction. |

| CLRW             | Clear W                                                                |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [ label ] CLRW                                                         |

| Operands:        | None                                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                      |

| Description:     | The W register is cleared. Zero bit (Z) is set.                        |

| CALL             | Subroutine Call                                                                                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                              |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                                                                                                    |

| Operation:       | $(PC) + 1 \rightarrow$ Top-of-Stack;<br>k $\rightarrow$ PC<7:0>;<br>$(STATUS<6:5>) \rightarrow$ PC<10:9>;<br>0 $\rightarrow$ PC<8>                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                 |

| Description:     | Subroutine call. First, return<br>address (PC + 1) is PUSHed onto<br>the stack. The eight-bit immediate<br>address is loaded into PC<br>bits <7:0>. The upper bits<br>PC<10:9> are loaded from<br>STATUS<6:5>, PC<8> is cleared.<br>CALL is a two-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                                                    |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                                                                                    |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT;} \\ 0 \rightarrow \underline{\text{WDT}} \text{ prescaler (if assigned);} \\ 1 \rightarrow \overline{\text{TO};} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                                                                  |

| Description:     | The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits $\overline{TO}$ and $\overline{PD}$ are set.                                   |

| CLRF             | Clear f                                                                |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                         |

| Operands:        | $0 \le f \le 31$                                                       |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                      |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.         |

| COMF             | Complement f                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in \ [0,1] \end{array}$                                                                                                                |

| Operation:       | $(\overline{f})  ightarrow (dest)$                                                                                                                                          |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back in<br>register 'f'. |

### 10.3 Timing Parameter Symbology and Load Conditions – PIC12F508/509/16F505

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

2. TppS

| Т           |        |  |  |

|-------------|--------|--|--|

| F Frequency | T Time |  |  |

Lowercase subscripts (pp) and their meanings:

| рр      |                                 |     |                |

|---------|---------------------------------|-----|----------------|

| 2       | to                              | mc  | MCLR           |

| ck      | CLKOUT                          | osc | Oscillator     |

| су      | Cycle time                      | os  | OSC1           |

| drt     | Device Reset Timer              | tO  | ТОСКІ          |

| io      | I/O port                        | wdt | Watchdog Timer |

| Upperca | ase letters and their meanings: |     |                |

| S       |                                 |     |                |

| F       | Fall                            | Р   | Period         |

| н       | High                            | R   | Rise           |

| I       | Invalid (high-impedance)        | V   | Valid          |

| L       | Low                             | Z   | High-impedance |

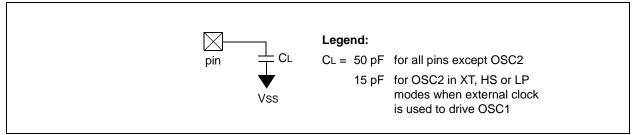

### FIGURE 10-3: LOAD CONDITIONS – PIC12F508/509/16F505

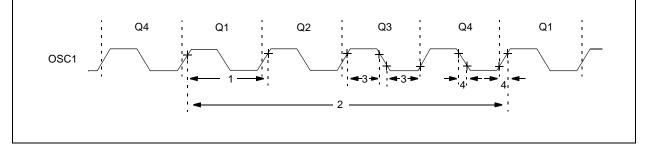

### FIGURE 10-4: EXTERNAL CLOCK TIMING – PIC12F508/509/16F505

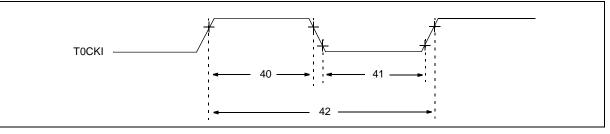

#### **FIGURE 10-7:** TIMER0 CLOCK TIMINGS - PIC12F508/509/16F505

### TABLE 10-7: TIMER0 CLOCK REQUIREMENTS - PIC12F508/509/16F505

| AC CHARACTERISTICS |      | Standard Operating Conditions (unless otherwise specified)         Operating Temperature       -40°C ≤ TA ≤ +85°C (industrial)         -40°C ≤ TA ≤ +125°C (extended)         Operating Voltage VDD range is described in         Section 10.1 "Power-on Reset (POR)" |                |                   |                    |      |       |                                                                |

|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|--------------------|------|-------|----------------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                                                                                                                                                                                                                                        |                | Min.              | Тур <sup>(1)</sup> | Max. | Units | Conditions                                                     |

| 40                 | Tt0H | T0CKI High Pulse                                                                                                                                                                                                                                                      | No Prescaler   | 0.5 TCY + 20*     | —                  | —    | ns    |                                                                |

|                    |      | Width                                                                                                                                                                                                                                                                 | With Prescaler | 10*               | _                  | _    | ns    |                                                                |

| 41 TtOL            | Tt0L | T0CKI Low Pulse                                                                                                                                                                                                                                                       | No Prescaler   | 0.5 TCY + 20*     | _                  | _    | ns    |                                                                |

|                    |      | Width                                                                                                                                                                                                                                                                 | With Prescaler | 10*               | —                  | _    | ns    |                                                                |

| 42                 | Tt0P | T0CKI Period                                                                                                                                                                                                                                                          | ·              | 20 or Tcy + 40* N | —                  | _    | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

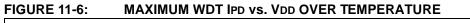

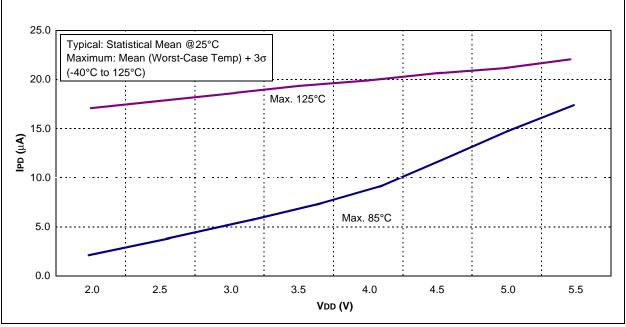

FIGURE 11-7: WDT TIME-OUT or DEVICE RESET TIMER vs. VDD OVER TEMPERATURE (NO WDT PRESCALER)<sup>(1)</sup>

the case of other types of Reset events.

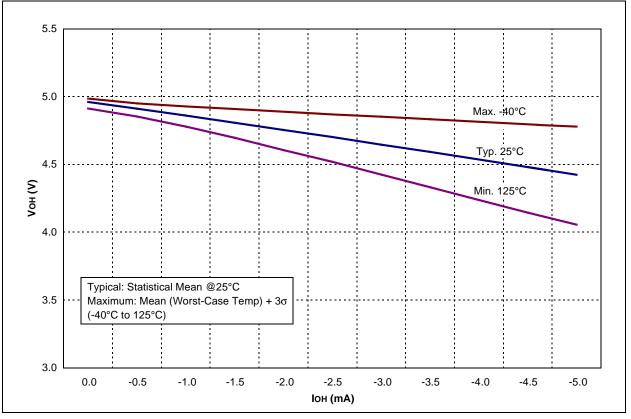

FIGURE 11-11: VOH VS. IOH OVER TEMPERATURE (VDD = 5.0V)

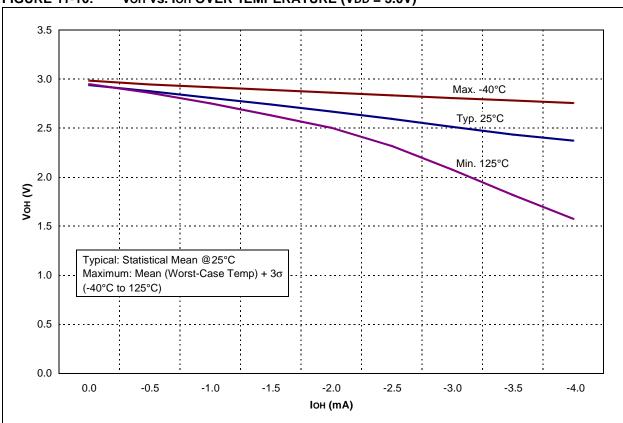

FIGURE 11-10: VOH vs. IOH OVER TEMPERATURE (VDD = 3.0V)

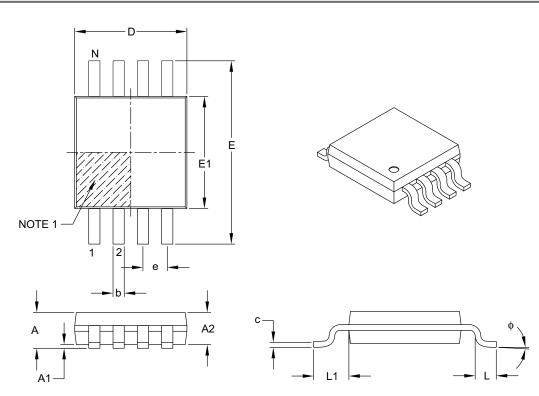

### 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |  |

|--------------------------|-------------|----------|----------|------|--|

| Dimension Limits         |             | MIN      | NOM      | MAX  |  |

| Number of Pins N         |             | 8        |          |      |  |

| Pitch                    | е           |          | 0.65 BSC |      |  |

| Overall Height           | Α           | -        | -        | 1.10 |  |

| Molded Package Thickness | A2          | 0.75     | 0.85     | 0.95 |  |

| Standoff                 | A1          | 0.00     | -        | 0.15 |  |

| Overall Width            | Е           |          | 4.90 BSC |      |  |

| Molded Package Width     | E1          |          | 3.00 BSC |      |  |

| Overall Length           | D           |          | 3.00 BSC |      |  |

| Foot Length              | L           | 0.40     | 0.60     | 0.80 |  |

| Footprint                | L1          | 0.95 REF |          |      |  |

| Foot Angle               | ¢           | 0°       | -        | 8°   |  |

| Lead Thickness           | с           | 0.08     | -        | 0.23 |  |

| Lead Width               | b           | 0.22     | -        | 0.40 |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111B

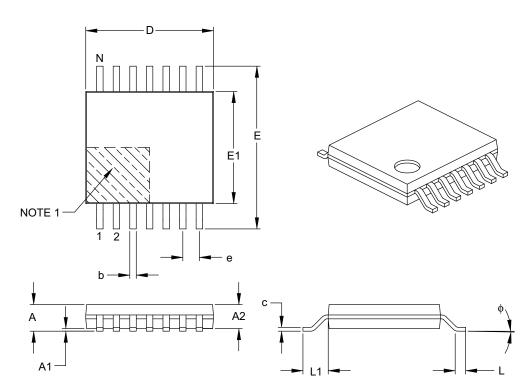

### 14-Lead Plastic Thin Shrink Small Outline (ST) – 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |          |          |      |  |  |

|--------------------------|------------------|----------|----------|------|--|--|

| Dimension Limits         |                  | MIN      | NOM      | MAX  |  |  |

| Number of Pins           | Number of Pins N |          | 14       |      |  |  |

| Pitch                    | е                | 0.65 BSC |          |      |  |  |

| Overall Height           | А                | _        | -        | 1.20 |  |  |

| Molded Package Thickness | A2               | 0.80     | 1.00     | 1.05 |  |  |

| Standoff                 | A1               | 0.05     | -        | 0.15 |  |  |

| Overall Width            | E                |          | 6.40 BSC |      |  |  |

| Molded Package Width     | E1               | 4.30     | 4.40     | 4.50 |  |  |

| Molded Package Length    | D                | 4.90     | 5.00     | 5.10 |  |  |

| Foot Length              | L                | 0.45     | 0.60     | 0.75 |  |  |

| Footprint                | L1               | 1.00 REF |          |      |  |  |

| Foot Angle               | ф                | 0°       | _        | 8°   |  |  |

| Lead Thickness           | С                | 0.09     | -        | 0.20 |  |  |

| Lead Width               | b                | 0.19     | -        | 0.30 |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-087B

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:                                             | Technical Publications Manager                                                | Total Pages Sent                                       |  |  |  |  |

|-------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| RE:                                             | Reader Response                                                               |                                                        |  |  |  |  |

| From                                            | n: Name                                                                       |                                                        |  |  |  |  |

|                                                 |                                                                               |                                                        |  |  |  |  |

|                                                 | Address                                                                       |                                                        |  |  |  |  |

|                                                 | City / State / ZIP / Country                                                  |                                                        |  |  |  |  |

|                                                 | Telephone: ()                                                                 | FAX: ()                                                |  |  |  |  |

| Appli                                           | cation (optional):                                                            |                                                        |  |  |  |  |

| Woul                                            | ld you like a reply?YN                                                        |                                                        |  |  |  |  |

| Devi                                            | ce: PIC12F508/509/16F505                                                      | Literature Number: DS41236E                            |  |  |  |  |

| Ques                                            | stions:                                                                       |                                                        |  |  |  |  |

| 1. What are the best features of this document? |                                                                               |                                                        |  |  |  |  |

|                                                 |                                                                               |                                                        |  |  |  |  |

| _                                               |                                                                               |                                                        |  |  |  |  |

| 2. ⊦                                            | How does this document meet your                                              | hardware and software development needs?               |  |  |  |  |

| _                                               |                                                                               |                                                        |  |  |  |  |

| _                                               |                                                                               |                                                        |  |  |  |  |

| 3. C                                            | 3. Do you find the organization of this document easy to follow? If not, why? |                                                        |  |  |  |  |

| _                                               |                                                                               |                                                        |  |  |  |  |

| -                                               |                                                                               |                                                        |  |  |  |  |

| 4. V                                            | What additions to the document do y                                           | you think would enhance the structure and subject?     |  |  |  |  |

| -                                               |                                                                               |                                                        |  |  |  |  |

|                                                 |                                                                               |                                                        |  |  |  |  |

| 5. V                                            | What deletions from the document c                                            | ould be made without affecting the overall usefulness? |  |  |  |  |

| _                                               |                                                                               |                                                        |  |  |  |  |

| -<br>-                                          | a thora any incorrect or micloading i                                         | nformation (what and whata)?                           |  |  |  |  |

| 0. I                                            | s there any incorrect or misleading i                                         | normation (what and where)?                            |  |  |  |  |

| _                                               |                                                                               |                                                        |  |  |  |  |

| _<br>7 ⊦                                        | How would you improve this docume                                             | ent?                                                   |  |  |  |  |

|                                                 |                                                                               |                                                        |  |  |  |  |

| -                                               |                                                                               |                                                        |  |  |  |  |

| -                                               |                                                                               |                                                        |  |  |  |  |