Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status Ac             | ctive                                                                  |

|-------------------------------|------------------------------------------------------------------------|

| Core Processor PIC            | с                                                                      |

| Core Size 8-I                 | Bit                                                                    |

| Speed 4M                      | ИНг                                                                    |

| Connectivity -                |                                                                        |

| Peripherals PC                | DR, WDT                                                                |

| Number of I/O 5               |                                                                        |

| Program Memory Size 1.5       | 5KB (1K x 12)                                                          |

| Program Memory Type FL        | ASH                                                                    |

| EEPROM Size -                 |                                                                        |

| RAM Size 41                   | L x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) 2V | / ~ 5.5V                                                               |

| Data Converters -             |                                                                        |

| Oscillator Type Int           | ternal                                                                 |

| Operating Temperature -40     | 0°C ~ 85°C (TA)                                                        |

| Mounting Type Su              | urface Mount                                                           |

| Package / Case 8-5            | SOIC (0.209", 5.30mm Width)                                            |

| Supplier Device Package 8-5   | SOIJ                                                                   |

| Purchase URL htt              | tps://www.e-xfl.com/product-detail/microchip-technology/pic12f509-i-sm |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

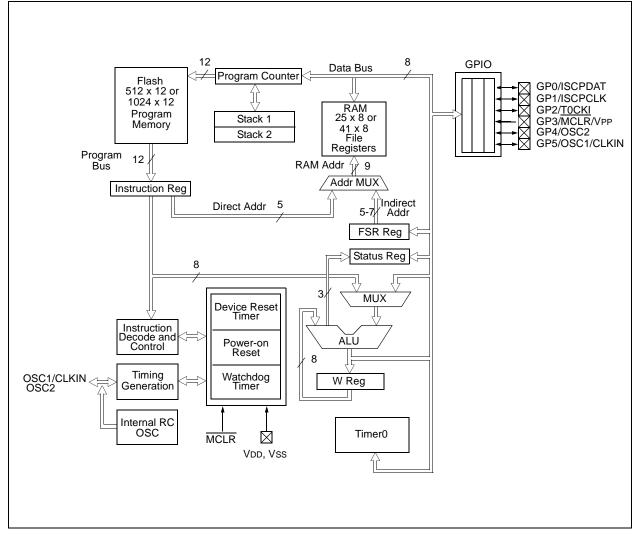

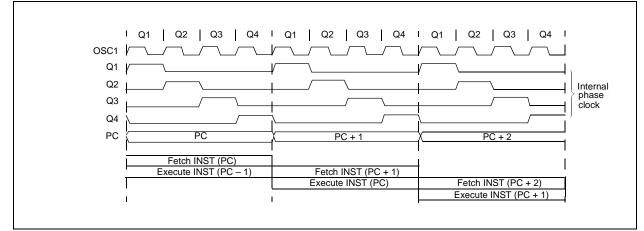

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the PC is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-3 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

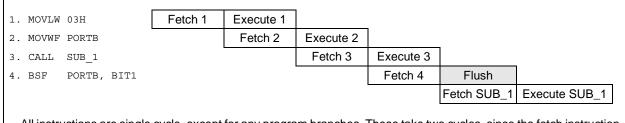

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

### 4.0 MEMORY ORGANIZATION

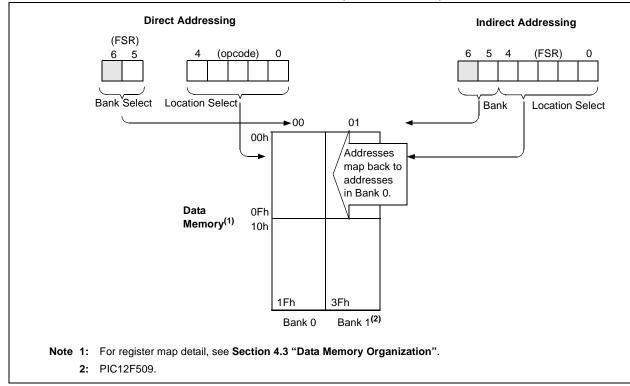

The PIC12F508/509/16F505 memories are organized into program memory and data memory. For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using one STATUS register bit. For the PIC12F509 and PIC16F505, with data memory register files of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Select Register (FSR).

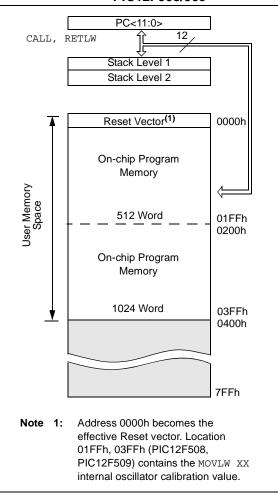

### 4.1 Program Memory Organization for the PIC12F508/509

The PIC12F508 device has a 10-bit Program Counter (PC) and PIC12F509 has a 11-bit Program Counter (PC) capable of addressing a 2K x 12 program memory space.

Only the first 512 x 12 (0000h-01FFh) for the PIC12F508, and 1K x 12 (0000h-03FFh) for the PIC12F509 are physically implemented (see Figure 4-1). Accessing a location above these boundaries will cause a wrap-around within the first 512 x 12 space (PIC12F508) or 1K x 12 space (PIC12F509). The effective Reset vector is a 0000h (see Figure 4-1). Location 01FFh (PIC12F508) and location 03FFh (PIC12F509) contain the internal clock oscillator calibration value. This value should never be overwritten.

#### FIGURE 4-1:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC12F508/509

#### 4.3.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1).

The Special Function Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

| TABLE 4-1: | SPECIAL FUNCTION REGISTER (SFR) SUMMARY (PIC12F508/509) |

|------------|---------------------------------------------------------|

|------------|---------------------------------------------------------|

| Address            | Name     | Bit 7                 | Bit 6      | Bit 5              | Bit 4     | Bit 3    | Bit 2     | Bit 1   | Bit 0 | Value on<br>Power-On<br>Reset <sup>(2)</sup> | Page # |

|--------------------|----------|-----------------------|------------|--------------------|-----------|----------|-----------|---------|-------|----------------------------------------------|--------|

| 00h                | INDF     | Uses Cor<br>register) | ntents of  | FSR to /           | Address   | Data Mer | mory (not | a physi | cal   | XXXX XXXX                                    | 28     |

| 01h                | TMR0     | 8-bit Real            | I-Time C   | lock/Cou           | unter     |          |           |         |       | xxxx xxxx                                    | 35     |

| 02h <sup>(1)</sup> | PCL      | Low-orde              | r 8 bits c | of PC              |           |          |           |         |       | 1111 1111                                    | 27     |

| 03h                | STATUS   | GPWUF                 | _          | PA0 <sup>(5)</sup> | TO        | PD       | Z         | DC      | С     | 0-01 1xxx <b>(3)</b>                         | 22     |

| 04h                | FSR      | Indirect D            | ata Men    | nory Add           | Iress Poi | inter    |           |         |       | 111x xxxx                                    | 28     |

| 04h <sup>(4)</sup> | FSR      | Indirect D            | ata Men    | nory Add           | lress Poi | inter    |           |         |       | 110x xxxx                                    | 28     |

| 05h                | OSCCAL   | CAL6                  | CAL5       | CAL4               | CAL3      | CAL2     | CAL1      | CAL0    | —     | 1111 111-                                    | 26     |

| 06h                | GPIO     | —                     | _          | GP5                | GP4       | GP3      | GP2       | GP1     | GP0   | xx xxxx                                      | 31     |

| N/A                | TRISGPIO | _                     | _          | I/O Con            | trol Regi | ister    |           |         |       | 11 1111                                      | 31     |

| N/A                | OPTION   | GPWU                  | GPPU       | TOCS               | TOSE      | PSA      | PS2       | PS1     | PS0   | 1111 1111                                    | 24     |

Legend: -= unimplemented, read as '0', x = unknown, u = unchanged, q = value depends on condition.

**Note 1:** The upper byte of the Program Counter is not directly accessible. See **Section 4.7** "**Program Counter**" for an explanation of how to access these bits.

- 2: Other (non Power-up) Resets include external Reset through MCLR, Watchdog Timer and wake-up on pin change Reset.

- 3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

4: PIC12F509 only.

5: This bit is used on the PIC12F509. For code compatibility do not use this bit on the PIC12F508.

#### 4.9 Indirect Data Addressing: INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### 4.9.1 INDIRECT ADDRESSING

- Register file 07 contains the value 10h

- Register file 08 contains the value 0Ah

- Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-1.

#### EXAMPLE 4-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT    | MOVLW<br>MOVWF<br>CLRF<br>INCF<br>BTFSC<br>GOTO | 0x10<br>FSR<br>INDF<br>FSR,F<br>FSR,4<br>NEXT | ;initialize pointer<br>;to RAM<br>;clear INDF<br>;register<br>;inc pointer<br>;all done?<br>;NO, clear next |

|---------|-------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| CONTINU | JE                                              |                                               |                                                                                                             |

|         | :                                               |                                               | ;YES, continue                                                                                              |

|         | :                                               |                                               |                                                                                                             |

|         |                                                 |                                               |                                                                                                             |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC12F508** – Does not use banking. FSR <7:5> are unimplemented and read as '1's.

**PIC12F509** – Uses FSR<5>. Selects between bank 0 and bank 1. FSR<7:6> are unimplemented, read as '1'.

**PIC16F505** – Uses FSR<6:5>. Selects from bank 0 to bank 3. FSR<7> is unimplemented, read as '1'.

#### FIGURE 4-7: DIRECT/INDIRECT ADDRESSING (PIC12F508/509)

### 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all set.

| Note: | On the PIC12F508/509, I/O PORTB is ref- |

|-------|-----------------------------------------|

|       | erenced as GPIO. On the PIC16F505, I/O  |

|       | PORTB is referenced as PORTB.           |

#### 5.1 PORTB/GPIO

PORTB/GPIO is an 8-bit I/O register. Only the loworder 6 bits are used (RB/GP<5:0>). Bits 7 and 6 are unimplemented and read as '0's. Please note that RB3/ GP3 is an input only pin. The Configuration Word can set several I/O's to alternate functions. When acting as alternate functions, the pins will read as '0' during a port read. Pins RB0/GP0, RB1/GP1, RB3/GP3 and RB4 can be configured with weak pull-ups and also for wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If RB3/GP3/ MCLR is configured as MCLR, weak pull-up is always on and wake-up on change for this pin is not enabled.

#### 5.2 PORTC (PIC16F505 Only)

PORTC is an 8-bit I/O register. Only the low-order 6 bits are used (RC<5:0>). Bits 7 and 6 are unimplemented and read as '0's.

| Note: | On power-up, TOCKI functionality is     |

|-------|-----------------------------------------|

|       | enabled in the OPTION register and must |

|       | be disabled to allow RC5 to be used as  |

|       | general purpose I/O.                    |

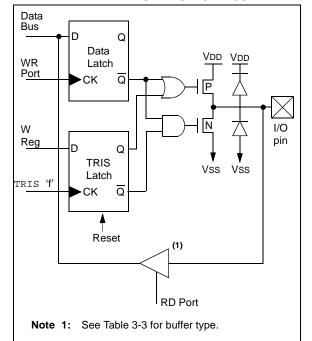

#### 5.3 TRIS Registers

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are RB3/GP3, which is input only and the TOCKI pin, which may be controlled by the OPTION register. See Register 4-3 and Register 4-4.

| Note: | A read of the ports reads the pins, not the    |

|-------|------------------------------------------------|

|       | output data latches. That is, if an output     |

|       | driver on a pin is enabled and driven high,    |

|       | but the external system is holding it low, a   |

|       | read of the port will indicate that the pin is |

|       | low.                                           |

The TRIS registers are "write-only" and are set (output drivers disabled) upon Reset.

#### 5.4 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-2. All port pins, except RB3/GP3 which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except RB3/GP3) can be programmed individually as input or output.

FIGURE 5-1:

#### PIC12F508/509/16F505 EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

#### FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

| PC<br>(Program<br>Counter)        | Q1 Q2 Q3 Q4<br>( | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4<br>(       | Q1 Q2 Q3 Q4<br>( | Q1 Q2 Q3 Q4            | Q1 Q2 Q3 Q4                | Q1 Q2 Q3 Q4<br>PC + 6 |

|-----------------------------------|------------------|-------------|-------------|------------------------|------------------|------------------------|----------------------------|-----------------------|

| Instruction<br>Fetch              | ,<br>1<br>1<br>1 | MOVWF TMR0  | MOVF TMR0,W | MOVF TMR0,W            | MOVF TMR0,W      | MOVF TMR0,W            | MOVF TMR0,W                |                       |

| Timer0<br>Instruction<br>Executed | (Υ               | T0 + 1      | Write TMR0  | Read TMR0<br>reads NT0 | NT0              | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | NT0 + 1               |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name                         | Bit 7    | Bit 6      | Bit 5                | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|------------------------------|----------|------------|----------------------|------------|-------|-------|-------|-----------|-------------------------------|---------------------------------|

| 01h     | TMR0                         | Timer0 – | 8-bit Real | I-Time Clock/Counter |            |       |       |       | xxxx xxxx | uuuu uuuu                     |                                 |

| N/A     | OPTION <sup>(1)</sup>        | GPWU     | GPPU       | TOCS                 | TOSE       | PSA   | PS2   | PS1   | PS0       | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup>        | RBWU     | RBPU       | TOCS                 | TOSE       | PSA   | PS2   | PS1   | PS0       | 1111 1111                     | 1111 1111                       |

| N/A     | TRISGPIO <sup>(1), (3)</sup> | _        | —          | I/O Con              | trol Regis | ster  | ter   |       |           | 11 1111                       | 11 1111                         |

| N/A     | TRISC <sup>(2), (3)</sup>    | _        | _          | RC5                  | RC4        | RC3   | RC2   | RC1   | RC0       | 11 1111                       | 11 1111                         |

**Legend:** Shaded cells are not used by Timer0. – = unimplemented, x = unknown, u = unchanged.

Note 1: PIC12F508/509 only.

2: PIC16F505 only.

3: The TRIS of the T0CKI pin is overridden when T0CS = 1.

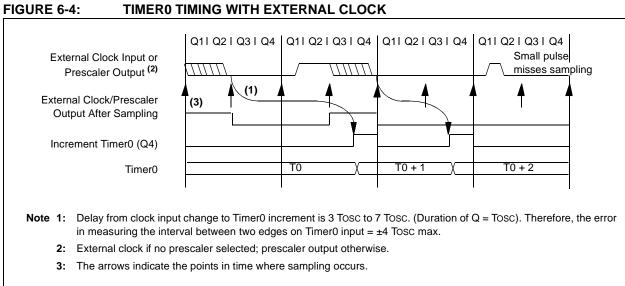

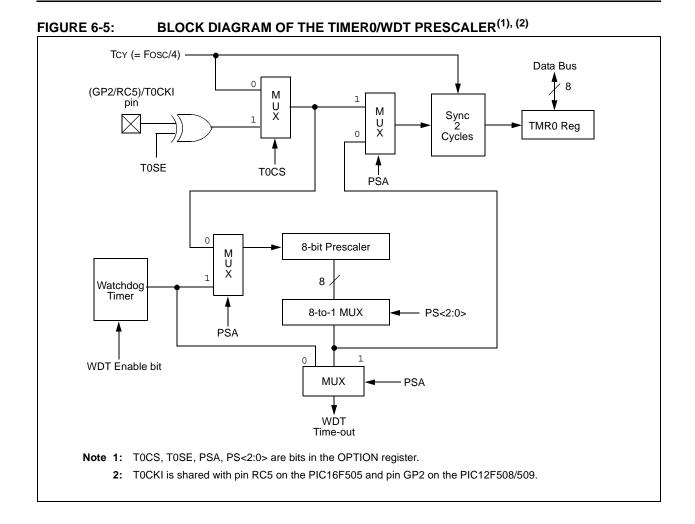

#### 6.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### EXTERNAL CLOCK 6.1.1 **SYNCHRONIZATION**

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 2 Tt0H) and low for at least 2 Tosc (and a small RC delay of 2 Tt0H). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4 Tosc (and a small RC delay of 4 Tt0H) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of Tt0H. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### TIMER0 INCREMENT DELAY 6.1.2

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-4 shows the delay from the external clock edge to the timer incrementing.

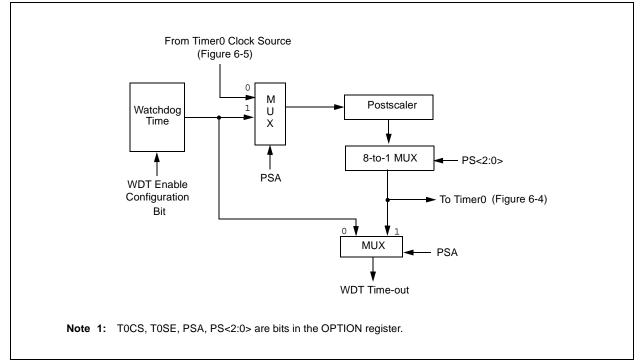

TABLE 7-7: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-----------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | OPTION <sup>(1)</sup> | GPWU  | GPPU  | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup> | RBWU  | RBPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: Shaded boxes = Not used by Watchdog Timer. - = unimplemented, read as '0', u = unchanged.

**Note 1:** PIC12F508/509 only.

2: PIC16F505 only.

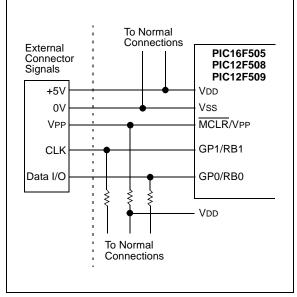

#### FIGURE 7-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| DC Cha       | racteri | stics                                         | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +85°C (industrial) |                    |             |          |                                                                            |  |  |

|--------------|---------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|----------|----------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym.    | Characteristic                                | Min.                                                                                                                          | Typ <sup>(1)</sup> | Max.        | Units    | Conditions                                                                 |  |  |

| D001         | Vdd     | Supply Voltage                                | 2.0                                                                                                                           |                    | 5.5         | V        | See Figure 10-1                                                            |  |  |

| D002         | Vdr     | RAM Data Retention Voltage <sup>(2)</sup>     |                                                                                                                               | 1.5*               | —           | V        | Device in Sleep mode                                                       |  |  |

| D003         | VPOR    | VDD Start Voltage to ensure<br>Power-on Reset | —                                                                                                                             | Vss                | —           | V        | See Section 7.4 "Power-on<br>Reset (POR)" for details                      |  |  |

| D004         | SVDD    | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*                                                                                                                         | —                  | —           | V/ms     | See Section 7.4 "Power-on<br>Reset (POR)" for details                      |  |  |

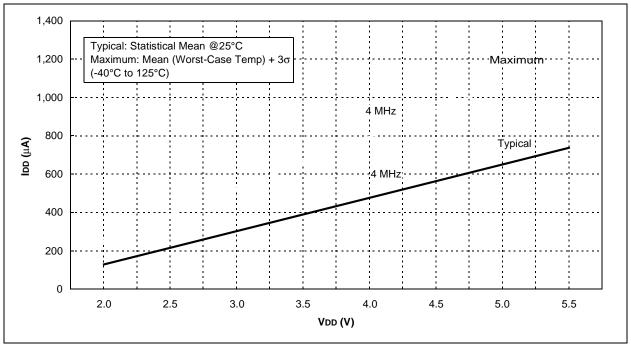

| D010         | Idd     | Supply Current <sup>(3,4)</sup>               | _                                                                                                                             | 175<br>0.625       | 275<br>1.1  | μA<br>mA | Fosc = 4 MHz, Vdd = 2.0V<br>Fosc = 4 MHz, Vdd = 5.0V                       |  |  |

|              |         |                                               | _                                                                                                                             | 500<br>1.5         | 650<br>2.2  | μA<br>mA | Fosc = 10 MHz, VDD = 3.0V<br>Fosc = 20 MHz, VDD = 5.0V<br>(PIC16F505 only) |  |  |

|              |         |                                               | _                                                                                                                             | 11<br>38           | 20<br>54    | μΑ<br>μΑ | Fosc = 32 kHz, VDD = 2.0V<br>Fosc = 32 kHz, VDD = 5.0V                     |  |  |

| D020         | IPD     | Power-down Current <sup>(5)</sup>             | —                                                                                                                             | 0.1<br>0.35        | 1.2<br>2.4  | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                   |  |  |

| D022         | Iwdt    | WDT Current <sup>(5)</sup>                    | _                                                                                                                             | 1.0<br>7.0         | 3.0<br>16.0 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                   |  |  |

#### 10.1 DC Characteristics: PIC12F508/509/16F505 (Industrial)

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- 4: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- 5: For standby current measurements, the conditions are the same as IDD, except that the device is in Sleep mode. If a module current is listed, the current is for that specific module enabled and the device in Sleep.

| AC CHA       | ARACTE | ERISTICS                                | Standard Operating Conditions (unless otherwise specified)         Operating Temperature       -40°C ≤ TA ≤ +85°C (industrial),         -40°C ≤ TA ≤ +125°C (extended)         Operating Voltage VDD range is described in Section 10.1 "Power-on Reset (POR)" |                    |        |       |                                            |  |  |  |

|--------------|--------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|-------|--------------------------------------------|--|--|--|

| Param<br>No. | Sym.   | Characteristic                          | Min.                                                                                                                                                                                                                                                           | Тур <sup>(1)</sup> | Max.   | Units | Conditions                                 |  |  |  |

| 1A           | Fosc   | External CLKIN Frequency <sup>(2)</sup> | DC                                                                                                                                                                                                                                                             | _                  | 4      | MHz   | XT Oscillator mode                         |  |  |  |

|              |        |                                         | DC                                                                                                                                                                                                                                                             | —                  | 20     | MHz   | EC, HS Oscillator mode<br>(PIC16F505 only) |  |  |  |

|              |        |                                         | DC                                                                                                                                                                                                                                                             | —                  | 200    | kHz   | LP Oscillator mode                         |  |  |  |

|              |        | Oscillator Frequency <sup>(2)</sup>     | —                                                                                                                                                                                                                                                              |                    | 4      | MHz   | EXTRC Oscillator mode                      |  |  |  |

|              |        |                                         | 0.1                                                                                                                                                                                                                                                            | —                  | 4      | MHz   | XT Oscillator mode                         |  |  |  |

|              |        |                                         | 4                                                                                                                                                                                                                                                              | —                  | 20     | MHz   | HS Oscillator mode (PIC16F505 only)        |  |  |  |

|              |        |                                         | —                                                                                                                                                                                                                                                              | —                  | 200    | kHz   | LP Oscillator mode                         |  |  |  |

| 1            | Tosc   | External CLKIN Period <sup>(2)</sup>    | 250                                                                                                                                                                                                                                                            | —                  | _      | ns    | XT Oscillator mode                         |  |  |  |

|              |        |                                         | 50                                                                                                                                                                                                                                                             | —                  | —      | ns    | EC, HS Oscillator mode<br>(PIC16F505 only) |  |  |  |

|              |        |                                         | 5                                                                                                                                                                                                                                                              |                    | —      | μs    | LP Oscillator mode                         |  |  |  |

|              |        | Oscillator Period <sup>(2)</sup>        | 250                                                                                                                                                                                                                                                            |                    | _      | ns    | EXTRC Oscillator mode                      |  |  |  |

|              |        |                                         | 250                                                                                                                                                                                                                                                            | —                  | 10,000 | ns    | XT Oscillator mode                         |  |  |  |

|              |        |                                         | 50                                                                                                                                                                                                                                                             | —                  | 250    | ns    | HS Oscillator mode (PIC16F505 only)        |  |  |  |

|              |        |                                         | 5                                                                                                                                                                                                                                                              | —                  | —      | μs    | LP Oscillator mode                         |  |  |  |

| 2            | Тсү    | Instruction Cycle Time                  | 200                                                                                                                                                                                                                                                            | 4/Fosc             |        | ns    |                                            |  |  |  |

| 3            | TosL,  | Clock in (OSC1) Low or High             | 50*                                                                                                                                                                                                                                                            | _                  | _      | ns    | XT Oscillator                              |  |  |  |

|              | TosH   | Time                                    | 2*                                                                                                                                                                                                                                                             | —                  | —      | μs    | LP Oscillator                              |  |  |  |

|              |        |                                         | 10*                                                                                                                                                                                                                                                            | —                  | —      | ns    | EC, HS Oscillator<br>(PIC16F505 only)      |  |  |  |

| 4            | TosR,  | Clock in (OSC1) Rise or Fall            | —                                                                                                                                                                                                                                                              | —                  | 25*    | ns    | XT Oscillator                              |  |  |  |

|              | TosF   | Time                                    | —                                                                                                                                                                                                                                                              | —                  | 50*    | ns    | LP Oscillator                              |  |  |  |

|              |        |                                         | —                                                                                                                                                                                                                                                              | _                  | 15*    | ns    | EC, HS Oscillator<br>(PIC16F505 only)      |  |  |  |

#### **TABLE 10-3**: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC12F508/509/16F505

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

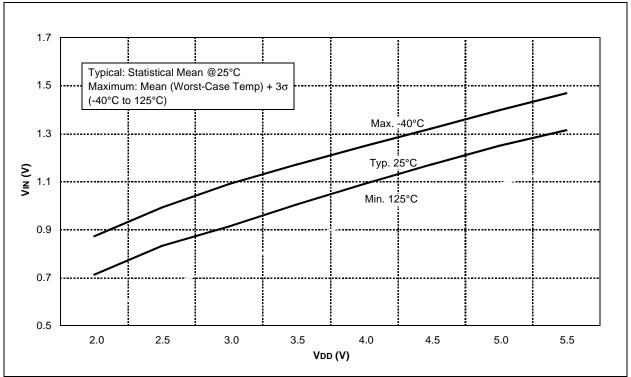

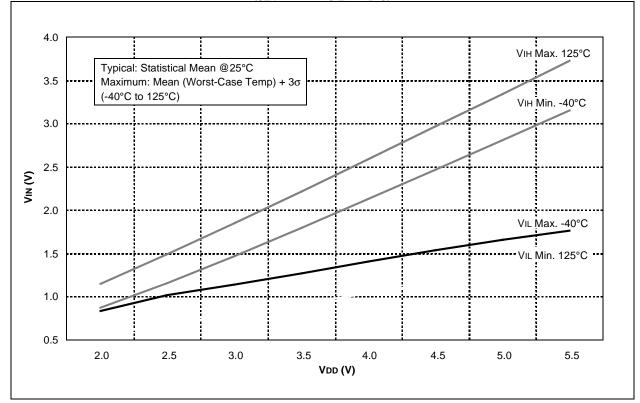

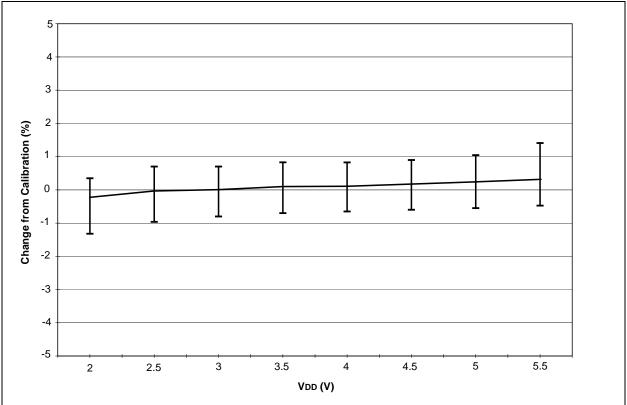

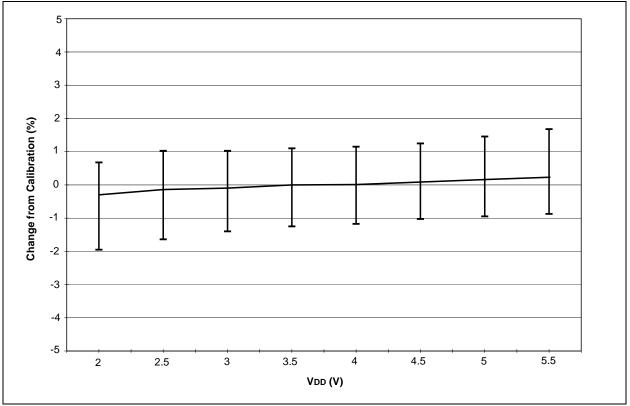

### 11.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where s is a standard deviation, over each temperature range.

FIGURE 11-1: IDD vs. VDD at Fosc = 4 MHz

#### 12.1 Package Marking Information (Continued)

| 14-Lead PDIP (300 mil) | Example                                    |  |  |

|------------------------|--------------------------------------------|--|--|

|                        | PIC16F505<br>) -I/P €3 0215<br>○ ☎ 0610017 |  |  |

#### 14-Lead SOIC (3.90 mm)

| Example                |  |

|------------------------|--|

| PIC16F505-E<br>/SL0125 |  |

| <b>1</b> 0610017       |  |

#### 14-Lead TSSOP (4.4 mm)

#### Example

| 16F505-I      |

|---------------|

| <b>1</b> 0610 |

| 017           |

#### 16-Lead QFN

Example

#### TABLE 12-1: 8-LEAD 2X3 DFN (MC) TOP MARKING

| Part Number          | Marking |

|----------------------|---------|

| PIC12F508 (T) - I/MC | BN0     |

| PIC12F508-E/MC       | BP0     |

| PIC12F509 (T) - I/MC | BQ0     |

| PIC12F509-E/MC       | BR0     |

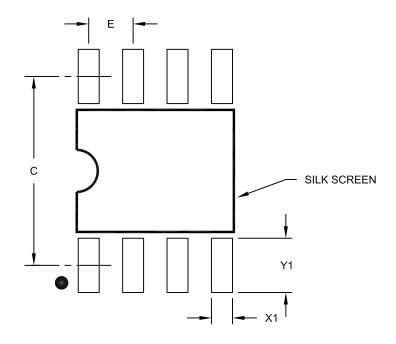

#### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

| Units                   |    | MILLIMETERS |      |      |  |

|-------------------------|----|-------------|------|------|--|

| Dimension Limits        |    | MIN         | NOM  | MAX  |  |

| Contact Pitch           | E  | 1.27 BSC    |      |      |  |

| Contact Pad Spacing     | С  |             | 5.40 |      |  |

| Contact Pad Width (X8)  | X1 |             |      | 0.60 |  |

| Contact Pad Length (X8) | Y1 |             |      | 1.55 |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com