#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               |                                                                           |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                |                                                                           |

| RAM Size                   | 41 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VFDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN (2x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f509t-i-mc |

|                            |                                                                           |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8/14-Pin, 8-Bit Flash Microcontrollers

# **Devices Included In This Data Sheet:**

• PIC12F508 • PIC12F509 • PIC16F505

# High-Performance RISC CPU:

- Only 33 Single-Word Instructions to Learn

- All Single-Cycle Instructions Except for Program Branches, which are Two-Cycle

- 12-Bit Wide Instructions

- 2-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes for Data and Instructions

- 8-Bit Wide Data Path

- 8 Special Function Hardware Registers

- Operating Speed:

- DC 20 MHz clock input (PIC16F505 only)

- DC 200 ns instruction cycle (PIC16F505 only)

- DC 4 MHz clock input

- DC 1000 ns instruction cycle

### **Special Microcontroller Features:**

- 4 MHz Precision Internal Oscillator:

- Factory calibrated to ±1%

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Debugging (ICD) Support

- Power-On Reset (POR)

- Device Reset Timer (DRT)

- Watchdog Timer (WDT) with Dedicated On-Chip RC Oscillator for Reliable Operation

- Programmable Code Protection

- Multiplexed MCLR Input Pin

- Internal Weak Pull-Ups on I/O Pins

- Power-Saving Sleep mode

- Wake-Wp from Sleep on Pin Change

- Selectable Oscillator Options:

- INTRC: 4 MHz precision Internal oscillator

- EXTRC: External low-cost RC oscillator

- XT: Standard crystal/resonator

- HS: High-speed crystal/resonator (PIC16F505 only)

- LP: Power-saving, low-frequency crystal

- EC: High-speed external clock input (PIC16F505 only)

### Low-Power Features/CMOS Technology:

- Operating Current:

- < 175 μA @ 2V, 4 MHz, typical

- Standby Current:

- 100 nA @ 2V, typical

- Low-Power, High-Speed Flash Technology:

- 100,000 Flash endurance

- > 40 year retention

- Fully Static Design

- Wide Operating Voltage Range: 2.0V to 5.5V

- Wide Temperature Range:

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

### Peripheral Features (PIC12F508/509):

- 6 I/O Pins:

- 5 I/O pins with individual direction control

- 1 input only pin

- High current sink/source for direct LED drive

- Wake-on-change

- Weak pull-ups

- 8-Bit Real-Time Clock/Counter (TMR0) with 8-Bit Programmable Prescaler

# Peripheral Features (PIC16F505):

- 12 I/O Pins:

- 11 I/O pins with individual direction control

- 1 input only pin

- High current sink/source for direct LED drive

- Wake-on-change

- Weak pull-ups

- 8-Bit Real-Time Clock/Counter (TMR0) with 8-Bit Programmable Prescaler

NOTES:

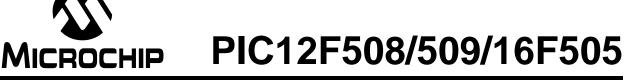

### 4.2 Program Memory Organization For The PIC16F505

The PIC16F505 device has a 11-bit Program Counter (PC) capable of addressing a 2K x 12 program memory space.

The 1K x 12 (0000h-03FFh) for the PIC16F505 are physically implemented. Refer to Figure 4-2. Accessing a location above this boundary will cause a wrap-around within the first 1K x 12 space. The effective Reset vector is at 0000h (see Figure 4-2). Location 03FFh contains the internal oscillator calibration value. This value should never be overwritten.

#### FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR THE PIC16F505

## 4.3 Data Memory Organization

Data memory is composed of registers or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers (SFR) and General Purpose Registers (GPR).

The Special Function Registers include the TMR0 register, the Program Counter (PCL), the STATUS register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Function Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC12F508/509, the register file is composed of 7 Special Function Registers, 9 General Purpose Registers and 16 or 32 General Purpose Registers accessed by banking (see Figure 4-3 and Figure 4-4).

For the PIC16F505, the register file is composed of 8 Special Function Registers, 8 General Purpose Registers and 64 General Purpose Registers accessed by banking (Figure 4-5).

### 4.3.1 GENERAL PURPOSE REGISTER FILE

The General Purpose Register file is accessed, either directly or indirectly, through the File Select Register (FSR). See Section 4.9 "Indirect Data Addressing: INDF and FSR Registers".

### 4.3.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1).

The Special Function Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

| TABLE 4-1: | SPECIAL FUNCTION REGISTER (SFR) SUMMARY (PIC12F508/509) |

|------------|---------------------------------------------------------|

|------------|---------------------------------------------------------|

| Address            | Name     | Bit 7                                                                 | Bit 6      | Bit 5              | Bit 4     | Bit 3 | Bit 2 | Bit 1     | Bit 0 | Value on<br>Power-On<br>Reset <sup>(2)</sup> | Page # |

|--------------------|----------|-----------------------------------------------------------------------|------------|--------------------|-----------|-------|-------|-----------|-------|----------------------------------------------|--------|

| 00h                | INDF     | Uses Contents of FSR to Address Data Memory (not a physical register) |            |                    |           |       | cal   | XXXX XXXX | 28    |                                              |        |

| 01h                | TMR0     | 8-bit Real                                                            | I-Time C   | lock/Cou           | unter     |       |       |           |       | xxxx xxxx                                    | 35     |

| 02h <sup>(1)</sup> | PCL      | Low-orde                                                              | r 8 bits c | of PC              |           |       |       |           |       | 1111 1111                                    | 27     |

| 03h                | STATUS   | GPWUF                                                                 | _          | PA0 <sup>(5)</sup> | TO        | PD    | Z     | DC        | С     | 0-01 1xxx <b>(3)</b>                         | 22     |

| 04h                | FSR      | Indirect Data Memory Address Pointer 111                              |            |                    |           |       |       | 111x xxxx | 28    |                                              |        |

| 04h <sup>(4)</sup> | FSR      | Indirect D                                                            | ata Men    | nory Add           | lress Poi | inter |       |           |       | 110x xxxx                                    | 28     |

| 05h                | OSCCAL   | CAL6                                                                  | CAL5       | CAL4               | CAL3      | CAL2  | CAL1  | CAL0      | —     | 1111 111-                                    | 26     |

| 06h                | GPIO     | —                                                                     | _          | GP5                | GP4       | GP3   | GP2   | GP1       | GP0   | xx xxxx                                      | 31     |

| N/A                | TRISGPIO | _                                                                     | _          | I/O Con            | trol Regi | ister |       |           |       | 11 1111                                      | 31     |

| N/A                | OPTION   | GPWU                                                                  | GPPU       | TOCS               | TOSE      | PSA   | PS2   | PS1       | PS0   | 1111 1111                                    | 24     |

Legend: -= unimplemented, read as '0', x = unknown, u = unchanged, q = value depends on condition.

**Note 1:** The upper byte of the Program Counter is not directly accessible. See **Section 4.7** "**Program Counter**" for an explanation of how to access these bits.

- 2: Other (non Power-up) Resets include external Reset through MCLR, Watchdog Timer and wake-up on pin change Reset.

- 3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

4: PIC12F509 only.

5: This bit is used on the PIC12F509. For code compatibility do not use this bit on the PIC12F508.

| R/W-0           | R/W-0                          | R/W-0                                | 、<br>R-1        | R-1            | ,<br>R/W-x        | R/W-x             | R/W-x    |

|-----------------|--------------------------------|--------------------------------------|-----------------|----------------|-------------------|-------------------|----------|

| RBWUF           | N/W-0                          |                                      | TO              | PD             | Z                 | -                 |          |

| bit 7           |                                | PA0                                  | 10              | PD             | Z                 | DC                | C        |

|                 |                                |                                      |                 |                |                   |                   | bit 0    |

| Legend:         |                                |                                      |                 |                |                   |                   |          |

| R = Readable    | bit                            | W = Writable                         | bit             | U = Unimpl     | emented bit, read | d as '0'          |          |

| -n = Value at I | POR                            | '1' = Bit is set                     |                 | '0' = Bit is c |                   | x = Bit is unkr   | nown     |

|                 |                                |                                      |                 |                |                   |                   |          |

| bit 7           | RBWUF: POF                     | RTB Reset bit                        |                 |                |                   |                   |          |

|                 |                                | e to wake-up fro                     |                 | pin change     |                   |                   |          |

|                 | •                              | er-up or other f                     | Reset           |                |                   |                   |          |

| bit 6           | Reserved: Do                   |                                      |                 |                |                   |                   |          |

| bit 5           | -                              | n Page Presele                       | Ct Dits         |                |                   |                   |          |

|                 | 1 = Page 1 (2<br>0 = Page 0 (0 |                                      |                 |                |                   |                   |          |

|                 | Each page is                   |                                      |                 |                |                   |                   |          |

|                 |                                |                                      |                 |                | devices which d   |                   |          |

|                 | ·                              |                                      | ed, since this  | may affect up  | ward compatibili  | ty with future pi | roducts. |

| bit 4           | TO: Time-Out                   |                                      |                 |                |                   |                   |          |

|                 |                                | er-up, CLRWDT                        |                 | r sleep instr  | uction            |                   |          |

| bit 3           | PD: Power-Do                   |                                      |                 |                |                   |                   |          |

|                 | 1 = After pow                  | er-up or by the                      | CLRWDT inst     | ruction        |                   |                   |          |

|                 | 0 = By execut                  | tion of the SLEI                     | EP instruction  |                |                   |                   |          |

| bit 2           | Z: Zero bit                    |                                      |                 |                |                   |                   |          |

|                 |                                | t of an arithmet                     |                 |                |                   |                   |          |

| h:+ 1           |                                | t of an arithmet                     |                 |                |                   |                   |          |

| bit 1           | ADDWF :                        | ry/Borrow bit (fe                    | JI ADDWF and    | I SUBME INSU   | ictions)          |                   |          |

|                 |                                | om the 4th low-                      | order bit of th | ne result occu | rred              |                   |          |

|                 | •                              | om the 4th low-                      |                 |                |                   |                   |          |

|                 | SUBWF:                         | · · · · · ·                          |                 |                |                   |                   |          |

|                 |                                | from the 4th lov<br>from the 4th lov |                 |                |                   |                   |          |

| bit 0           |                                | ow bit (for ADDI                     |                 |                |                   |                   |          |

|                 | ADDWF:                         | -                                    | JBWF:           |                | RRF OF RLF:       |                   |          |

|                 | 1 = A carry oc                 | curred 1                             | = A borrow d    |                | Load bit with LS  | b or MSb, respe   | ectively |

|                 | 0 = A carry di                 | d not occur 0                        | = A borrow o    | ccurred        |                   |                   |          |

# REGISTER 4-2: STATUS REGISTER (ADDRESS: 03h) (PIC16F505)

#### 4.5 **OPTION Register**

The OPTION register is a 8-bit wide, write-only register, which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A Reset sets the OPTION<7:0> bits.

- Note: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin (i.e., note that TRIS overrides Option control of GPPU/RBPU and GPWU/RBWU).

- If the TOCS bit is set to '1', it will override Note: the TRIS function on the T0CKI pin.

#### **REGISTER 4-3: OPTION REGISTER (PIC12F508/509)**

|               |                                                                                                                                                                             |                                                   | •              | ,                |                  |                    |       |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------|------------------|------------------|--------------------|-------|--|

| W-1           | W-1                                                                                                                                                                         | W-1                                               | W-1            | W-1              | W-1              | W-1                | W-1   |  |

| GPWU          | GPPU                                                                                                                                                                        | TOCS                                              | TOSE           | PSA              | PS2              | PS1                | PS0   |  |

| bit 7         |                                                                                                                                                                             |                                                   |                |                  |                  |                    | bit ( |  |

| Legend:       |                                                                                                                                                                             |                                                   |                |                  |                  |                    |       |  |

| R = Readable  | e bit                                                                                                                                                                       | W = Writable                                      | bit            | U = Unimpler     | mented bit, read | d as '0'           |       |  |

| -n = Value at | POR                                                                                                                                                                         | '1' = Bit is set                                  |                | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

| bit 7         | <b>GPWU:</b> Enab<br>1 = Disabled<br>0 = Enabled                                                                                                                            | le Wake-up on                                     | Pin Change     | bit (GP0, GP1,   | GP3)             |                    |       |  |

| bit 6         | <b>GPPU</b> : Enabl<br>1 = Disabled<br>0 = Enabled                                                                                                                          | e Weak Pull-up                                    | os bit (GP0, C | GP1, GP3)        |                  |                    |       |  |

| bit 5         | <b>TOCS</b> : Timer0 Clock Source Select bit<br>1 = Transition on T0CKI pin (overrides TRIS on the T0CKI pin)<br>0 = Transition on internal instruction cycle clock, Fosc/4 |                                                   |                |                  |                  |                    |       |  |

| bit 4         | <b>T0SE</b> : Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on the T0CKI pin<br>0 = Increment on low-to-high transition on the T0CKI pin         |                                                   |                |                  |                  |                    |       |  |

| bit 3         | 1 = Prescaler                                                                                                                                                               | er Assignment<br>assigned to th<br>assigned to Ti | e WDT          |                  |                  |                    |       |  |

| L:L 0 0       |                                                                                                                                                                             |                                                   | 1 . 1 .        |                  |                  |                    |       |  |

bit 2-0 PS<2:0>: Prescaler Rate Select bits

| Bit Value | Timer0 Rate | WDT Rate |

|-----------|-------------|----------|

| 000       | 1:2         | 1:1      |

| 001       | 1:4         | 1:2      |

| 010       | 1:8         | 1:4      |

| 010 | 1:8     | 1:4     |

|-----|---------|---------|

| 011 | 1:16    | 1:8     |

| 100 | 1:32    | 1:16    |

| 101 | 1:64    | 1:32    |

| 110 | 1 : 128 | 1:64    |

| 111 | 1 : 256 | 1 : 128 |

NOTES:

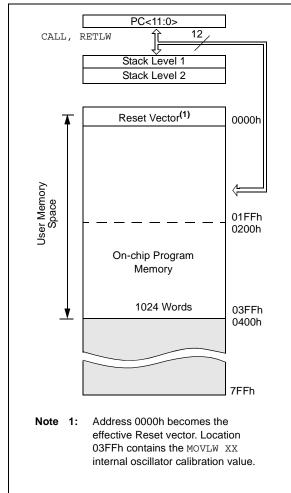

# 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select:

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1 "Using Timer0 with an External Clock".

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit, PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 6.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| PC<br>(Program<br>Counter)        | PC – 1 |            | Q1 Q2 Q3 Q4<br>PC + 1 | PC + 2      | (PC + 3     | (PC + 4)    | PC + 5      | (PC+6)  |

|-----------------------------------|--------|------------|-----------------------|-------------|-------------|-------------|-------------|---------|

| Instruction<br>Fetch              |        | MOVWF TMR0 | MOVF TMR0,W           | MOVF TMR0,W | MOVF TMR0,W | MOVF TMR0,W | MOVF TMR0,W |         |

| Timer0<br>Instruction<br>Executed | (то)   | T0 + 1 )   | T0 + 2)               | Read TMR0   | NT0         | Read TMR0   | NT0 + 1)∕   | NT0 + 2 |

# **REGISTER 7-2:** CONFIGURATION WORD FOR PIC16F505<sup>(1)</sup>

| —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     |                  |   | MCLRE          | CP       | WDTE        | FOSC2        | FOSC1   | FOSC0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------|---|----------------|----------|-------------|--------------|---------|-------|

| bit 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                     | ·                | i |                |          |             |              |         | bit 0 |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                     |                  |   |                |          |             |              |         |       |

| R = Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | able bit                                                                            | W = Writable b   | t | U = Unimp      | lemented | bit, read a | s '0'        |         |       |

| -n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e at POR                                                                            | '1' = Bit is set |   | '0' = Bit is o | cleared  |             | x = Bit is ι | Inknown |       |

| bit 11-6 <b>Unimplemented</b> : Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                     |                  |   |                |          |             |              |         |       |

| bit 5 MCLRE: RB3/MCLR Pin Function Select bit<br>1 = RB3/MCLR pin function is MCLR<br>0 = RB3/MCLR pin function is digital input, MCLR internally tied to VDD                                                                                                                                                                                                                                                                                                                                                                              |                                                                                     |                  |   |                |          |             |              |         |       |

| bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>CP:</b> Code Protection bit<br>1 = Code protection off<br>0 = Code protection on |                  |   |                |          |             |              |         |       |

| bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                  |   |                |          |             |              |         |       |

| bit 2-0 <b>FOSC&lt;1:0&gt;:</b> Oscillator Selection bits<br>111 = External RC oscillator/CLKOUT function on RB4/OSC2/CLKOUT pin<br>110 = External RC oscillator/RB4 function on RB4/OSC2/CLKOUT pin<br>101 = Internal RC oscillator/CLKOUT function on RB4/OSC2/CLKOUT pin<br>100 = Internal RC oscillator/RB4 function on RB4/OSC2/CLKOUT pin<br>011 = EC oscillator/RB4 function on RB4/OSC2/CLKOUT pin<br>011 = EC oscillator/RB4 function on RB4/OSC2/CLKOUT pin<br>010 = HS oscillator<br>001 = XT oscillator<br>000 = LP oscillator |                                                                                     |                  |   |                |          |             |              |         |       |

**Note 1:** Refer to the "*PIC16F505 Memory Programming Specifications*" (DS41226) to determine how to access the Configuration Word. The Configuration Word is not user addressable during device operation.

### 7.9 Power-down Mode (Sleep)

A device may be powered down (Sleep) and later powered up (wake-up from Sleep).

### 7.9.1 SLEEP

The Power-Down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit (STATUS<4>) is set, the PD bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low or high-impedance).

**Note:** A Reset generated by a WDT time-out does not drive the MCLR pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or Vss and the (GP3/RB3)/MCLR/VPP pin must be at a logic high level if MCLR is enabled.

### 7.9.2 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- An external Reset input on (GP3/RB3)/MCLR/ VPP pin, when configured as MCLR.

- 2. A Watchdog Timer time-out Reset (if WDT was enabled).

- A change on input pin GP0/RB0, GP1/RB1, GP3/RB3 or RB4 when wake-up on change is enabled.

These events cause a device Reset. The  $\overline{TO}$ ,  $\overline{PD}$  and GPWUF/RBWUF bits can be used to determine the cause of device Reset. The  $\overline{TO}$  bit is cleared if a WDT time-out occurred (and caused wake-up). The  $\overline{PD}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The GPWUF/RBWUF bit indicates a change in state while in Sleep at pins GP0/RB0, GP1/RB1, GP3/RB3 or RB4 (since the last file or bit operation on GP/RB port).

Note: Caution: Right before entering Sleep, read the input pins. When in Sleep, wakeup occurs when the values at the pins change from the state they were in at the last reading. If a wake-up on change occurs and the pins are not read before reentering Sleep, a wake-up will occur immediately even if no pins change while in Sleep mode.

The WDT is cleared when the device wakes from Sleep, regardless of the wake-up source.

### 7.10 Program Verification/Code Protection

If the code protection bit has not been programmed, the on-chip program memory can be read out for verification purposes.

The first 64 locations and the last location (OSCCAL) can be read, regardless of the code protection bit setting.

The last memory location can be read regardless of the code protection bit setting on the PIC12F508/509/ 16F505 devices.

### 7.11 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '0's.

# 7.12 In-Circuit Serial Programming™

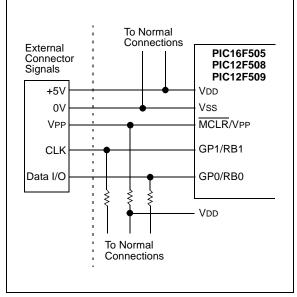

The PIC12F508/509/16F505 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The devices are placed into a Program/Verify mode by holding the <u>GP1/RB1</u> and GP0/RB0 pins low while raising the <u>MCLR</u> (VPP) pin from VIL to VIHH (see programming specification). GP1/RB1 becomes the programming clock and GP0/RB0 becomes the programming data. Both GP1/RB1 and GP0/RB0 are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial programming, please refer to the PIC12F508/509/16F505 Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 7-15.

### FIGURE 7-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| ADDWF            | Add W and f                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                   |

| Operation:       | (W) + (f) $\rightarrow$ (dest)                                                                                                                                                   |

| Status Affected: | C, DC, Z                                                                                                                                                                         |

| Description:     | Add the contents of the W register<br>and register 'f'. If 'd' is'0', the result<br>is stored in the W register. If 'd' is<br>'1', the result is stored back in<br>register 'f'. |

| BCF              | Bit Clear f                                                        |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [label] BCF f,b                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                          |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is cleared.                                |

| ANDLW            | AND literal with W                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | (W).AND. (k) $\rightarrow$ (W)                                                                                             |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BSF              | Bit Set f                                                          |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                          |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is set.                                    |

| ANDWF            | AND W with f                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                                         |

| Description:     | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is '0',<br>the result is stored in the W register.<br>If 'd' is '1', the result is stored back<br>in register 'f'. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSC f,b                                                                                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                           |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                                                                                         |

| Description:     | If bit 'b' in register 'f' is '0', then the<br>next instruction is skipped.<br>If bit 'b' is '0', then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded,<br>and a NOP is executed instead,<br>making this a two-cycle instruction. |

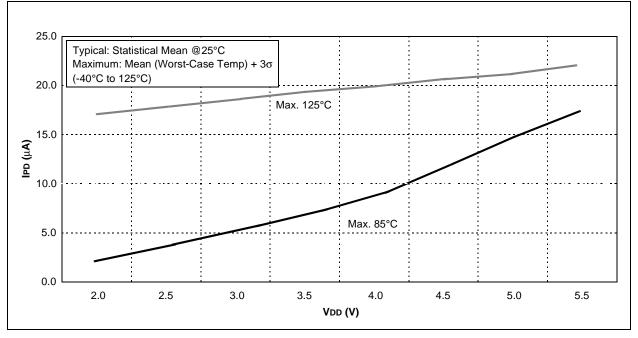

## TABLE 10-6: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER – PIC12F508/509/16F505

| AC CHA       | ARACTE | RISTICS                                       | Standard Operating Conditions (unless otherwise specOperating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended) |            |            |          | $TA \leq +85^{\circ}C$ (industrial)              |

|--------------|--------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|----------|--------------------------------------------------|

| Param<br>No. | Sym.   | Characteristic                                | Min. Typ <sup>(1)</sup> Max. Units Conditions                                                                                                                                    |            |            |          |                                                  |

| 30           | TMCL   | MCLR Pulse Width (low)                        | 2000*                                                                                                                                                                            | _          | _          | ns       | VDD = 5.0V                                       |

| 31           | Twdt   | Watchdog Timer Time-out Period (no prescaler) | 9*<br>9*                                                                                                                                                                         | 18*<br>18* | 30*<br>40* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 32           | Tdrt   | Device Reset Timer Period <sup>(2)</sup>      | 9*<br>9*                                                                                                                                                                         | 18*<br>18* | 30*<br>40* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 34           | Tioz   | I/O High-impedance from MCLR low              | —                                                                                                                                                                                | _          | 2000*      | ns       |                                                  |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

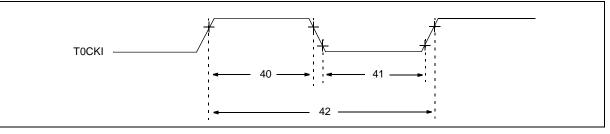

#### **FIGURE 10-7:** TIMER0 CLOCK TIMINGS - PIC12F508/509/16F505

### TABLE 10-7: TIMER0 CLOCK REQUIREMENTS - PIC12F508/509/16F505

| AC CHA       | RACT  | ERISTICS         | Standard Operating Conditions (unless otherwise specified)         Operating Temperature -40°C ≤ TA ≤ +85°C (industrial)         -40°C ≤ TA ≤ +125°C (extended)         Operating Voltage VDD range is described in         Section 10.1 "Power-on Reset (POR)" |                   |                    |      |       |                                                                |

|--------------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|------|-------|----------------------------------------------------------------|

| Param<br>No. | Sym.  | Characte         | eristic                                                                                                                                                                                                                                                         | Min.              | Тур <sup>(1)</sup> | Max. | Units | Conditions                                                     |

| 40           | Tt0H  | T0CKI High Pulse | No Prescaler                                                                                                                                                                                                                                                    | 0.5 TCY + 20*     | —                  | —    | ns    |                                                                |

|              | Width | With Prescaler   | 10*                                                                                                                                                                                                                                                             | _                 | _                  | ns   |       |                                                                |

| 41           | Tt0L  | T0CKI Low Pulse  | No Prescaler                                                                                                                                                                                                                                                    | 0.5 TCY + 20*     | _                  | _    | ns    |                                                                |

|              | Width |                  | With Prescaler                                                                                                                                                                                                                                                  | 10*               | —                  | _    | ns    |                                                                |

| 42           | Tt0P  | T0CKI Period     |                                                                                                                                                                                                                                                                 | 20 or Tcy + 40* N | —                  | _    | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

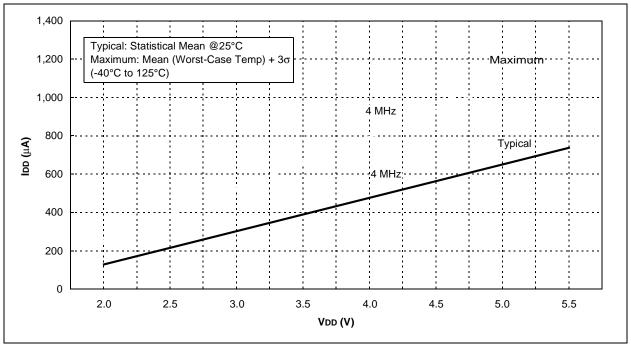

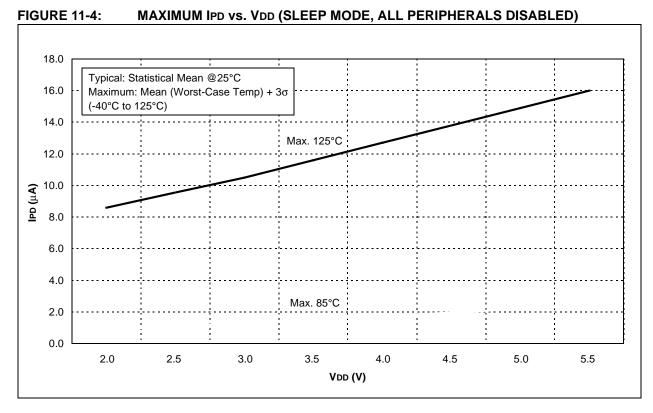

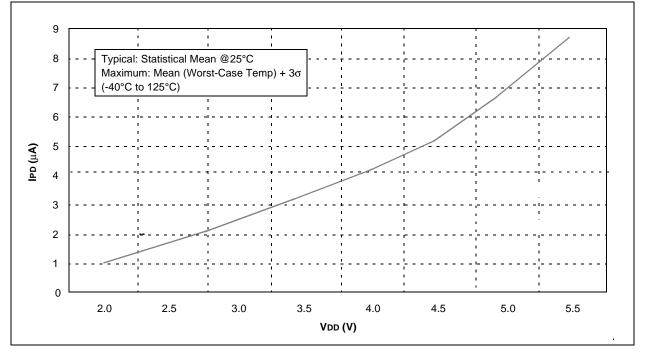

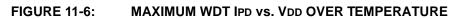

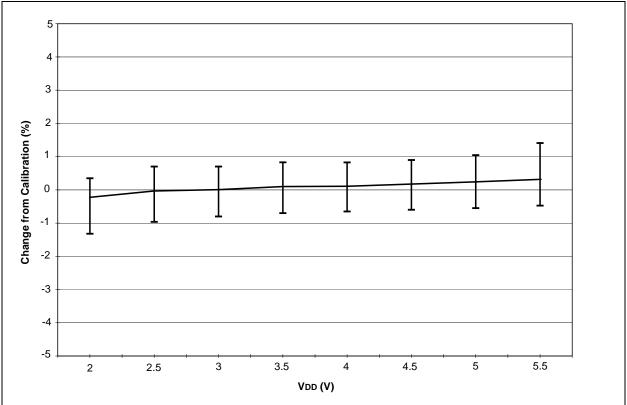

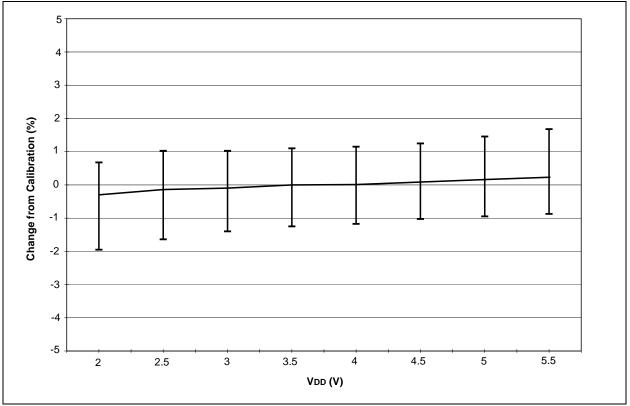

# 11.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where s is a standard deviation, over each temperature range.

FIGURE 11-1: IDD vs. VDD at Fosc = 4 MHz

the case of other types of Reset events.

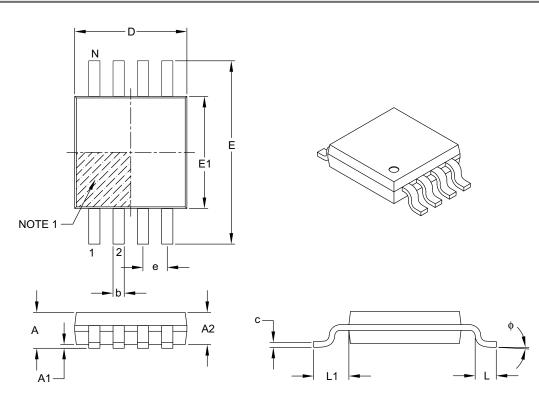

### 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |                |          | 5    |  |

|--------------------------|----------|----------------|----------|------|--|

| Dimension                | n Limits | MIN NOM MA     |          |      |  |

| Number of Pins           | Ν        |                | 8        |      |  |

| Pitch                    | е        |                | 0.65 BSC |      |  |

| Overall Height           | Α        | -              | -        | 1.10 |  |

| Molded Package Thickness | A2       | 0.75           | 0.85     | 0.95 |  |

| Standoff                 | A1       | 0.00           | -        | 0.15 |  |

| Overall Width            | Е        | 4.90 BSC       |          |      |  |

| Molded Package Width     | E1       | 3.00 BSC       |          |      |  |

| Overall Length           | D        | 3.00 BSC       |          |      |  |

| Foot Length              | L        | 0.40 0.60 0.80 |          |      |  |

| Footprint                | L1       | 0.95 REF       |          |      |  |

| Foot Angle               | ¢        | 0° – 8°        |          |      |  |

| Lead Thickness           | с        | 0.08 – 0.23    |          |      |  |

| Lead Width               | b        | 0.22 – 0.40    |          |      |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111B

# INDEX

| Α               |  |

|-----------------|--|

| ALU             |  |

| Assembler       |  |

| MPASM Assembler |  |

# В

| Block Diagram                |  |

|------------------------------|--|

| On-Chip Reset Circuit        |  |

| Timer0                       |  |

| TMR0/WDT Prescaler           |  |

| Watchdog Timer               |  |

| Brown-Out Protection Circuit |  |

# С

| C Compilers                          |  |

|--------------------------------------|--|

| MPLAB C18                            |  |

| MPLAB C30                            |  |

| Carry                                |  |

| Clocking Scheme                      |  |

| Code Protection                      |  |

| Configuration Bits                   |  |

| Configuration Word                   |  |

| Customer Change Notification Service |  |

| Customer Notification Service        |  |

| Customer Support                     |  |

|                                      |  |

## D

| DC and AC Characteristics | 81 |

|---------------------------|----|

| Development Support       | 65 |

| Digit Carry               | 11 |

# Е

| Errata | 6 |

|--------|---|

|--------|---|

# F

| Family of Devices       |   |

|-------------------------|---|

| PIC12F508/509/PIC16F505 | 7 |

| FSR                     |   |

## I

| I/O Interfacing                |        |

|--------------------------------|--------|

| I/O Ports                      |        |

| I/O Programming Considerations |        |

| ID Locations                   | 41, 55 |

| INDF                           |        |

| Indirect Data Addressing       | 28     |

| Instruction Cycle              | 16     |

| Instruction Flow/Pipelining    | 16     |

| Instruction Set Summary        | 58     |

| Internet Address               | 107    |

### L

# Μ

| Memory Organization                       | 17 |

|-------------------------------------------|----|

| Data Memory                               |    |

| Program Memory (PIC12F508/509)            | 17 |

| Program Memory (PIC16F505)                |    |

| Microchip Internet Web Site               |    |

| MPLAB ASM30 Assembler, Linker, Librarian  | 66 |

| MPLAB ICD 2 In-Circuit Debugger           | 67 |

| MPLAB ICE 2000 High-Performance Universal |    |

| In-Circuit Emulator                       | 67 |

|                                           |    |

| MPLAB Integrated Development Environment Software | 65 |

|---------------------------------------------------|----|

| MPLAB PM3 Device Programmer                       | 67 |

| MPLAB REAL ICE In-Circuit Emulator System         | 67 |

| MPLINK Object Linker/MPLIB Object Librarian       | 66 |

### 0

| Option Register           |    |

|---------------------------|----|

| OSC selection             | 41 |

| OSCCAL Register           | 26 |

| Oscillator Configurations | 44 |

| Oscillator Types          |    |

| HS                        | 44 |

| LP                        | 44 |

| RC                        | 44 |

| XT                        | 44 |

|                           |    |

### Ρ

| PIC12F508/509/16F505 Device Varieties<br>PICSTART Plus Development Programmer |        |

|-------------------------------------------------------------------------------|--------|

|                                                                               |        |

| Device Reset Timer (DRT)                                                      | 41, 52 |

| PD                                                                            | 54, 41 |

| TO                                                                            |        |

| PORTB                                                                         | 31     |

| Power-down Mode                                                               | 55     |

| Prescaler                                                                     |        |

| Program Counter                                                               |        |

| PORTB<br>Power-down Mode                                                      |        |

# Q

| Q cycles 16 |

|-------------|

|-------------|

### R

| RC Oscillator      | 45  |

|--------------------|-----|

| Reader Response    | 108 |

| Read-Modify-Write  | 33  |

| Register File Map  |     |

| PIC12F508          | 19  |

| PIC12F509          | 19  |

| PIC16F505          | 19  |

| Registers          |     |

| Special Function   | 20  |

| Reset              | 41  |

| Reset on Brown-Out | 54  |

|                    |     |

# S

| Sleep                          | 41. 55 |

|--------------------------------|--------|

| Software Simulator (MPLAB SIM) |        |

| Special Features of the CPU    |        |

| Special Function Registers     | 20     |

| Stack                          |        |

| Status Register                | 11, 22 |

### Т

| 35 |

|----|

| 35 |

| 37 |

| 75 |

| 75 |

| 31 |

|    |