Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 41 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                    |

| Supplier Device Package    | 8-MSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f509t-i-ms |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| W-1          | W-1                         | VV-1                                 | W-1          | W-1               | VV-1            | W-1             | W-1  |

|--------------|-----------------------------|--------------------------------------|--------------|-------------------|-----------------|-----------------|------|

| RBWU         | RBPU                        | TOCS                                 | T0SE         | PSA               | PS2             | PS1             | PS0  |

| oit 7        | ·                           |                                      |              |                   |                 |                 | bi   |

|              |                             |                                      |              |                   |                 |                 |      |

| Legend:      |                             |                                      |              |                   |                 |                 |      |

| R = Readal   | ole bit                     | W = Writable                         | bit          | U = Unimplen      | nented bit, rea | d as '0'        |      |

| -n = Value a | at POR                      | '1' = Bit is set                     |              | '0' = Bit is clea | ared            | x = Bit is unkr | nown |

|              |                             |                                      |              |                   |                 |                 |      |

| bit 7        |                             | le Wake-up on                        | Pin Change   | bit (RB0, RB1, I  | RB3, RB4)       |                 |      |

|              | 1 = Disabled<br>0 = Enabled |                                      |              |                   |                 |                 |      |

| bit 6        |                             | le Week Pull-ur                      | s hit (RB0 R | B1, RB3, RB4)     |                 |                 |      |

|              | 1 = Disabled                |                                      |              |                   |                 |                 |      |

|              | 0 = Enabled                 |                                      |              |                   |                 |                 |      |

| bit 5        | TOCS: Timer                 | 0 clock Source                       | Select bit   |                   |                 |                 |      |

|              |                             |                                      |              | IS on the TOCH    | (I pin)         |                 |      |

|              |                             | n on internal ins                    | -            | clock, Fosc/4     |                 |                 |      |

| bit 4        |                             | ) Source Edge                        |              |                   |                 |                 |      |

|              |                             | t on high-to-low<br>t on low-to-high |              |                   |                 |                 |      |

| bit 3        |                             | ler Assignment                       |              | ·                 |                 |                 |      |

|              |                             | r assigned to th                     |              |                   |                 |                 |      |

|              | 0 = Prescaler               | assigned to Ti                       | mer0         |                   |                 |                 |      |

| bit 2-0      | <b>PS&lt;2:0&gt;:</b> Pre   | escaler Rate Se                      | elect bits   |                   |                 |                 |      |

|              | Bit                         | Value Timer0                         | Rate WDT R   | late              |                 |                 |      |

|              |                             | 000 1:2                              |              |                   |                 |                 |      |

|              |                             | 001 1:4                              |              |                   |                 |                 |      |

|              |                             | 011 1:1                              |              |                   |                 |                 |      |

|              |                             | LOO 1:3                              | -            |                   |                 |                 |      |

|              |                             | LO1 1:6<br>L10 1:1                   |              |                   |                 |                 |      |

|              |                             | L10 1:1<br>L11 1:2                   |              |                   |                 |                 |      |

## REGISTER 4-4: OPTION REGISTER (PIC16F505)

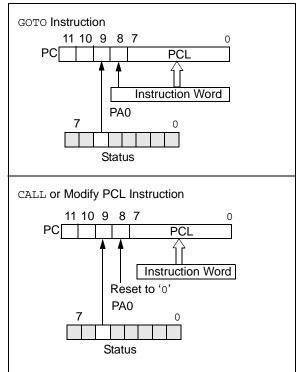

### 4.7 **Program Counter**

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The Program Counter (PCL) is mapped to PC<7:0>. Bit 5 of the STATUS register provides page information to bit 9 of the PC (Figure 4-6).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 4-6).

Instructions where the PCL is the destination, or modify PCL instructions, include MOVWF PC, ADDWF PC and BSF PC, 5.

Note: Because PC<8> is cleared in the CALL instruction or any modify PCL instruction, all subroutine calls or computed jumps are limited to the first 256 locations of any program memory page (512 words long).

#### FIGURE 4-6: LOADING OF PC BRANCH INSTRUCTIONS

## 4.7.1 EFFECTS OF RESET

The PC is set upon a Reset, which means that the PC addresses the last location in the last page (i.e., the oscillator calibration instruction). After executing MOVLW XX, the PC will roll over to location 00h and begin executing user code.

The STATUS register page preselect bits are cleared upon a Reset, which means that page 0 is pre-selected.

Therefore, upon a Reset, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered.

## 4.8 Stack

The PIC12F508/509/16F505 devices have a 2-deep, 12-bit wide hardware PUSH/POP stack.

A CALL instruction will PUSH the current value of Stack 1 into Stack 2 and then PUSH the current PC value, incremented by one, into Stack Level 1. If more than two sequential CALLs are executed, only the most recent two return addresses are stored.

A RETLW instruction will POP the contents of Stack Level 1 into the PC and then copy Stack Level 2 contents into Stack Level 1. If more than two sequential RETLWS are executed, the stack will be filled with the address previously stored in Stack Level 2. Note that the W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

| Note 1: |                                          |     |    |             | ndicate stack |  |

|---------|------------------------------------------|-----|----|-------------|---------------|--|

|         | overflows or stack underflow conditions. |     |    |             |               |  |

| 2:      | There                                    | are | no | instruction | mnemonics     |  |

called PUSH or POP. These are actions that occur from the execution of the CALL and RETLW instructions.

NOTES:

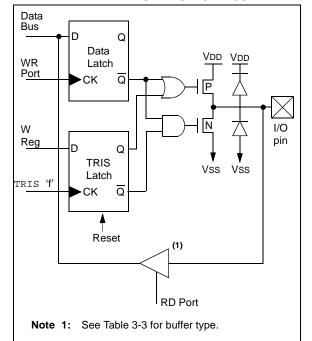

## 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all set.

| Note: | On the PIC12F508/509, I/O PORTB is ref- |

|-------|-----------------------------------------|

|       | erenced as GPIO. On the PIC16F505, I/O  |

|       | PORTB is referenced as PORTB.           |

### 5.1 PORTB/GPIO

PORTB/GPIO is an 8-bit I/O register. Only the loworder 6 bits are used (RB/GP<5:0>). Bits 7 and 6 are unimplemented and read as '0's. Please note that RB3/ GP3 is an input only pin. The Configuration Word can set several I/O's to alternate functions. When acting as alternate functions, the pins will read as '0' during a port read. Pins RB0/GP0, RB1/GP1, RB3/GP3 and RB4 can be configured with weak pull-ups and also for wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If RB3/GP3/ MCLR is configured as MCLR, weak pull-up is always on and wake-up on change for this pin is not enabled.

## 5.2 PORTC (PIC16F505 Only)

PORTC is an 8-bit I/O register. Only the low-order 6 bits are used (RC<5:0>). Bits 7 and 6 are unimplemented and read as '0's.

| Note: | On power-up, TOCKI functionality is     |

|-------|-----------------------------------------|

|       | enabled in the OPTION register and must |

|       | be disabled to allow RC5 to be used as  |

|       | general purpose I/O.                    |

### 5.3 TRIS Registers

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are RB3/GP3, which is input only and the TOCKI pin, which may be controlled by the OPTION register. See Register 4-3 and Register 4-4.

| Note: | A read of the ports reads the pins, not the    |

|-------|------------------------------------------------|

|       | output data latches. That is, if an output     |

|       | driver on a pin is enabled and driven high,    |

|       | but the external system is holding it low, a   |

|       | read of the port will indicate that the pin is |

|       | low.                                           |

The TRIS registers are "write-only" and are set (output drivers disabled) upon Reset.

## 5.4 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-2. All port pins, except RB3/GP3 which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except RB3/GP3) can be programmed individually as input or output.

FIGURE 5-1:

#### PIC12F508/509/16F505 EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

NOTES:

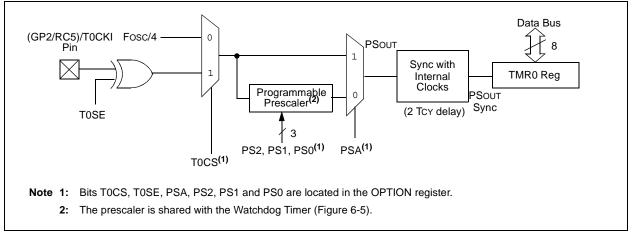

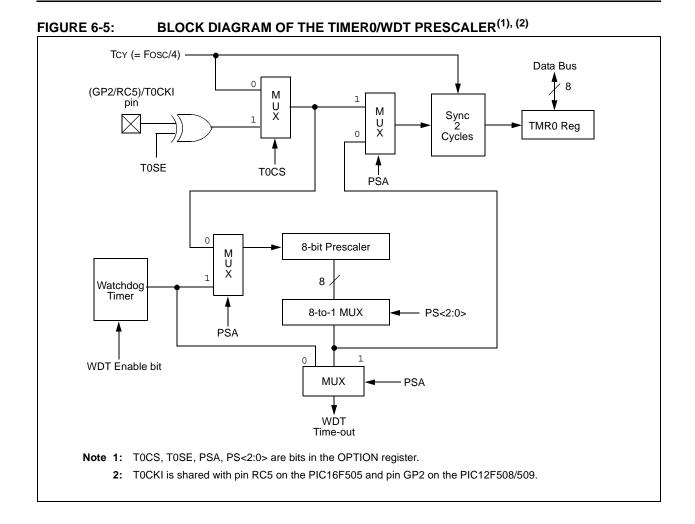

## 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select:

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1 "Using Timer0 with an External Clock".

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit, PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 6.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| PC<br>(Program<br>Counter)        | PC – 1 |            | Q1 Q2 Q3 Q4<br>PC + 1 | PC + 2      | (PC + 3     | (PC + 4)    | PC + 5      | (PC+6)  |

|-----------------------------------|--------|------------|-----------------------|-------------|-------------|-------------|-------------|---------|

| Instruction<br>Fetch              |        | MOVWF TMR0 | MOVF TMR0,W           | MOVF TMR0,W | MOVF TMR0,W | MOVF TMR0,W | MOVF TMR0,W |         |

| Timer0<br>Instruction<br>Executed | (то)   | T0 + 1 )   | T0 + 2)               | Read TMR0   | NT0         | Read TMR0   | NT0 + 1)∕   | NT0 + 2 |

## FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

| PC<br>(Program<br>Counter)        | Q1 Q2 Q3 Q4<br>( | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4<br>( | Q1 Q2 Q3 Q4<br>(       | Q1 Q2 Q3 Q4<br>( | Q1 Q2 Q3 Q4            | Q1 Q2 Q3 Q4                | Q1 Q2 Q3 Q4<br>PC + 6 |

|-----------------------------------|------------------|-------------|------------------|------------------------|------------------|------------------------|----------------------------|-----------------------|

| Instruction<br>Fetch              | ,<br>1<br>1<br>1 | MOVWF TMR0  | MOVF TMR0,W      | MOVF TMR0,W            | MOVF TMR0,W      | MOVF TMR0,W            | MOVF TMR0,W                |                       |

| Timer0<br>Instruction<br>Executed | (Υ               | T0 + 1      | Write TMR0       | Read TMR0<br>reads NT0 | NT0              | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | NT0 + 1               |

### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name                         | Bit 7    | Bit 6                                  | Bit 5                  | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|------------------------------|----------|----------------------------------------|------------------------|-------|-------|-----------|-----------|-------|-------------------------------|---------------------------------|

| 01h     | TMR0                         | Timer0 – | Timer0 – 8-bit Real-Time Clock/Counter |                        |       |       | xxxx xxxx | uuuu uuuu |       |                               |                                 |

| N/A     | OPTION <sup>(1)</sup>        | GPWU     | GPPU                                   | TOCS                   | TOSE  | PSA   | PS2       | PS1       | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup>        | RBWU     | RBPU                                   | TOCS                   | TOSE  | PSA   | PS2       | PS1       | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | TRISGPIO <sup>(1), (3)</sup> | _        | —                                      | - I/O Control Register |       |       | 11 1111   | 11 1111   |       |                               |                                 |

| N/A     | TRISC <sup>(2), (3)</sup>    | _        | _                                      | RC5                    | RC4   | RC3   | RC2       | RC1       | RC0   | 11 1111                       | 11 1111                         |

**Legend:** Shaded cells are not used by Timer0. – = unimplemented, x = unknown, u = unchanged.

Note 1: PIC12F508/509 only.

2: PIC16F505 only.

3: The TRIS of the T0CKI pin is overridden when T0CS = 1.

## 7.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of real-time applications. The PIC12F508/509/16F505 microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These features are:

- Oscillator Selection

- Reset:

- Power-on Reset (POR)

- Device Reset Timer (DRT)

- Wake-up from Sleep on Pin Change

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

- Clock Out

The PIC12F508/509/16F505 devices have a Watchdog Timer, which can be shut off only through Configuration bit WDTE. It runs off of its own RC oscillator for added reliability. If using HS (PIC16F505), XT or LP selectable oscillator options, there is always an 18 ms (nominal) delay provided by the Device Reset Timer (DRT), intended to keep the chip in Reset until the crystal oscillator is stable. If using INTRC or EXTRC, there is an 18 ms delay only on VDD power-up. With this timer on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through a change on input pins or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application, including an internal 4 MHz oscillator. The EXTRC oscillator option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options.

## 7.1 Configuration Bits

The PIC12F508/509/16F505 Configuration Words consist of 12 bits. Configuration bits can be programmed to select various device configurations. Three bits are for the selection of the oscillator type; (two bits on the PIC12F508/509), one bit is the Watchdog Timer enable bit, one bit is the MCLR enable bit and one bit is for code protection (Register 7-1, Register 7-2).

# TABLE 7-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR – PIC12F508/509/16F505<sup>(2)</sup>

| Osc<br>Type       | Resonator<br>Freq.                                                                                                                                                                                                                                                                                    | Cap. Range<br>C1           | Cap. Range<br>C2           |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|--|--|--|

| LP                | 32 kHz <sup>(1)</sup>                                                                                                                                                                                                                                                                                 | 15 pF                      | 15 pF                      |  |  |  |

| XT                | 200 kHz<br>1 MHz<br>4 MHz                                                                                                                                                                                                                                                                             | 47-68 pF<br>15 pF<br>15 pF | 47-68 pF<br>15 pF<br>15 pF |  |  |  |

| HS <sup>(3)</sup> | 20 MHz                                                                                                                                                                                                                                                                                                | 15-47 pF                   | 15-47 pF                   |  |  |  |

| Note 1:           | For VDD > 4.5V, C1 = C2 $\approx$ 30 pF is recommended.                                                                                                                                                                                                                                               |                            |                            |  |  |  |

| 2:                | These values are for design guidance<br>only. Rs may be required to avoid over-<br>driving crystals with low drive level specifi-<br>cation. Since each crystal has its own<br>characteristics, the user should consult<br>the crystal manufacturer for appropriate<br>values of external components. |                            |                            |  |  |  |

| 3:                | PIC16F505                                                                                                                                                                                                                                                                                             | only.                      |                            |  |  |  |

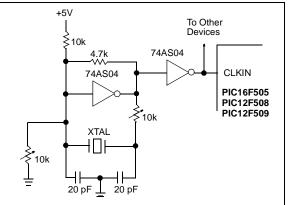

#### 7.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 7-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

## FIGURE 7-3:

#### EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

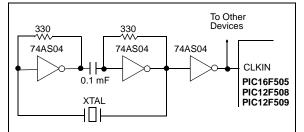

Figure 7-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

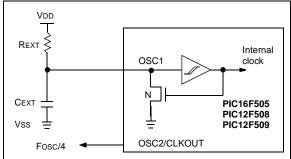

## 7.2.4 EXTERNAL RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit-to-unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 7-5 shows how the R/C combination is connected to the PIC12F508/509/16F505 devices. For REXT values below 3.0 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 5.0 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

**Section 10.0 "Electrical Characteristics"** shows RC frequency variation from part-to-part due to normal process variation. The variation is larger for larger values of R (since leakage current variation will affect RC frequency more for large R) and for smaller values of C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications section for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

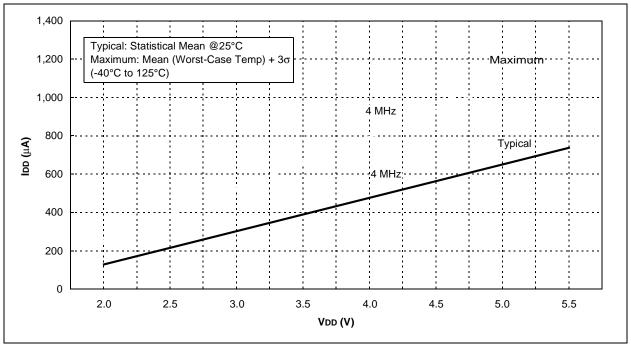

## 7.2.5 INTERNAL 4 MHz RC OSCILLATOR

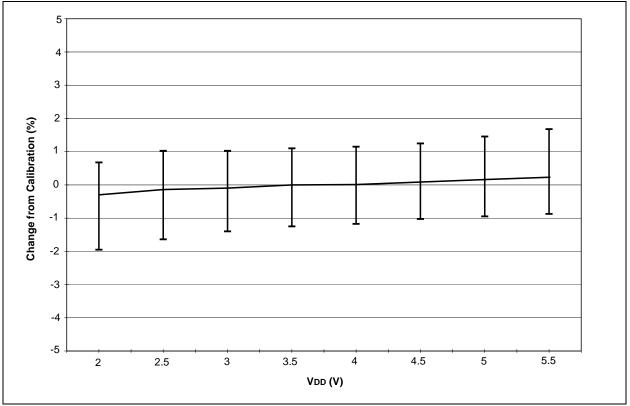

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and  $25^{\circ}C$ , (see **Section 10.0** "**Electrical Characteristics**" for information on variation over voltage and temperature).

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal RC oscillator. This location is always uncode protected, regardless of the code-protect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the Reset vector. This will load the W register with the calibration value upon Reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

| Note: | Erasing the device will also erase the pre- |

|-------|---------------------------------------------|

|       | programmed internal calibration value for   |

|       | the internal oscillator. The calibration    |

|       | value must be read prior to erasing the     |

|       | part so it can be reprogrammed correctly    |

|       | later.                                      |

For the PIC12F508/509/16F505 devices, only bits <7:1> of OSCCAL are implemented. Bits CAL6-CAL0 are used for calibration. Adjusting CAL6-CAL0 from '0000000' to '1111111' changes the clock speed. See Register 4-5 for more information.

| Note: | The 0 bit of OSCCAL is unimplemented    |

|-------|-----------------------------------------|

|       | and should be written as '0' when       |

|       | modifying OSCCAL for compatibility with |

|       | future devices.                         |

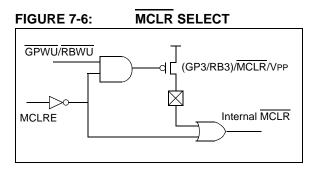

## 7.3.1 MCLR ENABLE

This Configuration bit, when unprogrammed (left in the '1' state), enables the external MCLR function. When programmed, the MCLR function is tied to the internal VDD and the pin is assigned to be an input only. See Figure 7-6.

## 7.4 Power-on Reset (POR)

The PIC12F508/509/16F505 devices incorporate an on-chip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the (GP3/RB3)/MCLR/VPP pin as MCLR and tie through a resistor to VDD, or program the pin as (GP3/RB3). An internal weak pull-up resistor is implemented using a transistor (refer to Table 10-2 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See **Section 10.0 "Electrical Characteristics"** for details.

When the devices start normal operation (exit the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the devices must be held in Reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-on Reset circuit is shown in Figure 7-7.

The Power-on Reset circuit and the Device Reset Timer (see **Section 7.5 "Device Reset Timer (DRT)**") circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will reset the Reset latch and thus end the on-chip Reset signal.

A power-up example where MCLR is held low is shown in Figure 7-8. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of Reset TDRT msec after MCLR goes high.

In Figure 7-9, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be (GP3/RB3). The VDD is stable before the start-up timer times out and there is no problem in getting a proper Reset. However, Figure 7-10 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 7-9).

| Note: | When the devices start normal operation     |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | (exit the Reset condition), device operat-  |  |  |  |  |

|       | ing parameters (voltage, frequency, tem-    |  |  |  |  |

|       | perature, etc.) must be met to ensure       |  |  |  |  |

|       | operation. If these conditions are not met, |  |  |  |  |

|       | the device must be held in Reset until the  |  |  |  |  |

|       | operating conditions are met.               |  |  |  |  |

For additional information, refer to Application Notes AN522 *"Power-Up Considerations"* (DS00522) and AN607 *"Power-up Trouble Shooting"* (DS00607).

## 7.7 Time-out Sequence, Power-down and <u>Wake-up</u> from Sleep Status Bits (TO, PD, GPWUF/RBWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$  and (GPWUF/RBWUF) bits in the STATUS register can be tested to determine if a Reset condition has been caused by a Power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) Reset.

## TABLE 7-8: TO/PD/(GPWUF/RBWUF) STATUS AFTER RESET

| GPWUF/<br>RBWUF | то | PD | Reset Caused By                     |

|-----------------|----|----|-------------------------------------|

| 0               | 0  | 0  | WDT wake-up from Sleep              |

| 0               | 0  | u  | WDT time-out (not from Sleep)       |

| 0               | 1  | 0  | MCLR wake-up from Sleep             |

| 0               | 1  | 1  | Power-up                            |

| 0               | u  | u  | MCLR not during Sleep               |

| 1               | 1  | 0  | Wake-up from Sleep on pin<br>change |

**Legend:** u = unchanged

Note 1: The TO, PD and GPWUF/RBWUF bits maintain their status (u) until a Reset occurs. A low-pulse on the MCLR input does not change the TO, PD and GPWUF/RBWUF Status bits.

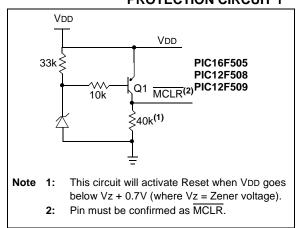

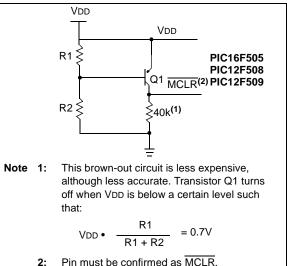

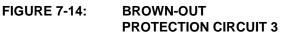

### 7.8 Reset on Brown-out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset PIC12F508/509/16F505 devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 7-12 and Figure 7-13.

#### FIGURE 7-12: BROWN-OUT PROTECTION CIRCUIT 1

| DC Characteristics |      | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) |       |                    |             |          |                                                                            |

|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|-------------|----------|----------------------------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                                                                                                          | Min.  | Typ <sup>(1)</sup> | Max.        | Units    | Conditions                                                                 |

| D001               | Vdd  | Supply Voltage                                                                                                                          | 2.0   |                    | 5.5         | V        | See Figure 10-1                                                            |

| D002               | Vdr  | RAM Data Retention Voltage <sup>(2)</sup>                                                                                               |       | 1.5*               | —           | V        | Device in Sleep mode                                                       |

| D003               | VPOR | VDD Start Voltage to ensure<br>Power-on Reset                                                                                           | —     | Vss                | —           | V        | See Section 7.4 "Power-on<br>Reset (POR)" for details                      |

| D004               | SVDD | VDD Rise Rate to ensure<br>Power-on Reset                                                                                               | 0.05* | —                  | _           | V/ms     | See Section 7.4 "Power-on<br>Reset (POR)" for details                      |

| D010               | Idd  | Supply Current <sup>(3,4)</sup>                                                                                                         | _     | 175<br>0.625       | 275<br>1.1  | μA<br>mA | Fosc = 4 MHz, Vdd = 2.0V<br>Fosc = 4 MHz, Vdd = 5.0V                       |

|                    |      |                                                                                                                                         | _     | 500<br>1.5         | 650<br>2.2  | μA<br>mA | Fosc = 10 MHz, VDD = 3.0V<br>Fosc = 20 MHz, VDD = 5.0V<br>(PIC16F505 only) |

|                    |      |                                                                                                                                         | _     | 11<br>38           | 20<br>54    | μΑ<br>μΑ | Fosc = 32 kHz, VDD = 2.0V<br>Fosc = 32 kHz, VDD = 5.0V                     |

| D020               | IPD  | Power-down Current <sup>(5)</sup>                                                                                                       | —     | 0.1<br>0.35        | 1.2<br>2.4  | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                   |

| D022               | Iwdt | WDT Current <sup>(5)</sup>                                                                                                              | _     | 1.0<br>7.0         | 3.0<br>16.0 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V                                                   |

### 10.1 DC Characteristics: PIC12F508/509/16F505 (Industrial)

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- 4: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- 5: For standby current measurements, the conditions are the same as IDD, except that the device is in Sleep mode. If a module current is listed, the current is for that specific module enabled and the device in Sleep.

#### **TABLE 10-1:** DC CHARACTERISTICS: PIC12F508/509/16F505 (Industrial, Extended)

| DC CHARACTERISTICS |      | $ \begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \ (industrial) \\ & -40^\circ C \leq TA \leq +125^\circ C \ (extended) \\ \mbox{Operating voltage VDD range as described in DC specification} \\ \end{array} $ |                   |           |          |       |                                                                      |  |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|----------|-------|----------------------------------------------------------------------|--|

| Param<br>No.       | Sym. | Characteristic                                                                                                                                                                                                                                                                                                             | Min.              | Typ† Max. |          | Units | Conditions                                                           |  |

|                    | VIL  | Input Low Voltage                                                                                                                                                                                                                                                                                                          |                   |           |          |       |                                                                      |  |

|                    |      | I/O ports:                                                                                                                                                                                                                                                                                                                 |                   |           |          |       |                                                                      |  |

| D030               |      | with TTL buffer                                                                                                                                                                                                                                                                                                            | Vss               | _         | 0.8V     | V     | For all $4.5 \le VDD \le 5.5V$                                       |  |

| D030A              |      |                                                                                                                                                                                                                                                                                                                            | Vss               | _         | 0.15 Vdd | V     | Otherwise                                                            |  |

| D031               |      | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                | Vss               | _         | 0.15 Vdd | V     |                                                                      |  |

| D032               |      | MCLR, TOCKI                                                                                                                                                                                                                                                                                                                | Vss               | _         | 0.15 Vdd | V     |                                                                      |  |

| D033               |      | OSC1 (in EXTRC)                                                                                                                                                                                                                                                                                                            | Vss               | _         | 0.15 Vdd | V     | (Note1)                                                              |  |

| D033               |      | OSC1 (in HS)                                                                                                                                                                                                                                                                                                               | Vss               | _         | 0.3 Vdd  | V     | (Note1)                                                              |  |

| D033               |      | OSC1 (in XT and LP)                                                                                                                                                                                                                                                                                                        | Vss               | _         | 0.3      | V     | (Note1)                                                              |  |

|                    | Vін  | Input High Voltage                                                                                                                                                                                                                                                                                                         |                   |           |          |       |                                                                      |  |

|                    |      | I/O ports:                                                                                                                                                                                                                                                                                                                 |                   | _         |          |       |                                                                      |  |

| D040               |      | with TTL buffer                                                                                                                                                                                                                                                                                                            | 2.0               | _         | Vdd      | v     | $4.5 \leq VDD \leq 5.5V$                                             |  |

| D040A              |      |                                                                                                                                                                                                                                                                                                                            | 0.25 Vdd          | —         | Vdd      | V     | Otherwise                                                            |  |

| D041               |      | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                | + 0.8<br>0.85 Vdd | _         | VDD      | v     | For entire VDD range                                                 |  |

| D042               |      | MCLR, TOCKI                                                                                                                                                                                                                                                                                                                | 0.85 VDD          | _         | VDD      | v     |                                                                      |  |

| D042               |      | OSC1 (in EXTRC)                                                                                                                                                                                                                                                                                                            | 0.85 VDD          | _         | VDD      | v     | (Note1)                                                              |  |

| D043               |      | OSC1 (in HS)                                                                                                                                                                                                                                                                                                               | 0.7 VDD           | _         | VDD      | v     | (Note1)                                                              |  |

| D043               |      | OSC1 (in XT and LP)                                                                                                                                                                                                                                                                                                        | 1.6               | _         | VDD      | v     |                                                                      |  |

| D070               | IPUR | GPIO/PORTB weak pull-up                                                                                                                                                                                                                                                                                                    | 50                | 250       | 400      | μA    | VDD = 5V, VPIN = VSS                                                 |  |

|                    |      | current <sup>(4)</sup>                                                                                                                                                                                                                                                                                                     |                   |           |          |       |                                                                      |  |

|                    | lı∟  | Input Leakage Current <sup>(2), (3)</sup>                                                                                                                                                                                                                                                                                  |                   |           |          |       |                                                                      |  |

| D060               |      | I/O ports                                                                                                                                                                                                                                                                                                                  | —                 | -         | ± 1      | μΑ    | $Vss \leq VPIN \leq VDD$ , Pin at high-impedance                     |  |

| D061               |      | GP3/RB3/MCLRI <sup>(5)</sup>                                                                                                                                                                                                                                                                                               | —                 | ± 0.7     | ± 5      | μΑ    | $Vss \leq Vpin \leq Vdd$                                             |  |

| D063               |      | OSC1                                                                                                                                                                                                                                                                                                                       | -                 | —         | ± 5      | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration   |  |

|                    |      | Output Low Voltage                                                                                                                                                                                                                                                                                                         |                   |           |          |       |                                                                      |  |

| D080               |      | I/O ports/CLKOUT                                                                                                                                                                                                                                                                                                           | -                 | —         | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V, -40°C to +85°C                             |  |

| D080A              |      |                                                                                                                                                                                                                                                                                                                            | —                 | —         | 0.6      | V     | IOL = 7.0 mA, VDD = 4.5V, -40°C to +125°C                            |  |

| D083               |      | OSC2                                                                                                                                                                                                                                                                                                                       | _                 | —         | 0.6      | V     | IOL = 1.6 mA, VDD = 4.5V, -40°C to +85°C                             |  |

| D083A              |      |                                                                                                                                                                                                                                                                                                                            | _                 | —         | 0.6      | V     | IOL = 1.2 mA, VDD = 4.5V, -40°C to +125°C                            |  |

|                    |      | Output High Voltage                                                                                                                                                                                                                                                                                                        |                   |           |          |       |                                                                      |  |

| D090               |      | I/O ports/CLKOUT <sup>(3)</sup>                                                                                                                                                                                                                                                                                            | Vdd - 0.7         | —         | —        | V     | IOH = -3.0 mA, VDD = 4.5V, -40°C to +85°C                            |  |

| D090A              |      |                                                                                                                                                                                                                                                                                                                            | Vdd - 0.7         | —         | —        | V     | IOH = -2.5 mA, VDD = 4.5V, -40°C to +125°C                           |  |

| D092               |      | OSC2                                                                                                                                                                                                                                                                                                                       | Vdd - 0.7         | —         | —        | V     | IOH = -1.3 mA, VDD = $4.5$ V, $-40^{\circ}$ C to $+85^{\circ}$ C     |  |

| D092A              |      |                                                                                                                                                                                                                                                                                                                            | Vdd - 0.7         | —         | —        | V     | IOH = -1.0 mA, VDD = $4.5$ V, $-40^{\circ}$ C to $+125^{\circ}$ C    |  |

|                    |      | Capacitive Loading Specs on<br>Output Pins                                                                                                                                                                                                                                                                                 |                   |           |          |       |                                                                      |  |

|                    |      |                                                                                                                                                                                                                                                                                                                            |                   |           |          | 1     |                                                                      |  |

| D100               |      | OSC2 pin                                                                                                                                                                                                                                                                                                                   | —                 | _         | 15       | pF    | In XT, HS and LP modes when external clock is<br>used to drive OSC1. |  |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. † 1:

Note

2:

3:

4:

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12F508/509/ 16F505 be driven with external clock in RC mode. The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages. Negative current is defined as coming out of the pin. The specification applies to all weak pull-up devices, including the weak pull-up on GP3/MCLR. The current listed will be the same whether GP3/MCLR is configured as GP3 with a weak pull-up or enabled as MCLR. This specification applies when GP3/RB3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic. 5:

## 11.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

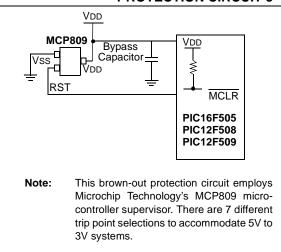

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where s is a standard deviation, over each temperature range.

FIGURE 11-1: IDD vs. VDD at Fosc = 4 MHz

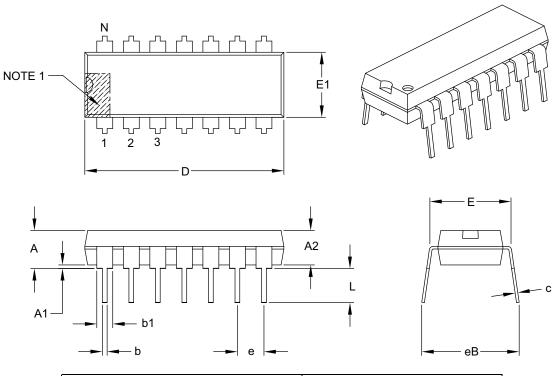

### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units       | INCHES |          |      |

|----------------------------|-------------|--------|----------|------|

| Dimen                      | sion Limits | MIN    | NOM      | MAX  |

| Number of Pins             | N           |        | 14       |      |

| Pitch                      | е           |        | .100 BSC |      |

| Top to Seating Plane       | А           | -      | -        | .210 |

| Molded Package Thickness   | A2          | .115   | .130     | .195 |

| Base to Seating Plane      | A1          | .015   | -        | -    |

| Shoulder to Shoulder Width | E           | .290   | .310     | .325 |

| Molded Package Width       | E1          | .240   | .250     | .280 |

| Overall Length             | D           | .735   | .750     | .775 |

| Tip to Seating Plane       | L           | .115   | .130     | .150 |

| Lead Thickness             | С           | .008   | .010     | .015 |

| Upper Lead Width           | b1          | .045   | .060     | .070 |

| Lower Lead Width           | b           | .014   | .018     | .022 |

| Overall Row Spacing §      | eB          | -      | -        | .430 |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

## W

| Wake-up from Sleep         |    |

|----------------------------|----|

| Watchdog Timer (WDT)       |    |

| Period                     | 52 |

| Programming Considerations |    |

| WWW Address                |    |

| WWW, On-Line Support       | 6  |

| Z                          |    |

| Zero bit                   | 11 |

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | <u>x /xx xxx</u>                                                                                                                                                           | Examples:                                                                                                                                                                                                   |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                | Temperature Package Pattern<br>Range                                                                                                                                       | <ul> <li>a) PIC12F508-E/P 301 = Extended Temp., PDIP<br/>package, QTP pattern #301</li> <li>b) PIC12F508-I/SN = Industrial Temp., SOIC<br/>package</li> </ul>                                               |

| Device:               | PIC16F505<br>PIC12F508<br>PIC12F509<br>PIC16F505T <sup>(1)</sup><br>PIC12F508T <sup>(2)</sup><br>PIC12F509T <sup>(2)</sup>                                                 | c) PIC12F508T-E/P = Extended Temp., PDIP<br>package, Tape and Reel                                                                                                                                          |

| Temperature<br>Range: | $ \begin{array}{rcl} I &=& -40^{\circ} C \text{ to } +85^{\circ} C \text{ (Industrial)} \\ E &=& -40^{\circ} C \text{ to } +125^{\circ} C \text{ (Extended)} \end{array} $ |                                                                                                                                                                                                             |

| Package:              | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                       | <ul> <li>Note 1: T = in tape and reel SOIC, TSSOP and QFN packages only</li> <li>2: T = in tape and reel SOIC and MSOP packages only.</li> <li>3: PIC12F508/PIC12F509 only.</li> <li>4: Pb-free.</li> </ul> |

|                       | Special Requirements<br>and Reel available for only the following packages: SOIC, MSOP<br>TSSOP.                                                                           | 5: PIC16F505 only.                                                                                                                                                                                          |

|                       |                                                                                                                                                                            |                                                                                                                                                                                                             |