Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               |                                                                          |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 1.5KB (1K x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 72 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 16-QFN (3x3)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f505-e-mg |

|                            |                                                                          |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

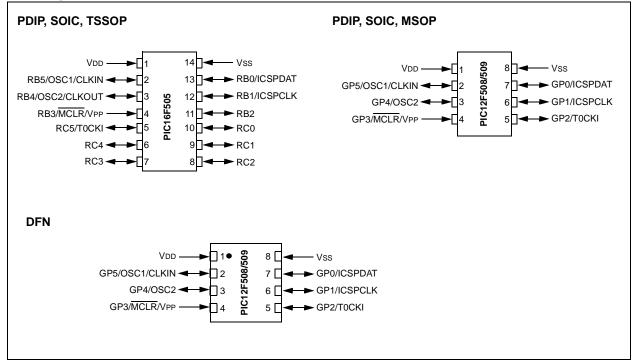

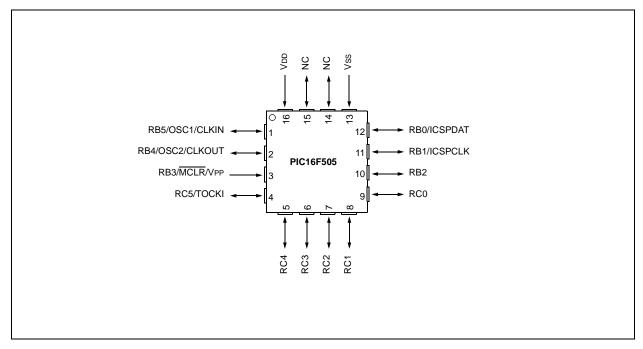

#### Pin Diagrams

## PIC16F505 16-Pin Diagram (QFN)

NOTES:

## 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all set.

| Note: | On the PIC12F508/509, I/O PORTB is ref- |

|-------|-----------------------------------------|

|       | erenced as GPIO. On the PIC16F505, I/O  |

|       | PORTB is referenced as PORTB.           |

#### 5.1 PORTB/GPIO

PORTB/GPIO is an 8-bit I/O register. Only the loworder 6 bits are used (RB/GP<5:0>). Bits 7 and 6 are unimplemented and read as '0's. Please note that RB3/ GP3 is an input only pin. The Configuration Word can set several I/O's to alternate functions. When acting as alternate functions, the pins will read as '0' during a port read. Pins RB0/GP0, RB1/GP1, RB3/GP3 and RB4 can be configured with weak pull-ups and also for wake-up on change. The wake-up on change and weak pull-up functions are not pin selectable. If RB3/GP3/ MCLR is configured as MCLR, weak pull-up is always on and wake-up on change for this pin is not enabled.

### 5.2 PORTC (PIC16F505 Only)

PORTC is an 8-bit I/O register. Only the low-order 6 bits are used (RC<5:0>). Bits 7 and 6 are unimplemented and read as '0's.

| Note: | On power-up, TOCKI functionality is     |

|-------|-----------------------------------------|

|       | enabled in the OPTION register and must |

|       | be disabled to allow RC5 to be used as  |

|       | general purpose I/O.                    |

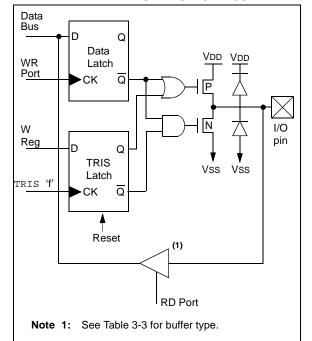

#### 5.3 TRIS Registers

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are RB3/GP3, which is input only and the TOCKI pin, which may be controlled by the OPTION register. See Register 4-3 and Register 4-4.

| Note: | A read of the ports reads the pins, not the    |  |  |

|-------|------------------------------------------------|--|--|

|       | output data latches. That is, if an output     |  |  |

|       | driver on a pin is enabled and driven high,    |  |  |

|       | but the external system is holding it low, a   |  |  |

|       | read of the port will indicate that the pin is |  |  |

|       | low.                                           |  |  |

The TRIS registers are "write-only" and are set (output drivers disabled) upon Reset.

### 5.4 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-2. All port pins, except RB3/GP3 which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except RB3/GP3) can be programmed individually as input or output.

FIGURE 5-1:

#### PIC12F508/509/16F505 EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

#### 5.5 I/O Programming Considerations

#### 5.5.1 BIDIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit 5 of PORTB/GPIO will cause all eight bits of PORTB/GPIO to be read into the CPU, bit 5 to be set and the PORTB/GPIO value to be written to the output latches. If another bit of PORTB/ GPIO is used as a bidirectional I/O pin (say bit 0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential Read-Modify-Write instructions (e.g., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired OR", "wired AND"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT(e.g., PIC16F505)

| ;Initial PORTB Settings<br>;PORTB<5:3> Inputs<br>;PORTB<2:0> Outputs |                                  |                                                    |

|----------------------------------------------------------------------|----------------------------------|----------------------------------------------------|

| ;<br>;                                                               | PORTB latch                      | PORTB pins                                         |

| BCF PORTB, 4<br>MOVLW 007h;                                          | ;01 -ppp<br>;10 -ppp<br>;10 -ppp | 11 pppp                                            |

| <b>be</b> '00                                                        | , ,                              | d the pin values to<br>CF caused RB5 to<br>(High). |

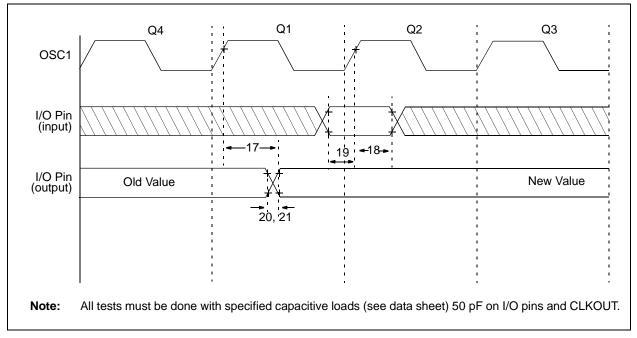

#### 5.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### Q1 | Q2 | Q3 | Q4 | PC + 1 PC + 3 This example shows a write to PORTB followed by a read from PORTB. PC Instruction Fetched MOVWF PORTB MOVF PORTB, W NOP NOP Data setup time = (0.25 TCY - TPD)where: TCY = instruction cycle RB<5.0> TPD = propagation delay Port pin written here Port pin sampled here Therefore, at higher clock frequencies, a write followed by a read may be problematic. Instruction Executed MOVWE PORTE MOVE PORTE W NOP (Write to PORTB) (Read PORTB)

#### FIGURE 5-2: SUCCESSIVE I/O OPERATION (PIC16F505 Shown)

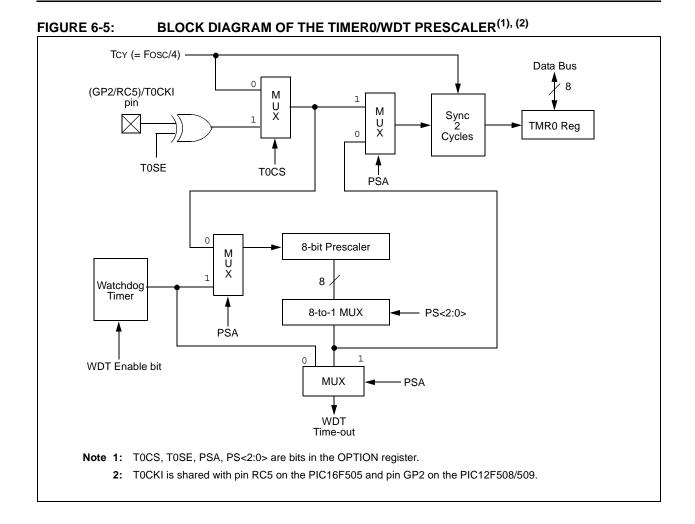

#### 6.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (see Section 7.6 "Watchdog Timer (WDT)"). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

| Note: | The prescaler may be used by either the |  |  |

|-------|-----------------------------------------|--|--|

|       | Timer0 module or the WDT, but not both. |  |  |

|       | Thus, a prescaler assignment for the    |  |  |

|       | Timer0 module means that there is no    |  |  |

|       | prescaler for the WDT and vice versa.   |  |  |

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a Reset, the prescaler contains all '0's.

#### 6.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

## EXAMPLE 6-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

|        | •           | ,                        |

|--------|-------------|--------------------------|

| CLRWDT |             | ;Clear WDT               |

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler  |

| MOVLW  | `00xx1111'b | ;These 3 lines (5, 6, 7) |

| OPTION |             | ;are required only if    |

|        |             | ;desired                 |

| CLRWDT |             | ;PS<2:0> are 000 or 001  |

| MOVLW  | `00xx1xxx'b | ;Set Postscaler to       |

| OPTION |             | ;desired WDT rate        |

|        |             |                          |

To change the prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

| EXAMPLE 6-2: | CHANGING PRESCALER         |  |

|--------------|----------------------------|--|

|              | (WDT $\rightarrow$ TIMER0) |  |

| CLRWDT           | ;Clear WDT and                  |

|------------------|---------------------------------|

| MOVLW 'xxxx0xxx' | ;prescaler<br>;Select TMR0, new |

| HOVEN AAAAAAAA   | ;prescale value and             |

|                  | ;clock source                   |

| OPTION           |                                 |

#### 7.2 Oscillator Configurations

#### 7.2.1 OSCILLATOR TYPES

The PIC12F508/509/16F505 devices can be operated in up to six different oscillator modes. The user can program up to three Configuration bits (FOSC<1:0> [PIC12F508/509], FOSC<2:0> [PIC16F505]). To select one of these modes:

- LP: Low-Power Crystal

- XT: Crystal/Resonator

- HS: High-Speed Crystal/Resonator (PIC16F505 only)

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

- EC: External High-Speed Clock Input (PIC16F505 only)

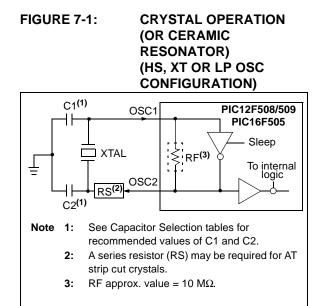

## 7.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

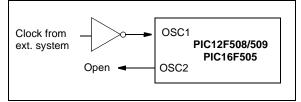

In HS (PIC16F505), XT or LP modes, a crystal or ceramic resonator is connected to the (GP5/RB5)/ OSC1/(CLKIN) and (GP4/RB4)/OSC2/(CLKOUT) pins to establish oscillation (Figure 7-1). The PIC12F508/ 509/16F505 oscillator designs require the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in HS (PIC16F505), XT or LP modes, the device can have an external clock source drive the (GP5/RB5)/OSC1/CLKIN pin (Figure 7-2). When the part is used in this fashion, the output drive levels on the OSC2 pin are very weak. This pin should be left open and unloaded. Also, when using this mode, the external clock should observe the frequency limits for the clock mode chosen (HS, XT or LP).

- Note 1: This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

- 2: The user should verify that the device oscillator starts and performs as expected. Adjusting the loading capacitor values and/or the Oscillator mode may be required.

FIGURE 7-2:

EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

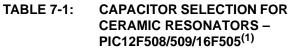

| Osc<br>Type       | Resonator<br>Freq.                                                                                                                                                                                            | Cap. Range<br>C1 | Cap. Range<br>C2 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|

| XT                | 4.0 MHz                                                                                                                                                                                                       | 30 pF            | 30 pF            |

| HS <sup>(2)</sup> | 16 MHz                                                                                                                                                                                                        | 10-47 pF         | 10-47 pF         |

| Note 1:           | These values are for design guidance<br>only. Since each resonator has its own<br>characteristics, the user should consult<br>the resonator manufacturer for<br>appropriate values of external<br>components. |                  |                  |

| 2:                | PIC16F505                                                                                                                                                                                                     | only.            |                  |

# TABLE 7-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR – PIC12F508/509/16F505<sup>(2)</sup>

| Osc<br>Type       | Resonator<br>Freq.                                                                                                                                                                                                                                                                                    | Cap. Range<br>C1           | Cap. Range<br>C2           |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|

| LP                | 32 kHz <sup>(1)</sup>                                                                                                                                                                                                                                                                                 | 15 pF                      | 15 pF                      |

| XT                | 200 kHz<br>1 MHz<br>4 MHz                                                                                                                                                                                                                                                                             | 47-68 pF<br>15 pF<br>15 pF | 47-68 pF<br>15 pF<br>15 pF |

| HS <sup>(3)</sup> | 20 MHz                                                                                                                                                                                                                                                                                                | 15-47 pF                   | 15-47 pF                   |

| Note 1:           | For VDD > 4<br>recommend                                                                                                                                                                                                                                                                              | .5V, C1 = C2 ≈ ed.         | 30 pF is                   |

| 2:                | These values are for design guidance<br>only. Rs may be required to avoid over-<br>driving crystals with low drive level specifi-<br>cation. Since each crystal has its own<br>characteristics, the user should consult<br>the crystal manufacturer for appropriate<br>values of external components. |                            |                            |

| 3:                | PIC16F505                                                                                                                                                                                                                                                                                             | only.                      |                            |

#### 7.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

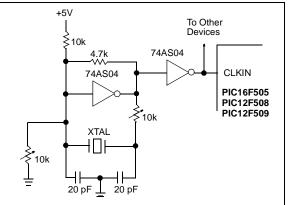

Figure 7-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

#### FIGURE 7-3:

#### EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

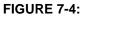

Figure 7-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

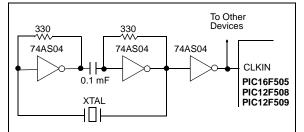

### 7.2.4 EXTERNAL RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit-to-unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 7-5 shows how the R/C combination is connected to the PIC12F508/509/16F505 devices. For REXT values below 3.0 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 5.0 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

**Section 10.0 "Electrical Characteristics"** shows RC frequency variation from part-to-part due to normal process variation. The variation is larger for larger values of R (since leakage current variation will affect RC frequency more for large R) and for smaller values of C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications section for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

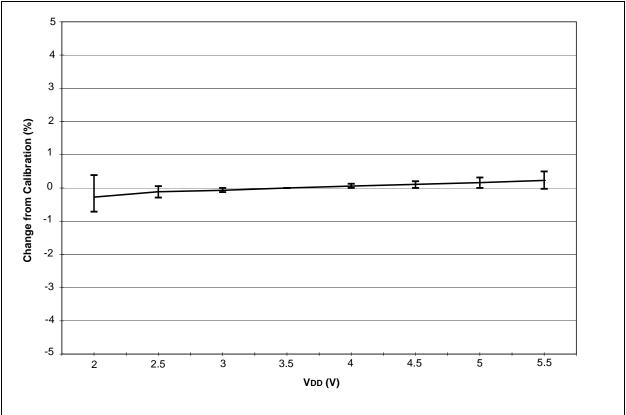

#### 7.2.5 INTERNAL 4 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and  $25^{\circ}C$ , (see **Section 10.0** "**Electrical Characteristics**" for information on variation over voltage and temperature).

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal RC oscillator. This location is always uncode protected, regardless of the code-protect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the Reset vector. This will load the W register with the calibration value upon Reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

| Note: | Erasing the device will also erase the pre- |  |  |

|-------|---------------------------------------------|--|--|

|       | programmed internal calibration value for   |  |  |

|       | the internal oscillator. The calibration    |  |  |

|       | value must be read prior to erasing the     |  |  |

|       | part so it can be reprogrammed correctly    |  |  |

|       | later.                                      |  |  |

For the PIC12F508/509/16F505 devices, only bits <7:1> of OSCCAL are implemented. Bits CAL6-CAL0 are used for calibration. Adjusting CAL6-CAL0 from '0000000' to '1111111' changes the clock speed. See Register 4-5 for more information.

| Note: | The 0 bit of OSCCAL is unimplemented    |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|

|       | and should be written as '0' when       |  |  |  |  |  |

|       | modifying OSCCAL for compatibility with |  |  |  |  |  |

|       | future devices.                         |  |  |  |  |  |

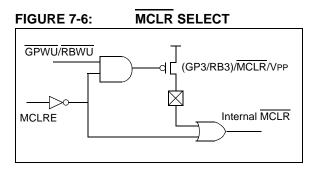

### 7.3.1 MCLR ENABLE

This Configuration bit, when unprogrammed (left in the '1' state), enables the external MCLR function. When programmed, the MCLR function is tied to the internal VDD and the pin is assigned to be an input only. See Figure 7-6.

#### 7.4 Power-on Reset (POR)

The PIC12F508/509/16F505 devices incorporate an on-chip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the (GP3/RB3)/MCLR/VPP pin as MCLR and tie through a resistor to VDD, or program the pin as (GP3/RB3). An internal weak pull-up resistor is implemented using a transistor (refer to Table 10-2 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See **Section 10.0 "Electrical Characteristics"** for details.

When the devices start normal operation (exit the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the devices must be held in Reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-on Reset circuit is shown in Figure 7-7.

The Power-on Reset circuit and the Device Reset Timer (see **Section 7.5 "Device Reset Timer (DRT)**") circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will reset the Reset latch and thus end the on-chip Reset signal.

A power-up example where MCLR is held low is shown in Figure 7-8. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of Reset TDRT msec after MCLR goes high.

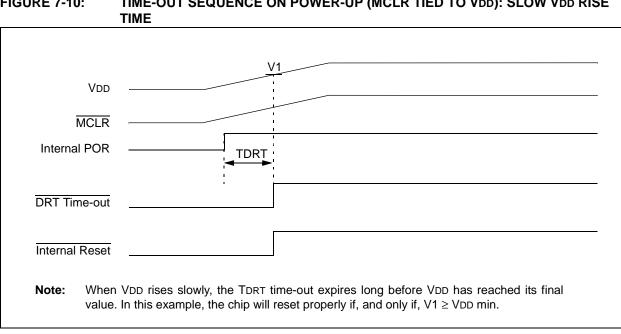

In Figure 7-9, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be (GP3/RB3). The VDD is stable before the start-up timer times out and there is no problem in getting a proper Reset. However, Figure 7-10 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 7-9).

| Note: | When the devices start normal operation     |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | (exit the Reset condition), device operat-  |  |  |  |  |

|       | ing parameters (voltage, frequency, tem-    |  |  |  |  |

|       | perature, etc.) must be met to ensure       |  |  |  |  |

|       | operation. If these conditions are not met, |  |  |  |  |

|       | the device must be held in Reset until the  |  |  |  |  |

|       | operating conditions are met.               |  |  |  |  |

For additional information, refer to Application Notes AN522 *"Power-Up Considerations"* (DS00522) and AN607 *"Power-up Trouble Shooting"* (DS00607).

#### TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE **FIGURE 7-10:**

#### 7.5 Device Reset Timer (DRT)

On the PIC12F508/509/16F505 devices, the DRT runs any time the device is powered up. DRT runs from Reset and varies based on oscillator selection and Reset type (see Table 7-6).

The DRT operates on an internal RC oscillator. The processor is kept in Reset as long as the DRT is active. The DRT delay allows VDD to rise above VDD min. and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the devices in a Reset condition for approximately 18 ms after MCLR has reached a logic high (VIH MCLR) level. Programming (GP3/RB3)/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases. This allows savings in cost-sensitive and/or space restricted applications, as well as allowing the use of the (GP3/RB3)/MCLR/VPP pin as a general purpose input.

The Device Reset Time delays will vary from chip-tochip due to VDD, temperature and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out from Sleep. This is particularly important for applications using the WDT to wake from Sleep mode automatically.

Reset sources are POR, MCLR, WDT time-out and wake-up on pin change. See Section 7.9.2 "Wake-up from Sleep", Notes 1, 2 and 3.

### 7.6 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the external RC oscillator of the (GP5/RB5)/OSC1/CLKIN pin and the internal 4 MHz oscillator. This means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or Sleep, a WDT Reset or wake-up Reset, generates a device Reset.

The  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset.

The WDT can be permanently disabled by programming the configuration WDTE as a '0' (see **Section 7.1 "Configuration Bits"**). Refer to the PIC12F508/509/16F505 Programming Specifications to determine how to access the Configuration Word.

## TABLE 7-6:DRT (DEVICE RESET TIMER<br/>PERIOD)

| Oscillator<br>Configuration | POR Reset       | Subsequent<br>Resets |

|-----------------------------|-----------------|----------------------|

| INTOSC, EXTRC               | 18 ms (typical) | 10 μs (typical)      |

| HS <sup>(1)</sup> , XT, LP  | 18 ms (typical) | 18 ms (typical)      |

| EC <sup>(1)</sup>           | 18 ms (typical) | 10 μs (typical)      |

Note 1: PIC16F505 only.

#### 7.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, a time-out period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see DC specs).

Under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

#### 7.6.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the postscaler, if assigned to the WDT, and prevents it from timing out and generating a device Reset.

The SLEEP instruction resets the WDT and the postscaler, if assigned to the WDT. This gives the maximum Sleep time before a WDT wake-up Reset.

#### 7.9 Power-down Mode (Sleep)

A device may be powered down (Sleep) and later powered up (wake-up from Sleep).

#### 7.9.1 SLEEP

The Power-Down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit (STATUS<4>) is set, the PD bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low or high-impedance).

**Note:** A Reset generated by a WDT time-out does not drive the MCLR pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or Vss and the (GP3/RB3)/MCLR/VPP pin must be at a logic high level if MCLR is enabled.

#### 7.9.2 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- An external Reset input on (GP3/RB3)/MCLR/ VPP pin, when configured as MCLR.

- 2. A Watchdog Timer time-out Reset (if WDT was enabled).

- A change on input pin GP0/RB0, GP1/RB1, GP3/RB3 or RB4 when wake-up on change is enabled.

These events cause a device Reset. The  $\overline{TO}$ ,  $\overline{PD}$  and GPWUF/RBWUF bits can be used to determine the cause of device Reset. The  $\overline{TO}$  bit is cleared if a WDT time-out occurred (and caused wake-up). The  $\overline{PD}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The GPWUF/RBWUF bit indicates a change in state while in Sleep at pins GP0/RB0, GP1/RB1, GP3/RB3 or RB4 (since the last file or bit operation on GP/RB port).

Note: Caution: Right before entering Sleep, read the input pins. When in Sleep, wakeup occurs when the values at the pins change from the state they were in at the last reading. If a wake-up on change occurs and the pins are not read before reentering Sleep, a wake-up will occur immediately even if no pins change while in Sleep mode.

The WDT is cleared when the device wakes from Sleep, regardless of the wake-up source.

#### 7.10 Program Verification/Code Protection

If the code protection bit has not been programmed, the on-chip program memory can be read out for verification purposes.

The first 64 locations and the last location (OSCCAL) can be read, regardless of the code protection bit setting.

The last memory location can be read regardless of the code protection bit setting on the PIC12F508/509/ 16F505 devices.

#### 7.11 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '0's.

### 7.12 In-Circuit Serial Programming™

The PIC12F508/509/16F505 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The devices are placed into a Program/Verify mode by holding the <u>GP1/RB1</u> and GP0/RB0 pins low while raising the <u>MCLR</u> (VPP) pin from VIL to VIHH (see programming specification). GP1/RB1 becomes the programming clock and GP0/RB0 becomes the programming data. Both GP1/RB1 and GP0/RB0 are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial programming, please refer to the PIC12F508/509/16F505 Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 7-15.

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] IORWF f,d                                                                                                                                                           |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                   |  |  |  |  |

| Operation:       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                            |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1',<br>the result is placed back in register<br>'f'. |  |  |  |  |

| MOVWF            | Move W to f                                    |  |  |  |  |

|------------------|------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWF f                       |  |  |  |  |

| Operands:        | $0 \le f \le 31$                               |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                          |  |  |  |  |

| Status Affected: | None                                           |  |  |  |  |

| Description:     | Move data from the W register to register 'f'. |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                           |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                 |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                        |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                         |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                |  |  |  |  |

| Description:     | The contents of register 'f' are<br>moved to destination 'd'. If 'd' is '0',<br>destination is the W register. If 'd'<br>is '1', the destination is file<br>register 'f'. 'd' = 1 is useful as a<br>test of a file register, since status<br>flag Z is affected. |  |  |  |  |

| NOP              | No Operation  |  |  |  |  |

|------------------|---------------|--|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |  |

| Operands:        | None          |  |  |  |  |

| Operation:       | No operation  |  |  |  |  |

| Status Affected: | None          |  |  |  |  |

| Description:     | No operation. |  |  |  |  |

| MOVLW            | Move Literal to W                                                                                        |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                                 |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                        |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                                      |  |  |  |  |

| Status Affected: | None                                                                                                     |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded<br>into the W register. The "don't<br>cares" will assembled as '0's. |  |  |  |  |

| OPTION           | Load OPTION Register                                                 |  |  |  |  |

|------------------|----------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] OPTION                                                       |  |  |  |  |

| Operands:        | None                                                                 |  |  |  |  |

| Operation:       | $(W) \to OPTION$                                                     |  |  |  |  |

| Status Affected: | None                                                                 |  |  |  |  |

| Description:     | The content of the W register is<br>loaded into the OPTION register. |  |  |  |  |

(W) .XOR.  $k \rightarrow (W)$

The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in the W

Ζ

register.

Operation: Status Affected:

Description:

| TRIS             | Load TRIS Register                         | XORWF            | Exclusive OR W with f                                                                                                                              |

|------------------|--------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] TRIS f                             | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                         |

| Operands:        | f = 6                                      | Operands:        | $0 \le f \le 31$                                                                                                                                   |

| Operation:       | (W) $\rightarrow$ TRIS register f          |                  | d ∈ [0,1]                                                                                                                                          |

| Status Affected: | None                                       | Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                 |

| Description:     | TRIS register 'f' (f = 6 or 7) is          | Status Affected: | Z                                                                                                                                                  |

|                  | loaded with the contents of the W register | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is |

| XORLW            | Exclusive OR literal with W                |                  | stored back in register 'f'.                                                                                                                       |

| Syntax:          | [ <i>label</i> ] XORLW k                   |                  | <u> </u>                                                                                                                                           |

| Operands:        | $0 \le k \le 255$                          |                  |                                                                                                                                                    |

| AC CHARACTERISTICS |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |                    |        |       |                                            |

|--------------------|-------|------------------------------------------------------|------|--------------------|--------|-------|--------------------------------------------|

| Param<br>No.       | Sym.  | Characteristic                                       | Min. | Тур <sup>(1)</sup> | Max.   | Units | Conditions                                 |

| 1A                 | Fosc  | External CLKIN Frequency <sup>(2)</sup>              | DC   | _                  | 4      | MHz   | XT Oscillator mode                         |

|                    |       |                                                      | DC   | —                  | 20     | MHz   | EC, HS Oscillator mode<br>(PIC16F505 only) |

|                    |       |                                                      | DC   | —                  | 200    | kHz   | LP Oscillator mode                         |

|                    |       | Oscillator Frequency <sup>(2)</sup>                  | —    |                    | 4      | MHz   | EXTRC Oscillator mode                      |

|                    |       |                                                      | 0.1  | —                  | 4      | MHz   | XT Oscillator mode                         |

|                    |       |                                                      | 4    | —                  | 20     | MHz   | HS Oscillator mode (PIC16F505 only)        |

|                    |       |                                                      | —    | —                  | 200    | kHz   | LP Oscillator mode                         |

| 1                  | Tosc  | External CLKIN Period <sup>(2)</sup>                 | 250  | —                  | _      | ns    | XT Oscillator mode                         |

|                    |       |                                                      | 50   | —                  | —      | ns    | EC, HS Oscillator mode<br>(PIC16F505 only) |

|                    |       |                                                      | 5    |                    | —      | μs    | LP Oscillator mode                         |

|                    |       | Oscillator Period <sup>(2)</sup>                     | 250  |                    | _      | ns    | EXTRC Oscillator mode                      |

|                    |       |                                                      | 250  | —                  | 10,000 | ns    | XT Oscillator mode                         |

|                    |       |                                                      | 50   | —                  | 250    | ns    | HS Oscillator mode (PIC16F505 only)        |

|                    |       |                                                      | 5    | —                  | —      | μs    | LP Oscillator mode                         |

| 2                  | Тсү   | Instruction Cycle Time                               | 200  | 4/Fosc             | —      | ns    |                                            |

| 3                  | TosL, | Clock in (OSC1) Low or High                          | 50*  | _                  | _      | ns    | XT Oscillator                              |

|                    | TosH  | Time                                                 | 2*   | —                  | —      | μs    | LP Oscillator                              |

|                    |       |                                                      | 10*  | —                  | —      | ns    | EC, HS Oscillator<br>(PIC16F505 only)      |

| 4                  | TosR, | Clock in (OSC1) Rise or Fall                         | —    | —                  | 25*    | ns    | XT Oscillator                              |

|                    | TosF  | Time                                                 | —    | —                  | 50*    | ns    | LP Oscillator                              |

|                    |       |                                                      | —    | _                  | 15*    | ns    | EC, HS Oscillator<br>(PIC16F505 only)      |

#### **TABLE 10-3**: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC12F508/509/16F505

Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for Note 1: design guidance only and are not tested.

2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

| AC CHA       | ARACTER | ISTICS                                                 | Standard Operating Conditions (unless otherw<br>Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (inc<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ (e) |              |              | 5°C (industrial), |            |                                                                                                      |

|--------------|---------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|-------------------|------------|------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym.    | Characteristic                                         | Freq<br>Tolerance                                                                                                                                                | Min.         | Тур†         | Max.              | Units      | Conditions                                                                                           |

| F10          | Fosc    | Internal Calibrated<br>INTOSC Frequency <sup>(1)</sup> | ± 1%<br>± 2%                                                                                                                                                     | 3.96<br>3.92 | 4.00<br>4.00 | 4.04<br>4.08      | MHz<br>MHz | VDD = $3.5V$ , TA = $25^{\circ}C$<br>$2.5V \le VDD \le 5.5V$<br>$0^{\circ}C \le TA \le +85^{\circ}C$ |

|              |         |                                                        | ± 5%                                                                                                                                                             | 3.80         | 4.00         | 4.20              | MHz        | $2.0V \le VDD \le 5.5V$<br>-40°C $\le TA \le +85°C$ (Ind.)<br>-40°C $\le TA \le +125°C$ (Ext.)       |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1 uF and 0.01 uF values in parallel are recommended.

FIGURE 10-5: I/O TIMING – PIC12F508/509/16F505

\*

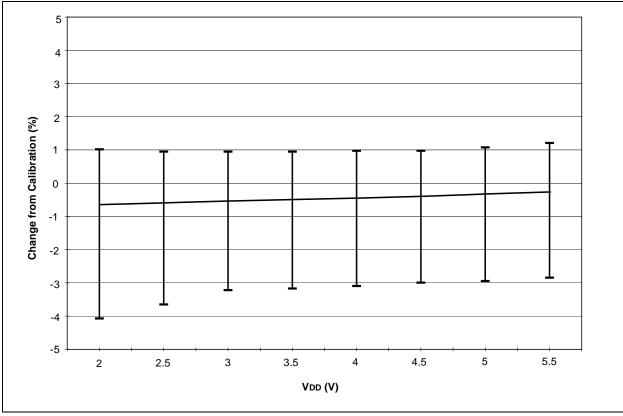

#### FIGURE 11-14: TYPICAL INTOSC FREQUENCY CHANGE vs VDD (25°C)

### INDEX

| Α               |  |

|-----------------|--|

| ALU             |  |

| Assembler       |  |

| MPASM Assembler |  |

### В

| Block Diagram                |    |

|------------------------------|----|

| On-Chip Reset Circuit        | 50 |

| Timer0                       |    |

| TMR0/WDT Prescaler           | 39 |

| Watchdog Timer               |    |

| Brown-Out Protection Circuit | 54 |

### С

| C Compilers                          |    |

|--------------------------------------|----|

| MPLAB C18                            |    |

| MPLAB C30                            |    |

| Carry                                |    |

| Clocking Scheme                      |    |

| Code Protection                      |    |

| Configuration Bits                   |    |

| Configuration Word                   | 43 |

| Customer Change Notification Service |    |

| Customer Notification Service        |    |

| Customer Support                     |    |

|                                      |    |

#### D

| DC and AC Characteristics | 81 |

|---------------------------|----|

| Development Support       | 65 |

| Digit Carry               | 11 |

### Е

| Errata | 6 |

|--------|---|

|--------|---|

## F

| Family of Devices       |   |

|-------------------------|---|

| PIC12F508/509/PIC16F505 | 7 |

| FSR                     |   |

#### I

| I/O Interfacing                |        |

|--------------------------------|--------|

| I/O Ports                      |        |

| I/O Programming Considerations |        |

| ID Locations                   | 41, 55 |

| INDF                           |        |

| Indirect Data Addressing       |        |

| Instruction Cycle              | 16     |

| Instruction Flow/Pipelining    | 16     |

| Instruction Set Summary        | 58     |

| Internet Address               | 107    |

#### L

### Μ

| Memory Organization                       | 17 |

|-------------------------------------------|----|

| Data Memory                               |    |

| Program Memory (PIC12F508/509)            | 17 |

| Program Memory (PIC16F505)                |    |

| Microchip Internet Web Site               |    |

| MPLAB ASM30 Assembler, Linker, Librarian  | 66 |

| MPLAB ICD 2 In-Circuit Debugger           | 67 |

| MPLAB ICE 2000 High-Performance Universal |    |

| In-Circuit Emulator                       | 67 |

|                                           |    |

| MPLAB Integrated Development Environment Software | 65 |

|---------------------------------------------------|----|

| MPLAB PM3 Device Programmer                       | 67 |

| MPLAB REAL ICE In-Circuit Emulator System         | 67 |

| MPLINK Object Linker/MPLIB Object Librarian       | 66 |

#### 0

| Option Register           |    |

|---------------------------|----|

| OSC selection             | 41 |

| OSCCAL Register           | 26 |

| Oscillator Configurations | 44 |

| Oscillator Types          |    |

| HS                        | 44 |

| LP                        | 44 |

| RC                        | 44 |

| ХТ                        | 44 |

|                           |    |

#### Ρ

| PIC12F508/509/16F505 Device Varieties<br>PICSTART Plus Development Programmer<br>POR |                |

|--------------------------------------------------------------------------------------|----------------|

|                                                                                      |                |

| Device Reset Timer (DRT)                                                             | 41, 52         |

| PD                                                                                   | 54, 41         |

| TO                                                                                   |                |

| PORTB                                                                                | 31             |

| Power-down Mode                                                                      | 55             |

| Prescaler                                                                            | 38             |

| Program Counter                                                                      | 27             |

| PORTB<br>Power-down Mode                                                             | 31<br>55<br>38 |

### Q

| Q cycles 16 |

|-------------|

|-------------|

#### R

| RC Oscillator      | 45  |

|--------------------|-----|

| Reader Response    | 108 |

| Read-Modify-Write  | 33  |

| Register File Map  |     |

| PIC12F508          | 19  |

| PIC12F509          | 19  |

| PIC16F505          | 19  |

| Registers          |     |

| Special Function   | 20  |

| Reset              | 41  |

| Reset on Brown-Out | 54  |

|                    |     |

### S

| Sleep                          | 41. 55 |

|--------------------------------|--------|

| Software Simulator (MPLAB SIM) |        |

| Special Features of the CPU    |        |

| Special Function Registers     | 20     |

| Stack                          |        |

| Status Register                | 11, 22 |

#### Т

| 35 |

|----|

| 35 |

| 37 |

| 75 |

| 75 |

| 31 |

|    |

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | <u>x /xx xxx</u>                                                                                                                                                           | Examples:                                                                                                                                                                                                   |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                | Temperature Package Pattern<br>Range                                                                                                                                       | <ul> <li>a) PIC12F508-E/P 301 = Extended Temp., PDIP<br/>package, QTP pattern #301</li> <li>b) PIC12F508-I/SN = Industrial Temp., SOIC<br/>package</li> </ul>                                               |

| Device:               | PIC16F505<br>PIC12F508<br>PIC12F509<br>PIC16F505T <sup>(1)</sup><br>PIC12F508T <sup>(2)</sup><br>PIC12F509T <sup>(2)</sup>                                                 | <ul> <li>package</li> <li>c) PIC12F508T-E/P = Extended Temp., PDIP package, Tape and Reel</li> </ul>                                                                                                        |

| Temperature<br>Range: | $ \begin{array}{rcl} I &=& -40^{\circ} C \text{ to } +85^{\circ} C \text{ (Industrial)} \\ E &=& -40^{\circ} C \text{ to } +125^{\circ} C \text{ (Extended)} \end{array} $ |                                                                                                                                                                                                             |

| Package:              | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                       | <ul> <li>Note 1: T = in tape and reel SOIC, TSSOP and QFN packages only</li> <li>2: T = in tape and reel SOIC and MSOP packages only.</li> <li>3: PIC12F508/PIC12F509 only.</li> <li>4: Pb-free.</li> </ul> |

|                       | Special Requirements<br>and Reel available for only the following packages: SOIC, MSOP<br>TSSOP.                                                                           | 5: PIC16F505 only.                                                                                                                                                                                          |

|                       |                                                                                                                                                                            |                                                                                                                                                                                                             |