Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 1.5KB (1K x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 72 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 14-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f505-e-st |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Name           | Function | Input<br>Type | Output<br>Type | Description                                                                                                                                                                                                                                                                                           |

|----------------|----------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0/ICSPDAT    | GP0      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                                     |

|                | ICSPDAT  | ST            | CMOS           | In-Circuit Serial Programming™ data pin.                                                                                                                                                                                                                                                              |

| GP1/ICSPCLK    | GP1      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                                     |

|                | ICSPCLK  | ST            | CMOS           | In-Circuit Serial Programming clock pin.                                                                                                                                                                                                                                                              |

| GP2/T0CKI      | GP2      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                |

|                | T0CKI    | ST            | _              | Clock input to TMR0.                                                                                                                                                                                                                                                                                  |

| GP3/MCLR/Vpp   | GP3      | TTL           | —              | Input pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                                                 |

|                | MCLR     | ST            | _              | Master Clear (Reset). When configured as $\overline{MCLR}$ , this pin is<br>an active-low Reset to the device. Voltage on $\overline{MCLR}$ /VPP must<br>not exceed VDD during normal device operation or the device<br>will enter Programming mode. Weak pull-up always on if<br>configured as MCLR. |

|                | Vpp      | ΗV            | _              | Programming voltage input.                                                                                                                                                                                                                                                                            |

| GP4/OSC2       | GP4      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                |

|                | OSC2     | _             | XTAL           | Oscillator crystal output. Connections to crystal or resonator in Crystal Oscillator mode (XT and LP modes only, GPIO in other modes).                                                                                                                                                                |

| GP5/OSC1/CLKIN | GP5      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                |

|                | OSC1     | XTAL          | _              | Oscillator crystal input.                                                                                                                                                                                                                                                                             |

|                | CLKIN    | ST            | _              | External clock source input.                                                                                                                                                                                                                                                                          |

| Vdd            | Vdd      |               | Р              | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                                               |

| Vss            | Vss      |               | Р              | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                              |

**Legend:** I = Input, O = Output, I/O = Input/Output, P = Power, — = Not used, TTL = TTL input, ST = Schmitt Trigger input, HV = High Voltage

### 4.7 **Program Counter**

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

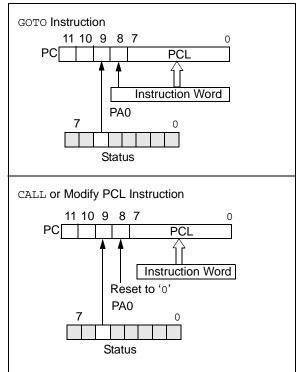

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The Program Counter (PCL) is mapped to PC<7:0>. Bit 5 of the STATUS register provides page information to bit 9 of the PC (Figure 4-6).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 4-6).

Instructions where the PCL is the destination, or modify PCL instructions, include MOVWF PC, ADDWF PC and BSF PC, 5.

Note: Because PC<8> is cleared in the CALL instruction or any modify PCL instruction, all subroutine calls or computed jumps are limited to the first 256 locations of any program memory page (512 words long).

#### FIGURE 4-6: LOADING OF PC BRANCH INSTRUCTIONS

### 4.7.1 EFFECTS OF RESET

The PC is set upon a Reset, which means that the PC addresses the last location in the last page (i.e., the oscillator calibration instruction). After executing MOVLW XX, the PC will roll over to location 00h and begin executing user code.

The STATUS register page preselect bits are cleared upon a Reset, which means that page 0 is pre-selected.

Therefore, upon a Reset, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered.

### 4.8 Stack

The PIC12F508/509/16F505 devices have a 2-deep, 12-bit wide hardware PUSH/POP stack.

A CALL instruction will PUSH the current value of Stack 1 into Stack 2 and then PUSH the current PC value, incremented by one, into Stack Level 1. If more than two sequential CALLs are executed, only the most recent two return addresses are stored.

A RETLW instruction will POP the contents of Stack Level 1 into the PC and then copy Stack Level 2 contents into Stack Level 1. If more than two sequential RETLWS are executed, the stack will be filled with the address previously stored in Stack Level 2. Note that the W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

| Note 1: | There are no Status bits to indicate stack |       |        |              |             |

|---------|--------------------------------------------|-------|--------|--------------|-------------|

|         | overflo                                    | ws or | r stad | ck underflow | conditions. |

| 2:      | There                                      | are   | no     | instruction  | mnemonics   |

called PUSH or POP. These are actions that occur from the execution of the CALL and RETLW instructions.

## 7.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of real-time applications. The PIC12F508/509/16F505 microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These features are:

- Oscillator Selection

- Reset:

- Power-on Reset (POR)

- Device Reset Timer (DRT)

- Wake-up from Sleep on Pin Change

- Watchdog Timer (WDT)

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

- Clock Out

The PIC12F508/509/16F505 devices have a Watchdog Timer, which can be shut off only through Configuration bit WDTE. It runs off of its own RC oscillator for added reliability. If using HS (PIC16F505), XT or LP selectable oscillator options, there is always an 18 ms (nominal) delay provided by the Device Reset Timer (DRT), intended to keep the chip in Reset until the crystal oscillator is stable. If using INTRC or EXTRC, there is an 18 ms delay only on VDD power-up. With this timer on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through a change on input pins or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application, including an internal 4 MHz oscillator. The EXTRC oscillator option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options.

### 7.1 Configuration Bits

The PIC12F508/509/16F505 Configuration Words consist of 12 bits. Configuration bits can be programmed to select various device configurations. Three bits are for the selection of the oscillator type; (two bits on the PIC12F508/509), one bit is the Watchdog Timer enable bit, one bit is the MCLR enable bit and one bit is for code protection (Register 7-1, Register 7-2).

### **REGISTER 7-2:** CONFIGURATION WORD FOR PIC16F505<sup>(1)</sup>

| —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |                                 |    | MCLRE          | CP          | WDTE        | FOSC2        | FOSC1   | FOSC0 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|----|----------------|-------------|-------------|--------------|---------|-------|

| bit 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            | ·                               | i  |                |             |             |              |         | bit 0 |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |                                 |    |                |             |             |              |         |       |

| R = Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | able bit                                                                   | W = Writable b                  | t  | U = Unimp      | lemented    | bit, read a | s '0'        |         |       |

| -n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | e at POR                                                                   | '1' = Bit is set                |    | '0' = Bit is o | cleared     |             | x = Bit is ι | Inknown |       |

| bit 11-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Unimplemented                                                              | l: Read as 'o'                  |    |                |             |             |              |         |       |

| bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>MCLRE:</b> RB3/M0<br>1 = RB3/MCLR p<br>0 = RB3/MCLR p                   | oin function is $\overline{MC}$ | LR | LR internally  | v tied to ' | Vdd         |              |         |       |

| bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |                                 |    |                |             |             |              |         |       |

| bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | t 3 WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled |                                 |    |                |             |             |              |         |       |

| bit 2-0 <b>FOSC&lt;1:0&gt;:</b> Oscillator Selection bits<br>111 = External RC oscillator/CLKOUT function on RB4/OSC2/CLKOUT pin<br>110 = External RC oscillator/RB4 function on RB4/OSC2/CLKOUT pin<br>101 = Internal RC oscillator/CLKOUT function on RB4/OSC2/CLKOUT pin<br>100 = Internal RC oscillator/RB4 function on RB4/OSC2/CLKOUT pin<br>011 = EC oscillator/RB4 function on RB4/OSC2/CLKOUT pin<br>011 = EC oscillator/RB4 function on RB4/OSC2/CLKOUT pin<br>010 = HS oscillator<br>010 = HS oscillator<br>001 = XT oscillator<br>000 = LP oscillator |                                                                            |                                 |    |                |             |             |              |         |       |

**Note 1:** Refer to the "*PIC16F505 Memory Programming Specifications*" (DS41226) to determine how to access the Configuration Word. The Configuration Word is not user addressable during device operation.

### 7.2 Oscillator Configurations

### 7.2.1 OSCILLATOR TYPES

The PIC12F508/509/16F505 devices can be operated in up to six different oscillator modes. The user can program up to three Configuration bits (FOSC<1:0> [PIC12F508/509], FOSC<2:0> [PIC16F505]). To select one of these modes:

- LP: Low-Power Crystal

- XT: Crystal/Resonator

- HS: High-Speed Crystal/Resonator (PIC16F505 only)

- INTRC: Internal 4 MHz Oscillator

- EXTRC: External Resistor/Capacitor

- EC: External High-Speed Clock Input (PIC16F505 only)

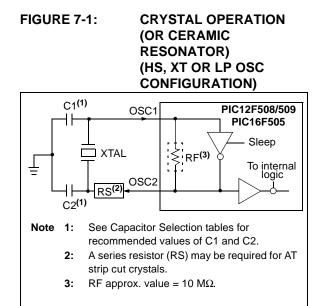

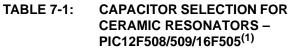

### 7.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

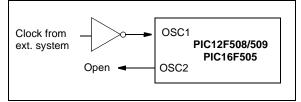

In HS (PIC16F505), XT or LP modes, a crystal or ceramic resonator is connected to the (GP5/RB5)/ OSC1/(CLKIN) and (GP4/RB4)/OSC2/(CLKOUT) pins to establish oscillation (Figure 7-1). The PIC12F508/ 509/16F505 oscillator designs require the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in HS (PIC16F505), XT or LP modes, the device can have an external clock source drive the (GP5/RB5)/OSC1/CLKIN pin (Figure 7-2). When the part is used in this fashion, the output drive levels on the OSC2 pin are very weak. This pin should be left open and unloaded. Also, when using this mode, the external clock should observe the frequency limits for the clock mode chosen (HS, XT or LP).

- Note 1: This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

- 2: The user should verify that the device oscillator starts and performs as expected. Adjusting the loading capacitor values and/or the Oscillator mode may be required.

FIGURE 7-2:

EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

| Osc<br>Type       | Resonator<br>Freq.                                                                                                                                                                                            | Cap. Range<br>C1 | Cap. Range<br>C2 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|

| XT                | 4.0 MHz                                                                                                                                                                                                       | 30 pF            | 30 pF            |

| HS <sup>(2)</sup> | 16 MHz                                                                                                                                                                                                        | 10-47 pF         | 10-47 pF         |

| Note 1:           | These values are for design guidance<br>only. Since each resonator has its own<br>characteristics, the user should consult<br>the resonator manufacturer for<br>appropriate values of external<br>components. |                  |                  |

| 2:                | PIC16F505                                                                                                                                                                                                     | only.            |                  |

# TABLE 7-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR – PIC12F508/509/16F505<sup>(2)</sup>

| Osc<br>Type       | Resonator<br>Freq.                                                                                                                                                                                                                                                                                    | 5                          |                            |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|

| LP                | 32 kHz <sup>(1)</sup>                                                                                                                                                                                                                                                                                 | 15 pF                      | 15 pF                      |

| XT                | 200 kHz<br>1 MHz<br>4 MHz                                                                                                                                                                                                                                                                             | 47-68 pF<br>15 pF<br>15 pF | 47-68 pF<br>15 pF<br>15 pF |

| HS <sup>(3)</sup> | 20 MHz                                                                                                                                                                                                                                                                                                | 15-47 pF                   | 15-47 pF                   |

| Note 1:           | For VDD > 4.5V, C1 = C2 $\approx$ 30 pF is recommended.                                                                                                                                                                                                                                               |                            |                            |

| 2:                | These values are for design guidance<br>only. Rs may be required to avoid over-<br>driving crystals with low drive level specifi-<br>cation. Since each crystal has its own<br>characteristics, the user should consult<br>the crystal manufacturer for appropriate<br>values of external components. |                            |                            |

| 3:                | PIC16F505 only.                                                                                                                                                                                                                                                                                       |                            |                            |

### 7.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

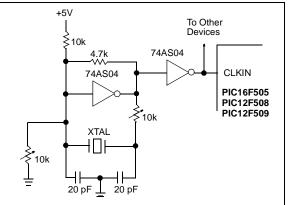

Figure 7-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

### FIGURE 7-3:

#### EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

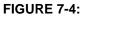

Figure 7-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

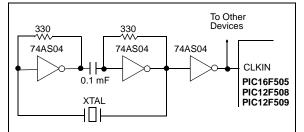

### 7.2.4 EXTERNAL RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit-to-unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 7-5 shows how the R/C combination is connected to the PIC12F508/509/16F505 devices. For REXT values below 3.0 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 5.0 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

**Section 10.0 "Electrical Characteristics"** shows RC frequency variation from part-to-part due to normal process variation. The variation is larger for larger values of R (since leakage current variation will affect RC frequency more for large R) and for smaller values of C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications section for variation of oscillator frequency due to VDD for given REXT/CEXT values, as well as frequency variation due to operating temperature for given R, C and VDD values.

### 7.2.5 INTERNAL 4 MHz RC OSCILLATOR

The internal RC oscillator provides a fixed 4 MHz (nominal) system clock at VDD = 5V and  $25^{\circ}C$ , (see **Section 10.0** "**Electrical Characteristics**" for information on variation over voltage and temperature).

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal RC oscillator. This location is always uncode protected, regardless of the code-protect settings. This value is programmed as a MOVLW XX instruction where XX is the calibration value, and is placed at the Reset vector. This will load the W register with the calibration value upon Reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

| Note: | Erasing the device will also erase the pre- |

|-------|---------------------------------------------|

|       | programmed internal calibration value for   |

|       | the internal oscillator. The calibration    |

|       | value must be read prior to erasing the     |

|       | part so it can be reprogrammed correctly    |

|       | later.                                      |

For the PIC12F508/509/16F505 devices, only bits <7:1> of OSCCAL are implemented. Bits CAL6-CAL0 are used for calibration. Adjusting CAL6-CAL0 from '0000000' to '1111111' changes the clock speed. See Register 4-5 for more information.

| Note: | The 0 bit of OSCCAL is unimplemented    |

|-------|-----------------------------------------|

|       | and should be written as '0' when       |

|       | modifying OSCCAL for compatibility with |

|       | future devices.                         |

### 7.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT time-out Reset during normal operation

- WDT time-out Reset during Sleep

- Wake-up from Sleep on pin change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up on pin change Reset during normal operation. They are not affected by a WDT Reset during Sleep or MCLR Reset during Sleep, since these Resets are viewed as resumption of normal operation. The exceptions to this are TO, PD and RBWUF/GPWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 7-4 for a full description of Reset states of all registers.

| Register           | Address | Power-on Reset           | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change |

|--------------------|---------|--------------------------|----------------------------------------------------|

| W                  | _       | qqqq qqqu <sup>(1)</sup> | qqqq qqqu <sup>(1)</sup>                           |

| INDF               | 00h     | XXXX XXXX                | uuuu uuuu                                          |

| TMR0               | 01h     | xxxx xxxx                | uuuu uuuu                                          |

| PC                 | 02h     | 1111 1111                | 1111 1111                                          |

| STATUS             | 03h     | 0001 1xxx                | q00q quuu <b>(2), (3)</b>                          |

| FSR <sup>(4)</sup> | 04h     | 110x xxxx                | 11uu uuuu                                          |

| FSR <sup>(5)</sup> | 04h     | 111x xxxx                | 111u uuuu                                          |

| OSCCAL             | 05h     | 1111 111-                | uuuu uuu-                                          |

| GPIO               | 06h     | xx xxxx                  | uu uuuu                                            |

| OPTION             | —       | 1111 1111                | 1111 1111                                          |

| TRIS               | —       | 11 1111                  | 11 1111                                            |

|                    |         |                          |                                                    |

#### TABLE 7-3: RESET CONDITIONS FOR REGISTERS – PIC12F508/509

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

2: See Table 7-5 for Reset value for specific conditions.

**3:** If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

4: PIC12F509 only.

5: PIC12F508 only.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSS f,b                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                                                             |

| Operation:       | skip if (f <b>) = <math>1</math></b>                                                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                                        |

| Description:     | If bit 'b' in register 'f' is '1', then the next instruction is skipped.<br>If bit 'b' is '1', then the next instruction fetched during the current instruction execution, is discarded and a NOP is executed instead, making this a two-cycle instruction. |

| CLRW             | Clear W                                                                |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [ label ] CLRW                                                         |

| Operands:        | None                                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                      |

| Description:     | The W register is cleared. Zero bit (Z) is set.                        |

| CALL             | Subroutine Call                                                                                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                                              |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                                                                                                    |

| Operation:       | $(PC) + 1 \rightarrow$ Top-of-Stack;<br>k $\rightarrow$ PC<7:0>;<br>$(STATUS<6:5>) \rightarrow$ PC<10:9>;<br>0 $\rightarrow$ PC<8>                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                                                 |

| Description:     | Subroutine call. First, return<br>address (PC + 1) is PUSHed onto<br>the stack. The eight-bit immediate<br>address is loaded into PC<br>bits <7:0>. The upper bits<br>PC<10:9> are loaded from<br>STATUS<6:5>, PC<8> is cleared.<br>CALL is a two-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                                                    |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                                                                                    |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT;} \\ 0 \rightarrow \underline{\text{WDT}} \text{ prescaler (if assigned);} \\ 1 \rightarrow \overline{\text{TO};} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                                                                  |

| Description:     | The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits $\overline{TO}$ and $\overline{PD}$ are set.                                   |

| CLRF             | Clear f                                                                |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                         |

| Operands:        | $0 \le f \le 31$                                                       |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                      |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.         |

| COMF             | Complement f                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                            |

| Operation:       | $(\overline{f})  ightarrow (dest)$                                                                                                                                          |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back in<br>register 'f'. |

### 9.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

### 9.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

### 9.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### TABLE 10-1: DC CHARACTERISTICS: PIC12F508/509/16F505 (Industrial, Extended)

| DC CHARACTERISTICS |      |                                            | Operating to      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |          |       |                                                                      |  |

|--------------------|------|--------------------------------------------|-------------------|------------------------------------------------------|----------|-------|----------------------------------------------------------------------|--|

| Param<br>No.       | Sym. | Characteristic                             | Min.              | Тур†                                                 | Max.     | Units | Conditions                                                           |  |

|                    | VIL  | Input Low Voltage                          |                   |                                                      |          |       |                                                                      |  |

|                    |      | I/O ports:                                 |                   |                                                      |          |       |                                                                      |  |

| D030               |      | with TTL buffer                            | Vss               | _                                                    | 0.8V     | V     | For all $4.5 \le VDD \le 5.5V$                                       |  |

| D030A              |      |                                            | Vss               | _                                                    | 0.15 Vdd | V     | Otherwise                                                            |  |

| D031               |      | with Schmitt Trigger buffer                | Vss               | _                                                    | 0.15 Vdd | V     |                                                                      |  |

| D032               |      | MCLR, TOCKI                                | Vss               | _                                                    | 0.15 Vdd | V     |                                                                      |  |

| D033               |      | OSC1 (in EXTRC)                            | Vss               | _                                                    | 0.15 Vdd | V     | (Note1)                                                              |  |

| D033               |      | OSC1 (in HS)                               | Vss               | _                                                    | 0.3 Vdd  | V     | (Note1)                                                              |  |

| D033               |      | OSC1 (in XT and LP)                        | Vss               | _                                                    | 0.3      | V     | (Note1)                                                              |  |

|                    | Vін  | Input High Voltage                         |                   |                                                      |          |       |                                                                      |  |

|                    |      | I/O ports:                                 |                   | _                                                    |          |       |                                                                      |  |

| D040               |      | with TTL buffer                            | 2.0               | _                                                    | Vdd      | v     | $4.5 \leq VDD \leq 5.5V$                                             |  |

| D040A              |      |                                            | 0.25 Vdd          | _                                                    | Vdd      | V     | Otherwise                                                            |  |

| D041               |      | with Schmitt Trigger buffer                | + 0.8<br>0.85 VDD | _                                                    | VDD      | v     | For entire VDD range                                                 |  |

| D042               |      | MCLR, TOCKI                                | 0.85 VDD          | _                                                    | VDD      | v     |                                                                      |  |

| D042               |      | OSC1 (in EXTRC)                            | 0.85 VDD          | _                                                    | VDD      | v     | (Note1)                                                              |  |

| D043               |      | OSC1 (in HS)                               | 0.7 VDD           | _                                                    | VDD      | v     | (Note1)                                                              |  |

| D043               |      | OSC1 (in XT and LP)                        | 1.6               | _                                                    | VDD      | v     |                                                                      |  |

| D070               | IPUR | GPIO/PORTB weak pull-up                    | 50                | 250                                                  | 400      | μA    | VDD = 5V, VPIN = VSS                                                 |  |

|                    |      | current <sup>(4)</sup>                     |                   |                                                      |          |       |                                                                      |  |

|                    | lı∟  | Input Leakage Current <sup>(2), (3)</sup>  |                   |                                                      |          |       |                                                                      |  |

| D060               |      | I/O ports                                  | —                 | —                                                    | ± 1      | μΑ    | $Vss \leq VPIN \leq VDD$ , Pin at high-impedance                     |  |

| D061               |      | GP3/RB3/MCLRI <sup>(5)</sup>               | —                 | ± 0.7                                                | ± 5      | μΑ    | $Vss \leq Vpin \leq Vdd$                                             |  |

| D063               |      | OSC1                                       | —                 | —                                                    | ± 5      | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration   |  |

|                    |      | Output Low Voltage                         |                   |                                                      |          |       |                                                                      |  |

| D080               |      | I/O ports/CLKOUT                           | —                 |                                                      | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V, -40°C to +85°C                             |  |

| D080A              |      |                                            | —                 | —                                                    | 0.6      | V     | IOL = 7.0 mA, VDD = 4.5V, -40°C to +125°C                            |  |

| D083               |      | OSC2                                       | —                 | —                                                    | 0.6      | V     | IOL = 1.6 mA, VDD = 4.5V, -40°C to +85°C                             |  |

| D083A              |      |                                            | —                 | _                                                    | 0.6      | V     | IOL = 1.2 mA, VDD = 4.5V, -40°C to +125°C                            |  |

|                    |      | Output High Voltage                        |                   |                                                      |          |       |                                                                      |  |

| D090               |      | I/O ports/CLKOUT <sup>(3)</sup>            | Vdd - 0.7         | —                                                    | —        | V     | IOH = -3.0 mA, VDD = 4.5V, -40°C to +85°C                            |  |

| D090A              |      |                                            | Vdd - 0.7         | —                                                    | —        | V     | IOH = -2.5 mA, VDD = 4.5V, -40°C to +125°C                           |  |

| D092               |      | OSC2                                       | Vdd - 0.7         | —                                                    | —        | V     | IOH = -1.3 mA, VDD = 4.5V, -40°C to +85°C                            |  |

| D092A              |      |                                            | Vdd - 0.7         | —                                                    | —        | V     | IOH = -1.0 mA, VDD = $4.5$ V, $-40^{\circ}$ C to $+125^{\circ}$ C    |  |

|                    |      | Capacitive Loading Specs on<br>Output Pins |                   |                                                      |          |       |                                                                      |  |

|                    |      |                                            |                   |                                                      | 1        | 1     |                                                                      |  |

| D100               |      | OSC2 pin                                   | _                 | —                                                    | 15       | pF    | In XT, HS and LP modes when external clock is<br>used to drive OSC1. |  |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. † 1:

Note

2:

3:

4:

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12F508/509/ 16F505 be driven with external clock in RC mode. The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages. Negative current is defined as coming out of the pin. The specification applies to all weak pull-up devices, including the weak pull-up on GP3/MCLR. The current listed will be the same whether GP3/MCLR is configured as GP3 with a weak pull-up or enabled as MCLR. This specification applies when GP3/RB3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic. 5:

| AC CHARACTERISTICS |      | Standard C<br>Operating                                | -                 | ature ·      | -40°C ≤      | Ta ≤ +8      | o <b>therwise specified)</b><br>5°C (industrial),<br>25°C (extended) |                                                                                                      |

|--------------------|------|--------------------------------------------------------|-------------------|--------------|--------------|--------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                         | Freq<br>Tolerance | Min.         | Тур†         | Max.         | Units                                                                | Conditions                                                                                           |

| F10                | Fosc | Internal Calibrated<br>INTOSC Frequency <sup>(1)</sup> | ± 1%<br>± 2%      | 3.96<br>3.92 | 4.00<br>4.00 | 4.04<br>4.08 | MHz<br>MHz                                                           | VDD = $3.5V$ , TA = $25^{\circ}C$<br>$2.5V \le VDD \le 5.5V$<br>$0^{\circ}C \le TA \le +85^{\circ}C$ |

|                    |      |                                                        | ± 5%              | 3.80         | 4.00         | 4.20         | MHz                                                                  | $2.0V \le VDD \le 5.5V$<br>-40°C $\le TA \le +85°C$ (Ind.)<br>-40°C $\le TA \le +125°C$ (Ext.)       |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1 uF and 0.01 uF values in parallel are recommended.

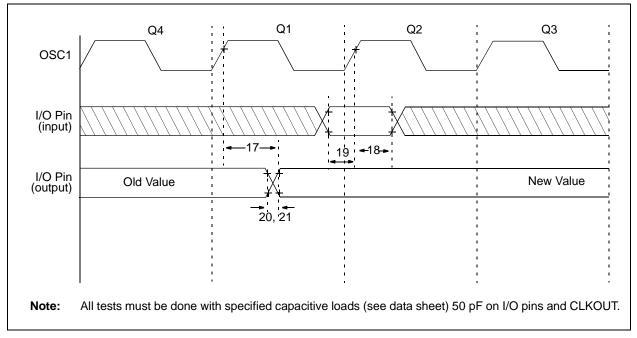

FIGURE 10-5: I/O TIMING – PIC12F508/509/16F505

\*

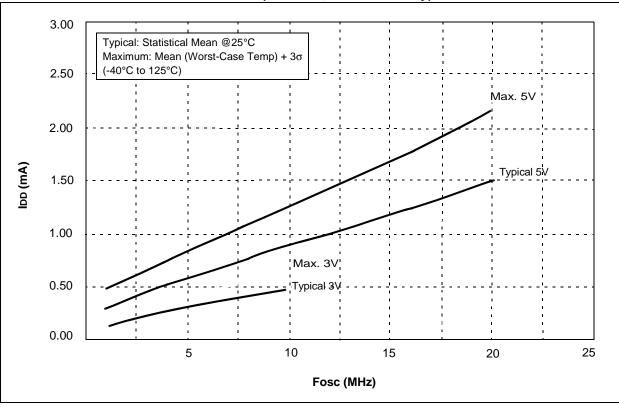

### FIGURE 11-2: IDD VS. FOSC Over VDD (HS MODE, PIC16F505 only)

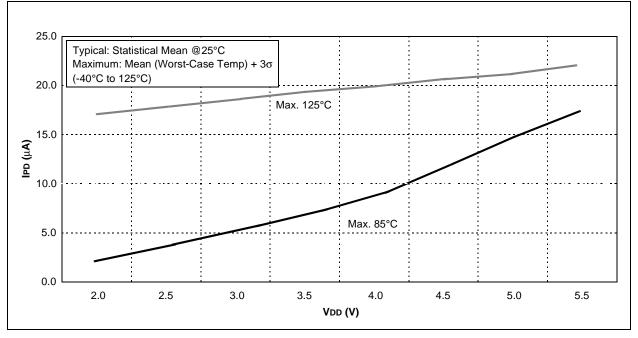

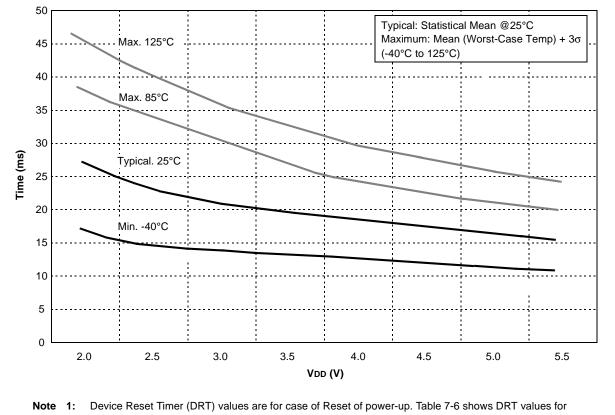

the case of other types of Reset events.

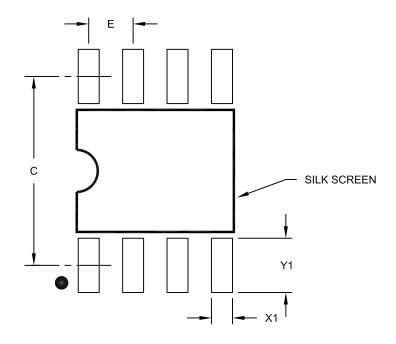

### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | N   | IILLIMETER: | S        |      |

|-------------------------|-----|-------------|----------|------|

| Dimension               | MIN | NOM         | MAX      |      |

| Contact Pitch           | E   |             | 1.27 BSC |      |

| Contact Pad Spacing     | С   |             | 5.40     |      |

| Contact Pad Width (X8)  | X1  |             |          | 0.60 |

| Contact Pad Length (X8) | Y1  |             |          | 1.55 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

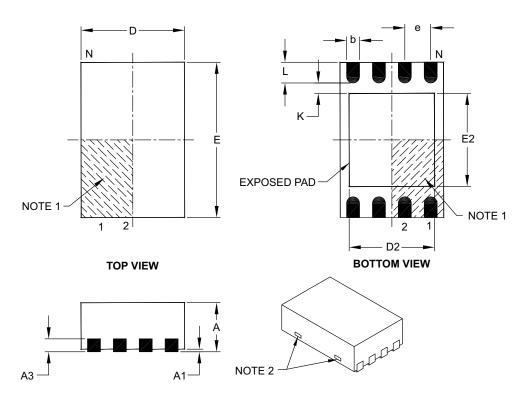

### 8-Lead Plastic Dual Flat, No Lead Package (MC) – 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |          |      |  |

|------------------------|------------------|-------------|----------|------|--|

|                        | Dimension Limits | MIN         | NOM      | MAX  |  |

| Number of Pins         | N                |             | 8        |      |  |

| Pitch                  | e                |             | 0.50 BSC |      |  |

| Overall Height         | A                | 0.80        | 0.90     | 1.00 |  |

| Standoff               | A1               | 0.00        | 0.02     | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF    |          |      |  |

| Overall Length         | D                | 2.00 BSC    |          |      |  |

| Overall Width          | E                |             | 3.00 BSC |      |  |

| Exposed Pad Length     | D2               | 1.30        | -        | 1.55 |  |

| Exposed Pad Width      | E2               | 1.50        | -        | 1.75 |  |

| Contact Width          | b                | 0.20        | 0.25     | 0.30 |  |

| Contact Length         | L                | 0.30        | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | К                | 0.20        | -        | _    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

3. Package is saw singulated.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-123C

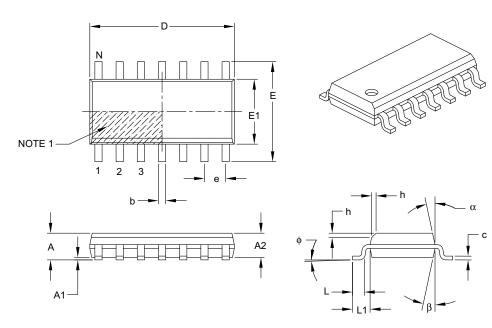

### 14-Lead Plastic Small Outline (SL) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      | MILLIMETERS | 6    |

|--------------------------|------------------|------|-------------|------|

|                          | Dimension Limits | MIN  | NOM         | MAX  |

| Number of Pins           | N                |      | 14          |      |

| Pitch                    | е                |      | 1.27 BSC    |      |

| Overall Height           | A                | -    | -           | 1.75 |

| Molded Package Thickness | A2               | 1.25 | -           | -    |

| Standoff §               | A1               | 0.10 | -           | 0.25 |

| Overall Width            | E                |      | 6.00 BSC    |      |

| Molded Package Width     | E1               |      | 3.90 BSC    |      |

| Overall Length           | D                |      | 8.65 BSC    |      |

| Chamfer (optional)       | h                | 0.25 | -           | 0.50 |

| Foot Length              | L                | 0.40 | -           | 1.27 |

| Footprint                | L1               |      | 1.04 REF    |      |

| Foot Angle               | φ                | 0°   | -           | 8°   |

| Lead Thickness           | С                | 0.17 | -           | 0.25 |

| Lead Width               | b                | 0.31 | -           | 0.51 |

| Mold Draft Angle Top     | α                | 5°   | -           | 15°  |

| Mold Draft Angle Bottom  | β                | 5°   | _           | 15°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-065B

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com

### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:          | Technical Publications Manager         | Total Pages Sent                                       |

|--------------|----------------------------------------|--------------------------------------------------------|

| RE:          | Reader Response                        |                                                        |

| From         | : Name                                 |                                                        |

|              |                                        |                                                        |

|              | Address                                |                                                        |

|              | City / State / ZIP / Country           |                                                        |

|              | Telephone: ()                          | FAX: ()                                                |

| Appli        | cation (optional):                     |                                                        |

| Woul         | ld you like a reply?YN                 |                                                        |

| Devi         | ce: PIC12F508/509/16F505               | Literature Number: DS41236E                            |

| Ques         | stions:                                |                                                        |

| 1. V         | What are the best features of this do  | cument?                                                |

|              |                                        |                                                        |

| _            |                                        |                                                        |

| 2. ⊦         | low does this document meet your       | hardware and software development needs?               |

| _            |                                        |                                                        |

| _            |                                        |                                                        |

| 3. E         | Do you find the organization of this o | locument easy to follow? If not, why?                  |

| _            |                                        |                                                        |

| _            |                                        |                                                        |

| 4. V         | What additions to the document do y    | you think would enhance the structure and subject?     |

| -            |                                        |                                                        |

| -            |                                        |                                                        |

| 5. V         | Vhat deletions from the document c     | ould be made without affecting the overall usefulness? |

| -            |                                        |                                                        |

| -            |                                        | <i>.</i>                                               |

| 6. I         | s there any incorrect or misleading i  | nformation (what and where)?                           |

| -            |                                        |                                                        |

| 7 1          | low would you improve this desume      | not?                                                   |

| <i>i</i> . F | low would you improve this docume      | 211.1                                                  |

| -            |                                        |                                                        |

| _            |                                        |                                                        |