# E·XFL

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 1.5KB (1K x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | ·                                                                        |

| RAM Size                   | 72 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 16-QFN (3x3)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f505-i-mg |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8/14-Pin, 8-Bit Flash Microcontrollers

## **Devices Included In This Data Sheet:**

• PIC12F508 • PIC12F509 • PIC16F505

# High-Performance RISC CPU:

- Only 33 Single-Word Instructions to Learn

- All Single-Cycle Instructions Except for Program Branches, which are Two-Cycle

- 12-Bit Wide Instructions

- 2-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes for Data and Instructions

- 8-Bit Wide Data Path

- 8 Special Function Hardware Registers

- Operating Speed:

- DC 20 MHz clock input (PIC16F505 only)

- DC 200 ns instruction cycle (PIC16F505 only)

- DC 4 MHz clock input

- DC 1000 ns instruction cycle

### **Special Microcontroller Features:**

- 4 MHz Precision Internal Oscillator:

- Factory calibrated to ±1%

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Debugging (ICD) Support

- Power-On Reset (POR)

- Device Reset Timer (DRT)

- Watchdog Timer (WDT) with Dedicated On-Chip RC Oscillator for Reliable Operation

- Programmable Code Protection

- Multiplexed MCLR Input Pin

- Internal Weak Pull-Ups on I/O Pins

- Power-Saving Sleep mode

- Wake-Wp from Sleep on Pin Change

- Selectable Oscillator Options:

- INTRC: 4 MHz precision Internal oscillator

- EXTRC: External low-cost RC oscillator

- XT: Standard crystal/resonator

- HS: High-speed crystal/resonator (PIC16F505 only)

- LP: Power-saving, low-frequency crystal

- EC: High-speed external clock input (PIC16F505 only)

### Low-Power Features/CMOS Technology:

- Operating Current:

- < 175 μA @ 2V, 4 MHz, typical

- Standby Current:

- 100 nA @ 2V, typical

- Low-Power, High-Speed Flash Technology:

- 100,000 Flash endurance

- > 40 year retention

- Fully Static Design

- Wide Operating Voltage Range: 2.0V to 5.5V

- Wide Temperature Range:

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

### Peripheral Features (PIC12F508/509):

- 6 I/O Pins:

- 5 I/O pins with individual direction control

- 1 input only pin

- High current sink/source for direct LED drive

- Wake-on-change

- Weak pull-ups

- 8-Bit Real-Time Clock/Counter (TMR0) with 8-Bit Programmable Prescaler

## Peripheral Features (PIC16F505):

- 12 I/O Pins:

- 11 I/O pins with individual direction control

- 1 input only pin

- High current sink/source for direct LED drive

- Wake-on-change

- Weak pull-ups

- 8-Bit Real-Time Clock/Counter (TMR0) with 8-Bit Programmable Prescaler

| Name           | Function | Input<br>Type | Output<br>Type | Description                                                                                                                                                                                                                                                                                           |

|----------------|----------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0/ICSPDAT    | GP0      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                                     |

|                | ICSPDAT  | ST            | CMOS           | In-Circuit Serial Programming™ data pin.                                                                                                                                                                                                                                                              |

| GP1/ICSPCLK    | GP1      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                                     |

|                | ICSPCLK  | ST            | CMOS           | In-Circuit Serial Programming clock pin.                                                                                                                                                                                                                                                              |

| GP2/T0CKI      | GP2      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                |

|                | T0CKI    | ST            | _              | Clock input to TMR0.                                                                                                                                                                                                                                                                                  |

| GP3/MCLR/Vpp   | GP3      | TTL           | —              | Input pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                                                 |

|                | MCLR     | ST            | _              | Master Clear (Reset). When configured as $\overline{MCLR}$ , this pin is<br>an active-low Reset to the device. Voltage on $\overline{MCLR}$ /VPP must<br>not exceed VDD during normal device operation or the device<br>will enter Programming mode. Weak pull-up always on if<br>configured as MCLR. |

|                | Vpp      | ΗV            | _              | Programming voltage input.                                                                                                                                                                                                                                                                            |

| GP4/OSC2       | GP4      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                |

|                | OSC2     | _             | XTAL           | Oscillator crystal output. Connections to crystal or resonator in Crystal Oscillator mode (XT and LP modes only, GPIO in other modes).                                                                                                                                                                |

| GP5/OSC1/CLKIN | GP5      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                                                |

|                | OSC1     | XTAL          | _              | Oscillator crystal input.                                                                                                                                                                                                                                                                             |

|                | CLKIN    | ST            | _              | External clock source input.                                                                                                                                                                                                                                                                          |

| Vdd            | Vdd      |               | Р              | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                                               |

| Vss            | Vss      |               | Р              | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                                              |

**Legend:** I = Input, O = Output, I/O = Input/Output, P = Power, — = Not used, TTL = TTL input, ST = Schmitt Trigger input, HV = High Voltage

## 4.0 MEMORY ORGANIZATION

The PIC12F508/509/16F505 memories are organized into program memory and data memory. For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using one STATUS register bit. For the PIC12F509 and PIC16F505, with data memory register files of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Select Register (FSR).

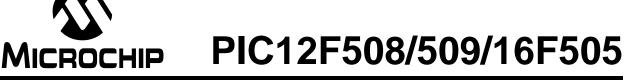

# 4.1 Program Memory Organization for the PIC12F508/509

The PIC12F508 device has a 10-bit Program Counter (PC) and PIC12F509 has a 11-bit Program Counter (PC) capable of addressing a 2K x 12 program memory space.

Only the first 512 x 12 (0000h-01FFh) for the PIC12F508, and 1K x 12 (0000h-03FFh) for the PIC12F509 are physically implemented (see Figure 4-1). Accessing a location above these boundaries will cause a wrap-around within the first 512 x 12 space (PIC12F508) or 1K x 12 space (PIC12F509). The effective Reset vector is a 0000h (see Figure 4-1). Location 01FFh (PIC12F508) and location 03FFh (PIC12F509) contain the internal clock oscillator calibration value. This value should never be overwritten.

### FIGURE 4-1:

### PROGRAM MEMORY MAP AND STACK FOR THE PIC12F508/509

|                    |        |                       |                                                                       |                      | •          |       |       | •     |         |                                              |        |

|--------------------|--------|-----------------------|-----------------------------------------------------------------------|----------------------|------------|-------|-------|-------|---------|----------------------------------------------|--------|

| Address            | Name   | Bit 7                 | Bit 6                                                                 | Bit 5                | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0   | Value on<br>Power-On<br>Reset <sup>(2)</sup> | Page # |

| 00h                | INDF   | Uses Cor<br>register) | Uses Contents of FSR to Address Data Memory (not a physical register) |                      |            |       |       |       |         | XXXX XXXX                                    | 28     |

| 01h                | TMR0   | 8-bit Rea             | I-Time C                                                              | lock/Cou             | nter       |       |       |       |         | xxxx xxxx                                    | 35     |

| 02h <sup>(1)</sup> | PCL    | Low-orde              | er 8 bits c                                                           | of PC                |            |       |       |       |         | 1111 1111                                    | 27     |

| 03h                | STATUS | RBWUF                 |                                                                       | PA0                  | TO         | PD    | Z     | DC    | С       | 0-01 1xxx                                    | 22     |

| 04h                | FSR    | Indirect D            | Data Men                                                              | nory Add             | ress Poir  | nter  |       |       |         | 100x xxxx                                    | 28     |

| 05h                | OSCCAL | CAL6                  | CAL5                                                                  | CAL4                 | CAL3       | CAL2  | CAL1  | CAL0  |         | 1111 111-                                    | 26     |

| 06h                | PORTB  | —                     |                                                                       | RB5                  | RB4        | RB3   | RB2   | RB1   | RB0     | xx xxxx                                      | 31     |

| 07h                | PORTC  | —                     | _                                                                     | RC5                  | RC4        | RC3   | RC2   | RC1   | RC0     | xx xxxx                                      | 31     |

| N/A                | TRISB  | —                     |                                                                       | I/O Control Register |            |       |       |       | 11 1111 | 31                                           |        |

| N/A                | TRISC  | —                     |                                                                       | I/O Cont             | trol Regis | ster  |       |       |         | 11 1111                                      | 31     |

| N/A                | OPTION | RBWU                  | RBPU                                                                  | TOCS                 | TOSE       | PSA   | PS2   | PS1   | PS0     | 1111 1111                                    | 25     |

|                    |        |                       |                                                                       |                      |            |       |       |       |         |                                              |        |

| TABLE 4-2: | SPECIAL FUNCTION REGISTER (SFR) SUMMARY (PIC16F505) |

|------------|-----------------------------------------------------|

|------------|-----------------------------------------------------|

**Legend:** -= unimplemented, read as '0', x = unknown, u = unchanged, q = value depends on condition. **Note 1:** If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

Other (non Power-up) Resets include external reset through MCLR, Watchdog Timer and wake-up on pin change Reset.

### TABLE 5-1:SUMMARY OF PORT REGISTERS

| Address | Name                    | Bit 7 | Bit 6 | Bit 5     | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-------------------------|-------|-------|-----------|------------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | TRISGPIO <sup>(1)</sup> | -     | _     | I/O Contr | ol Registe | r     |       |       |       | 11 1111                       | 11 1111                         |

| N/A     | TRISB <sup>(2)</sup>    | —     | —     | I/O Contr | ol Registe | r     |       |       |       | 11 1111                       | 11 1111                         |

| N/A     | TRISC <sup>(2)</sup>    | _     | —     | I/O Contr | ol Registe | r     |       |       |       | 11 1111                       | 11 1111                         |

| N/A     | OPTION <sup>(1)</sup>   | GPWU  | GPPU  | TOCS      | TOSE       | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | OPTION <sup>(2)</sup>   | RBWU  | RBPU  | TOCS      | TOSE       | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| 03h     | STATUS <sup>(1)</sup>   | GPWUF | —     | PAO       | ТО         | PD    | Z     | DC    | С     | 0-01 1xxx                     | q00q quuu <sup>(3)</sup>        |

| 03h     | STATUS <sup>(2)</sup>   | RBWUF | _     | PAO       | TO         | PD    | Z     | DC    | С     | 0-01 1xxx                     | q00q quuu <b>(3)</b>            |

| 06h     | GPIO <sup>(1)</sup>     | —     | —     | GP5       | GP4        | GP3   | GP2   | GP1   | GP0   | xx xxxx                       | uu uuuu                         |

| 06h     | PORTB <sup>(2)</sup>    | _     | _     | RB5       | RB4        | RB3   | RB2   | RB1   | RB0   | xx xxxx                       | uu uuuu                         |

| 07h     | PORTC <sup>(2)</sup>    | _     | _     | RC5       | RC4        | RC3   | RC2   | RC1   | RC0   | xx xxxx                       | uu uuuu                         |

**Legend:** Shaded cells are not used by Port registers, read as '0'. – = unimplemented, read as '0', x = unknown, u = unchanged, q = depends on condition.

Note 1: PIC12F508/509 only.

2: PIC16F505 only.

3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

### 5.5 I/O Programming Considerations

### 5.5.1 BIDIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit 5 of PORTB/GPIO will cause all eight bits of PORTB/GPIO to be read into the CPU, bit 5 to be set and the PORTB/GPIO value to be written to the output latches. If another bit of PORTB/ GPIO is used as a bidirectional I/O pin (say bit 0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential Read-Modify-Write instructions (e.g., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired OR", "wired AND"). The resulting high output currents may damage the chip.

### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT(e.g., PIC16F505)

| ;Initial PORTB Se<br>;PORTB<5:3> Input<br>;PORTB<2:0> Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | s                                |            |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------|--|--|--|--|--|

| ;<br>;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PORTB latch                      | PORTB pins |  |  |  |  |  |

| BCF PORTB, 4<br>MOVLW 007h;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ;01 -ppp<br>;10 -ppp<br>;10 -ppp | 11 pppp    |  |  |  |  |  |

| <ul> <li>in the point of th</li></ul> |                                  |            |  |  |  |  |  |

### 5.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### Q1 | Q2 | Q3 | Q4 | PC + 1 PC + 3 This example shows a write to PORTB followed by a read from PORTB. PC Instruction Fetched MOVWF PORTB MOVF PORTB, W NOP NOP Data setup time = (0.25 TCY - TPD)where: TCY = instruction cycle RB<5.0> TPD = propagation delay Port pin written here Port pin sampled here Therefore, at higher clock frequencies, a write followed by a read may be problematic. Instruction Executed MOVWE PORTE MOVE PORTE W NOP (Write to PORTB) (Read PORTB)

### FIGURE 5-2: SUCCESSIVE I/O OPERATION (PIC16F505 Shown)

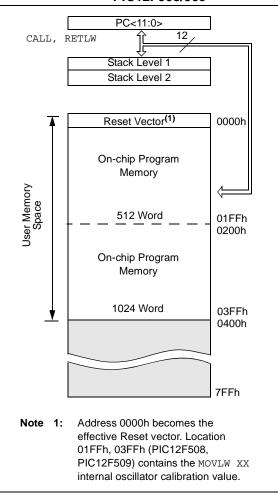

## 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select:

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1 "Using Timer0 with an External Clock".

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit, PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 6.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| PC<br>(Program<br>Counter)        | PC – 1 |            | Q1 Q2 Q3 Q4<br>PC + 1 | PC + 2      | (PC + 3     | $\frac{Q1}{Q2}\frac{Q3}{Q4}$ | PC + 5      | (PC+6)  |

|-----------------------------------|--------|------------|-----------------------|-------------|-------------|------------------------------|-------------|---------|

| Instruction<br>Fetch              |        | MOVWF TMR0 | MOVF TMR0,W           | MOVF TMR0,W | MOVF TMR0,W | MOVF TMR0,W                  | MOVF TMR0,W |         |

| Timer0<br>Instruction<br>Executed | (то)   | T0 + 1 )   | T0 + 2)               | Read TMR0   | NT0         | Read TMR0                    | NT0 + 1)∕   | NT0 + 2 |

### 7.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT time-out Reset during normal operation

- WDT time-out Reset during Sleep

- Wake-up from Sleep on pin change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up on pin change Reset during normal operation. They are not affected by a WDT Reset during Sleep or MCLR Reset during Sleep, since these Resets are viewed as resumption of normal operation. The exceptions to this are TO, PD and RBWUF/GPWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 7-4 for a full description of Reset states of all registers.

| Register           | Address | Power-on Reset           | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change |

|--------------------|---------|--------------------------|----------------------------------------------------|

| W                  | _       | qqqq qqqu <sup>(1)</sup> | qqqq qqqu <sup>(1)</sup>                           |

| INDF               | 00h     | XXXX XXXX                | uuuu uuuu                                          |

| TMR0               | 01h     | xxxx xxxx                | uuuu uuuu                                          |

| PC                 | 02h     | 1111 1111                | 1111 1111                                          |

| STATUS             | 03h     | 0001 1xxx                | q00q quuu <b>(2), (3)</b>                          |

| FSR <sup>(4)</sup> | 04h     | 110x xxxx                | 11uu uuuu                                          |

| FSR <sup>(5)</sup> | 04h     | 111x xxxx                | 111u uuuu                                          |

| OSCCAL             | 05h     | 1111 111-                | uuuu uuu-                                          |

| GPIO               | 06h     | xx xxxx                  | uu uuuu                                            |

| OPTION             | —       | 1111 1111                | 1111 1111                                          |

| TRIS               | —       | 11 1111                  | 11 1111                                            |

|                    |         |                          |                                                    |

### TABLE 7-3: RESET CONDITIONS FOR REGISTERS – PIC12F508/509

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

2: See Table 7-5 for Reset value for specific conditions.

**3:** If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

4: PIC12F509 only.

5: PIC12F508 only.

TMR0

STATUS

OSCCAL

PORTB

PORTC

OPTION

TRISB

TRISC

PC

FSR

| TABLE 7-4: RESET CONDITIONS FOR REGISTERS – PIC16F505 |     |                |                                                  |  |  |  |  |

|-------------------------------------------------------|-----|----------------|--------------------------------------------------|--|--|--|--|

| Register Address                                      |     | Power-on Reset | MCLR Reset, WDT Time-ou<br>Wake-up On Pin Change |  |  |  |  |

| W                                                     | —   | qqqq qqqu(1)   | qqqq qqqu <sup>(1)</sup>                         |  |  |  |  |

| INDF                                                  | 00h | XXXX XXXX      | <u>uuuu</u> uuuu                                 |  |  |  |  |

#### DECET CONDITIONS FOR DECISTERS DICACEEOE

01h

02h

03h

04h

05h

06h

07h

\_

\_

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

XXXX XXXX

1111 1111

0001 1xxx

100x xxxx

1111 111-

--xx xxxx

--xx xxxx

1111 1111

--11 1111

--11 1111

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

- 2: See Table 7-5 for Reset value for specific conditions.

- 3: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

#### **TABLE 7-5**: **RESET CONDITION FOR SPECIAL REGISTERS**

|                                    | STATUS Addr: 03h | PCL Addr: 02h |

|------------------------------------|------------------|---------------|

| Power-on Reset                     | 0001 1xxx        | 1111 1111     |

| MCLR Reset during normal operation | 000u uuuu        | 1111 1111     |

| MCLR Reset during Sleep            | 0001 Ouuu        | 1111 1111     |

| WDT Reset during Sleep             | 0000 Ouuu        | 1111 1111     |

| WDT Reset normal operation         | 0000 uuuu        | 1111 1111     |

| Wake-up from Sleep on pin change   | 1001 Ouuu        | 1111 1111     |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

WDT Time-out,

uuuu uuuu

1111 1111 q00q quuu**(2), (3)**

1uuu uuuu

uuuu uuu-

--uu uuuu

--uu uuuu

1111 1111

--11 1111

--11 1111

| Mnemonic, |         | Description                                       | Cycles           | 12-       | Bit Opc   | Status    | Notes     |          |

|-----------|---------|---------------------------------------------------|------------------|-----------|-----------|-----------|-----------|----------|

| Opera     | ands    | Description                                       | Cycles           | MSb       |           | LSb       | Affected  | notes    |

| ADDWF     | f, d    | Add W and f                                       | 1                | 0001      | 11df      | ffff      | C, DC, Z  | 1, 2, 4  |

| ANDWF     | f, d    | AND W with f                                      | 1                | 0001      | 01df      | ffff      | Z         | 2, 4     |

| CLRF      | f       | Clear f                                           | 1                | 0000      | 011f      | ffff      | Z         | 4        |

| CLRW      | —       | Clear W                                           | 1                | 0000      | 0100      | 0000      | Z         |          |

| COMF      | f, d    | Complement f                                      | 1                | 0010      | 01df      | ffff      | Z         |          |

| DECF      | f, d    | Decrement f                                       | 1                | 0000      | 11df      | ffff      | Z         | 2, 4     |

| DECFSZ    | f, d    | Decrement f, Skip if 0                            | 1 <sup>(2)</sup> | 0010      | 11df      | ffff      | None      | 2, 4     |

| INCF      | f, d    | Increment f                                       | 1                | 0010      | 10df      | ffff      | Z         | 2, 4     |

| INCFSZ    | f, d    | Increment f, Skip if 0                            | 1 <sup>(2)</sup> | 0011      | 11df      | ffff      | None      | 2, 4     |

| IORWF     | f, d    | Inclusive OR W with f                             | 1                | 0001      | 00df      | ffff      | Z         | 2, 4     |

| MOVF      | f, d    | Move f                                            | 1                | 0010      | 00df      | ffff      | Z         | 2, 4     |

| MOVWF     | f       | Move W to f                                       | 1                | 0000      | 001f      | ffff      | None      | 1, 4     |

| NOP       | _       | No Operation                                      | 1                | 0000      | 0000      | 0000      | None      |          |

| RLF       | f, d    | Rotate left f through Carry                       | 1                | 0011      | 01df      | ffff      | С         | 2, 4     |

| RRF       | f, d    | Rotate right f through Carry                      | 1                | 0011      | 00df      | ffff      | С         | 2, 4     |

| SUBWF     | f, d    | Subtract W from f                                 | 1                | 0000      | 10df      | ffff      | C, DC, Z  | 1, 2, 4  |

| SWAPF     | f, d    | Swap f                                            | 1                | 0011      | 10df      | ffff      | None      | 2, 4     |

| XORWF     | f, d    | Exclusive OR W with f                             | 1                | 0001      | 10df      | ffff      | Z         | 2, 4     |

|           |         | BIT-ORIENTED FILE REGISTE                         | R OPER           | ATIONS    | 5         |           |           |          |

| BCF       | f, b    | Bit Clear f                                       | 1                | 0100      | bbbf      | ffff      | None      | 2, 4     |

| BSF       | f, b    | Bit Set f                                         | 1                | 0101      | bbbf      | ffff      | None      | 2, 4     |

| BTFSC     | f, b    | Bit Test f, Skip if Clear                         | 1 <sup>(2)</sup> | 0110      | bbbf      | ffff      | None      |          |

| BTFSS     | f, b    | Bit Test f, Skip if Set                           | 1 <sup>(2)</sup> | 0111      | bbbf      | ffff      | None      |          |

|           |         | LITERAL AND CONTROL                               | OPERATI          | ONS       |           |           |           |          |

| ANDLW     | k       | AND literal with W                                | 1                | 1110      | kkkk      | kkkk      | Z         |          |

| CALL      | k       | Call Subroutine                                   | 2                | 1001      | kkkk      | kkkk      | None      | 1        |

| CLRWDT    | _       | Clear Watchdog Timer                              | 1                | 0000      | 0000      | 0100      | TO, PD    |          |

| GOTO      | k       | Unconditional branch                              | 2                | 101k      | kkkk      | kkkk      | None      |          |

| IORLW     | k       | Inclusive OR literal with W                       | 1                | 1101      | kkkk      | kkkk      | Z         |          |

| MOVLW     | k       | Move literal to W                                 | 1                | 1100      | kkkk      | kkkk      | None      |          |

| OPTION    | _       | Load OPTION register                              | 1                | 0000      | 0000      | 0010      | None      |          |

| RETLW     | k       | Return, place literal in W                        | 2                | 1000      | kkkk      | kkkk      | None      |          |

| SLEEP     | _       | Go into Standby mode                              | 1                | 0000      | 0000      | 0011      | TO, PD    |          |

| TRIS      | f       | Load TRIS register                                | 1                | 0000      | 0000      | Offf      | None      | 3        |

| XORLW     | k       | Exclusive OR literal to W                         | 1                | 1111      | kkkk      | kkkk      | Z         |          |

| Note 1:   | The 9th | bit of the program counter will be forced to a 'o | ' by any i       | nstructio | on that v | writes to | the PC ex | cept for |

### TABLE 8-2: INSTRUCTION SET SUMMARY

ote 1: The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO. See Section 4.7 "Program Counter".

When an I/O register is madified as a function of itself (a g. NONE, DODED, 1), the value used will be that

2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 6, causes the contents of the W register to be written to the tri-state latches of PORTB. A '1' forces the pin to a high-impedance state and disables the output buffers.

4: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

# PIC12F508/509/16F505

| IORWF            | Inclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                            |

| Operation:       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                            |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is '1',<br>the result is placed back in register<br>'f'. |

| MOVWF            | Move W to f                                    |

|------------------|------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                       |

| Operands:        | $0 \le f \le 31$                               |

| Operation:       | $(W) \rightarrow (f)$                          |

| Status Affected: | None                                           |

| Description:     | Move data from the W register to register 'f'. |

| MOVF             | Move f                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                 |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                         |

| Status Affected: | Z                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>moved to destination 'd'. If 'd' is '0',<br>destination is the W register. If 'd'<br>is '1', the destination is file<br>register 'f'. 'd' = 1 is useful as a<br>test of a file register, since status<br>flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                                 |

| Operands:        | $0 \le k \le 255$                                                                                        |

| Operation:       | $k \rightarrow (W)$                                                                                      |

| Status Affected: | None                                                                                                     |

| Description:     | The eight-bit literal 'k' is loaded<br>into the W register. The "don't<br>cares" will assembled as '0's. |

| OPTION           | Load OPTION Register                                              |

|------------------|-------------------------------------------------------------------|

| Syntax:          | [label] OPTION                                                    |

| Operands:        | None                                                              |

| Operation:       | $(W) \rightarrow OPTION$                                          |

| Status Affected: | None                                                              |

| Description:     | The content of the W register is loaded into the OPTION register. |

# PIC12F508/509/16F505

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address). This<br>is a two-cycle instruction. |

| SLEEP            | Enter SLEEP Mode                                                                                                                                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                                                                                                |

| Operands:        | None                                                                                                                                                                                                                                                                                                         |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT; \\ 0 \rightarrow WDT \mbox{ prescaler}; \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                                                                   |

| Status Affected: | TO, PD, RBWUF                                                                                                                                                                                                                                                                                                |

| Description:     | Time-out Status bit (TO) is set. The<br>Power-down Status bit (PD) is<br>cleared.<br>RBWUF is unaffected.<br>The WDT and its prescaler are<br>cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped.<br>See Section 7.9 "Power-down<br>Mode (Sleep)" on Sleep for more<br>details. |

| RLF              | Rotate Left f th                                                             | nrough Carry                                                             |

|------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Syntax:          | [ label ]                                                                    | RLF f,d                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$             |                                                                          |

| Operation:       | See description                                                              | n below                                                                  |

| Status Affected: | С                                                                            |                                                                          |

| Description:     | the Carry flag. I<br>is placed in the<br>'1', the result is<br>register 'f'. | to the left through<br>f 'd' is '0', the result<br>W register. If 'd' is |

| SUBWF            | Subtract W from f                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                                |

| Operation:       | $(f) - (W) \rightarrow (dest)$                                                                                                                                                                  |

| Status Affected: | C, DC, Z                                                                                                                                                                                        |

| Description:     | Subtract (2's complement method)<br>the W register from register 'f'. If 'd'<br>is '0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                                                                      |

| Operation:       | See description below                                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

|                  | C register 'f'                                                                                                                                                                                                        |

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in \ [0,1] \end{array}$                                                                                                   |

| Operation:       | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                          |

| Status Affected: | None                                                                                                                                                               |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in W register. If 'd' is '1', the result is placed in register 'f'. |

### 9.7 MPLAB ICE 2000 High-Performance In-Circuit Emulator

The MPLAB ICE 2000 In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 In-Circuit Emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The architecture of the MPLAB ICE 2000 In-Circuit Emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 In-Circuit Emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows<sup>®</sup> 32-bit operating system were chosen to best make these features available in a simple, unified application.

### 9.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The MPLAB REAL ICE probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with the popular MPLAB ICD 2 system (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

MPLAB REAL ICE is field upgradeable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added, such as software breakpoints and assembly code trace. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, real-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 9.9 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC MCUs and dsPIC DSCs. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers costeffective, in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single stepping and watching variables, and CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

### 9.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

### 9.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

### 9.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

### 9.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# **10.0 ELECTRICAL CHARACTERISTICS**

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                      | 40°C to +125°C                   |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Storage temperature                                                                                                 | 65°C to +150°C                   |

| Voltage on VDD with respect to Vss                                                                                  | 0 to +6.5V                       |

| Voltage on MCLR with respect to Vss                                                                                 | 0 to +13.5V                      |

| Voltage on all other pins with respect to Vss                                                                       | -0.3V to (VDD + 0.3V)            |

| Total power dissipation <sup>(1)</sup>                                                                              | 800 mW                           |

| Max. current out of Vss pin                                                                                         | 200 mA                           |

| Max. current into Vod pin                                                                                           | 150 mA                           |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                        | ±20 mA                           |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                      | ±20 mA                           |

| Max. output current sunk by any I/O pin                                                                             | 25 mA                            |

| Max. output current sourced by any I/O pin                                                                          | 25 mA                            |

| Max. output current sourced by I/O port                                                                             | 75 mA                            |

| Max. output current sunk by I/O port                                                                                | 75 mA                            |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\Sigma$ IOH} + $\Sigma$ {(VDD $-V$ O | H) X IOH} + $\Sigma$ (VOL X IOL) |

<sup>†</sup>NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## TABLE 10-6: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER – PIC12F508/509/16F505

| AC CHARACTERISTICS |      | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)} \end{array}$ |          |                    |            |          |                                                  |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|------------|----------|--------------------------------------------------|

| Param<br>No.       | Sym. | Characteristic                                                                                                                                                                                                                                                 | Min.     | Typ <sup>(1)</sup> | Max.       | Units    | Conditions                                       |

| 30                 | TMCL | MCLR Pulse Width (low)                                                                                                                                                                                                                                         | 2000*    | _                  | _          | ns       | VDD = 5.0V                                       |

| 31                 | Twdt | Watchdog Timer Time-out Period (no prescaler)                                                                                                                                                                                                                  | 9*<br>9* | 18*<br>18*         | 30*<br>40* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 32                 | Tdrt | Device Reset Timer Period <sup>(2)</sup>                                                                                                                                                                                                                       | 9*<br>9* | 18*<br>18*         | 30*<br>40* | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 34                 | Tioz | I/O High-impedance from MCLR low                                                                                                                                                                                                                               | —        |                    | 2000*      | ns       |                                                  |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC12F508/509/16F505

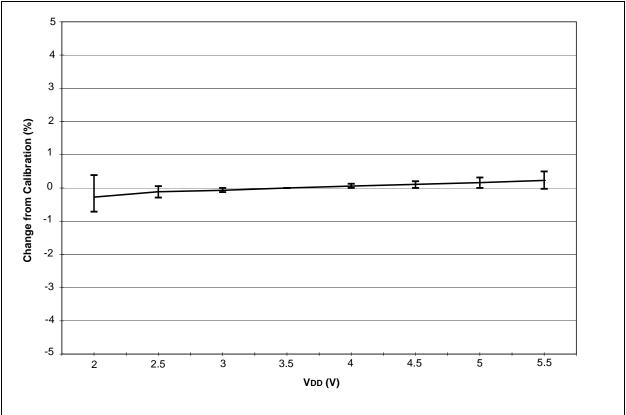

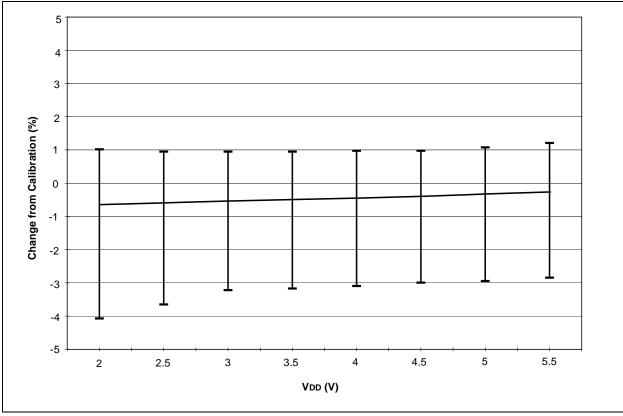

### FIGURE 11-14: TYPICAL INTOSC FREQUENCY CHANGE vs VDD (25°C)

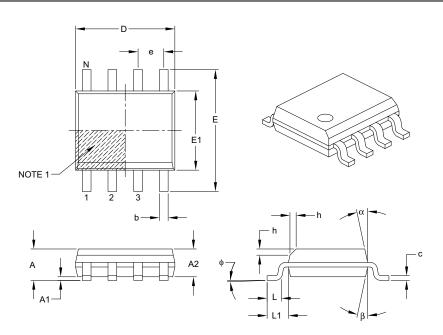

### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |               | MILLIMETERS |          |      |  |

|--------------------------|---------------|-------------|----------|------|--|

| Dime                     | ension Limits | MIN         | NOM      | MAX  |  |

| Number of Pins           | N             |             | 8        |      |  |

| Pitch                    | е             | 1.27 BSC    |          |      |  |

| Overall Height           | А             | -           | -        | 1.75 |  |

| Molded Package Thickness | A2            | 1.25        | -        | -    |  |

| Standoff §               | A1            | 0.10        | -        | 0.25 |  |

| Overall Width            | E             | 6.00 BSC    |          |      |  |

| Molded Package Width     | E1            | 3.90 BSC    |          |      |  |

| Overall Length           | D             | 4.90 BSC    |          |      |  |

| Chamfer (optional)       | h             | 0.25        | -        | 0.50 |  |

| Foot Length              | L             | 0.40        | -        | 1.27 |  |

| Footprint                | L1            |             | 1.04 REF |      |  |

| Foot Angle               | ф             | 0°          | -        | 8°   |  |

| Lead Thickness           | С             | 0.17        | _        | 0.25 |  |

| Lead Width               | b             | 0.31        | _        | 0.51 |  |

| Mold Draft Angle Top     | α             | 5°          | _        | 15°  |  |

| Mold Draft Angle Bottom  | β             | 5°          | _        | 15°  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-057B

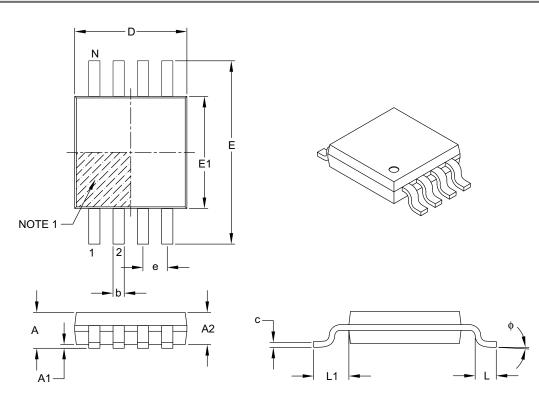

### 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |                  | MILLIMETERS |          |      |  |

|--------------------------|------------------|-------------|----------|------|--|

| Dimension                | Dimension Limits |             | NOM      | MAX  |  |

| Number of Pins           | Ν                |             | 8        |      |  |

| Pitch                    | е                |             | 0.65 BSC |      |  |

| Overall Height           | Α                | -           | -        | 1.10 |  |

| Molded Package Thickness | A2               | 0.75        | 0.85     | 0.95 |  |

| Standoff                 | A1               | 0.00        | -        | 0.15 |  |

| Overall Width            | Е                |             | 4.90 BSC |      |  |

| Molded Package Width     | E1               |             | 3.00 BSC |      |  |