#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | SH-2                                                                           |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 50MHz                                                                          |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SCI                                                 |

| Peripherals                | DMA, POR, PWM, WDT                                                             |

| Number of I/O              | 74                                                                             |

| Program Memory Size        | •                                                                              |

| Program Memory Type        | ROMIess                                                                        |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 8x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 112-BQFP                                                                       |

| Supplier Device Package    | 112-QFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd6417144f50v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 10.11 DMA Transfer Example in Cyc       | le-Steal Mode1                         | 95  |

|------------------------------------------------|----------------------------------------|-----|

| Figure 10.12 DMA Transfer Example in Burs      | st Mode1                               | 95  |

| Figure 10.13 Bus Handling when Multiple Cl     | hannels Are Operating1                 | 97  |

| Figure 10.14 Cycle Steal, Dual Address and I   | Level Detection (Fastest Operation)2   | 200 |

| Figure 10.15 Cycle Steal, Dual Address and I   | Level Detection (Normal Operation)2    | 200 |

| Figure 10.16 Cycle Steal, Single Address and   | Level Detection (Fastest Operation)2   | 200 |

| Figure 10.17 Cycle Steal, Single Address and   | Level Detection (Normal Operation)2    | 200 |

| Figure 10.18 Burst Mode, Dual Address and      | Level Detection (Fastest Operation)2   | 201 |

| Figure 10.19 Burst Mode, Dual Address and      | Level Detection (Normal Operation)2    | 201 |

| Figure 10.20 Burst Mode, Single Address and    | d Level Detection (Fastest Operation)2 | 201 |

| Figure 10.21 Burst Mode, Single Address and    | d Level Detection (Normal Operation)2  | 202 |

| Figure 10.22 Burst Mode, Dual Address and      | Edge Detection2                        | 202 |

|                                                | d Edge Detection2                      |     |

|                                                | n2                                     |     |

| Figure 10.25 Source Address Reload Function    | n Timing Chart2                        | 203 |

| Section 11 Multi-Function Timer Pulse Un       | iit (MTU)                              |     |

| Figure 11.1 Block Diagram of MTU               |                                        | 216 |

| Figure 11.2 Complementary PWM Mode Ou          | tput Level Example2                    | 254 |

| Figure 11.3 Example of Counter Operation S     | etting Procedure2                      | 259 |

| Figure 11.4 Free-Running Counter Operation     | ۱2                                     | 260 |

| Figure 11.5 Periodic Counter Operation         |                                        | 261 |

| Figure 11.6 Example of Setting Procedure for   | r Waveform Output by Compare Match2    | 261 |

| Figure 11.7 Example of 0 Output/1 Output O     | peration2                              | 262 |

| Figure 11.8 Example of Toggle Output Operation | ation2                                 | 262 |

| Figure 11.9 Example of Input Capture Operation | tion Setting Procedure2                | 263 |

| Figure 11.10 Example of Input Capture Oper     | ation2                                 | 264 |

|                                                | tion Setting Procedure2                |     |

| Figure 11.12 Example of Synchronous Opera      | ntion2                                 | 266 |

| Figure 11.13 Compare Match Buffer Operation    | on2                                    | 267 |

|                                                | 2                                      |     |

| Figure 11.15 Example of Buffer Operation Se    | etting Procedure2                      | 267 |

| Figure 11.16 Example of Buffer Operation (1    |                                        | 268 |

| Figure 11.17 Example of Buffer Operation (2    | 2)2                                    | 269 |

| Figure 11.18 Cascaded Operation Setting Pro    | 2                                      | 270 |

| Figure 11.19 Example of Cascaded Operation     | n2                                     | 270 |

| Figure 11.20 Example of PWM Mode Setting       | g Procedure2                           | 273 |

| Figure 11.21 Example of PWM Mode Operat        | tion (1)2                              | 273 |

| Figure 11.22 Example of PWM Mode Operat        | tion (2)2                              | 274 |

|                                                | tion (3)2                              |     |

| Figure 11.24 Example of Phase Counting Mc      | ode Setting Procedure2                 | 276 |

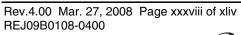

the IRQ status register (ISR). Interrupts held pending due to edge detection are cleared by a power-on reset or a manual reset.

### Figure 6.3 Interrupt Sequence Flowchart

Rev.4.00 Mar. 27, 2008 Page 94 of 882 REJ09B0108-0400

# 9.4 Address Map

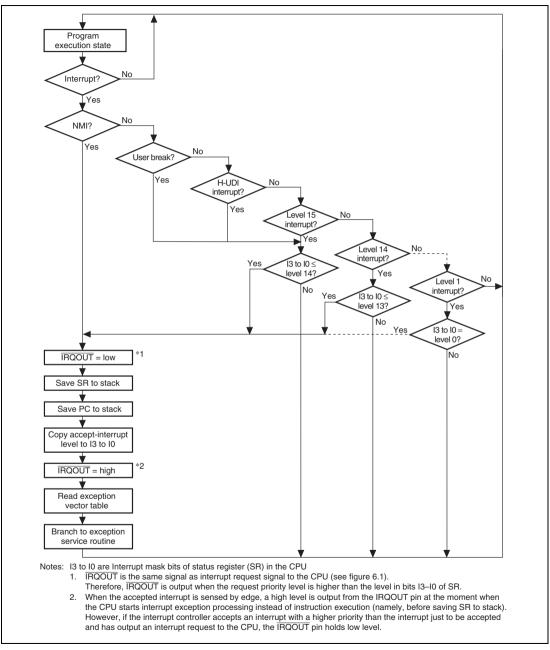

Figure 9.2 shows the address format used by this LSI.

Figure 9.2 Address Format

This chip uses 32-bit addresses:

- Bits A31 to A24 are used to select the type of space and are not output externally.

- Bits A23 and A22 are decoded and output as chip select signals ( $\overline{\text{CS0}}$  to  $\overline{\text{CS7}}$ ) for the corresponding areas when bits A31 to A24 are 00000000 or 00000001.

- Bits A21 to A0 are output externally.

Table 9.2 shows the address map.

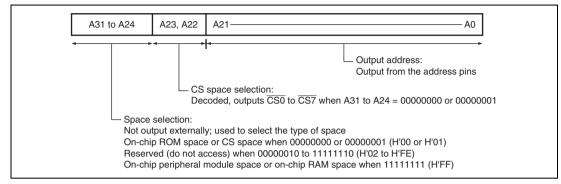

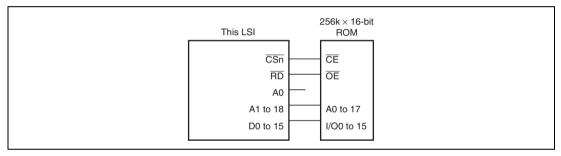

# 9.9 Memory Connection Example

Since A21 to A18 function as input ports at power-on reset, take the procedure such as pulling down as required.

Figure 9.10 Example of 8-bit Data Bus Width ROM Connection

Figure 9.11 Example of 16-bit Data Bus Width ROM Connection

#### 11.6.2 Interrupt Signal Timing

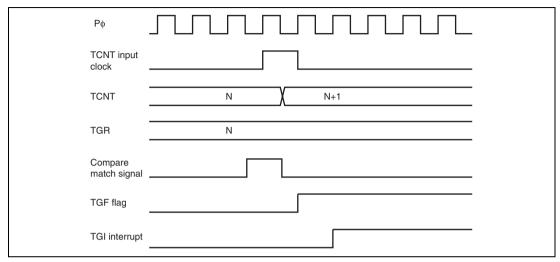

**TGF Flag Setting Timing in Case of Compare Match:** Figure 11.64 shows the timing for setting of the TGF flag in TSR on compare match, and TGI interrupt request signal timing.

Figure 11.64 TGI Interrupt Timing (Compare Match)

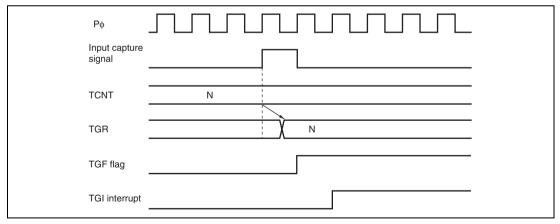

**TGF Flag Setting Timing in Case of Input Capture:** Figure 11.65 shows the timing for setting of the TGF flag in TSR on input capture, and TGI interrupt request signal timing.

Figure 11.65 TGI Interrupt Timing (Input Capture)

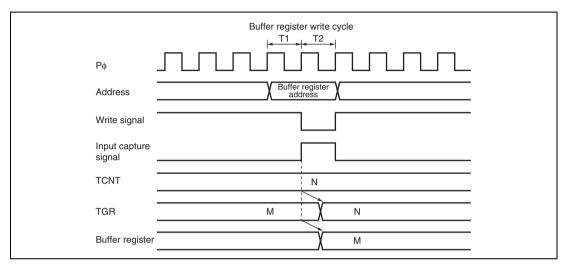

### 11.7.10 Contention between Buffer Register Write and Input Capture

If an input capture signal is generated in the T2 state of a buffer register write cycle, the buffer operation takes precedence and the write to the buffer register is not performed.

Figure 11.78 shows the timing in this case.

Figure 11.78 Contention between Buffer Register Write and Input Capture

### 11.7.11 TCNT2 Write and Overflow/Underflow Contention in Cascade Connection

With timer counters TCNT1 and TCNT2 in a cascade connection, when a contention occurs during TCNT\_1 count (during a TCNT\_2 overflow/underflow) in the  $T_2$  state of the TCNT\_2 write cycle, the write to TCNT\_2 is conducted, and the TCNT\_1 count signal is disabled. At this point, if there is match with TGRA\_1 and the TCNT\_1 value, a compare signal is issued. Furthermore, when the TCNT\_1 count clock is selected as the input capture source of channel 0, TGRA\_0 to D\_0 carry out the input capture operation. In addition, when the compare match/input capture is selected as the input capture source of TGRB\_1, TGRB\_1 carries out input capture operation. The timing is shown in figure 11.79.

For cascade connections, be sure to synchronize settings for channels 1 and 2 when setting TCNT clearing.

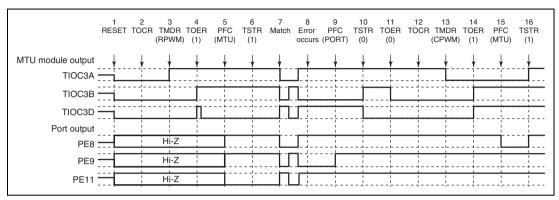

**Operation when Error Occurs during Reset-Synchronous PWM Mode Operation, and Operation is Restarted in Complementary PWM Mode:** Figure 11.112 shows an explanatory diagram of the case where an error occurs in reset-synchronous PWM mode and operation is restarted in complementary PWM mode after re-setting.

- 1 to 10 are the same as in figure 11.110.

- 11. Disable channel 3 and 4 output with TOER.

- 12. Select the complementary PWM output level and cyclic output enabling/disabling with TOCR.

- 13. Set complementary PWM. (The MTU cyclic output pin goes low.)

- 14. Enable channel 3 and 4 output with TOER.

- 15. Set MTU output with the PFC.

- 16. Operation is restarted by TSTR.

| Bit    | Bit Name | Initial value | R/W | Description                                                            |

|--------|----------|---------------|-----|------------------------------------------------------------------------|

| 8      | OIE      | 0             | R/W | Output Short Interrupt Enable                                          |

|        |          |               |     | This bit makes interrupt requests when the OSF bit of the OCSR is set. |

|        |          |               |     | 00: Interrupt requests disabled                                        |

|        |          |               |     | 01: Interrupt request enabled                                          |

| 7 to ( | D —      | All 0         | R   | Reserved                                                               |

|        |          |               |     | These bits are always read as 0. The write value should always be 0.   |

Note: \* Only 0 can be written to write the flag.

#### 11.9.4 Operation

#### **Input Level Detection Operation:**

If the input conditions set by the ICSR1 occur on any of the POE pins, all high-current pins become high-impedance state. Note however, that these high-current pins become high-impedance state only when general input/output function or MTU function is selected in these pins.

1. Falling Edge Detection

When a change from high to low level is input to the  $\overline{\text{POE}}$  pins.

2. Low-Level Detection

Figure 11.115 shows the low-level detection operation. Sixteen continuous low levels are sampled with the sampling clock established by the ICSR1. If even one high level is detected during this interval, the low level is not accepted.

Sampling starts when detecting the falling edge of the  $\overline{POE}$  pin. Thereby, negate the  $\overline{POE}$  pin when using  $\overline{POE}$  function after sampling.

Furthermore, the timing when the large-current pins enter the high-impedance state from the sampling clock is the same in both falling-edge detection and in low-level detection.

# 12.3.3 Reset Control/Status Register (RSTCSR)

RSTCSR is an 8-bit readable/writable register that controls the generation of the internal reset signal when TCNT overflows, and selects the type of internal reset signal.

| Bit    | Bit Name | Initial Value | R/W    | Description                                                                                                                              |

|--------|----------|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | WOVF     | 0             | R/(W)* | Watchdog Timer Overflow Flag                                                                                                             |

|        |          |               |        | This bit is set when TCNT overflows in watchdog timer mode. This bit cannot be set in interval timer mode.                               |

|        |          |               |        | [Setting condition]                                                                                                                      |

|        |          |               |        | <ul> <li>Set when TCNT overflows in watchdog timer<br/>mode</li> </ul>                                                                   |

|        |          |               |        | [Clearing condition]                                                                                                                     |

|        |          |               |        | Cleared by reading WOVF, and then writing 0 to WOVF                                                                                      |

| 6      | RSTE     | 0             | R/W    | Reset Enable                                                                                                                             |

|        |          |               |        | Specifies whether or not an internal reset signal is generated in the chip if TCNT overflows in watchdog timer mode.                     |

|        |          |               |        | 0: Internal reset signal is not generated even if<br>TCNT overflows<br>(Though this LSI is not reset, TCNT and TCSR in<br>WDT are reset) |

|        |          |               |        | 1: Internal reset signal is generated if TCNT overflows                                                                                  |

| 5      | RSTS     | 0             | R/W    | Reset Select                                                                                                                             |

|        |          |               |        | Selects the type of internal reset generated if TCNT overflows in watchdog timer mode.                                                   |

|        |          |               |        | 0: Power-on reset                                                                                                                        |

|        |          |               |        | 1: Manual reset                                                                                                                          |

| 4 to 0 | )        | All 1         | R      | Reserved                                                                                                                                 |

|        |          |               |        | These bits are always read as 1. The write value should always be 1.                                                                     |

Note: \* Only 0 can be written for flag clearing.

#### 12.6.3 Changing CKS2 to CKS0 Bit Values

If the values of bits CKS2 to CKS0 in the timer control/status register (TCSR) are rewritten while the WDT is running, the count may not increment correctly. Always stop the watchdog timer (by clearing the TME bit to 0) before changing the values of bits CKS2 to CKS0.

#### 12.6.4 Changing between Watchdog Timer and Interval Timer Modes

To prevent incorrect operation, always stop the watchdog timer (by clearing the TME bit to 0) before switching between interval timer mode and watchdog timer mode.

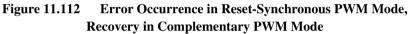

### 12.6.5 System Reset by WDTOVF Signal

If a  $\overline{\text{WDTOVF}}$  output signal is input to the  $\overline{\text{RES}}$  pin, the chip cannot initialize correctly.

Avoid inputting the  $\overline{\text{WDTOVF}}$  signal to the  $\overline{\text{RES}}$  pin directly. To reset the entire system with the  $\overline{\text{WDTOVF}}$  signal, use the circuit shown in figure 12.9.

Figure 12.9 Example of System Reset Circuit Using WDTOVF Signal

#### 12.6.6 Internal Reset in Watchdog Timer Mode

If the RSTE bit is cleared to 0 in watchdog timer mode, the chip will not be reset internally when a TCNT overflow occurs, but TCNT and TCSR in the WDT will be reset.

#### 13. Serial Communication Interface (SCI)

SSD Status Elan

Table 13.11 shows the states of the SSR status flags and receive data handling when a receive error is detected. If a receive error is detected, the RDRF flag retains its state before receiving data. Reception cannot be resumed while a receive error flag is set to 1. Accordingly, clear the OER, FER, PER, and RDRF bits to 0 before resuming reception. Figure 13.9 shows a sample flow chart for serial data reception.

|       | 22H 2 | tatus Flag | g   |                    |                                              |

|-------|-------|------------|-----|--------------------|----------------------------------------------|

| RDRF* | OER   | FER        | PER | Receive Data       | Receive Error Type                           |

| 1     | 1     | 0          | 0   | Lost               | Overrun error                                |

| 0     | 0     | 1          | 0   | Transferred to RDR | Framing error                                |

| 0     | 0     | 0          | 1   | Transferred to RDR | Parity error                                 |

| 1     | 1     | 1          | 0   | Lost               | Overrun error + framing error                |

| 1     | 1     | 0          | 1   | Lost               | Overrun error + parity error                 |

| 0     | 0     | 1          | 1   | Transferred to RDR | Framing error + parity error                 |

| 1     | 1     | 1          | 1   | Lost               | Overrun error + framing error + parity error |

#### Table 13.11 SSR Status Flags and Receive Data Handling

Note: \* The RDRF flag retains its state before data reception.

# Section 14 I<sup>2</sup>C Bus Interface (IIC) Option

The I<sup>2</sup>C bus interface is an optional feature. When using this optional feature, pay attention to the following point:

• A "W" is added to the product-type name of a mask-ROM product which includes an optional feature.

This LSI incorporates a single-channel  $I^2C$  bus interface. The  $I^2C$  bus interface conforms to the Philips  $I^2C$  bus (Inter-IC bus) interface system and provides a subset of the functions. Note, however, that the configuration of the registers that control the  $I^2C$  bus differs on some points from that of Phillips'.

Data transfer is carried out by the data line (SDA0) and clock line (SCL0). This makes the interface efficient in terms of the use of area for connectors and printed circuits.

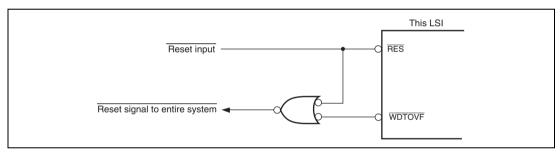

#### 14.4.7 Timing for Setting IRIC and the Control of SCL

The timing with which the interrupt-request flag (IRIC) is set varies according to the settings of the WAIT bit in ICMR, FS bit in SAR, and the FSX bit in SARX. When the ICDRE and ICDRF flags are set to 1, the level on SCL is automatically set low in synchronization with the internal clock after the transfer of one frame of data. Figures 14.25 to 14.27 show the timing with which IRIC is set and the control of SCL.

Figure 14.25 IRIC Flag Set Timing and the Control of SCL (1)

21. RAM

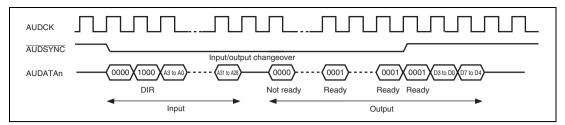

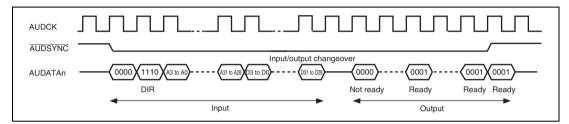

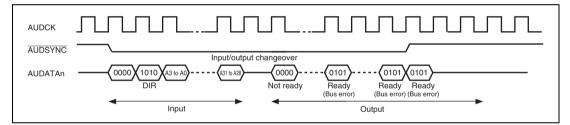

Figure 23.5 Example of Read Operation (Byte Read)

Figure 23.6 Example of Write Operation (Longword Write)

Figure 23.7 Example of Error Occurrence (Longword Read)

| Register<br>abbreviation | Bit7  | Bit6  | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0  | Module          |

|--------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|

| TCR_3                    | CCLR2 | CCLR1 | CCLR0 | CKEG1 | CKEG0 | TPSC2 | TPSC1 | TPSC0 | MTU             |

| TCR_4                    | CCLR2 | CCLR1 | CCLR0 | CKEG1 | CKEG0 | TPSC2 | TPSC1 | TPSC0 | (Channels 3, 4) |

| TMDR_3                   | _     | _     | BFB   | BFA   | MD3   | MD2   | MD1   | MD0   |                 |

| TMDR_4                   | _     | _     | BFB   | BFA   | MD3   | MD2   | MD1   | MD0   |                 |

| TIORH_3                  | IOB3  | IOB2  | IOB1  | IOB0  | IOA3  | IOA2  | IOA1  | IOA0  |                 |

| TIORL_3                  | IOD3  | IOD2  | IOD1  | IOD0  | IOC3  | IOC2  | IOC1  | IOC0  |                 |

| TIORH_4                  | IOB3  | IOB2  | IOB1  | IOB0  | IOA3  | IOA2  | IOA1  | IOA0  |                 |

| TIORL_4                  | IOD3  | IOD2  | IOD1  | IOD0  | IOC3  | IOC2  | IOC1  | IOC0  |                 |

| TIER_3                   | TTGE  | _     | _     | TCIEV | TGIED | TGIEC | TGIEB | TGIEA |                 |

| TIER_4                   | TTGE  | _     | _     | TCIEV | TGIED | TGIEC | TGIEB | TGIEA |                 |

| TOER                     | _     | _     | OE4D  | OE4C  | OE3D  | OE4B  | OE4A  | OE3B  |                 |

| TOCR                     | _     | PSYE  | _     | _     | _     | _     | OLSN  | OLSP  |                 |

| TGCR                     | _     | BDC   | Ν     | Р     | FB    | WF    | VF    | UF    |                 |

| TCNT_3                   |       |       |       |       |       |       |       |       |                 |

| TCNT_4                   |       |       |       |       |       |       |       |       |                 |

| TCDR                     |       |       |       |       |       |       |       |       | _               |

| TDDR                     |       |       |       |       |       |       |       |       |                 |

| TGRA_3                   |       |       |       |       |       |       |       |       |                 |

| TGRB_3                   |       |       |       |       |       |       |       |       |                 |

| TGRA_4                   |       |       |       |       |       |       |       |       | _               |

| TGRB_4                   |       |       |       |       |       |       |       |       | _               |

| TCNTS                    |       |       |       |       |       |       |       |       | _               |

| TCBR                     |       |       |       |       |       |       |       |       |                 |

### 26.3.9 Serial Communication Interface (SCI) Timing

Table 26.11 shows serial communication interface timing.

#### Table 26.11 Serial Communication Interface Timing

Conditions:  $V_{cc} = PLLV_{cc} = 3.3 V \pm 0.3 V$ ,  $AV_{cc} = 3.3 V \pm 0.3 V$ ,  $AV_{cc} = V_{cc} \pm 0.3 V$ ,  $AV_{ref} = 3.0 V$  to  $AV_{cc}$ ,  $V_{ss} = PLLV_{ss} = AV_{ss} = 0 V$ ,  $T_a = -20^{\circ}C$  to  $+75^{\circ}C$  (regular specifications),  $T_a = -40^{\circ}C$  to  $+85^{\circ}C$  (wide-range specifications), When programming or erasing flash memory,  $T_a = -20^{\circ}C$  to  $+75^{\circ}C$ .

| Item                         | Symbol                           | Min.              | Max.                   | Unit            | Figure            |        |

|------------------------------|----------------------------------|-------------------|------------------------|-----------------|-------------------|--------|

| Input clock cycle (asynchro  | Input clock cycle (asynchronous) |                   |                        |                 | t <sub>pcyc</sub> | Figure |

| Input clock cycle (clock syn | ic)                              | t <sub>scyc</sub> | 6                      |                 | t <sub>pcyc</sub> | 26.19  |

| Input clock pulse width      |                                  | t <sub>sckw</sub> | 0.4                    | 0.6             | t <sub>scyc</sub> | _      |

| Input clock rise time        |                                  | t <sub>sckr</sub> | _                      | 1.5             | t <sub>pcyc</sub> | _      |

| Input clock fall time        | Input clock fall time            |                   |                        | 1.5             | t <sub>pcyc</sub> | _      |

| Transmit data delay time     | asynchronous                     | t <sub>TxD</sub>  | _                      | 100             | ns                | Figure |

| Received data setup time     | _                                | t <sub>RxS</sub>  | 100                    | _               | ns                | 26.20  |

| Received data hold time      | _                                | t <sub>RxH</sub>  | 100                    |                 | ns                | _      |

| Transmit data delay time     | clock sync                       | t <sub>TxD</sub>  | _                      | $t_{pcyc} + 43$ | ns                | _      |

| Received data setup time     | (When SCK                        | t <sub>RxS</sub>  | $t_{pcyc} + 25$        | _               | ns                | _      |

| Received data hold time      | - input)                         | t <sub>sxH</sub>  | $t_{pcyc} + 25$        | _               | ns                | _      |

| Transmit data delay time     | clock sync                       | t <sub>_txD</sub> | _                      | 65              | ns                | _      |

| Received data setup time     | (When SCK                        | t <sub>RxS</sub>  | $0.5 t_{_{pcyc}} + 50$ |                 | ns                | _      |

| Received data hold time      | output)                          | t <sub>BxH</sub>  | 1.5 $t_{pcyc}$         |                 | ns                |        |

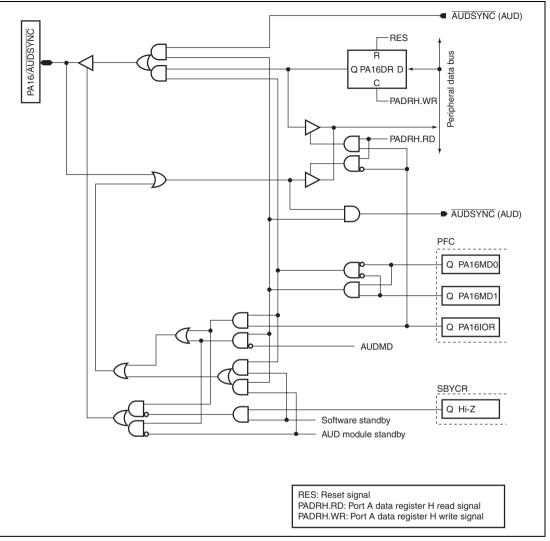

# Figure D.8 PA16/AUDSYNC

|              | Symb         | ol in Figure D.8 | Available Products |                                               |                   |                                               |  |  |

|--------------|--------------|------------------|--------------------|-----------------------------------------------|-------------------|-----------------------------------------------|--|--|

|              |              |                  |                    | SH7144                                        |                   | SH7145                                        |  |  |

| Pins         | <b>PA</b> 16 | AUDSYNC          | F-ZTAT<br>version  | Masked ROM<br>version/<br>ROM less<br>version | F-ZTAT<br>version | Masked ROM<br>version/<br>ROM less<br>version |  |  |

| PA16/AUDSYNC | PA16         | AUDSYNC<br>(AUD) |                    |                                               |                   |                                               |  |  |

| Item                                                                                                                                               | Page | Revision (See Manual for Details)                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------|

| 11.7.16 Contention<br>between<br>Overflow/Underflow and<br>Counter Clearing<br>Figure 11.83 Contention<br>between Overflow and<br>Counter Clearing | 333  | Figure amended  P  TCNT input Clock  TCNT H'FFFF H'0000  Counter clear signal  TGF  TCFV Disabled  |

| 11.7.17 Contention<br>between TCNT Write and<br>Overflow/Underflow<br>Figure 11.84 Contention<br>between TCNT Write and<br>Overflow                | 334  | Figure amended  TCNT write cycle  P  Address  TCNT address  Write signal  TCNT H'FFFF M  TCFV flag |

| 11.7.22 Note on Buffer<br>Operation Setting                                                                                                        | 335  | Newly added                                                                                        |

| 12.1 Features                                                                                                                                      | 379  | Description replaced                                                                               |

| 13.4.4 SCI Initialization<br>(Asynchronous Mode)                                                                                                   | 430  | Figure replaced                                                                                    |

| Figure 13.5 Sample SCI<br>Initialization Flowchart                                                                                                 |      |                                                                                                    |